Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 100MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 3x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck256mp508t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4 ICSP Pins

The PGCx and PGDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGCx and PGDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to PICkit<sup>™</sup> 3, MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup> emulator.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE emulator connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) (DS51765)

- "Development Tools Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator" (poster) (DS51749)

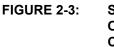

## 2.5 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator (POSC) and a low-frequency Secondary Oscillator (SOSC). For details, see Section 9.2 "Primary Oscillator (POSC)".

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### : SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| REGISTER      | 3-2: CURC                                                                                                                                                                            | UN: CORE (                                                 |                                   | EGISTER             |                   |                    |              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|-------------------|--------------------|--------------|

| R/W-0         | U-0                                                                                                                                                                                  | R/W-0                                                      | R/W-0                             | R/W-0               | R-0               | R-0                | R-0          |

| VAR           | —                                                                                                                                                                                    | US1                                                        | US0                               | EDT <sup>(1)</sup>  | DL2               | DL1                | DL0          |

| bit 15        |                                                                                                                                                                                      |                                                            |                                   |                     |                   |                    | bit 8        |

| R/W-0         | R/W-0                                                                                                                                                                                | R/W-1                                                      | R/W-0                             | R/C-0               | R-0               | R/W-0              | R/W-0        |

| SATA          | SATB                                                                                                                                                                                 | SATDW                                                      | ACCSAT                            | IPL3 <sup>(2)</sup> | SFA               | RND                | IF           |

| bit 7         | SAID                                                                                                                                                                                 | SAIDW                                                      | ACCOAT                            | IFL3, ,             | SFA               | RND                | bit (        |

|               |                                                                                                                                                                                      |                                                            |                                   |                     |                   |                    |              |

| Legend:       |                                                                                                                                                                                      | C = Clearable                                              | e bit                             |                     |                   |                    |              |

| R = Readable  | e bit                                                                                                                                                                                | W = Writable                                               | bit                               | U = Unimpler        | mented bit, read  | 1 as '0'           |              |

| -n = Value at | POR                                                                                                                                                                                  | '1' = Bit is se                                            | t                                 | '0' = Bit is cle    | ared              | x = Bit is unkn    | own          |

| bit 15        | 1 = Variable e                                                                                                                                                                       | e Exception Pr<br>exception proc                           | essing is enab                    | led                 |                   |                    |              |

| bit 14        | Unimplemen                                                                                                                                                                           | ted: Read as                                               | 0'                                |                     |                   |                    |              |

| bit 13-12     | <b>US&lt;1:0&gt;:</b> DS                                                                                                                                                             | P Multiply Uns                                             | igned/Signed                      | Control bits        |                   |                    |              |

|               | <ul> <li>11 = Reserved</li> <li>10 = DSP engine multiplies are mixed sign</li> <li>01 = DSP engine multiplies are unsigned</li> <li>00 = DSP engine multiplies are signed</li> </ul> |                                                            |                                   |                     |                   |                    |              |

| bit 11        | EDT: Early Do Loop Termination Control bit <sup>(1)</sup>                                                                                                                            |                                                            |                                   |                     |                   |                    |              |

|               |                                                                                                                                                                                      | es executing Do                                            |                                   |                     | nt loop iteratior | Ì                  |              |

| bit 10-8      | DL<2:0>: DO Loop Nesting Level Status bits<br>111 = 7 DO loops are active                                                                                                            |                                                            |                                   |                     |                   |                    |              |

|               | <br>001 = 1 DO lo<br>000 = 0 DO lo                                                                                                                                                   | oop is active<br>oops are active                           |                                   |                     |                   |                    |              |

| bit 7         | SATA: ACCA                                                                                                                                                                           | Saturation En                                              | able bit                          |                     |                   |                    |              |

|               | 1 = Accumulator A saturation is enabled<br>0 = Accumulator A saturation is disabled                                                                                                  |                                                            |                                   |                     |                   |                    |              |

| bit 6         | SATB: ACCB Saturation Enable bit                                                                                                                                                     |                                                            |                                   |                     |                   |                    |              |

|               | 1 = Accumulator B saturation is enabled<br>0 = Accumulator B saturation is disabled                                                                                                  |                                                            |                                   |                     |                   |                    |              |

| bit 5         | SATDW: Data                                                                                                                                                                          | a Space Write                                              | from DSP Eng                      | ine Saturation      | Enable bit        |                    |              |

|               | SATDW: Data Space Write from DSP Engine Saturation Enable bit<br>1 = Data Space write saturation is enabled<br>0 = Data Space write saturation is disabled                           |                                                            |                                   |                     |                   |                    |              |

| bit 4         | ACCSAT: Accumulator Saturation Mode Select bit<br>1 = 9.31 saturation (super saturation)<br>0 = 1.31 saturation (normal saturation)                                                  |                                                            |                                   |                     |                   |                    |              |

| bit 3         | <b>IPL3:</b> CPU In<br>1 = CPU Inter                                                                                                                                                 | terrupt Priority<br>rrupt Priority Lo<br>rrupt Priority Lo | Level Status b<br>evel is greater | than 7              |                   |                    |              |

|               | nis bit is always r                                                                                                                                                                  |                                                            |                                   |                     |                   |                    |              |

| 2: Th         | ne IPL3 bit is cor                                                                                                                                                                   | catenated with                                             | the IPL<2:0>                      | bits (SR<7:5>       | ) to form the CI  | PU Interrupt Price | ority Level. |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

#### 6.0 RESETS

- **Note 1:** This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices.

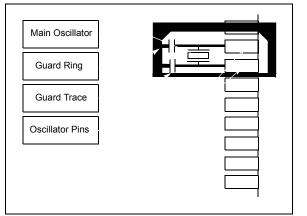

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

#### FIGURE 6-1: **RESET SYSTEM BLOCK DIAGRAM**

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the BOR and POR bits (RCON<1:0>) that are set. The user application can set or clear any bit, at any time, during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSCx bits is loaded into the NOSC<2:0> (OSCCON<10:8>) bits on Reset, which in turn, initializes the system clock.

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      | •                    |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

|                      |                      |                      |       |       |       |       |       |

|                      |                      | a a:                 |       |       |       |       |       |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

**3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

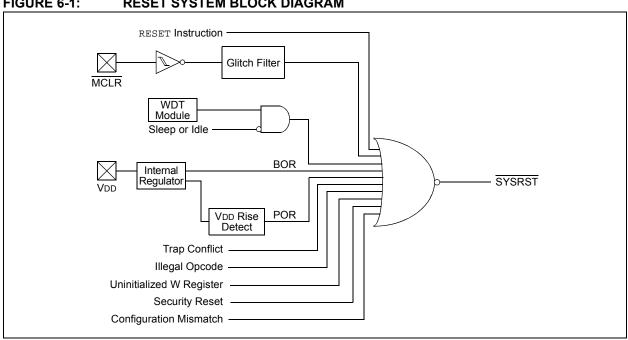

The Primary Oscillator and internal FRC Oscillator sources can optionally use an on-chip PLL to obtain higher operating speeds. Figure 9-3 illustrates a block diagram of the PLL module. For PLL operation, the following requirements must be met at all times without exception:

- The PLL Input Frequency (FPLLI) must be in the range of 8 MHz to 64 MHz

- The PFD Input Frequency (FPFD) must be in the range of 8 MHz to (FVCO/16) MHz

The VCO Output Frequency (Fvco) must be in the range of 400 MHz to 1600 MHz

## 9.6 Oscillator Control Registers

| U-0     | R-0   | R-0   | R-0   | U-0               | R/W-y                | R/W-y                | R/W-y                |

|---------|-------|-------|-------|-------------------|----------------------|----------------------|----------------------|

| —       | COSC2 | COSC1 | COSC0 | —                 | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15  |       |       |       |                   |                      |                      | bit 8                |

|         |       |       |       |                   |                      |                      |                      |

| R/W-0   | U-0   | R-0   | U-0   | R/W-0             | U-0                  | U-0                  | R/W-0                |

| CLKLOCK |       | LOCK  | —     | CF <sup>(3)</sup> | —                    | —                    | OSWEN                |

| bit 7   |       |       |       |                   |                      |                      | bit 0                |

#### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| Legend:           | y = Value set from Co | y = Value set from Configuration bits on POR |                    |  |  |  |

|-------------------|-----------------------|----------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                        | t, read as '0'     |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits (read-only)

- 111 = Fast RC Oscillator (FRC) with Divide-by-n (FRCDIVN)

- 110 = Backup FRC (BFRC)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Reserved default to FRC

- 011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

- 111 = Fast RC Oscillator (FRC) with Divide-by-n (FRCDIVN)

- 110 = Backup FRC (BFRC)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Reserved default to FRC

- 011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

#### bit 7 CLKLOCK: Clock Lock Enable bit

- 1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

- 0 = Clock and PLL selections are not locked, configurations may be modified

- bit 6 Unimplemented: Read as '0'

- bit 5 LOCK: PLL Lock Status bit (read-only)

- 1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

- 0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

- bit 4 Unimplemented: Read as '0'

- **Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

NOTES:

#### REGISTER 11-46: C1BDIAG0H: CAN BUS DIAGNOSTICS REGISTER 0 HIGH

| R/W-0                              | R/W-0          | R/W-0            | R/W-0             | R/W-0         | R/W-0           | R/W-0          | R/W-0          |

|------------------------------------|----------------|------------------|-------------------|---------------|-----------------|----------------|----------------|

|                                    |                |                  | DTERF             | RCNT<7:0>     |                 |                |                |

| bit 15                             |                |                  |                   |               |                 |                | bit 8          |

| DAMA                               | <b>D</b> 444 0 | <b>D</b> 444 0   | <b>D</b> # 4 / 0  |               | <b>D</b> (14) 0 | <b>D</b> #44 0 | <b>D</b> 444 0 |

| R/W-0                              | R/W-0          | R/W-0            | R/W-0             | R/W-0         | R/W-0           | R/W-0          | R/W-0          |

|                                    |                |                  | DRERF             | RCNT<7:0>     |                 |                |                |

| bit 7                              |                |                  |                   |               |                 |                | bit 0          |

| Legend:                            |                |                  |                   |               |                 |                |                |

| R = Readable                       | bit            | W = Writable bit |                   | U = Unimpleme | ented bit, rea  | ad as '0'      |                |

| -n = Value at POR '1' = Bit is set |                |                  | '0' = Bit is clea | red           | x = Bit is unki | nown           |                |

| bit 15-8 | DTERRCNT<7:0>: Data Bit Rate Transmit Error Counter bits |

|----------|----------------------------------------------------------|

|          |                                                          |

bit 7-0 DRERRCNT<7:0>: Data Bit Rate Receive Error Counter bits

### REGISTER 11-47: C1BDIAG0L: CAN BUS DIAGNOSTICS REGISTER 0 LOW

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0     | R/W-0              | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|-----------|--------------------|-------|-------|

|                                    |       |       | NTERF                              | RCNT<7:0> |                    |       |       |

| bit 15                             |       |       |                                    |           |                    |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0     | R/W-0              | R/W-0 | R/W-0 |

|                                    |       |       | NRERF                              | RCNT<7:0> |                    |       |       |

| bit 7                              |       |       |                                    |           |                    |       | bit 0 |

|                                    |       |       |                                    |           |                    |       |       |

| Legend:                            |       |       |                                    |           |                    |       |       |

| R = Readable bit W = Writable bit  |       | oit   | U = Unimplemented bit, read as '0' |           |                    |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared               |           | x = Bit is unknown |       |       |

bit 15-8 NTERRCNT<7:0>: Nominal Bit Rate Transmit Error Counter bits

bit 7-0 NRERRCNT<7:0>: Nominal Bit Rate Receive Error Counter bits

## **REGISTER 12-10: PWMEVTy: PWM EVENT OUTPUT CONTROL REGISTER y**<sup>(5)</sup> **(CONTINUED)**

bit 2-0 EVTyPGS<2:0>: PWM Event Source Selection bits<sup>(2)</sup> 111 = PWM Generator 8 110 = PWM Generator 7 ... 000 = PWM Generator 1

- **Note 1:** The event signal is stretched using peripheral\_clk because different PWM Generators may be operating from different clock sources.

- 2: No event will be produced if the selected PWM Generator is not present.

- 3: This is the PWM Generator output signal prior to output mode logic and any output override logic.

- **4:** This signal should be the PGx\_clk domain signal prior to any synchronization into the system clock domain.

- 5: 'y' denotes a common instance (A-F).

#### REGISTER 14-9: SLPxCONL: DACx SLOPE CONTROL LOW REGISTER (CONTINUED)

The selected Slope Stop A signal is logically OR'd with the selected Slope Stop B signal to terminate the slope function.

| Slope Stop A<br>Signal Selection | Master         |

|----------------------------------|----------------|

| 1101-1111                        | 1              |

| 1000                             | PWM8 Trigger 2 |

| 0111                             | PWM7 Trigger 2 |

| 0110                             | PWM6 Trigger 2 |

| 0101                             | PWM5 Trigger 2 |

| 0100                             | PWM4 Trigger 2 |

| 0011                             | PWM3 Trigger 2 |

| 0010                             | PWM2 Trigger 2 |

| 0001                             | PWM1 Trigger 2 |

| 0000                             | 0              |

## bit 7-4 SLPSTOPB<3:0>: Slope Stop B Signal Select bits

The selected Slope Stop B signal is logically OR'd with the selected Slope Stop A signal to terminate the slope function.

| Slope Start B<br>Signal Selection | Master   |

|-----------------------------------|----------|

| 0100-1111                         | 1        |

| 0011                              | CMP3 Out |

| 0010                              | CMP2 Out |

| 0001                              | CMP1 Out |

| 0000                              | 0        |

#### bit 3-0

SLPSTRT<3:0>: Slope Start Signal Select bits

| Slope Start<br>Signal Selection | Master         |

|---------------------------------|----------------|

| 1101-1111                       | 1              |

| 1000                            | PWM8 Trigger 1 |

| 0111                            | PWM7 Trigger 1 |

| 0110                            | PWM6 Trigger 1 |

| 0101                            | PWM5 Trigger 1 |

| 0100                            | PWM4 Trigger 1 |

| 0011                            | PWM3 Trigger 1 |

| 0010                            | PWM2 Trigger 1 |

| 0001                            | PWM1 Trigger 1 |

| 0000                            | 0              |

bit 11-8 SLPSTOPA<3:0>: Slope Stop A Signal Select bits

#### U-0 U-0 R/W-0. HS R/W-0. HS U-0 R/W-0. HS R/W-0, HS R/W-0, HS RXRPTIF TXRPTIF BTCIF WTCIF GTCIF \_\_\_\_ bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 RXRPTIE TXRPTIE BTCIE WTCIE GTCIE bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-14 Unimplemented: Read as '0' bit 13 **RXRPTIF:** Receive Repeat Interrupt Flag bit 1 = Parity error has persisted after the same character has been received five times (four retransmits) 0 = Flag is cleared **TXRPTIF:** Transmit Repeat Interrupt Flag bit bit 12 1 = Line error has been detected after the last retransmit per TXRPT<1:0> 0 = Flag is cleared bit 11 Unimplemented: Read as '0' bit 10 **BTCIF:** Block Time Counter Interrupt Flag bit 1 = Block Time Counter has reached 0 0 = Block Time Counter has not reached 0 bit 9 WTCIF: Waiting Time Counter Interrupt Flag bit 1 = Waiting Time Counter has reached 0 0 = Waiting Time Counter has not reached 0 bit 8 **GTCIF:** Guard Time Counter Interrupt Flag bit 1 = Guard Time Counter has reached 0 0 = Guard Time Counter has not reached 0 bit 7-6 Unimplemented: Read as '0' **RXRPTIE:** Receive Repeat Interrupt Enable bit bit 5 1 = An interrupt is invoked when a parity error has persisted after the same character has been received five times (four retransmits) 0 = Interrupt is disabled bit 4 **TXRPTIE:** Transmit Repeat Interrupt Enable bit 1 = An interrupt is invoked when a line error is detected after the last retransmit per TXRPT<1:0> has been completed 0 = Interrupt is disabled bit 3 Unimplemented: Read as '0' bit 2 BTCIE: Block Time Counter Interrupt Enable bit 1 = Block Time Counter interrupt is enabled 0 = Block Time Counter interrupt is disabled bit 1 WTCIE: Waiting Time Counter Interrupt Enable bit 1 = Waiting Time Counter interrupt is enabled 0 = Waiting Time Counter Interrupt is disabled bit 0 GTCIE: Guard Time Counter interrupt enable bit 1 = Guard Time Counter interrupt is enabled 0 = Guard Time Counter interrupt is disabled

### REGISTER 16-16: UxSCINT: UARTx SMART CARD INTERRUPT REGISTER

| IADLE 10-2. I | ADLE 10-2. IZCA REGERVED ADDREGGEG |                                        |  |  |  |  |  |  |

|---------------|------------------------------------|----------------------------------------|--|--|--|--|--|--|

| Slave Address | R/W Bit                            | Description                            |  |  |  |  |  |  |

| 0000 000      | 0                                  | General Call Address <sup>(2)</sup>    |  |  |  |  |  |  |

| 0000 0000     | 1                                  | Start Byte                             |  |  |  |  |  |  |

| 0000 001      | х                                  | Cbus Address                           |  |  |  |  |  |  |

| 0000 01x      | х                                  | Reserved                               |  |  |  |  |  |  |

| 0000 1xx      | x                                  | HS Mode Master Code                    |  |  |  |  |  |  |

| 1111 0xx      | x                                  | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |  |  |  |

| 1111 1xx      | х                                  | Reserved                               |  |  |  |  |  |  |

## TABLE 18-2: I2Cx RESERVED ADDRESSES<sup>(1)</sup>

**Note 1:** The address bits listed here will never cause an address match independent of address mask settings.

2: This address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

NOTES:

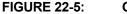

## 22.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module, on compare match events, has the ability to generate a single output transition or a train of output pulses. Like most PIC<sup>®</sup> MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 22-2 shows the various modes available in Output Compare modes.

| TABLE 22-2: OUTPUT COMPARE x/PWMx MOD | ES |

|---------------------------------------|----|

|---------------------------------------|----|

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                      |                  |  |  |

|------------------------------|-----------------------|-------------------------------------|------------------|--|--|

| 0001                         | 0                     | Output High on Compare (16-bit)     |                  |  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)     |                  |  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)      |                  |  |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)      | Single Edge Mode |  |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)   |                  |  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)   |                  |  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)          | Dual Edge Mode   |  |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered) | PWM Mode         |  |  |

#### OUTPUT COMPARE x BLOCK DIAGRAM

## 24.2 PTG Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS LOW REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | U-0 | R/W-0, HC             | R/W-0                  | R/W-0   |

|--------|-----|---------|---------|-----|-----------------------|------------------------|---------|

| PTGEN  | _   | PTGSIDL | PTGTOGL |     | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS |

| bit 15 |     |         |         |     |                       |                        | bit 8   |

| R/W-0, HC | R/W-0, HS | R/W-0, HS, HC | U-0 | U-0 | U-0 | R/W-0                  | R/W-0                  |

|-----------|-----------|---------------|-----|-----|-----|------------------------|------------------------|

| PTGSTRT   | PTGWDTO   | PTGBUSY       |     | —   | —   | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7 bit |           |               |     |     |     |                        |                        |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit              |

|-------------------|-----------------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |

| bit 15  | PTGEN: PTG Enable bit                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PTG is enabled                                                                                                                               |

|         | 0 = PTG is disabled                                                                                                                              |

| bit 14  | Unimplemented: Read as '0'                                                                                                                       |

| bit 13  | PTGSIDL: PTG Freeze in Debug Mode bit                                                                                                            |

|         | 1 = Halts PTG operation when device is Idle                                                                                                      |

|         | 0 = PTG operation continues when device is Idle                                                                                                  |

| bit 12  | PTGTOGL: PTG Toggle Trigger Output bit                                                                                                           |

|         | 1 = Toggles state of TRIG output for each execution of PTGTRIG                                                                                   |

|         | 0 = Generates a single TRIG pulse for each execution of PTGTRIG                                                                                  |

| bit 11  | Unimplemented: Read as '0'                                                                                                                       |

| bit 10  | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                  |

|         | 1 = Toggles state of TRIG output for each execution of PTGTRIG                                                                                   |

| h:10    | 0 = Generates a single TRIG pulse for each execution of PTGTRIG                                                                                  |

| bit 9   | PTGSSEN: PTG Single-Step Command bit <sup>(3)</sup>                                                                                              |

|         | 1 = Enables single Step when in Debug mode<br>0 = Disables single Step                                                                           |

| bit 8   |                                                                                                                                                  |

| DILO    | <b>PTGIVIS:</b> PTG Counter/Timer Visibility bit<br>1 = Reading the PTGSDLIM, PTGCxLIM or PTGTxLIM registers returns the current values of their |

|         | corresponding Counter/Timer registers (PTGSDLIM, PTGCxLIM and PTGTxLIM)                                                                          |

|         | 0 = Reading the PTGSDLIM, PTGCxLIM or PTGTxLIM registers returns the value of these Limit registers                                              |

| bit 7   | PTGSTRT: PTG Start Sequencer bit                                                                                                                 |

|         | 1 = Starts to sequentially execute the commands (Continuous mode)                                                                                |

|         | 0 = Stops executing the commands                                                                                                                 |

| bit 6   | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                  |

|         | 1 = PTG Watchdog Timer has timed out                                                                                                             |

|         | 0 = PTG Watchdog Timer has not timed out                                                                                                         |

| bit 5   | PTGBUSY: PTG State Machine Busy bit                                                                                                              |

|         | 1 = PTG is running on the selected clock source; no SFR writes are allowed to PTGCLK<2:0> or<br>PTGDIV<4:0>                                      |

|         | 0 = PTG state machine is not running                                                                                                             |

| Note 1: | These bits apply to the PTGWHI and PTGWLO commands only.                                                                                         |

| 2:      | This bit is only used with the PTGCTRL Step command software trigger option.                                                                     |

| •       |                                                                                                                                                  |

3: The PTGSSEN bit may only be written when in Debug mode.

| ) Step<br>Comman            | d OPTION<3:0> | Option Description                                                                   |

|-----------------------------|---------------|--------------------------------------------------------------------------------------|

| PTGWHI(1)                   | 0000          | PTGI0 (see Table 24-3 for input assignments).                                        |

| or                          | •             | •                                                                                    |

| PTGWLO(1)                   | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 1111          | PTGI15 (see Table 24-3 for input assignments).                                       |

| PTGIRQ <sup>(1)</sup>       | 0000          | Generate PTG Interrupt 0.                                                            |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 0111          | Generate PTG Interrupt 7.                                                            |

|                             | 1000          | Reserved; do not use.                                                                |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 1111          | Reserved; do not use.                                                                |

| PTGTRIG                     | 00000         | PTGO0 (see Table 24-4 for output assignments).                                       |

|                             | 00001         | PTGO1 (see Table 24-4 for output assignments).                                       |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 11110         | PTGO30 (see Table 24-4 for output assignments).                                      |

| (1)                         | 11111         | PTGO31 (see Table 24-4 for output assignments).                                      |

| PTGWHI(1)                   | 0000          | PTGI0 (see specific device data sheet for input assignments).                        |

| or<br><sub>PTGWLO</sub> (1) | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •<br>DTC/45 (and specific davies data short for input periodente)                    |

| (1)                         | 1111          | PTGI15 (see specific device data sheet for input assignments).                       |

| PTGIRQ(1)                   | 0000          | Generate PTG Interrupt 0 (see specific device data sheet for interrupt assignments). |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             |                                                                                      |

|                             | 0111          | Generate PTG Interrupt 7 (see specific device data sheet for interrupt assignments). |

|                             | 1000          | Reserved; do not use.                                                                |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | •             | •                                                                                    |

|                             | 1111          | Reserved; do not use.                                                                |

| PTGTRIG                     | 00000         | PTGO0 (see specific device data sheet for assignments).                              |

|                             | 00001         | PTGO1 (see specific device data sheet for assignments).                              |

# TABLE 24-2: PTG COMMAND OPTIONS (CONTINUED)

Note 1: All reserved commands or options will execute, but they do not have any affect (i.e., execute as a NOP instruction).

## 30.2 Device Calibration and Identification

The dsPIC33CK256MP508 devices have two Identification registers, near the end of configuration memory space, that store the Device ID (DEVID) and Device Revision (DEVREV). These registers are used to determine the mask, variant and manufacturing information about the device. These registers are read-only and are shown in Register 30-18 and Register 30-19.

### REGISTER 30-18: DEVREV: DEVICE REVISION REGISTER

| R       | R                 | R | R      | R            | R          | R | R      |

|---------|-------------------|---|--------|--------------|------------|---|--------|

|         |                   |   | DEVREV | /<23:16>     |            |   |        |

| bit 23  |                   |   |        |              |            |   | bit 16 |

|         |                   |   |        |              |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

|         |                   |   | DEVRE  | V<15:8>      |            |   |        |

| bit 15  |                   |   |        |              |            |   | bit 8  |

|         |                   |   |        |              |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

|         |                   |   | DEVRE  | :V<7:0>      |            |   |        |

| bit 7   |                   |   |        |              |            |   | bit 0  |

|         |                   |   |        |              |            |   |        |

| Legend: | R = Read-only bit |   |        | U = Unimpler | mented bit |   |        |

bit 23-0 **DEVREV<23:0>:** Device Revision bits

#### **REGISTER 30-19: DEVID: DEVICE ID REGISTERS**

| U-1           | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |  |

|---------------|-----|-----|-----|-----|-----|-----|-----|--|

| _             | —   | —   | —   | —   | —   | —   | —   |  |

| bit 23 bit 16 |     |     |     |     |     |     |     |  |

| R      | R      | R      | R      | R      | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R                   | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> | DEV2 <sup>(1)</sup> | DEV1 <sup>(1)</sup> | DEV0 <sup>(1)</sup> |

| bit 7               |                     |                     |                     |                     |                     |                     | bit 0               |

Legend: R = Read-only bit U = Unimplemented bit

bit 23-16 Unimplemented: Read as '1'

- bit 15-8 **FAMID<7:0>:** Device Family Identifier bits

- 0111 1100 = dsPIC33CK256MP508 family

- bit 7-0 **DEV<7:0>:** Individual Device Identifier bits<sup>(1)</sup>

Note 1: See Table 30-4 for the list of Device Identifier bits.

## 30.3 User OTP Memory

The dsPIC33CK256MP508 family devices contain 64 One-Time-Programmable (OTP) double words, located at addresses, 801700h through 8017FEh. Each 48-bit OTP double word can only be written one time. The OTP Words can be used for storing checksums, code revisions, manufacturing dates, manufacturing lot numbers or any other application-specific information.

The OTP area is not cleared by any erase command. This memory can be written only once.

## 30.4 On-Chip Voltage Regulators

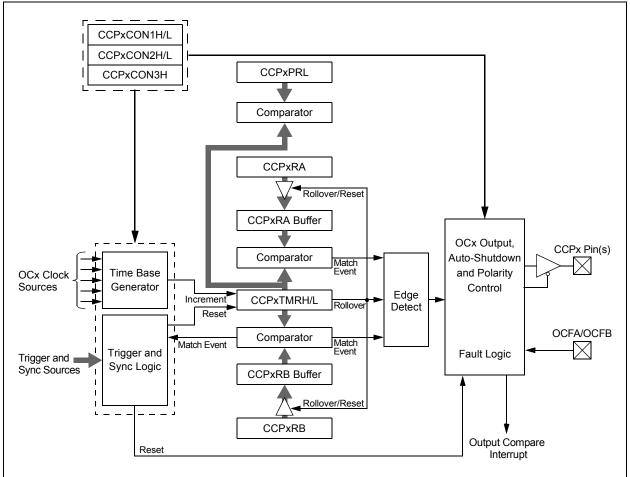

dsPIC33CK256MP508 family devices have a capacitorless internal voltage regulator to supply power to the core at 1.2V (typical). A pair of voltage regulators, VREG1 and VREG2 together, provide power for the core. The PLL is powered using a separate regulator, VREGPLL, as shown in Figure 30-1.

The regulators have Low-Power and Standby modes for use in Sleep modes. For additional information about Sleep, see **Section 29.2.1 "Sleep Mode"**.

When the regulators are in Low-Power mode (LPWREN = 1), the power available to the core is limited. Before the LPWREN bit is set, the device should be placed into a lower power state by disabling peripherals and lowering CPU frequency (e.g., 8 MHz FRC without PLL).

The output voltages of the three regulators can be controlled independently by the user, which gives the capability to save additional power during Sleep mode.

## FIGURE 30-1: INTERNAL REGULATOR

## TABLE 33-9:WATCHDOG TIMER DELTA CURRENT $(\triangle IwDT)^{(1)}$

| Operating Conditions:3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |      |       |            |      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|------|--|--|

| Parameter No.                                                                                                                                                                               | Тур. | Max. | Units | Conditions |      |  |  |

| DC61                                                                                                                                                                                        | 0.75 | 5    | μA    | -40°C      |      |  |  |

|                                                                                                                                                                                             | 2.0  | 12   | μA    | +25°C      | 3.3V |  |  |

|                                                                                                                                                                                             | 3.88 | 24   | μA    | +85°C      | 3.3V |  |  |

|                                                                                                                                                                                             | 5.69 | 40   | μA    | +125°C     |      |  |  |

**Note 1:** The  $\triangle$ IWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

| Operating Con<br>Operating temp |      | -40°C | $3 \le TA \le +8$ |            | ial  |                                                                                 |  |  |

|---------------------------------|------|-------|-------------------|------------|------|---------------------------------------------------------------------------------|--|--|

| Parameter No.                   | Тур. | Max.  | Units             | Conditions |      |                                                                                 |  |  |

| DC100                           | 5.96 | 6.6   | mA                | -40°C      | 3.3V |                                                                                 |  |  |

|                                 | 5.99 | 6.7   | mA                | +25°C      |      | PWM Input (AFPLLO = 500 MHz)                                                    |  |  |

|                                 | 5.92 | 6.9   | mA                | +85°C      |      | (AVCO = 1000 MHz, PLLFBD = 125,<br>APLLDIV1 = 2)                                |  |  |

|                                 | 5.47 | 7     | mA                | +125°C     |      | · · ·,                                                                          |  |  |

| DC101                           | 4.89 | 5.4   | mA                | -40°C      | 3.3V |                                                                                 |  |  |

|                                 | 4.91 | 5.5   | mA                | +25°C      |      | PWM Input (AFPLLO = 400 MHz),<br>(AVCO = 400 MHz, PLLFBD = 50,<br>APLLDIV1 = 1) |  |  |

|                                 | 4.85 | 5.7   | mA                | +85°C      |      |                                                                                 |  |  |

|                                 | 4.42 | 5.7   | mA                | +125°C     |      | ··· · · · · · · · · · · · · · · · ·                                             |  |  |

| DC102                           | 2.77 | 3.7   | mA                | -40°C      | 3.3V | PWM Input (AFPLLO = 200 MHz),<br>(AVCO = 400 MHz, PLLFBD = 50,<br>APLLDIV1 = 2) |  |  |

|                                 | 2.75 | 3.7   | mA                | +25°C      |      |                                                                                 |  |  |

|                                 | 2.7  | 3.7   | mA                | +85°C      |      |                                                                                 |  |  |

|                                 | 2.26 | 3.7   | mA                | +125°C     |      | ,                                                                               |  |  |

| DC103                           | 1.67 | 2     | mA                | -40°C      | 3.3V | PWM Input (AFPLLO = 100 MHz),<br>(AVCO = 400 MHz, PLLFBD = 50,<br>APLLDIV1 = 4) |  |  |

|                                 | 1.66 | 2.2   | mA                | +25°C      |      |                                                                                 |  |  |

|                                 | 1.63 | 2.3   | mA                | +85°C      |      |                                                                                 |  |  |

|                                 | 1.17 | 2.3   | mA                | +125°C     |      | , ,                                                                             |  |  |

TABLE 33-10: PWM DELTA CURRENT<sup>(1)</sup>

**Note 1:** APLL current is not included. The APLL current will be the same if more than 1 PWM is running. Listed delta currents are for only one PWM instance. All parameters are characterized but not tested during manufacturing.

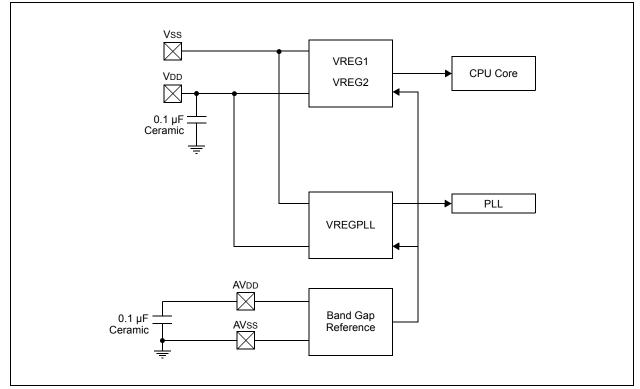

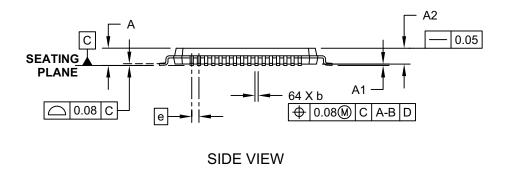

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-085C Sheet 1 of 2