Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck32mp206t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

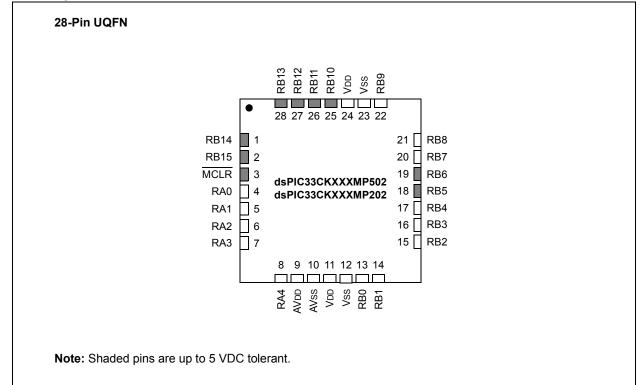

# **Pin Diagrams (Continued)**

## TABLE 4:28-PIN UQFN

| Pin # | Function                        | Pin # | Function                                                 |

|-------|---------------------------------|-------|----------------------------------------------------------|

| 1     | <b>RP46</b> /PWM1H/RB14         | 15    | OA2OUT/AN1/AN7/ANA0/CMP1D/CMP2D/CMP3D/RP34/SCL3/INT0/RB2 |

| 2     | RP47/PWM1L/RB15                 | 16    | PGD2/OA2IN-/AN8/ <b>RP35</b> /RB3                        |

| 3     | MCLR                            | 17    | PGC2/OA2IN+/ <b>RP36</b> /RB4                            |

| 4     | OA1OUT/AN0/CMP1A/IBIAS0/RA0     | 18    | PGD3/ <b>RP37</b> /SDA2/RB5                              |

| 5     | OA1IN-/ANA1/RA1                 | 19    | PGC3/ <b>RP38</b> /SCL2/RB6                              |

| 6     | OA1IN+/AN9/RA2                  | 20    | TDO/AN2/CMP3A/ <b>RP39</b> /SDA3/RB7                     |

| 7     | DACOUT1/AN3/CMP1C/RA3           | 21    | PGD1/AN10/ <b>RP40</b> /SCL1/RB8                         |

| 8     | AN4/CMP3B/IBIAS3/RA4            | 22    | PGC1/AN11/ <b>RP41</b> /SDA1/RB9                         |

| 9     | AVdd                            | 23    | Vss                                                      |

| 10    | AVss                            | 24    | VDD                                                      |

| 11    | Vdd                             | 25    | TMS/RP42/PWM3H/RB10                                      |

| 12    | Vss                             | 26    | TCK/ <b>RP43</b> /PWM3L/RB11                             |

| 13    | OSCI/CLKI/AN5/RP32/RB0          | 27    | TDI/ <b>RP44</b> /PWM2H/RB12                             |

| 14    | OSCO/CLKO/AN6/ <b>RP33</b> /RB1 | 28    | RP45/PWM2L/RB13                                          |

Note: RPn represents remappable peripheral functions.

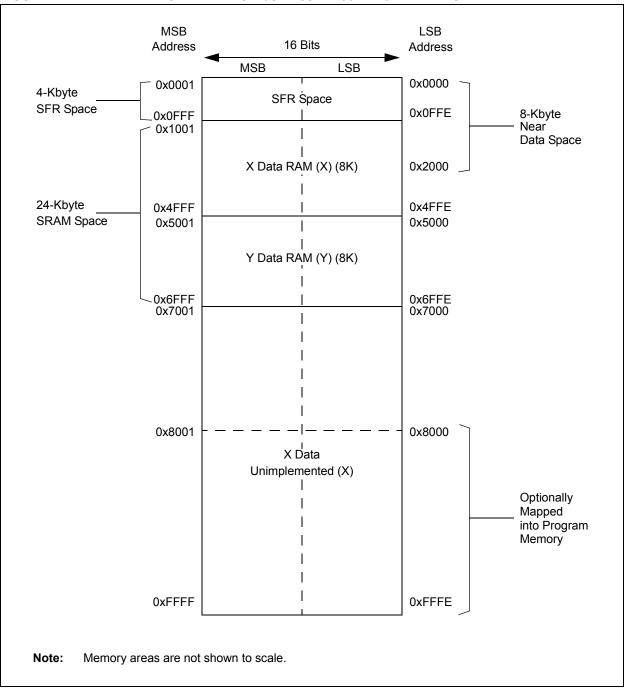

FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33CK256MPX0X DEVICES

#### 8.5.10 PERIPHERAL PIN SELECT REGISTERS

# **REGISTER 8-13:** RPCON: PERIPHERAL REMAPPING CONFIGURATION REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|--------|-----|-----|-------|

|        | —   | _   | _   | IOLOCK | —   | —   | —     |

| bit 15 |     |     |     |        |     |     | bit 8 |

|        |     |     |     |        |     |     |       |

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0 | U-0 | U-0   |

|        |     |     | -   | -      |     | _   | —     |

| bit 7  |     |     |     |        |     |     | bit 0 |

|        |     |     |     |        |     |     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-12 **Unimplemented:** Read as '0'

bit 11 IOLOCK: Peripheral Remapping Register Lock bit

$\ensuremath{\mathtt{1}}$  = All Peripheral Remapping registers are locked and cannot be written

$\ensuremath{\scriptscriptstyle 0}$  = All Peripheral Remapping registers are unlocked and can be written

bit 10-0 Unimplemented: Read as '0'

**Note 1:** Writing to this register needs an unlock sequence.

### REGISTER 8-14: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| INT1R7 | INT1R6 | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    |

| —      |        |        | —      | _      | —      | —      |        |

bit 0

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 **INT1R<7:0>:** Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 Unimplemented: Read as '0'

bit 7

Unimplemented: Read as '0'

Unimplemented: Read as '0'

(see Table 8-7 for peripheral function numbers)

(see Table 8-7 for peripheral function numbers)

| U-0             | U-0                                                                  | R/W-0  | R/W-0  | R/W-0            | R/W-0  | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------|--------|--------|------------------|--------|-----------------|--------|

| —               | —                                                                    | RP41R5 | RP41R4 | RP41R3           | RP41R2 | RP41R1          | RP41R0 |

| bit 15          |                                                                      |        |        |                  |        |                 | bit 8  |

|                 |                                                                      |        |        |                  |        |                 |        |

| U-0             | U-0                                                                  | R/W-0  | R/W-0  | R/W-0            | R/W-0  | R/W-0           | R/W-0  |

| —               | _                                                                    | RP40R5 | RP40R4 | RP40R3           | RP40R2 | RP40R1          | RP40R0 |

| bit 7           |                                                                      |        |        |                  |        |                 | bit 0  |

|                 |                                                                      |        |        |                  |        |                 |        |

| Legend:         |                                                                      |        |        |                  |        |                 |        |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |        |                  |        |                 |        |

| -n = Value at P | -n = Value at POR '1' = Bit is set                                   |        |        | '0' = Bit is cle | ared   | x = Bit is unkr | nown   |

RP41R<5:0>: Peripheral Output Function is Assigned to RP41 Output Pin bits

RP40R<5:0>: Peripheral Output Function is Assigned to RP40 Output Pin bits

**RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5**

#### REGISTER 8-58: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| -n = Value at F                   | POR | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |

|-----------------------------------|-----|------------------|--------|------------------------------------|--------|--------------------|--------|

| R = Readable bit W = Writable bit |     |                  | bit    | U = Unimplemented bit, read as '0' |        |                    |        |

| Legend:                           |     |                  |        |                                    |        |                    |        |

|                                   |     |                  |        |                                    |        |                    |        |

| bit 7                             |     |                  | I      |                                    |        | •                  | bit (  |

| _                                 |     | RP42R5           | RP42R4 | RP42R3                             | RP42R2 | RP42R1             | RP42R0 |

| U-0                               | U-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

|                                   |     |                  |        |                                    |        |                    |        |

| bit 15                            | •   |                  |        | ·                                  |        | •                  | bit    |

| —                                 | —   | RP43R5           | RP43R4 | RP43R3                             | RP43R2 | RP43R1             | RP43R0 |

| U-0                               | U-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP43R<5:0>:** Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 8-7 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP42R<5:0>:** Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 8-7 for peripheral function numbers)

bit 15-14

bit 13-8

bit 7-6

bit 5-0

**REGISTER 8-59:**

#### REGISTER 9-7: APLLFBD1: APLL FEEDBACK DIVIDER REGISTER

| U-0    | U-0 | U-0 | U-0 | r-0 | r-0 | r-0 | r-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R/W-1 | R/W-0          | R/W-0 | R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-0 |  |  |  |  |

|-------|----------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | APLLFBDIV<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 |                |       |       |       |       |       | bit 0 |  |  |  |  |

| Legend:           | r = Reserved bit |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-8 Reserved: Maintain as '0'

- bit 7-0 APLLFBDIV<7:0>: APLL Feedback Divider bits

- 11111111 = Reserved

- ... 11001000 **= 200** maximum<sup>(1)</sup>

... 10010110 = **150 (default)**

... 00010000 = 16 minimum<sup>(1)</sup>

- ... 00000010 = Reserved 00000001 = Reserved 00000000 = Reserved

- **Note 1:** The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power-on default feedback divider is 150 (decimal) with an 8 MHz FRC input clock; the VCO frequency is 1.2 GHz.

# 12.0 HIGH-RESOLUTION PWM WITH FINE EDGE PLACEMENT

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Resolution PWM with Fine Edge Placement" (DS70005320) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The High-Speed PWM (HSPWM) module is a Pulse-Width Modulated (PWM) module to support both motor control and power supply applications. This flexible module provides features to support many types of Motor Control (MC) and Power Control (PC) applications, including:

- AC-to-DC Converters

- DC-to-DC Converters

- AC and DC Motors: BLDC, PMSM, ACIM, SRM, etc.

- Inverters

- Battery Chargers

- Digital Lighting

- Power Factor Correction (PFC)

# 12.1 Features

- 8 Independent PWM Generators, each with Dual Outputs

- · Operating modes:

- Independent Edge mode

- Variable Phase PWM mode

- Center-Aligned mode

- Double Update Center-Aligned mode

- Dual Edge Center-Aligned mode

- Dual PWM mode

- · Output modes:

- Complementary

- Independent

- Push-Pull

- Dead-Time Generator

- Leading-Edge Blanking (LEB)

- · Output Override for Fault Handling

- Flexible Period/Duty Cycle Updating Options

- Programmable Control Inputs (PCI)

- Advanced Triggering Options

- 6 Combinatorial Logic Outputs

- · 6 PWM Event Outputs

### REGISTER 12-2: FSCL: FREQUENCY SCALE REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                   |       |                  | FSCI  | _<15:8>                                 |       |       |       |

| bit 15                            |       |                  |       |                                         |       |       | bit 8 |

|                                   |       |                  |       |                                         |       |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                   |       |                  | FSC   | L<7:0>                                  |       |       |       |

| bit 7                             |       |                  |       |                                         |       |       | bit 0 |

|                                   |       |                  |       |                                         |       |       |       |

| Legend:                           |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit |       |                  | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at POR '1' = Bit is s  |       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 **FSCL<15:0>:** Frequency Scale Register bits The value in this register is added to the frequency scaling accumulator at each pwm\_master\_clk. When the accumulated value exceeds the value of FSMINPER, a clock pulse is produced.

#### REGISTER 12-3: FSMINPER: FREQUENCY SCALING MINIMUM PERIOD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|--------|------------------------------------|-------|--------------------|-------|

|                                   |       |                  | FSMINP | ER<15:8>                           |       |                    |       |

| bit 15                            |       |                  |        |                                    |       |                    | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|                                   |       |                  | FSMINF | PER<7:0>                           |       |                    |       |

| bit 7                             |       |                  |        |                                    |       |                    | bit 0 |

| Legend:                           |       |                  |        |                                    |       |                    |       |

| R = Readable bit W = Writable bit |       |                  |        | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR '1'             |       | '1' = Bit is set |        | '0' = Bit is cleared               |       | x = Bit is unknown |       |

bit 15-0 **FSMINPER<15:0>:** Frequency Scaling Minimum Period Register bits This register holds the minimum clock period (maximum clock frequency) that can be produced by the frequency scaling circuit.

### **REGISTER 12-13: PGxCONH: PWM GENERATOR x CONTROL REGISTER HIGH (CONTINUED)**

- bit 6 **TRGMOD:** PWM Generator Trigger Mode Selection bit 1 = PWM Generator operates in Retriggerable mode

- 0 = PWM Generator operates in Single Trigger mode

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 SOCS<3:0>: Start-of-Cycle Selection bits<sup>(1,2,3)</sup>

- 1111 = TRIG bit or PCI Sync function only (no hardware trigger source is selected)

- 1110-0101 = Reserved

- 0100 = Trigger output selected by PG4 or PG8 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

- 0011 = Trigger output selected by PG3 or PG7 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

- 0010 = Trigger output selected by PG2 or PG6 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

- 0001 = Trigger output selected by PG1 or PG5 PGTRGSEL<2:0> bits (PGxEVTL<2:0>)

- 0000 = Local EOC PWM Generator is self-triggered

- **Note 1:** The PCI selected Sync signal is always available to be OR'd with the selected SOC signal per the SOCS<3:0> bits if the PCI Sync function is enabled.

- 2: The source selected by the SOCS<3:0> bits MUST operate from the same clock source as the local PWM Generator. If not, the source must be routed through the PCI Sync logic so the trigger signal may be synchronized to the PWM Generator clock domain.

- **3:** PWM Generators are grouped into groups of four: PG1-PG4 and PG5-PG8, if available. Any generator within a group of four may be used to trigger another generator within the same group.

| REGISTER 13-4: AD | CON2H: ADC CONTROL REGISTER 2 HIGH |

|-------------------|------------------------------------|

|-------------------|------------------------------------|

| R-0, HSC | R-0, HSC | U-0 | r-0 | r-0 | r-0 | R/W-0    | R/W-0    |

|----------|----------|-----|-----|-----|-----|----------|----------|

| REFRDY   | REFERR   | —   | —   | —   | —   | SHRSAMC9 | SHRSAMC8 |

| bit 15   |          |     |     |     |     |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SHRSAMC7 | SHRSAMC6 | SHRSAMC5 | SHRSAMC4 | SHRSAMC3 | SHRSAMC2 | SHRSAMC1 | SHRSAMC0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | r = Reserved bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | HSC = Hardware Settat  | ble/Clearable bit                  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15 **REFRDY:** Band Gap and Reference Voltage Ready Flag bit 1 = Band gap is ready 0 = Band gap is not ready bit 14 REFERR: Band Gap or Reference Voltage Error Flag bit 1 = Band gap was removed after the ADC module was enabled (ADON = 1) 0 = No band gap error was detected bit 13 Unimplemented: Read as '0' bit 12-10 Reserved: Maintain as '0' bit 9-0 SHRSAMC<9:0>: Shared ADC Core Sample Time Selection bits These bits specify the number of shared ADC Core Clock Periods (TADCORE) for the shared ADC core sample time. 1111111111 = 1025 TADCORE . . . 000000001 = 3 TADCORE 0000000000 = 2 TADCORE

NOTES:

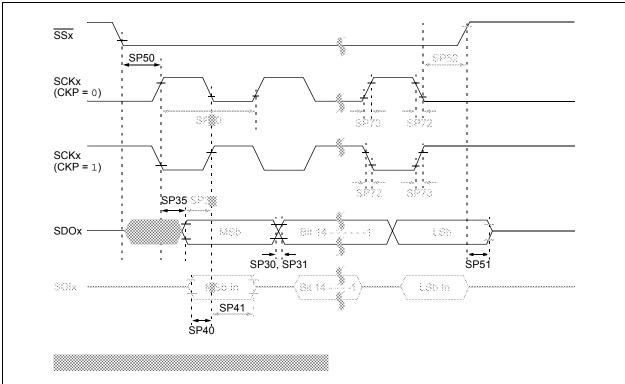

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

| Note 1: | This data sheet summarizes the features      |

|---------|----------------------------------------------|

|         | of the dsPIC33CK256MP508 family of           |

|         | devices. It is not intended to be a compre-  |

|         | hensive reference source. To complement      |

|         | the information in this data sheet, refer to |

|         | "Serial Peripheral Interface (SPI) with      |

|         | Audio Codec Support" (DS70005136) in         |

|         | the "dsPIC33/PIC24 Family Reference          |

|         | Manual", which is available from the         |

|         | Microchip web site (www.microchip.com).      |

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the dsPIC33CK256MP508 family include three SPI modules. On 48, 64 and 80-pin devices, SPI instance SPI2 can work up to 50 MHz speed when selected as a non-PPS pin. The selection is done using the SPI2PIN bit (FDEVOPT<13>). If the bit for SPI2PIN is '1', the PPS pin will be used. When SPI2PIN is '0', the SPI signals are routed to dedicated pins.

The module supports operation in two Buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

**Note:** FIFO depth for this device is 4 (in 8-Bit Data mode).

Variable length data can be transmitted and received, from 2 to 32 bits.

Note: Do not perform Read-Modify-Write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- Left Justified mode

- Right Justified mode

- PCM/DSP mode

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the Master and the other is the Slave. However, audio data can be transferred between two Slaves. Because the audio protocols require free-running clocks, the Master can be a third-party controller. In either case, the Master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC).

The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

|  | REGISTER 19-9: | PMAEN: PARALLEL MASTER PORT PIN ENABLE REGISTER |

|--|----------------|-------------------------------------------------|

|--|----------------|-------------------------------------------------|

| R/W-0        | R/W-0           | R/W-0                                | R/W-0           | R/W-0                              | R/W-0          | R/W-0                | R/W-0      |

|--------------|-----------------|--------------------------------------|-----------------|------------------------------------|----------------|----------------------|------------|

| PTE          | N<15:14>        |                                      |                 | PTEN                               | <13:8>         |                      |            |

| bit 15       |                 |                                      |                 |                                    |                |                      | bit 8      |

|              |                 |                                      |                 |                                    |                |                      |            |

| R/W-0        | R/W-0           | R/W-0                                | R/W-0           | R/W-0                              | R/W-0          | R/W-0                | R/W-0      |

|              |                 | PTEN                                 | <7:2>           |                                    |                | PTEN                 | <1:0>      |

| bit 7        |                 |                                      |                 |                                    |                |                      | bit 0      |

|              |                 |                                      |                 |                                    |                |                      |            |

| Legend:      |                 |                                      |                 |                                    |                |                      |            |

| R = Readab   | le bit          | W = Writable bit<br>'1' = Bit is set |                 | U = Unimplemented bit, read as '0' |                |                      |            |

| -n = Value a | t POR           |                                      |                 | '0' = Bit is cleared               |                | x = Bit is unknown   |            |

|              |                 |                                      |                 |                                    |                |                      |            |

| bit 15-14    |                 | I>: PMCSx Stro                       |                 | -                                  |                |                      |            |

|              |                 | and PMA14 fun                        |                 |                                    | or PMCS2 and   | PMCS1 <sup>(1)</sup> |            |

|              | 0 = PMA15       | and PMA14 fun                        | ction as port I | /Os                                |                |                      |            |

| bit 13-2     | PTEN<13:2>      | PMP Address                          | Port Enable     | bits                               |                |                      |            |

|              |                 | :2> function as                      |                 | lines                              |                |                      |            |

|              | 0 = PMA<13      | :2> function as                      | port I/Os       |                                    |                |                      |            |

| bit 1-0      | PTEN<1:0>:      | PMALH/PMAL                           | L Strobe Enat   | ole bits                           |                |                      |            |

|              |                 | nd PMA0 functi                       |                 |                                    | ALH and PMA    | LL <sup>(2)</sup>    |            |

|              | 0 = PMA1 a      | nd PMA0 pads                         | function as po  | ort I/Os                           |                |                      |            |

| Note 1: ⊤    | he use of these | pins as address                      | or Chip Sele    | ct lines is selec                  | ted by the CSF | <1:0> bits (PM       | CON<7:6>). |

2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

# 21.1 Timer1 Control Register

| R/W-0                       | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R-0                                                                                                                                                                        | R-0                  | R/W-0              | R/W-0       |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-------------|--|--|

| TON <sup>(1)</sup>          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TMWDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TMWIP                                                                                                                                                                      | PRWIP                | TECS1              | TECS0       |  |  |

| bit 15                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                                                                                                                                                          |                      | •                  | bit         |  |  |

| R/W-0                       | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                        | R/W-0                | R/W-0              | U-0         |  |  |

| TGATE                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TCKPS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TCKPS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                            | TSYNC <sup>(1)</sup> | TCS <sup>(1)</sup> |             |  |  |