Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck32mp206t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.4.2.3 Move and Accumulator Instructions

Move instructions, and the DSP accumulator class of instructions, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.4.2.4 MAC Instructions

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- · Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.4.2.5 Other Instructions

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ICM7R7  | ICM7R6  | ICM7R5  | ICM7R4  | ICM7R3  | ICM7R2  | ICM7R1  | ICM7R0  |

| bit 15  | -<br>-  |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/W-0   |

| TCKI7R7 | TCKI7R6 | TCKI7R5 | TCKI7R4 | TCKI7R3 | TCKI7R2 | TCKI7R1 | TCKI7R0 |

| bit 7   |         |         |         |         |         | •       | bit 0   |

|         |         |         |         |         |         |         |         |

| Lonondi |         |         |         |         |         |         |         |

## REGISTER 8-23: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 ICM7R<7:0>: Assign SCCP Capture 7 (ICM7) Input to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 **TCKI7R<7:0>:** Assign SCCP Timer7 (TCKI7) Input to the Corresponding RPn Pin bits See Table 8-4.

## REGISTER 8-24: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ICM8R7 | ICM8R6 | ICM8R5 | ICM8R4 | ICM8R3 | ICM8R2 | ICM8R1 | ICM8R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TCKI8R7 | TCKI8R6 | TCKI8R5 | TCKI8R4 | TCKI8R3 | TCKI8R2 | TCKI8R1 | TCKI8R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 ICM8R<7:0>: Assign SCCP Capture 8 (ICM8) Input to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 **TCKI8R<7:0>:** Assign SCCP Timer8 (TCKI8) Input to the Corresponding RPn Pin bits See Table 8-4.

Unimplemented: Read as '0'

| U-0                                | U-0 | R/W-0  | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|-----|--------|--------|-----------------------------------------|--------|--------|--------|

| —                                  | —   | RP33R5 | RP33R4 | RP33R3                                  | RP33R2 | RP33R1 | RP33R0 |

| bit 15                             |     |        |        |                                         |        |        | bit 8  |

|                                    |     |        |        |                                         |        |        |        |

| U-0                                | U-0 | R/W-0  | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |

| —                                  | —   | RP32R5 | RP32R4 | RP32R3                                  | RP32R2 | RP32R1 | RP32R0 |

| bit 7                              |     |        |        |                                         |        |        | bit 0  |

|                                    |     |        |        |                                         |        |        |        |

| Legend:                            |     |        |        |                                         |        |        |        |

| R = Readable bit W = Writable bit  |     |        | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at POR '1' = Bit is set |     |        |        | '0' = Bit is cleared x = Bit is unknown |        |        |        |

## REGISTER 8-54: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 13-8 | <b>RP33R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP33 Output Pin bits (see Table 8-7 for peripheral function numbers) |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                              |

| bit 5-0  | <b>RP32R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP32 Output Pin bits (see Table 8-7 for peripheral function numbers) |

## REGISTER 8-55: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                         | U-0                                                                                     | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------|------------------|--------|------------------------------------|--------|--------------------|--------|--|--|

| _                           | —                                                                                       | RP35R5           | RP35R4 | RP35R3                             | RP35R2 | RP35R1             | RP35R0 |  |  |

| bit 15                      | ÷                                                                                       |                  |        |                                    | ·      |                    | bit 8  |  |  |

|                             |                                                                                         |                  |        |                                    |        |                    |        |  |  |

| U-0                         | U-0                                                                                     | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |

|                             | —                                                                                       | RP34R5           | RP34R4 | RP34R3                             | RP34R2 | RP34R1             | RP34R0 |  |  |

| bit 7                       |                                                                                         |                  |        |                                    |        |                    | bit 0  |  |  |

|                             |                                                                                         |                  |        |                                    |        |                    |        |  |  |

| Legend:                     |                                                                                         |                  |        |                                    |        |                    |        |  |  |

| R = Readable                | e bit                                                                                   | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                    |        |  |  |

| -n = Value at POR '1' = Bit |                                                                                         | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |  |

|                             |                                                                                         |                  |        |                                    |        |                    |        |  |  |

| bit 15-14                   | Unimplemented: Read as '0'                                                              |                  |        |                                    |        |                    |        |  |  |

| bit 13-8                    | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits |                  |        |                                    |        |                    |        |  |  |

(see Table 8-7 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP34R<5:0>:** Peripheral Output Function is Assigned to RP34 Output Pin bits (see Table 8-7 for peripheral function numbers)

bit 15-14

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note 1: This data sheet summarizes the features of this group of dsPIC33 devices. It is not intended to be a comprehensive reference source. For more information, refer to "Direct Memory Access Controller (DMA)" (DS39742) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Direct Memory Access (DMA) Controller is designed to service high data throughput peripherals operating on the SFR bus, allowing them to access data memory directly and alleviating the need for CPU-intensive management. By allowing these data-intensive peripherals to share their own data path, the main data bus is also deloaded, resulting in additional power savings.

The DMA Controller functions both as a peripheral and a direct extension of the CPU. It is located on the microcontroller data bus, between the CPU and DMA-enabled peripherals, with direct access to SRAM. This partitions the SFR bus into two buses, allowing the DMA Controller access to the DMA-capable peripherals located on the new DMA SFR bus. The controller serves as a Master device on the DMA SFR bus, controlling data flow from DMA-capable peripherals. The controller also monitors CPU instruction processing directly, allowing it to be aware of when the CPU requires access to peripherals on the DMA bus and automatically relinquishing control to the CPU as needed. This increases the effective bandwidth for handling data without DMA operations, causing a processor Stall. This makes the controller essentially transparent to the user.

The DMA Controller has these features:

- Four Independently Programmable Channels

- Concurrent Operation with the CPU (no DMA caused Wait states)

- DMA Bus Arbitration

- Five Programmable Address modes

- Four Programmable Transfer modes

- Four Flexible Internal Data Transfer modes

- Byte or Word Support for Data Transfer

- 16-Bit Source and Destination Address Register for each Channel, Dynamically Updated and Reloadable

- 16-Bit Transaction Count Register, Dynamically Updated and Reloadable

- Upper and Lower Address Limit Registers

- Counter Half-Full Level Interrupt

- Software Triggered Transfer

- Null Write mode for Symmetric Buffer Operations

- A simplified block diagram of the DMA Controller is shown if Figure 10-1.

| HS/C-0               | HS/C-0                                                                                                                                                   | HS/C-0                                                                                            | HS/C-0                | R-0                  | R-0                  | U-0            | U-0   |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------------|----------------|-------|--|--|--|

| IVMIF <sup>(1)</sup> | WAKIF <sup>(1)</sup>                                                                                                                                     | CERRIF <sup>(1)</sup>                                                                             | SERRIF <sup>(1)</sup> | RXOVIF               | TXATIF               |                | _     |  |  |  |

| bit 15               | I                                                                                                                                                        |                                                                                                   | 1                     |                      |                      |                | bit 8 |  |  |  |

|                      |                                                                                                                                                          |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| U-0                  | U-0                                                                                                                                                      | U-0                                                                                               | R-0                   | HS/C-0               | HS/C-0               | R-0            | R-0   |  |  |  |

| _                    | —                                                                                                                                                        | _                                                                                                 | TEFIF                 | MODIF <sup>(1)</sup> | TBCIF <sup>(1)</sup> | RXIF           | TXIF  |  |  |  |

| bit 7                |                                                                                                                                                          |                                                                                                   |                       |                      |                      |                | bit   |  |  |  |

|                      |                                                                                                                                                          |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| Legend:              |                                                                                                                                                          | C = Clearable                                                                                     | bit                   | HS = Hardwa          | are Settable bit     |                |       |  |  |  |

| R = Readable         | bit                                                                                                                                                      | W = Writable b                                                                                    | oit                   | U = Unimple          | mented bit, rea      | d as '0'       |       |  |  |  |

| -n = Value at I      | POR                                                                                                                                                      | '1' = Bit is set                                                                                  |                       | '0' = Bit is cle     | eared                | x = Bit is unk | nown  |  |  |  |

|                      |                                                                                                                                                          |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| bit 15               |                                                                                                                                                          | d Message Inter                                                                                   |                       |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | essage interrup                                                                                   |                       |                      |                      |                |       |  |  |  |

| L:1 4 4              |                                                                                                                                                          | d message inter                                                                                   | -                     |                      |                      |                |       |  |  |  |

| bit 14               |                                                                                                                                                          | Wake-up Activit                                                                                   |                       | g bit <sup>(1)</sup> |                      |                |       |  |  |  |

|                      | <ol> <li>Wake-up activity interrupt occurred</li> <li>No wake-up activity interrupt occurred</li> </ol>                                                  |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| bit 13               |                                                                                                                                                          | N Bus Error Inte                                                                                  | •                     | 1)                   |                      |                |       |  |  |  |

|                      | 1 = CAN bus error interrupt occurred                                                                                                                     |                                                                                                   |                       |                      |                      |                |       |  |  |  |

|                      | 0 = No CAN                                                                                                                                               | bus error interru                                                                                 | pt occurred           |                      |                      |                |       |  |  |  |

| bit 12               | SERRIF: System Error Interrupt Flag bit <sup>(1)</sup>                                                                                                   |                                                                                                   |                       |                      |                      |                |       |  |  |  |

|                      | <ol> <li>System error interrupt occurred</li> <li>No system error interrupt occurred</li> </ol>                                                          |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| 1.11.44              | -                                                                                                                                                        | -                                                                                                 |                       |                      |                      |                |       |  |  |  |

| bit 11               |                                                                                                                                                          | XOVIF: Receive Buffer Overflow Interrupt Flag bit<br>= Receive buffer overflow interrupt occurred |                       |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | e buffer overflov                                                                                 |                       |                      |                      |                |       |  |  |  |

| bit 10               |                                                                                                                                                          |                                                                                                   | •                     |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | <b>TXATIF:</b> Transmit Attempt Interrupt Flag bit<br>1 = Transmit attempt interrupt occurred     |                       |                      |                      |                |       |  |  |  |

|                      | 0 = No transmit attempt Interrupt occurred                                                                                                               |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| bit 9-5              | Unimplemen                                                                                                                                               | ited: Read as '0                                                                                  | ,                     |                      |                      |                |       |  |  |  |

| bit 4                | TEFIF: Trans                                                                                                                                             | mit Event FIFO                                                                                    | Interrupt Flag        | bit                  |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | event FIFO inte                                                                                   | •                     |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | nit event FIFO i                                                                                  | -                     |                      |                      |                |       |  |  |  |

| bit 3                | MODIF: CAN Mode Change Interrupt Flag bit <sup>(1)</sup>                                                                                                 |                                                                                                   |                       |                      |                      |                |       |  |  |  |

|                      | <ul> <li>1 = CAN module mode change occurred (OPMOD&lt;2:0&gt; have changed to reflect REQOP&lt;2:0&gt;)</li> <li>0 = No mode change occurred</li> </ul> |                                                                                                   |                       |                      |                      |                |       |  |  |  |

| bit 2                | <b>TBCIF:</b> CAN Timer Overflow Interrupt Flag bit <sup>(1)</sup>                                                                                       |                                                                                                   |                       |                      |                      |                |       |  |  |  |

|                      | 1 = TBC has overflowed                                                                                                                                   |                                                                                                   |                       |                      |                      |                |       |  |  |  |

|                      | 0 = TBC has                                                                                                                                              | not overflowed                                                                                    |                       |                      |                      |                |       |  |  |  |

| bit 1                | RXIF: Receiv                                                                                                                                             | e Object Interru                                                                                  | pt Flag bit           |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | object interrupt i                                                                                |                       |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | e object interru                                                                                  | -                     | g                    |                      |                |       |  |  |  |

| bit 0                |                                                                                                                                                          | nit Object Interru                                                                                |                       |                      |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | object interrupt                                                                                  |                       | na                   |                      |                |       |  |  |  |

|                      |                                                                                                                                                          | nit object interru                                                                                |                       | ng                   |                      |                |       |  |  |  |

## REGISTER 11-16: C1INTL: CAN INTERRUPT REGISTER LOW

Note 1: C1INTL: Flags are set by hardware and cleared by application.

| U-0                  | U-0                                                                                                                                            | U-0                  | R-0                         | R-0                    | R-0                    | R-0                    | R-0                    |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|

| _                    | —                                                                                                                                              | _                    | FIFOCI4 <sup>(1)</sup>      | FIFOCI3 <sup>(1)</sup> | FIFOCI2 <sup>(1)</sup> | FIFOCI1 <sup>(1)</sup> | FIFOCI0 <sup>(1)</sup> |  |  |  |  |

| pit 15               |                                                                                                                                                |                      |                             |                        |                        |                        | bit                    |  |  |  |  |

|                      |                                                                                                                                                |                      | 0///0.0                     | 0///0.0                |                        |                        |                        |  |  |  |  |

| R-0                  | R-0                                                                                                                                            | R-0                  | C/HS-0                      | C/HS-0                 | R-0                    | R-0                    | R-0                    |  |  |  |  |

| TXABT <sup>(3)</sup> | TXLARB <sup>(2)</sup>                                                                                                                          | TXERR <sup>(2)</sup> | TXATIF                      | RXOVIF                 | TFERFFIF               | TFHRFHIF               | TFNRFNIF               |  |  |  |  |

| bit 7                |                                                                                                                                                |                      |                             |                        |                        |                        | bit                    |  |  |  |  |

| Legend:              |                                                                                                                                                | C = Clearable        | bit                         | HS = Hardwa            | are Settable bit       |                        |                        |  |  |  |  |

| R = Readable         | e bit                                                                                                                                          | W = Writable b       | bit                         | U = Unimpler           | mented bit, read       | d as '0'               |                        |  |  |  |  |

| n = Value at l       | POR                                                                                                                                            | '1' = Bit is set     |                             | '0' = Bit is cle       | ared                   | x = Bit is unkr        | nown                   |  |  |  |  |

|                      |                                                                                                                                                |                      |                             |                        |                        |                        |                        |  |  |  |  |

| bit 15-13            | Unimplemen                                                                                                                                     | ted: Read as '0      | )'                          |                        |                        |                        |                        |  |  |  |  |

| bit 12-8             | FIFOCI<4:0>                                                                                                                                    | : FIFO Messag        | e Index bits <sup>(1)</sup> |                        |                        |                        |                        |  |  |  |  |

|                      | <b>FIFOCI&lt;4:0&gt;:</b> FIFO Message Index bits <sup>(1)</sup><br>TXEN = 1 (FIFO configured as a transmit buffer):                           |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | A read of this register will return an index to the message that the FIFO will next attempt to transmit.                                       |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | TXEN = 0 (FIFO configured as a receive buffer):                                                                                                |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | A read of this register will return an index to the message that the FIFO will use to save the next message.                                   |                      |                             |                        |                        |                        |                        |  |  |  |  |

| bit 7                | TXABT: Message Aborted Status bit <sup>(3)</sup>                                                                                               |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | 1 = Message was aborted                                                                                                                        |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | 0 = Message completed successfully                                                                                                             |                      |                             |                        |                        |                        |                        |  |  |  |  |

| bit 6                | TXLARB: Message Lost Arbitration Status bit <sup>(2)</sup>                                                                                     |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | •                                                                                                                                              | lost arbitration     | •                           |                        |                        |                        |                        |  |  |  |  |

| bit 5                | <ul> <li>0 = Message did not lose arbitration while being sent</li> <li>TXERR: Error Detected During Transmission bit<sup>(2)</sup></li> </ul> |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | 1 = A bus error occurred while the message was being sent                                                                                      |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | 0 = A bus error did not occur while the message was being sent                                                                                 |                      |                             |                        |                        |                        |                        |  |  |  |  |

| bit 4                | <b>TXATIF:</b> Transmit Attempts Exhausted Interrupt Pending bit                                                                               |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | TXEN = 1 (FIFO configured as a transmit buffer):                                                                                               |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | 1 = Interrupt is pending                                                                                                                       |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | 0 = Interrupt is not pending                                                                                                                   |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | TXEN = 0 (FIFO configured as a receive buffer):<br>Unused, read as '0'.                                                                        |                      |                             |                        |                        |                        |                        |  |  |  |  |

| bit 3                | <b>RXOVIF:</b> Receive FIFO Overflow Interrupt Flag bit                                                                                        |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | TXEN = 1 (FIFO configured as a transmit buffer):                                                                                               |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      | Unused, read as '0'.<br>TXEN = 0 (FIFO configured as a receive buffer):                                                                        |                      |                             |                        |                        |                        |                        |  |  |  |  |

|                      |                                                                                                                                                | event has occu       |                             | <u></u>                |                        |                        |                        |  |  |  |  |

|                      |                                                                                                                                                | ow event has o       |                             |                        |                        |                        |                        |  |  |  |  |

| Note 1: FIF          | -OCI<4:0> give:                                                                                                                                | s a zero-indexe      | d value to the              | message in th          | e FIFO. If the F       | IFO is 4 messa         | ages deep              |  |  |  |  |

|                      | SIZE<4:0> = 3),                                                                                                                                |                      |                             |                        |                        |                        |                        |  |  |  |  |

| <b>2</b> ∙ Th        | aca hite ara unc                                                                                                                               | lated when a m       | assaga compl                | otos (or aborts        | ) or when the F        | IEO is resot           |                        |  |  |  |  |

- 2: These bits are updated when a message completes (or aborts) or when the FIFO is reset.

- **3:** This bit is reset on any read of this register or when the TXQ is reset. The bits are cleared when TXREQ is set or using an SPI write.

| R/W-      | 0 R/W-0                              | R/W-0                                    | R/W-0                      | U-0            | U-0                        | U-0             | U-0          |

|-----------|--------------------------------------|------------------------------------------|----------------------------|----------------|----------------------------|-----------------|--------------|

| EVTyC     | EN EVTyPO                            | L EVTySTRD                               | EVTySYNC                   | —              | _                          |                 | _            |

| bit 15    |                                      |                                          | •                          |                |                            |                 | bit 8        |

|           |                                      | <b></b>                                  | 5444.6                     |                |                            | <b>D</b> 444 A  |              |

| R/W-      |                                      | R/W-0                                    | R/W-0                      | U-0            | R/W-0                      | R/W-0           | R/W-0        |

| EVTyS     | EL3 EVTySEL                          | 2 EVTySEL1                               | EVTySEL0                   |                | EVTyPGS2 <sup>(2)</sup>    | EVTyPGS1(2)     | 2            |

| bit 7     |                                      |                                          |                            |                |                            |                 | bit C        |

| Legend:   |                                      |                                          |                            |                |                            |                 |              |

| R = Read  | lable bit                            | W = Writable                             | bit                        | U = Unimple    | emented bit, read          | d as '0'        |              |

| -n = Valu | e at POR                             | '1' = Bit is set                         |                            | '0' = Bit is c | leared                     | x = Bit is unkn | own          |

| bit 15    |                                      | DWM Event Out                            | nut Enchla hit             |                |                            |                 |              |

| JIL IS    | -                                    | : PWM Event Out<br>output signal is o    | -                          |                |                            |                 |              |

|           |                                      | output signal is in                      | •                          | сурп           |                            |                 |              |

| bit 14    | EVTyPOL                              | : PWM Event Out                          | put Polarity bit           |                |                            |                 |              |

|           |                                      | output signal is a                       |                            |                |                            |                 |              |

|           |                                      | output signal is a                       | •                          |                |                            |                 |              |

| bit 13    |                                      | D: PWM Event O                           |                            |                |                            |                 |              |

|           |                                      | output signal pul                        |                            |                | (1)                        |                 |              |

| L:4 4 0   |                                      | output signal is s                       |                            | VVIVI CIOCK Cy | cies minimum               |                 |              |

| bit 12    | -                                    | C: PWM Event O                           |                            | the eveter     | alaak                      |                 |              |

|           |                                      | output signal is s<br>output is not syne |                            |                |                            |                 |              |

|           |                                      | out signal pulse w                       |                            |                |                            | d EVTySTRD =    | 1.           |

| bit 11-8  | Unimplem                             | nented: Read as                          | 0'                         |                |                            |                 |              |

| bit 7-4   | <b>EVTySEL</b>                       | <3:0>: PWM Ever                          | nt Selection bit           | S              |                            |                 |              |

|           |                                      | gh-resolution erro                       | r event signal             |                |                            |                 |              |

|           |                                      | 0 = Reserved                             | _ 1                        |                |                            |                 |              |

|           |                                      | DC Trigger 2 signa                       |                            |                |                            |                 |              |

|           |                                      | FER signal (avai                         |                            | Pull Output m  | nodes only) <sup>(4)</sup> |                 |              |

|           | 0110 <b>= C</b> A                    | AHALF signal (av                         | ailable in Cente           |                |                            |                 |              |

|           |                                      | CI Fault active out                      |                            |                |                            |                 |              |

|           |                                      | CI Current-limit ac<br>CI Feed-forward a |                            |                |                            |                 |              |

|           |                                      | CI Sync active out                       |                            | griai          |                            |                 |              |

|           | 0001 = PV                            | NM Generator ou                          | tput signal <sup>(3)</sup> |                |                            |                 |              |

|           | 0000 <b>= Sc</b>                     | ource is selected I                      | by the PGTRG               | SEL<2:0> bi    | ts                         |                 |              |

| bit 3     | Unimplem                             | nented: Read as '                        | 0'                         |                |                            |                 |              |

| Note 1:   | The event signa<br>from different cl | al is stretched usin<br>lock sources.    | ng peripheral_o            | clk because o  | different PWM G            | enerators may   | be operating |

| 2:        |                                      | e produced if the s                      |                            |                | -                          |                 |              |

| 3:        | This is the PWN                      | A Generator output                       | ut signal prior t          | o output mod   | le logic and any           | output override | logic.       |

|           | The second second second             |                                          |                            |                |                            | • • • •         |              |

## REGISTER 12-10: PWMEVTy: PWM EVENT OUTPUT CONTROL REGISTER y<sup>(5)</sup>

- 4: This signal should be the PGx\_clk domain signal prior to any synchronization into the system clock domain.

- 5: 'y' denotes a common instance (A-F).

## REGISTER 12-25: PGxDCA: PWM GENERATOR x DUTY CYCLE ADJUSTMENT REGISTER

| U-0         | U-0   | U-0             | U-0   | U-0          | U-0              | U-0      | U-0   |

|-------------|-------|-----------------|-------|--------------|------------------|----------|-------|

|             | _     | —               | _     | —            | _                |          |       |

| bit 15      |       |                 |       |              |                  |          | bit 8 |

|             |       |                 |       |              |                  |          |       |

| R/W-0       | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|             |       |                 | PGxD  | )CA<7:0>     |                  |          |       |

| bit 7       |       |                 |       |              |                  |          | bit 0 |

|             |       |                 |       |              |                  |          |       |

| Legend:     |       |                 |       |              |                  |          |       |

| R = Readabl | e bit | W = Writable bi | t     | U = Unimpler | mented bit, read | l as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **PGxDCA<7:0>:** PWM Generator x Duty Cycle Adjustment Value bits Depending on the state of the selected PCI source, the PGxDCA value will be added to the value in the PGxDC register to create the effective duty cycle. When the PCI source is active, PGxDCA is added.

## REGISTER 12-26: PGxPER: PWM GENERATOR x PERIOD REGISTER

| R/W-0         | R/W-0   | R/W-0            | R/W-0 | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |

|---------------|---------|------------------|-------|-------------------------|------------------|-----------------|-------|

|               |         |                  | PGxPE | ER<15:8> <sup>(1)</sup> |                  |                 |       |

| bit 15        |         |                  |       |                         |                  |                 | bit 8 |

| R/W-0         | R/W-0   | R/W-0            | R/W-0 | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |

| 1.1.1.1       | FV/VV-U | F\/VV-0          | -     | ER<7:0> <sup>(1)</sup>  | N/ VV-U          | N/W-0           | N/W-0 |

|               |         |                  | I GAI |                         |                  |                 |       |

| bit 7         |         |                  |       |                         |                  |                 | bit 0 |

|               |         |                  |       |                         |                  |                 |       |

| Legend:       |         |                  |       |                         |                  |                 |       |

| R = Readable  | e bit   | W = Writable b   | it    | U = Unimplem            | nented bit, read | d as '0'        |       |

| -n = Value at | POR     | '1' = Bit is set |       | '0' = Bit is clea       | ared             | x = Bit is unkn | own   |

bit 15-0 **PGxPER<15:0>:** PWM Generator x Period Register bits<sup>(1)</sup>

Note 1: Period values less than '0x0010' should not be used ('0x0080' in High-Resolution mode).

# 13.0 HIGH-SPEED, 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "12-Bit High-Speed, Multiple SARs A/D Converter (ADC)" (DS70005213) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33CK256MP508 devices have a high-speed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters. The devices implement the ADC with three SAR cores, two dedicated and one shared.

# 13.1 ADC Features Overview

The High-Speed, 12-Bit Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- Three ADC Cores: Two Dedicated Cores and One Shared (common) Core

- User-Configurable Resolution of up to 12 Bits for each Core

- Up to 3.5 Msps Conversion Rate per Channel at 12-Bit Resolution

- Low-Latency Conversion

- Up to 24 Analog Input Channels, with a Separate 16-Bit Conversion Result Register for each Input

- Conversion Result can be Formatted as Unsigned or Signed Data, on a per Channel Basis, for All Channels

- Simultaneous Sampling of up to 3 Analog Inputs

- Channel Scan Capability

- Multiple Conversion Trigger Options for each Core, including:

- PWM triggers from CPU cores

- MCCP/SCCP modules triggers

- CLC modules triggers

- External pin trigger event (ADTRG31)

- Software trigger

- Four Integrated Digital Comparators with Dedicated Interrupts:

- Multiple comparison options

- Assignable to specific analog inputs

- Four Oversampling Filters with Dedicated Interrupts:

- Provide increased resolution

- Assignable to a specific analog input

The module consists of three independent SAR ADC cores. Simplified block diagrams of the Multiple SARs 12-Bit ADC are shown in Figure 13-1 and Figure 13-2.

The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S&H) circuit of each ADC core. The core uses the channel information (the output format, the Measurement mode and the input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input, and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

The ADC module can sample up to three inputs at a time (two inputs from the dedicated SAR cores and one from the shared SAR core). If multiple ADC inputs request conversion on the shared core, the module will convert them in a sequential manner, starting with the lowest order input.

The ADC provides each analog input the ability to specify its own trigger source. This capability allows the ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

# dsPIC33CK256MP508 FAMILY

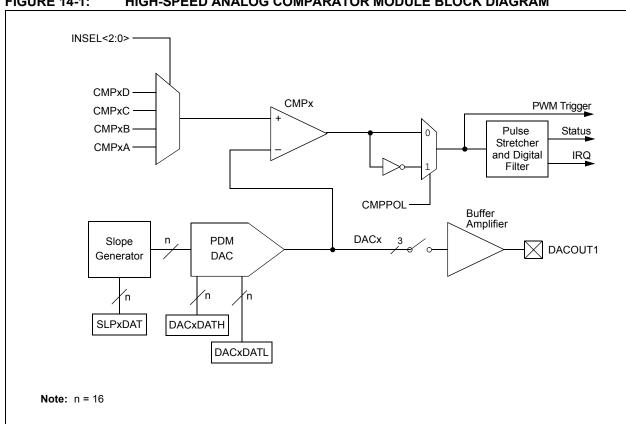

## FIGURE 14-1: HIGH-SPEED ANALOG COMPARATOR MODULE BLOCK DIAGRAM

## REGISTER 15-11: INTxTMRL: INTERVAL x TIMER REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | INTTN | /IR<15:8>         |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | MR<7:0>           |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

|                 |       |                  |       |                   |                |                 |       |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | ented bit, rea | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared           | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INTxTMR) bits

## REGISTER 15-12: INTxTMRH: INTERVAL x TIMER REGISTER HIGH

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<31:24>         |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | IR<23:16>         |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | iown  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INTxTMR) bits

## REGISTER 19-12: PMRADDR: PARALLEL MASTER PORT READ ADDRESS REGISTER<sup>(2)</sup>

| -                      | <b>-</b>                                      | 54446                                       |                             | 5444.0                             | -                    |               | <b>-</b>           |  |  |

|------------------------|-----------------------------------------------|---------------------------------------------|-----------------------------|------------------------------------|----------------------|---------------|--------------------|--|--|

| R/W-0                  | R/W-0                                         | R/W-0                                       | R/W-0                       | R/W-0                              | R/W-0                | R/W-0         | R/W-0              |  |  |

| RCS2 <sup>(1)</sup>    | RCS1 <sup>(1)</sup>                           | 4                                           |                             | RADD                               | R<13:8>              |               |                    |  |  |

| RADDR15 <sup>(1)</sup> | RADDR14 <sup>(1)</sup>                        |                                             |                             | 10.66                              | 10.0                 |               |                    |  |  |

| bit 15                 |                                               |                                             |                             |                                    |                      |               | bit 8              |  |  |

|                        | <b>D</b> 444 A                                | <b>D</b> 444 0                              | DAM A                       | <b>D</b> 444 0                     | <b>D</b> 444 0       | 5444.0        | <b>D</b> 444 0     |  |  |

| R/W-0                  | R/W-0                                         | R/W-0                                       | R/W-0                       | R/W-0                              | R/W-0                | R/W-0         | R/W-0              |  |  |

|                        |                                               |                                             | RADD                        | )R<7:0>                            |                      |               |                    |  |  |

| bit 7                  |                                               |                                             |                             |                                    |                      |               | bit 0              |  |  |

|                        |                                               |                                             |                             |                                    |                      |               |                    |  |  |

| Legend:                |                                               |                                             |                             |                                    |                      |               |                    |  |  |

| R = Readable           | e bit                                         | W = Writable                                | bit                         | U = Unimplemented bit, read as '0' |                      |               |                    |  |  |

| -n = Value at          | POR                                           | '1' = Bit is set                            | '1' = Bit is set            |                                    | '0' = Bit is cleared |               | x = Bit is unknown |  |  |

|                        |                                               |                                             |                             |                                    |                      |               |                    |  |  |

| bit 15                 | RCS2: Chip S                                  | Select 2 bit <sup>(1)</sup>                 |                             |                                    |                      |               |                    |  |  |

|                        | 1 = Chip Sel                                  | ect 2 is active                             |                             |                                    |                      |               |                    |  |  |

|                        | 0 = Chip Sel                                  | ect 2 is inactive                           | e (RADDR15                  | function is sele                   | cted)                |               |                    |  |  |

| bit 15                 | RADDR15: T                                    | arget Read Add                              | dress bit 15 <sup>(1)</sup> |                                    |                      |               |                    |  |  |

| bit 14                 | RCS1: Chip S                                  | Select 1 bit <sup>(1)</sup>                 |                             |                                    |                      |               |                    |  |  |

|                        | 1 = Chip Sel                                  | ect 1 is active                             |                             |                                    |                      |               |                    |  |  |

|                        | 0 = Chip Sel                                  | ect 1 is inactive                           | e (RADDR14 1                | function is sele                   | cted)                |               |                    |  |  |

| bit 14                 | RADDR14: T                                    | arget Read Add                              | dress bit 14 <sup>(1)</sup> | )                                  |                      |               |                    |  |  |

| bit 13-0               | RADDR<13:0                                    | 0>: Target Read                             | d Address bits              | 6                                  |                      |               |                    |  |  |

| Note 1: Th             | RADDR<13:0<br>e use of these p<br>MCON<7:6>). | <b>0&gt;:</b> Target Read<br>bins as PMA15/ |                             |                                    | elected by the       | CSF<1:0> bits |                    |  |  |

2: This register is only used when the DUALBUF bit (PMCONH<1>) is set to '1'.

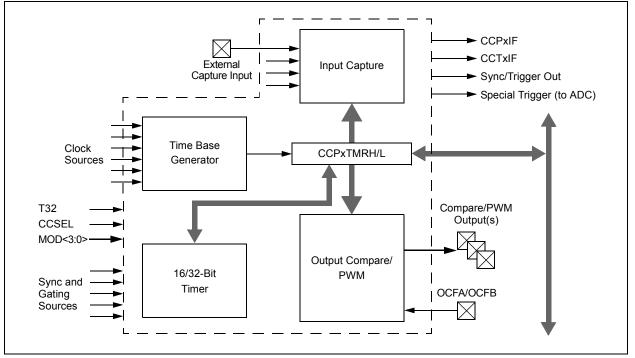

# 22.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (SCCP/MCCP)

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. For more information on the MCCP/SCCP modules, refer to "Capture/Compare/ PWM/Timer (MCCP and SCCP)" (DS33035) in the "dsPIC33/PIC24 Family Reference Manual".

dsPIC33CK256MP508 family devices include 8 SCCP and 1 MCCP Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals from earlier PIC24F devices. The module can operate in one of three major modes:

- General Purpose Timer

- · Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM (SCCP) output modules provide only one PWM output.

Multiple Capture/Compare/PWM (MCCP) output modules can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical. The SCCPx and MCCPx modules can be operated in only one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode.

A conceptual block diagram for the module is shown in Figure 22-1. All three modes share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of six control and status registers:

- CCPxCON1L (Register 22-1)

- CCPxCON1H (Register 22-2)

- CCPxCON2L (Register 22-3)

- CCPxCON2H (Register 22-4)

- CCPxCON3H (Register 22-6)

- CCPxSTATL (Register 22-7)

Each module also includes eight buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (CCPx Timer High/Low Counters)

- CCPxPRH/CCPxPRL (CCPx Timer Period High/Low)

- CCPxRA (CCPx Primary Output Compare Data Buffer)

- CCPxRB (CCPx Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (CCPx Input Capture High/Low Buffers)

#### FIGURE 22-1: SCCPx CONCEPTUAL BLOCK DIAGRAM

## REGISTER 23-1: CLCxCONL: CLCx CONTROL REGISTER (LOW) (CONTINUED)

- bit 2-0 MODE<2:0>: CLCx Mode bits

- 111 = Single input transparent latch with S and R

- 110 = JK flip-flop with R

- 101 = Two-input D flip-flop with R

- 100 = Single input D flip-flop with S and R

- 011 = SR latch

- 010 = Four-input AND

- 001 = Four-input OR-XOR

- 000 = Four-input AND-OR

#### REGISTER 23-2: CLCxCONH: CLCx CONTROL REGISTER (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | G4POL | G3POL | G2POL | G1POL |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### Legend:

| Legena.           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | G4POL: Gate 4 Polarity Control bit                                                                                                            |

|          | <ul> <li>1 = Channel 4 logic output is inverted when applied to the logic cell</li> <li>0 = Channel 4 logic output is not inverted</li> </ul> |

| bit 2    | G3POL: Gate 3 Polarity Control bit                                                                                                            |

|          | <ul> <li>1 = Channel 3 logic output is inverted when applied to the logic cell</li> <li>0 = Channel 3 logic output is not inverted</li> </ul> |

| bit 1    | G2POL: Gate 2 Polarity Control bit                                                                                                            |

|          | <ul> <li>1 = Channel 2 logic output is inverted when applied to the logic cell</li> <li>0 = Channel 2 logic output is not inverted</li> </ul> |

| bit 0    | G1POL: Gate 1 Polarity Control bit                                                                                                            |

|          | <ul> <li>1 = Channel 1 logic output is inverted when applied to the logic cell</li> <li>0 = Channel 1 logic output is not inverted</li> </ul> |

# 25.1 Control Registers

## REGISTER 25-1: CRCCONL: CRC CONTROL REGISTER LOW