Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

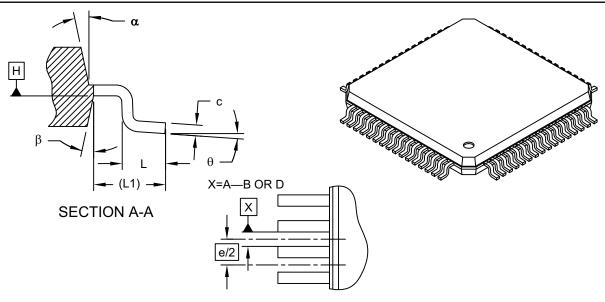

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck32mp506t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4 ICSP Pins

The PGCx and PGDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGCx and PGDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to PICkit<sup>™</sup> 3, MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup> emulator.

For more information on MPLAB ICD 2, MPLAB ICD 3 and REAL ICE emulator connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) (DS51765)

- "Development Tools Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator" (poster) (DS51749)

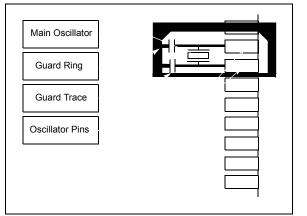

#### 2.5 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator (POSC) and a low-frequency Secondary Oscillator (SOSC). For details, see Section 9.2 "Primary Oscillator (POSC)".

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### : SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| TADLE 4-1 | 15. 51  |                                         |          |         |                                         |             |         |                                         |

|-----------|---------|-----------------------------------------|----------|---------|-----------------------------------------|-------------|---------|-----------------------------------------|

| Register  | Address | All Resets                              | Register | Address | All Resets                              | Register    | Address | All Resets                              |

| I/O Ports |         |                                         | CNEN0B   | E2C     | 000000000000000000000000000000000000000 | CNPUD       | E5E     | 000000000000000000                      |

| ANSELA    | E00     | 11111                                   | CNSTATB  | E2E     | 0000000000000000000                     | CNPDD       | E60     | 000000000000000000                      |

| TRISA     | E02     | 11111                                   | CNEN1B   | E30     | 000000000000000000000000000000000000000 | CNCOND      | E62     | 0                                       |

| PORTA     | E04     | xxxxx                                   | CNFB     | E32     | 00000000000000000                       | CNEN0D      | E64     | 000000000000000000                      |

| LATA      | E06     | xxxxx                                   | ANSELC   | E38     | 111111                                  | CNSTATD     | E66     | 000000000000000000                      |

| ODCA      | E08     | 00000                                   | TRISC    | E3A     | 11111111111111111                       | CNEN1D      | E68     | 000000000000000000                      |

| CNPUA     | E0A     | 00000                                   | PORTC    | E3C     | *****                                   | CNFD        | E6A     | 000000000000000000                      |

| CNPDA     | E0C     | 00000                                   | LATC     | E3E     | *****                                   | ANSELE      | E70     | 1111                                    |

| CNCONA    | E0E     | 0                                       | ODCC     | E40     | 00000000000000000                       | TRISE       | E72     | 11111111111111111                       |

| CNEN0A    | E10     | 00000                                   | CNPUC    | E42     | 000000000000000000000000000000000000000 | PORTE       | E74     | *****                                   |

| CNSTATA   | E12     | 00000                                   | CNPDC    | E44     | 00000000000000000                       | LATE        | E76     | *****                                   |

| CNEN1A    | E14     | 00000                                   | CNCONC   | E46     | 0                                       | ODCE        | E78     | 000000000000000000000000000000000000000 |

| CNFA      | E16     | 00000                                   | CNEN0C   | E48     | 00000000000000000                       | CNPUE       | E7A     | 000000000000000000000000000000000000000 |

| ANSELB    | E1C     | 11111111                                | CNSTATC  | E4A     | 00000000000000000                       | CNPDE       | E7C     | 000000000000000000000000000000000000000 |

| TRISB     | E1E     | 111111111111111111                      | CNEN1C   | E4C     | 00000000000000000                       | CNCONE      | E7E     | 0                                       |

| PORTB     | E20     | *****                                   | CNFC     | E4E     | 00000000000000000                       | CNEN0E      | E80     | 000000000000000000000000000000000000000 |

| LATB      | E22     | *****                                   | ANSELD   | E54     | 1-11                                    | CNSTATE     | E82     | 000000000000000000000000000000000000000 |

| ODCB      | E24     | 000000000000000000000000000000000000000 | TRISD    | E56     | 11111111111111111                       | CNEN1E      | E84     | 000000000000000000000000000000000000000 |

| CNPUB     | E26     | 000000000000000000000000000000000000000 | PORTD    | E58     | *****                                   | CNFE        | E86     | 000000000000000000000000000000000000000 |

| CNPDB     | E28     | 000000000000000000000000000000000000000 | LATD     | E5A     | *****                                   | Memory BIST |         |                                         |

| CNCONB    | E2A     | 0                                       | ODCD     | E5C     | 0000000000000000000                     | MBISTCON    | EFC     | 1                                       |

#### TABLE 4-15: SFR BLOCK E00h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

#### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page contains the latest updates and additional information.

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 7.4 Interrupt Control and Status Registers

The dsPIC33CK256MP508 family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.0.1 INTCON1 through INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior, contains the Global Interrupt Enable bit (GIE) and the Alternate Interrupt Vector Table Enable bit (AIVTEN).

INTCON3 contains the status flags for the Auxiliary PLL and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap Status bit (SGHT).

#### 7.4.0.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.0.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.0.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of seven priority levels.

#### 7.4.0.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and Interrupt Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP<2:0> bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.0.6 Status/Control Registers

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "dsPIC33E Enhanced CPU" (DS70005158) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

#### REGISTER 8-6: CNPUX: CHANGE NOTIFICATION PULL-UP ENABLE FOR PORTX REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | CNPL  | Jx<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | CNP   | Jx<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 CNPUx<15:0>: Change Notification Pull-up Enable for PORTx bits

1 = The pull-up for PORTx[n] is enabled – takes precedence over the pull-down selection

0 = The pull-up for PORTx[n] is disabled

#### REGISTER 8-7: CNPDx: CHANGE NOTIFICATION PULL-DOWN ENABLE FOR PORTx REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | CNPDx | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

|        |       |       |       |        |       |       |       |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | CNPD  | x<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 CNPDx<15:0>: Change Notification Pull-Down Enable for PORTx bits

1 = The pull-down for PORTx[n] is enabled (if the pull-up for PORTx[n] is not enabled)

0 = The pull-down for PORTx[n] is disabled

#### REGISTER 8-12: CNFx: INTERRUPT CHANGE NOTIFICATION FLAG FOR PORTx REGISTER

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|-------|--------|-------|-------|-------|

|         |       |       | CNFx  | <15:8> |       |       |       |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | CNFx  | <7:0>  |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| Ecgenia.          |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15- CNFx<15:0>: Interrupt Change Notification Flag for PORTx bits

When CNSTYLE (CNCONx<11>) = 1:

1 = An enabled edge event occurred on the PORTx[n] pin

0 = An enabled edge event did not occur on the PORTx[n] pin

#### REGISTER 9-8: APLLDIV1: APLL OUTPUT DIVIDER REGISTER

|                 |                             |                  | -              |                             |                 |                 |              |

|-----------------|-----------------------------|------------------|----------------|-----------------------------|-----------------|-----------------|--------------|

| U-0             | U-0                         | U-0              | U-0            | U-0                         | U-0             | R/W-0           | R/W-0        |

| _               | _                           | —                |                | _                           | _               | AVCOD           | IV<1:0>      |

| bit 15          |                             |                  |                |                             |                 |                 | bit 8        |

|                 |                             |                  |                |                             |                 |                 |              |

| U-0             | R/W-1                       | R/W-0            | R/W-0          | U-0                         | R/W-0           | R/W-0           | R/W-1        |

| —               | APC                         | )ST1DIV<2:0>(*   | 1,2)           |                             | APC             | OST2DIV<2:0>    | (1,2)        |

| bit 7           |                             |                  |                |                             |                 |                 | bit C        |

|                 |                             |                  |                |                             |                 |                 |              |

| Legend:         |                             |                  |                |                             |                 |                 |              |

| R = Readable    | bit                         | W = Writable b   | oit            | U = Unimpler                | mented bit, rea | d as '0'        |              |

| -n = Value at P | OR                          | '1' = Bit is set |                | '0' = Bit is cle            | ared            | x = Bit is unki | nown         |

|                 |                             |                  |                |                             |                 |                 |              |

| bit 15-10       | Unimplement                 | ed: Read as '0'  |                |                             |                 |                 |              |

| bit 9-8         | AVCODIV<1:0                 | >: APLL VCO C    | Output Divider | Select bits                 |                 |                 |              |

|                 | 11 <b>= AF</b> vco          |                  |                |                             |                 |                 |              |

|                 | 10 = AFvco/2                |                  |                |                             |                 |                 |              |

|                 | 01 = AFvco/3 $00 = AFvco/4$ |                  |                |                             |                 |                 |              |

| bit 7           | Unimplement                 | ed: Read as '0'  |                |                             |                 |                 |              |

| bit 6-4         | •                           | 2:0>: APLL Out   | out Divider #1 | Ratio hits(1,2)             |                 |                 |              |

|                 |                             | 2:0> can have a  |                |                             |                 | value should be | oreater than |

|                 |                             | APOST2DIVx v     |                | · ·                         |                 |                 | 0            |

|                 |                             | APOST2DIVx d     | ,              |                             | 0               | ·               | 0            |

| bit 3           | Unimplement                 | ed: Read as '0'  |                |                             |                 |                 |              |

| bit 2-0         | APOST2DIV<                  | 2:0>: APLL Out   | out Divider #2 | Ratio bits <sup>(1,2)</sup> |                 |                 |              |

APOST2DIV<2:0> can have a valid value, from 1 to 7 (the APOST2DIVx value should be less than or equal to the APOST1DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

- Note 1: The APOST1DIVx and APOST2DIVx values must not be changed while the PLL is operating.

- 2: The default values for APOST1DIVx and APOST2DIVx are 4 and 1, respectively, yielding a 150 MHz system source clock.

#### REGISTER 11-51: C1FLTCONxL: CAN FILTER CONTROL REGISTER x LOW (x = 0 TO 3; a = 0, 4, 8, 12; b = 1, 5, 9, 13)

|               | a = 0                                                            | , 4, 8, 12; D =                                      | 1, 5, 9, 13)     |             |                  |       |       |

|---------------|------------------------------------------------------------------|------------------------------------------------------|------------------|-------------|------------------|-------|-------|

| R/W-0         | U-0                                                              | U-0                                                  | R/W-0            | R/W-0       | R/W-0            | R/W-0 | R/W-0 |

| FLTENb        | _                                                                | —                                                    | FbBP4            | FbBP3       | FbBP2            | FbBP1 | FbBP0 |

| bit 15        |                                                                  |                                                      |                  |             |                  | ·     | bit 8 |

|               |                                                                  |                                                      |                  |             |                  |       |       |

| R/W-0         | U-0                                                              | U-0                                                  | R/W-0            | R/W-0       | R/W-0            | R/W-0 | R/W-0 |

| FLTENa        |                                                                  | —                                                    | FaBP4            | FaBP3       | FaBP2            | FaBP1 | FaBP0 |

| bit 7         |                                                                  |                                                      |                  |             |                  |       | bit 0 |

|               |                                                                  |                                                      |                  |             |                  |       |       |

| Legend:       |                                                                  |                                                      |                  |             |                  |       |       |

| R = Readabl   |                                                                  | W = Writable                                         |                  | -           | nented bit, read |       |       |

| -n = Value at | Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |                                                      |                  |             |                  |       |       |

| bit 15        | FLTENb: Ena<br>1 = Filter is e<br>0 = Filter is d                |                                                      | Accept Messag    | ges bit     |                  |       |       |

| bit 14-13     | Unimplemer                                                       | nted: Read as '                                      | 0'               |             |                  |       |       |

| bit 12-8      | FbBP<4:0>:                                                       | Pointer to Obje                                      | ct When Filter   | b Hits bits |                  |       |       |

|               | 00111 <b>= Me</b> s                                              | 000 = Reserved<br>ssage matching<br>ssage matching   | filter is stored |             |                  |       |       |

|               | 00001 <b>= Me</b> s                                              | ssage matching<br>ssage matching<br>served; Object ( | filter is stored | in Object 1 | ceive message    | 25    |       |

| bit 7         |                                                                  | able Filter a to A                                   |                  |             |                  |       |       |

|               | 1 = Filter is e<br>0 = Filter is d                               | enabled                                              |                  |             |                  |       |       |

| bit 6-5       | Unimplemer                                                       | nted: Read as '                                      | 0'               |             |                  |       |       |

| bit 4-0       | FaBP<4:0>:                                                       | Pointer to Obje                                      | ct When Filter   | a Hits bits |                  |       |       |

|               |                                                                  | 000 <b>= Reserve</b>                                 |                  |             |                  |       |       |

|               | 00110 <b>= Me</b> s                                              | ssage matching<br>ssage matching                     |                  |             |                  |       |       |

|               | 00001 <b>= Me</b> s                                              | ssage matching<br>ssage matching<br>served; Object ( | filter is stored | in Object 1 | ceive message    | es    |       |

|               |                                                                  |                                                      |                  |             |                  |       |       |

# 14.0 HIGH-SPEED ANALOG COMPARATOR WITH SLOPE COMPENSATION DAC

Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed Analog Comparator Module" (DS70005280) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The high-speed analog comparator module provides a method to monitor voltage, current and other critical signals in a power conversion application that may be too fast for the CPU and ADC to capture. There are a total of 3 comparator modules. The analog comparator module can be used to implement Peak Current mode control, Critical Conduction mode (variable frequency) and Hysteretic Control mode.

## 14.1 Overview

The high-speed analog comparator module is comprised of a high-speed comparator, Pulse Density Modulation (PDM) DAC and a slope compensation unit. The slope compensation unit provides a user-defined slope which can be used to alter the DAC output. This feature is useful in applications, such as Peak Current mode control, where slope compensation is required to maintain the stability of the power supply. The user simply specifies the direction and rate of change for the slope compensation and the output of the DAC is modified accordingly. The DAC consists of a PDM unit, followed by a digitally controlled multiphase RC filter. The PDM unit uses a phase accumulator circuit to generate an output stream of pulses. The density of the pulse stream is proportional to the input data value, relative to the maximum value supported by the bit width of the accumulator. The output pulse density is representative of the desired output voltage. The pulse stream is filtered with an RC filter to yield an analog voltage. The output of the DAC is connected to the negative input of the comparator. The positive input of the comparator can be selected using a MUX from either of the input pins. The comparator provides a high-speed operation with a typical delay of 15 ns.

The output of the comparator is processed by the pulse stretcher and the digital filter blocks, which prevent comparator response to unintended fast transients in the inputs. Figure 14-1 shows a block diagram of the high-speed analog comparator module. The DAC module can be operated in one of three modes: Slope Generation mode, Hysteretic mode and Triangle Wave mode. Each of these modes can be used in a variety of power supply applications.

Note: The DACOUT1 pin can only be associated with a single DAC output at any given time. If more than one DACOEN bit is set, the DACOUT1 pin will be a combination of the signals. To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- 5. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

| R/W-0               | R/W-0                      | R/W-0                                | R/W-0                       | R/W-0                  | R/W-0                 | R/W-0             | R/W-0                  |

|---------------------|----------------------------|--------------------------------------|-----------------------------|------------------------|-----------------------|-------------------|------------------------|

| AUDEN <sup>(1</sup> | I) SPISGNEXT               | IGNROV                               | IGNTUR                      | AUDMONO <sup>(2)</sup> | URDTEN <sup>(3)</sup> | AUDMOD1(4)        | AUDMOD0 <sup>(4)</sup> |

| bit 15              |                            |                                      |                             |                        |                       |                   | bit 8                  |

|                     |                            |                                      |                             |                        |                       |                   |                        |

| R/W-0               | R/W-0                      | R/W-0                                | R/W-0                       | R/W-0                  | R/W-0                 | R/W-0             | R/W-0                  |

| FRMEN               | FRMSYNC                    | FRMPOL                               | MSSEN                       | FRMSYPW                | FRMCNT2               | FRMCNT1           | FRMCNT0                |

| bit 7               | ·                          | •                                    |                             |                        |                       |                   | bit C                  |

|                     |                            |                                      |                             |                        |                       |                   |                        |

| Legend:             |                            |                                      |                             |                        |                       |                   |                        |

| R = Reada           | able bit                   | W = Writable I                       | oit                         | U = Unimpleme          | ented bit, read       | l as '0'          |                        |

| -n = Value          | at POR                     | '1' = Bit is set                     |                             | '0' = Bit is clear     | red                   | x = Bit is unkr   | nown                   |

|                     |                            |                                      |                             |                        |                       |                   |                        |

| bit 15              | AUDEN: Audi                | io Codec Suppo                       | ort Enable bit <sup>(</sup> | 1)                     |                       |                   |                        |

|                     |                            |                                      |                             | ntrols the directio    |                       | •                 |                        |

|                     |                            |                                      |                             | , FRMSYNC = M          | STEN, FRMC            | NT<2:0> = 001     | and SMP = 0            |

|                     |                            | s of their actua<br>tocol is disable |                             |                        |                       |                   |                        |

| bit 14              | •                          |                                      |                             | Read Data Enabl        | le hit                |                   |                        |

|                     |                            | RX FIFO is sig                       |                             |                        |                       |                   |                        |

|                     |                            | RX FIFO is no                        |                             | ed                     |                       |                   |                        |

| bit 13              | IGNROV: Igno               | ore Receive Ov                       | erflow bit                  |                        |                       |                   |                        |

|                     | 1 = A Receiv               | e Overflow (RC                       | V) is NOT a                 | critical error; duri   | ng ROV, data          | in the FIFO is r  | not overwritter        |

|                     |                            | ceive data                           |                             |                        |                       |                   |                        |

|                     |                            | a critical error                     | •                           | I operation            |                       |                   |                        |

| bit 12              | -                          | ore Transmit Ur                      |                             |                        |                       |                   | ·                      |

|                     |                            | SPIxTXB is not                       |                             | critical error and     |                       | a by URDIEN       | is transmitted         |

|                     |                            | a critical error                     |                             | l operation            |                       |                   |                        |

| bit 11              |                            | Audio Data For                       | -                           | -                      |                       |                   |                        |

|                     | 1 = Audio data             | a is mono (i.e.,                     | each data wo                | rd is transmitted      | on both left ar       | nd right channel  | s)                     |

|                     | 0 = Audio data             |                                      |                             |                        |                       |                   |                        |

| bit 10              |                            | Insmit Underru                       |                             |                        |                       |                   |                        |

|                     |                            |                                      | 0                           | ter during Transr      |                       |                   |                        |

| 1.1.0.0             |                            |                                      |                             | g Transmit Under       | run conditions        | •                 |                        |

| bit 9-8             |                            | 0>: Audio Proto                      | ocol Mode Sel               | ection bits            |                       |                   |                        |

|                     | 11 = PCM/DS                |                                      | nis module fu               | nctions as if SPIF     | E = 1 recard          | less of its actua | l value                |

|                     |                            |                                      |                             | ctions as if SPIFE     |                       |                   |                        |

|                     | 00 = I <sup>2</sup> S mode | e: This module                       | functions as i              | f SPIFE = 0, rega      | ardless of its a      | ctual value       |                        |

| bit 7               | FRMEN: Fran                | ned SPIx Supp                        | ort bit                     |                        |                       |                   |                        |

|                     |                            | Plx support is e<br>Plx support is e |                             | pin is used as the     | e FSYNC inpu          | ıt/output)        |                        |

| Note 1:             | AUDEN can only             | be written whe                       | n the SPIEN                 | bit = 0.               |                       |                   |                        |

|                     | AUDMONO can                |                                      |                             |                        | only valid for        | AUDEN = 1.        |                        |

|                     | URDTEN is only             |                                      |                             |                        |                       |                   |                        |

| 4:                  | AUDMOD<1:0> o              |                                      |                             | SPIEN bit = 0 ar       |                       |                   | = 1. When              |

#### REGISTER 17-2: SPIxCON1H: SPIx CONTROL REGISTER 1 HIGH

AUDMOD<1:0> can only be written when the SPIEN bit = 0 and is only valid when AUDEN = 1. Whe NOT in PCM/DSP mode, this module functions as if FRMSYPW = 1, regardless of its actual value.

# 18.4 Control Registers

#### REGISTER 18-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

| I2CEN<br>pit 15 | U-0           | R/W-0, HC                           | R/W-1                           | R/W-0                       | R/W-0              | R/W-0            | R/W-0        |

|-----------------|---------------|-------------------------------------|---------------------------------|-----------------------------|--------------------|------------------|--------------|

| oit 15          |               | I2CSIDL                             | SCLREL <sup>(1)</sup>           | STRICT                      | A10M               | DISSLW           | SMEN         |

|                 |               |                                     |                                 | •                           |                    |                  | bit          |

| R/W-0           | R/W-0         | R/W-0                               | R/W-0, HC                       | R/W-0, HC                   | R/W-0, HC          | R/W-0, HC        | R/W-0, HC    |

| GCEN            | STREN         | ACKDT                               | ACKEN                           | RCEN                        | PEN                | RSEN             | SEN          |

| Dit 7           | STILLIN       | AGRUT                               | AGNEN                           | NOLN                        |                    | NOLIN            | bit          |

|                 |               |                                     |                                 |                             |                    |                  |              |

| Legend:         |               | HC = Hardware                       | e Clearable bit                 |                             |                    |                  |              |

| R = Readable    | bit           | W = Writable b                      | bit                             | U = Unimplem                | nented bit, read   | l as '0'         |              |

| n = Value at l  | POR           | '1' = Bit is set                    |                                 | '0' = Bit is clea           | ared               | x = Bit is unkr  | iown         |

| oit 15          | 12CEN: 12Cx   | Enable bit (writa                   | able from softwa                | are only)                   |                    |                  |              |

|                 | 1 = Enables t | the I2Cx module                     | , and configure                 | s the SDAx and              |                    | serial port pins | 5            |

| oit 14          | Unimplemen    | ted: Read as '0                     | ,                               |                             |                    |                  |              |

| oit 13          | I2CSIDL: I2C  | x Stop in Idle M                    | ode bit                         |                             |                    |                  |              |

|                 |               | ues module ope<br>s module operat   |                                 |                             | e mode             |                  |              |

| oit 12          | SCLREL: SC    | Lx Release Cor                      | ntrol bit (I <sup>2</sup> C Sla | ive mode only) <sup>(</sup> | 1)                 |                  |              |

|                 |               | the SCLx clock                      |                                 |                             |                    |                  |              |

|                 | If STREN = 1  |                                     |                                 |                             |                    |                  |              |

|                 |               | e may write '0' to                  | initiate a clock                | stretch and wri             | ite '1' to release | e the clock. Har | dware clea   |

|                 |               | ing of every Sla<br>reception. Hard |                                 |                             |                    |                  | every Slav   |

|                 | If STREN = 0  |                                     |                                 |                             |                    |                  |              |

|                 |               | e may only write<br>smission. Hard  |                                 |                             |                    |                  |              |

| oit 11          | -             | K Strict Reserve                    |                                 | -                           |                    |                  |              |

|                 | (In Slave     | erved addressir<br>Mode) – The de   | evice doesn't re                |                             |                    |                  | sses falling |

|                 |               | gory are NACKe<br>er Mode) – The    |                                 | ed to generate :            | addresses with     | reserved addr    | ess snace    |

|                 |               | d addressing wo                     |                                 |                             |                    |                  | coo opace.   |

|                 |               | Mode) – The c                       |                                 |                             |                    |                  |              |

|                 |               | ere is a match w<br>er Mode) – Rese |                                 | eserved addres              | ses, the device    | e will generate  | an ACK.      |

|                 |               | Slave Address                       |                                 |                             |                    |                  |              |

| oit 10          |               | is a 10-bit Slav                    | U U                             |                             |                    |                  |              |

| pit 10          |               |                                     |                                 |                             |                    |                  |              |

| oit 10          | 0 = 120  xADD | is a 7-bit Slave                    | address                         |                             |                    |                  |              |

| oit 10<br>oit 9 | DISSLW: Sle   | w Rate Control                      | Disable bit                     |                             |                    |                  |              |

|                 | DISSLW: Sle   |                                     | Disable bit<br>led for Standar  |                             | •                  | disabled for 1   | MHz mode)    |

2: Automatically cleared to '0' at the beginning of Slave transmission.

| REGISTER 10-2. IZCZCONII. IZCZ CONTROL REGISTER HIGH | REGISTER 18-2: | I2CxCONH: I2Cx CONTROL REGISTER HIGH |

|------------------------------------------------------|----------------|--------------------------------------|

|------------------------------------------------------|----------------|--------------------------------------|

| REGISTEF     | R 18-2: I2Cx                                                                                                                                                               | CONH: I2Cx (       | CONTROL R                     | EGISTER HIC       | θH               |                  |                |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|-------------------|------------------|------------------|----------------|--|--|--|

| U-0          | U-0                                                                                                                                                                        | U-0                | U-0                           | U-0               | U-0              | U-0              | U-0            |  |  |  |

|              |                                                                                                                                                                            |                    |                               |                   |                  |                  | —              |  |  |  |

| bit 15       |                                                                                                                                                                            |                    |                               |                   |                  |                  | bit 8          |  |  |  |

| U-0          | R/W-0                                                                                                                                                                      | R/W-0              | R/W-0                         | R/W-0             | R/W-0            | R/W-0            | R/W-0          |  |  |  |

| _            | PCIE                                                                                                                                                                       | SCIE               | BOEN                          | SDAHT             | SBCDE            | AHEN             | DHEN           |  |  |  |

| bit 7        |                                                                                                                                                                            |                    |                               |                   |                  |                  | bit            |  |  |  |

| Legend:      |                                                                                                                                                                            |                    |                               |                   |                  |                  |                |  |  |  |

| R = Readal   | ble bit                                                                                                                                                                    | W = Writable       | bit                           | U = Unimplen      | nented bit, read | d as '0'         |                |  |  |  |

| -n = Value a | at POR                                                                                                                                                                     | '1' = Bit is set   |                               | '0' = Bit is clea | ared             | x = Bit is unkr  | Bit is unknown |  |  |  |

|              |                                                                                                                                                                            |                    |                               |                   |                  |                  |                |  |  |  |

| bit 15-7     | -                                                                                                                                                                          | nted: Read as '    |                               |                   |                  |                  |                |  |  |  |

| bit 6        | •                                                                                                                                                                          | Condition Interru  |                               |                   | e only).         |                  |                |  |  |  |

|              |                                                                                                                                                                            | interrupt on deter |                               | condition         |                  |                  |                |  |  |  |

| L:1 C        | <ul> <li>0 = Stop detection interrupts are disabled</li> <li>SCIE: Start Condition Interrupt Enable bit (I<sup>2</sup>C Slave mode only)</li> </ul>                        |                    |                               |                   |                  |                  |                |  |  |  |

| bit 5        |                                                                                                                                                                            |                    | •                             |                   | • ·              |                  |                |  |  |  |

|              | <ol> <li>Enables interrupt on detection of Start or Restart conditions</li> <li>Start detection interrupts are disabled</li> </ol>                                         |                    |                               |                   |                  |                  |                |  |  |  |

| bit 4        | <b>BOEN:</b> Buffer Overwrite Enable bit ( $I^2$ C Slave mode only)                                                                                                        |                    |                               |                   |                  |                  |                |  |  |  |

|              |                                                                                                                                                                            |                    |                               | • /               |                  | s/data bvte, ion | oring the stat |  |  |  |

|              | <ul> <li>1 = I2CxRCV is updated and an ACK is generated for a received address/data byte, ignoring the state<br/>of the I2COV bit only if RBF bit = 0</li> </ul>           |                    |                               |                   |                  |                  |                |  |  |  |

|              |                                                                                                                                                                            | √ is only update   |                               | / is clear        |                  |                  |                |  |  |  |

| bit 3        | SDAHT: SDAx Hold Time Selection bit                                                                                                                                        |                    |                               |                   |                  |                  |                |  |  |  |

|              | <ul> <li>1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx</li> <li>0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx</li> </ul> |                    |                               |                   |                  |                  |                |  |  |  |

|              |                                                                                                                                                                            |                    |                               | -                 | -                |                  |                |  |  |  |

| bit 2        |                                                                                                                                                                            | ve Mode Bus C      |                               | •                 |                  | • /              |                |  |  |  |

|              | If, on the rising edge of SCLx, SDAx is sampled low when the module is outputting a high state, the                                                                        |                    |                               |                   |                  |                  |                |  |  |  |

|              | BCL bit is set and the bus goes Idle. This Detection mode is only valid during data and ACK transmit                                                                       |                    |                               |                   |                  |                  |                |  |  |  |

|              | sequences.<br>1 = Enables Slave bus collision interrupts                                                                                                                   |                    |                               |                   |                  |                  |                |  |  |  |

|              | 0 = Slave bus collision interrupts are disabled                                                                                                                            |                    |                               |                   |                  |                  |                |  |  |  |

| bit 1        | AHEN: Addr                                                                                                                                                                 | ess Hold Enable    | e bit (l <sup>2</sup> C Slave | e mode only)      |                  |                  |                |  |  |  |

|              | 1 = Followin                                                                                                                                                               | g the 8th fallin   | g edge of So                  | CLx for a mate    | ching received   | address byte     | ; SCLREL b     |  |  |  |

|              |                                                                                                                                                                            | NL<12>) will be    |                               | the SCLx will be  | e held low       |                  |                |  |  |  |

|              |                                                                                                                                                                            | holding is disat   |                               |                   |                  |                  |                |  |  |  |

| bit 0        |                                                                                                                                                                            | Hold Enable bit    | •                             | • /               | :                |                  |                |  |  |  |

|              |                                                                                                                                                                            | g the 8th falling  |                               |                   | ata byte; Slave  | hardware clear   | s the SCLRE    |  |  |  |

|              | bit (I2CxCONL<12>) and SCLx is held low<br>0 = Data holding is disabled                                                                                                    |                    |                               |                   |                  |                  |                |  |  |  |

0 = Data holding is disabled

# REGISTER 19-11: PMWADDR: PARALLEL MASTER PORT WRITE ADDRESS REGISTER<sup>(2)</sup>

| R/W-0<br>WCS1 <sup>(1)</sup><br>VADDR14 <sup>(1)</sup><br>R/W-0 | R/W-0<br>R/W-0                                                                                                                                         | R/W-0<br>R/W-0<br>WADE                                                                                                                                                                                                                                                                                                                                                | R/W-0<br>WADD<br>R/W-0<br>DR<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0<br>R<13:8><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0<br>bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VADDR14 <sup>(1)</sup>                                          | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                 | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| R/W-0                                                           | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| R/W-0                                                           | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DAALO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |