Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 39                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 19x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-TQFP                                                                          |

| Supplier Device Package    | 48-TQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck64mp205t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

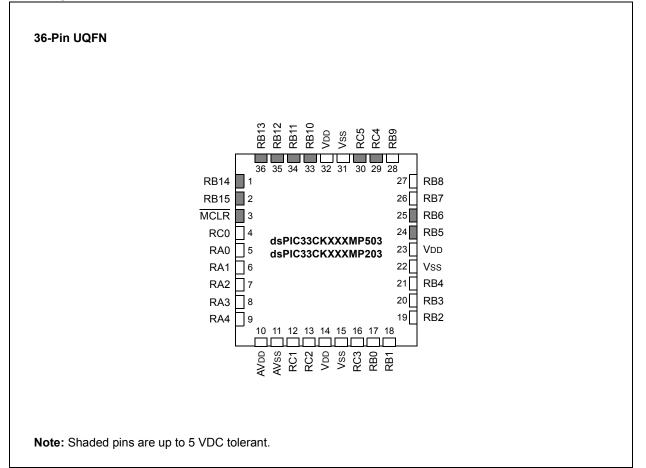

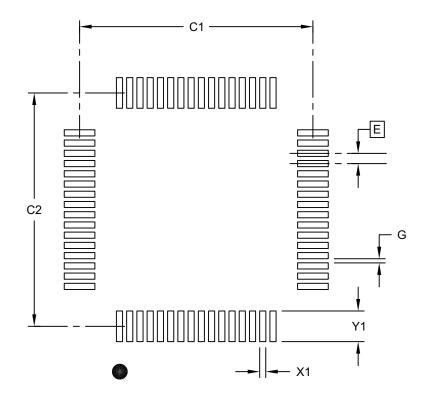

#### **Pin Diagrams (Continued)**

#### TABLE 5: 36-PIN UQFN

| Pin # | Function                         | Pin # | Function                                                 |

|-------|----------------------------------|-------|----------------------------------------------------------|

| 1     | <b>RP46</b> /PWM1H/RB14          | 19    | OA2OUT/AN1/AN7/ANA0/CMP1D/CMP2D/CMP3D/RP34/SCL3/INT0/RB2 |

| 2     | <b>RP47</b> /PWM1L/RB15          | 20    | PGD2/OA2IN-/AN8/ <b>RP35</b> /RB3                        |

| 3     | MCLR                             | 21    | PGC2/OA2IN+/ <b>RP36</b> /RB4                            |

| 4     | AN12/ANN0/ <b>RP48</b> /RC0      | 22    | Vss                                                      |

| 5     | OA1OUT/AN0/CMP1A/IBIAS0/RA0      | 23    | VDD                                                      |

| 6     | OA1IN-/ANA1/RA1                  | 24    | PGD3/ <b>RP37</b> /PWM6L/SDA2/RB5                        |

| 7     | OA1IN+/AN9/RA2                   | 25    | PGC3/RP38/PWM6H/SCL2/RB6                                 |

| 8     | DACOUT1/AN3/CMP1C/RA3            | 26    | TDO/AN2/CMP3A/ <b>RP39</b> /SDA3/RB7                     |

| 9     | OA3OUT/AN4/CMP3B/IBIAS3/RA4      | 27    | PGD1/AN10/ <b>RP40</b> /SCL1/RB8                         |

| 10    | AVdd                             | 28    | PGC1/AN11/ <b>RP41</b> /SDA1/RB9                         |

| 11    | AVss                             | 29    | RP52/PWM5H/ASDA2/RC4                                     |

| 12    | OA3IN-/AN13/CMP1B/ISRC0/RP49/RC1 | 30    | RP53/PWM5L/ASCL2/RC5                                     |

| 13    | OA3IN+/AN14/CMP2B/ISRC1/RP50/RC2 | 31    | Vss                                                      |

| 14    | VDD                              | 32    | VDD                                                      |

| 15    | Vss                              | 33    | TMS/ <b>RP42</b> /PWM3H/RB10                             |

| 16    | AN15/CMP2A/IBIAS2/RP51/RC3       | 34    | TCK/ <b>RP43</b> /PWM3L/RB11                             |

| 17    | OSCI/CLKI/AN5/RP32/RB0           | 35    | TDI/ <b>RP44</b> /PWM2H/RB12                             |

| 18    | OSCO/CLKO/AN6/RP33/RB1           | 36    | RP45/PWM2L/RB13                                          |

Note: RPn represents remappable peripheral functions.

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

#### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      | •                    |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

|                      |                      |                      |       |       |       |       |       |

|                      |                      | a a:                 |       |       |       |       |       |

| Legend:           | C = Clearable bit |                                    |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)

**Note 1:** For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

**3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0                                | U-0 | U-0          | U-0                                     | U-0          | U-0              | U-0                    | U-0   |  |

|------------------------------------|-----|--------------|-----------------------------------------|--------------|------------------|------------------------|-------|--|

|                                    | 00  | <u> </u>     | 50                                      |              | 50               |                        | 50    |  |

|                                    |     | —            |                                         |              | —                | —                      |       |  |

| bit 15                             |     |              |                                         |              |                  |                        | bit   |  |

|                                    |     |              |                                         |              |                  |                        |       |  |

| U-0                                | U-0 | U-0          | U-0                                     | U-0          | U-0              | R/W-0                  | R/W-0 |  |

| _                                  | _   | —            | _                                       | —            | —                | ECCDBE                 | SGHT  |  |

| bit 7                              |     |              |                                         |              |                  |                        | bit   |  |

|                                    |     |              |                                         |              |                  |                        |       |  |

| Legend:                            |     |              |                                         |              |                  |                        |       |  |

| R = Readable b                     | it  | W = Writable | bit                                     | U = Unimpler | mented bit, read | ented bit, read as '0' |       |  |

| -n = Value at POR '1' = Bit is set |     |              | '0' = Bit is cleared x = Bit is unknown |              |                  |                        |       |  |

bit 15-2 Unimplemented: Read as '0'

1 = ECC double-bit error trap has occurred

0 = ECC double-bit error trap has not occurred

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

#### 8.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Enable for PORTx register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs, other than VDD, by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

#### 8.2 Configuring Analog and Digital Port Pins

The ANSELx registers control the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx registers have a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 8.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 8.3 PORT Control Registers

The following registers are in the PORT module:

- Register 8-1: ANSELx (one per port)

- Register 8-2: TRISx (one per port)

- Register 8-3: PORTx (one per port)

- Register 8-4: LATx (one per port)

- Register 8-5: ODCx (one per port)

- Register 8-6: CNPUx (one per port)

- Register 8-7: CNPDx (one per port)

- Register 8-8: CNCONx (one per port optional)

- Register 8-9: CNEN0x (one per port)

- Register 8-10: CNSTATx (one per port optional)

- Register 8-11: CNEN1x (one per port)

- Register 8-12: CNFx (one per port)

#### **REGISTER 8-1:** ANSELX: ANALOG SELECT FOR PORTX REGISTER

| R/W-1                             | R/W-1 | R/W-1            | R/W-1 | R/W-1                              | R/W-1 | R/W-1              | R/W-1 |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                                   |       |                  | ANSEI | _x<15:8>                           |       |                    |       |  |

| bit 15                            |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-1                             | R/W-1 | R/W-1            | R/W-1 | R/W-1                              | R/W-1 | R/W-1              | R/W-1 |  |

|                                   |       |                  | ANSE  | Lx<7:0>                            |       |                    |       |  |

| bit 7                             |       |                  |       |                                    |       |                    | bit 0 |  |

| Legend:                           |       |                  |       |                                    |       |                    |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

bit 15-0

ANSELx<15:0>: Analog Select for PORTx bits

1 = Analog input is enabled and digital input is disabled on the PORTx[n] pin

0 = Analog input is disabled and digital input is enabled on the PORTx[n] pin

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ICM1R7 | ICM1R6 | ICM1R5 | ICM1R4 | ICM1R3 | ICM1R2 | ICM1R1 | ICM1R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

#### REGISTER 8-17: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| R/W-0       | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |  |  |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| TCKI1R7     | TCKI1R6 | TCKI1R5 | TCKI1R4 | TCKI1R3 | TCKI1R2 | TCKI1R1 | TCKI1R0 |  |  |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15-8 ICM1R<7:0>: Assign SCCP Capture 1 (ICM1) Input to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 **TCKI1<7:0>:** Assign SCCP Timer1 (TCKI1) Input to the Corresponding RPn Pin bits See Table 8-4.

#### REGISTER 8-18: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ICM2R7 | ICM2R6 | ICM2R5 | ICM2R4 | ICM2R3 | ICM2R2 | ICM2R1 | ICM2R0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TCKI2R7 | TCKI2R6 | TCKI2R5 | TCKI2R4 | TCKI2R3 | TCKI2R2 | TCKI2R1 | TCKI2R0 |

| bit 7   | •       |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 ICM2R<7:0>: Assign SCCP Capture 2 (ICM2) Input to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 **TCKI2R<7:0>:** Assign SCCP Timer2 (TCKI2) Input to the Corresponding RPn Pin bits See Table 8-4.

#### REGISTER 8-29: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 |

| bit 15    |           |           |           |           |           |           | bit 8     |

| R/W-0     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| bit 7     | •         |           |           |           |           |           | bit 0     |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **QEIHOM1R<7:0>:** Assign QEI Home 1 Input (QEIHOM1) to the Corresponding RPn Pin bits See Table 8-4.

#### REGISTER 8-30: RPINR16: PERIPHERAL PIN SELECT INPUT REGISTER 16

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| QEIB2R7 | QEIB2R6 | QEIB2R5 | QEIB2R4 | QEIB2R3 | QEIB2R2 | QEIB2R1 | QEIB2R0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| QEIA2R7 | QEIA2R6 | QEIA2R5 | QEIA2R4 | QEIA2R3 | QEIA2R2 | QEIA2R1 | QEIA2R0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8

QEIB2R<7:0>: Assign QEI2 Input B (QEIB2) to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0

QEIA2R<7:0>: Assign QEI2 Input A (QEIA2) to the Corresponding RPn Pin bits See Table 8-4.

bit 7-0 **QEINDX1R<7:0>:** Assign QEI Index 1 Input (QEINDX1) to the Corresponding RPn Pin bits See Table 8-4.

#### REGISTER 11-34: C1FIFOSTAX: CAN FIFO STATUS REGISTER x (x = 1 TO 7) (CONTINUED)

| bit 2   | TFERFFIF: Transmit/Receive FIFO Empty/Full Interrupt Flag bit                                  |

|---------|------------------------------------------------------------------------------------------------|

|         | TXEN = 1 (FIFO configured as a transmit FIFO):                                                 |

|         | Transmit FIFO Empty Interrupt Flag                                                             |

|         | 1 = FIFO is empty                                                                              |

|         | 0 = FIFO is not empty, at least 1 message is queued to be transmitted                          |

|         | TXEN = 0 (FIFO configured as a receive FIFO):                                                  |

|         | Receive FIFO Full Interrupt Flag                                                               |

|         | 1 = FIFO is full                                                                               |

|         | 0 = FIFO is not full                                                                           |

| bit 1   | TFHRFHIF: Transmit/Receive FIFO Half Empty/Half Full Interrupt Flag bit                        |

|         | TXEN = 1 (FIFO configured as a transmit FIFO):                                                 |

|         | Transmit FIFO Half Empty Interrupt Flag                                                        |

|         | 1 = FIFO is ≤ half full                                                                        |

|         | 0 = FIFO is > half full                                                                        |

|         | TXEN = 0 (FIFO configured as a receive FIFO):                                                  |

|         | Receive FIFO Half Full Interrupt Flag<br>1 = FIFO is > half full                               |

|         | 0 = FIFO is < half full                                                                        |

| bit 0   |                                                                                                |

|         | <b>TFNRFNIF:</b> Transmit/Receive FIFO Not Full/Not Empty Interrupt Flag bit                   |

|         | <u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Not Full Interrupt Flag |

|         | 1 = FIFO is not full                                                                           |

|         | 0 = FIFO is full                                                                               |

|         | TXEN = 0 (FIFO configured as a receive FIFO):                                                  |

|         | Receive FIFO Not Empty Interrupt Flag                                                          |

|         | 1 = FIFO is not empty, has at least 1 message                                                  |

|         | 0 = FIFO is empty                                                                              |

| Noto 1: | EIEOCICION gives a zero indexed value to the message in the EIEO. If the EIEO is 4 messages    |

- Note 1: FIFOCI<4:0> gives a zero-indexed value to the message in the FIFO. If the FIFO is 4 messages deep (FSIZE<4:0> = 3), FIFOCIx will take on a value of 0 to 3, depending on the state of the FIFO.

- 2: These bits are updated when a message completes (or aborts) or when the FIFO is reset.

- **3:** This bit is reset on any read of this register or when the TXQ is reset. The bits are cleared when TXREQ is set or using an SPI write.

#### REGISTER 12-2: FSCL: FREQUENCY SCALE REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0          | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|------------------|------------------------------------|----------------|-------|-------|--|

|                                    |       |       | FSCI             | _<15:8>                            |                |       |       |  |

| bit 15                             |       |       |                  |                                    |                |       | bit 8 |  |

|                                    |       |       |                  |                                    |                |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0          | R/W-0 | R/W-0 |  |

|                                    |       |       | FSC              | L<7:0>                             |                |       |       |  |

| bit 7                              |       |       |                  |                                    |                |       | bit 0 |  |

|                                    |       |       |                  |                                    |                |       |       |  |

| Legend:                            |       |       |                  |                                    |                |       |       |  |

| R = Readable bit W = Writable bit  |       |       | oit              | U = Unimplemented bit, read as '0' |                |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared                               | x = Bit is unk | nown  |       |  |

bit 15-0 **FSCL<15:0>:** Frequency Scale Register bits The value in this register is added to the frequency scaling accumulator at each pwm\_master\_clk. When the accumulated value exceeds the value of FSMINPER, a clock pulse is produced.

#### REGISTER 12-3: FSMINPER: FREQUENCY SCALING MINIMUM PERIOD REGISTER

| R/W-0                              | R/W-0 | R/W-0            | R/W-0              | R/W-0         | R/W-0           | R/W-0    | R/W-0 |

|------------------------------------|-------|------------------|--------------------|---------------|-----------------|----------|-------|

|                                    |       |                  | FSMINP             | ER<15:8>      |                 |          |       |

| bit 15                             |       |                  |                    |               |                 |          | bit 8 |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0              | R/W-0         | R/W-0           | R/W-0    | R/W-0 |

|                                    |       |                  | FSMINF             | PER<7:0>      |                 |          |       |

| bit 7                              |       |                  |                    |               |                 |          | bit 0 |

| Legend:                            |       |                  |                    |               |                 |          |       |

| R = Readable b                     | it    | W = Writable bit |                    | U = Unimpleme | ented bit, read | l as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                  | '0' = Bit is clear | ed            | x = Bit is unkn | own      |       |

bit 15-0 **FSMINPER<15:0>:** Frequency Scaling Minimum Period Register bits This register holds the minimum clock period (maximum clock frequency) that can be produced by the frequency scaling circuit.

# REGISTER 13-27: ADTRIGnL/ADTRIGnH: ADC CHANNEL TRIGGER n(x) SELECTION REGISTERS LOW AND HIGH (x = 0 TO 25; n = 0 TO 6)

| U-0    | U-0 | U-0 | R/W-0        | R/W-0        | R/W-0        | R/W-0        | R/W-0        |

|--------|-----|-----|--------------|--------------|--------------|--------------|--------------|

| _      | —   | _   | TRGSRC(x+1)4 | TRGSRC(x+1)3 | TRGSRC(x+1)2 | TRGSRC(x+1)1 | TRGSRC(x+1)0 |

| bit 15 |     |     |              |              |              |              | bit 8        |

| U-0   | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-----|-----|----------|----------|----------|----------|----------|

|       | —   | —   | TRGSRCx4 | TRGSRCx3 | TRGSRCx2 | TRGSRCx1 | TRGSRCx0 |

| bit 7 |     |     |          |          |          |          | bit 0    |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | <b>TRGSRC(x+1)&lt;4:0&gt;:</b> Trigger Source Selection for Corresponding Analog Inputs bits (TRGSRC1 to TRGSRC25 – Odd) |

|----------|--------------------------------------------------------------------------------------------------------------------------|

|          | 11111 = ADTRG31 (PPS input)                                                                                              |

|          | 11110 = PTG                                                                                                              |

|          | 11101 = CLC2                                                                                                             |

|          | 11100 = CLC1                                                                                                             |

|          | 11011 = MCCP9                                                                                                            |

|          | 11010 = SCCP7                                                                                                            |

|          | 11001 = SCCP6                                                                                                            |

|          | 11000 <b>= SCCP5</b>                                                                                                     |

|          | 10111 = SCCP4                                                                                                            |

|          | 10110 = SCCP3                                                                                                            |

|          | 10101 <b>= SCCP2</b>                                                                                                     |

|          | 10100 = SCCP1                                                                                                            |

|          | 10011 = PWM8 Trigger 2                                                                                                   |

|          | 10010 <b>= PWM8 Trigger 1</b>                                                                                            |

|          | 10001 = PWM7 Trigger 2                                                                                                   |

|          | 10000 <b>= PWM7 Trigger 1</b>                                                                                            |

|          | 01111 = PWM6 Trigger 2                                                                                                   |

|          | 01110 = PWM6 Trigger 1                                                                                                   |

|          | 01101 = PWM5 Trigger 2                                                                                                   |

|          | 01100 = PWM5 Trigger 1                                                                                                   |

|          | 01011 = PWM4 Trigger 2                                                                                                   |

|          | 01010 = PWM4 Trigger 1                                                                                                   |

|          | 01001 = PWM3 Trigger 2                                                                                                   |

|          | 01000 = PWM3 Trigger 1                                                                                                   |

|          | 00111 = PWM2 Trigger 2                                                                                                   |

|          | 00110 = PWM2 Trigger 1                                                                                                   |

|          | 00101 = PWM1 Trigger 2                                                                                                   |

|          | 00100 = PWM1 Trigger 1                                                                                                   |

|          | 00011 = Reserved                                                                                                         |

|          | 00010 = Level software trigger                                                                                           |

|          | 00001 = Common software trigger<br>00000 = No trigger is enabled                                                         |

|          |                                                                                                                          |

| hit 7_5  | Unimplemented: Read as '0'                                                                                               |

bit 7-5 Unimplemented: Read as '0'

| R/W-0         | R/W-0                                | R/W-0                                       | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0             |

|---------------|--------------------------------------|---------------------------------------------|------------------|-------------------|------------------|-----------------|-------------------|

| TXMTIE        | PERIE                                | ABDOVE                                      | CERIE            | FERIE             | RXBKIE           | OERIE           | TXCIE             |

| bit 15        |                                      |                                             |                  |                   |                  |                 | bit 8             |

| R-1           | R-0                                  | R/W-0, HS                                   | R/W-0, HC        | R-0               | R/W-0, HC        | R/W-0, HC       | R/W-0, HC         |

| TRMT          | PERR                                 | ABDOVF                                      | CERIF            | FERR              | RXBKIF           | OERR            | TXCIF             |

| bit 7         | FLNN                                 | ABDOVE                                      | GERIF            | FERN              | RADRIF           | UERK            | bit C             |

|               |                                      |                                             |                  |                   |                  |                 |                   |

| Legend:       |                                      | HS = Hardwar                                | e Settable bit   |                   | re Clearable bi  |                 |                   |

| R = Readabl   |                                      | W = Writable                                | bit              | -                 | nented bit, read | l as '0'        |                   |

| -n = Value at | POR                                  | '1' = Bit is set                            |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown              |

| bit 15        | TXMTIE: Tran                         | ısmit Shifter Err                           | npty Interrupt E | nable bit         |                  |                 |                   |

|               | 1 = Interrupt is                     |                                             |                  |                   |                  |                 |                   |

|               | 0 = Interrupt is                     | s disabled                                  |                  |                   |                  |                 |                   |

| bit 14        | PERIE: Parity                        | Error Interrupt                             | Enable bit       |                   |                  |                 |                   |

|               | 1 = Interrupt is                     |                                             |                  |                   |                  |                 |                   |

| 1.1.40        | 0 = Interrupt is                     |                                             |                  |                   |                  |                 |                   |

| bit 13        | 1 = Interrupt is                     | to-Baud Rate A<br>s enabled                 | cquisition inter | rrupt Enable bil  | [                |                 |                   |

|               | 0 = Interrupt is                     |                                             |                  |                   |                  |                 |                   |

| bit 12        | CERIE: Check                         | ksum Error Inte                             | rrupt Enable b   | it                |                  |                 |                   |

|               | 1 = Interrupt is<br>0 = Interrupt is |                                             |                  |                   |                  |                 |                   |

| bit 11        | FERIE: Frami                         | ng Error Interru                            | pt Enable bit    |                   |                  |                 |                   |

|               | 1 = Interrupt is<br>0 = Interrupt is |                                             |                  |                   |                  |                 |                   |

| bit 10        | RXBKIE: Rec                          | eive Break Inte                             | rrupt Enable b   | it                |                  |                 |                   |

|               | 1 = Interrupt is<br>0 = Interrupt is |                                             |                  |                   |                  |                 |                   |

| bit 9         | OERIE: Recei                         | ive Buffer Over                             | flow Interrupt E | Enable bit        |                  |                 |                   |

|               | 1 = Interrupt is<br>0 = Interrupt is |                                             | ·                |                   |                  |                 |                   |

| bit 8         | •                                    | mit Collision Int                           | errupt Enable    | bit               |                  |                 |                   |

|               | 1 = Interrupt is<br>0 = Interrupt is | s enabled                                   | ·                |                   |                  |                 |                   |

| bit 7         | -                                    | nit Shifter Empt                            | y Interrupt Flag | g bit (read-only  | )                |                 |                   |

|               | 1 = Transmit<br>bit when \$          | Shift Register ( <sup>*</sup><br>STPMD = 0) | rsR) is empty    |                   | p bit when STP   | MD = 1  or mide | lle of first Stop |

| L:1 0         |                                      | Shift Register is                           |                  |                   |                  |                 |                   |

| bit 6         | LIN and Parity                       | Error/Address                               | Received/Forw    | ard Frame Inte    | errupt Flag bit  |                 |                   |

|               | 1 = Parity erro<br>0 = No parity e   | or detected                                 |                  |                   |                  |                 |                   |

|               | Address Mode                         |                                             |                  |                   |                  |                 |                   |

|               | 1 = Address re                       |                                             |                  |                   |                  |                 |                   |

|               | 0 = No addres                        |                                             |                  |                   |                  |                 |                   |

|               | All Other Mod<br>Not used.           | <u>es:</u>                                  |                  |                   |                  |                 |                   |

|               |                                      |                                             |                  |                   |                  |                 |                   |

#### **REGISTER 16-3: UXSTA: UARTX STATUS REGISTER**

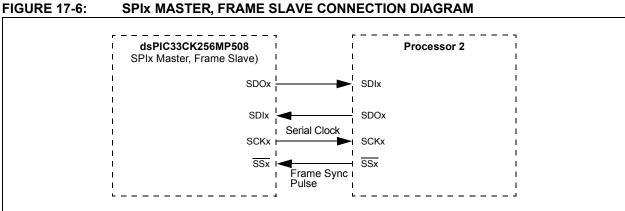

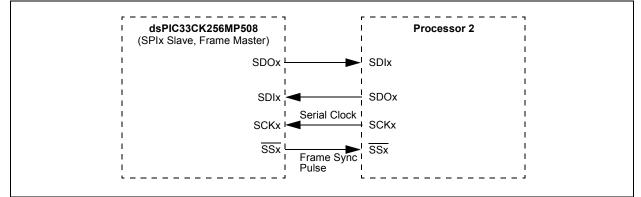

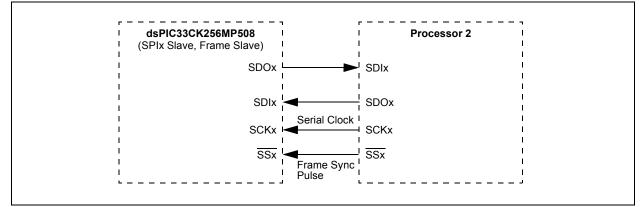

# dsPIC33CK256MP508 FAMILY

#### **FIGURE 17-7:** SPIx SLAVE, FRAME MASTER CONNECTION DIAGRAM

#### **FIGURE 17-8:** SPIx SLAVE, FRAME SLAVE CONNECTION DIAGRAM

#### EQUATION 17-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED

$$Baud Rate = \frac{FPB}{(2 * (SPIxBRG + 1))}$$

Where:

FPB is the Peripheral Bus Clock Frequency.

#### REGISTER 18-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <b>S:</b> I2Cx Start bit<br>Updated when Start, Reset or Stop is detected; cleared when the I <sup>2</sup> C module is disabled, I2CEN = 0.<br>1 = Indicates that a Start (or Repeated Start) bit has been detected last<br>0 = Start bit was not detected last |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C Slave)                                                                                                                                                                              |

|       | <ul> <li>1 = Read: Indicates the data transfer is output from the Slave</li> <li>0 = Write: Indicates the data transfer is input to the Slave</li> </ul>                                                                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                             |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> </ul>                                                                                                                                             |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                            |

|       | 1 = Transmit is in progress, I2CxTRN is full (8-bits of data)                                                                                                                                                                                                   |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                                 |

#### REGISTER 18-4: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0 |

|--------|-----|-----|-----|-----|-----|----------|-------|

| —      | —   | —   | —   | —   | —   | MSK<9:8> |       |

| bit 15 |     |     |     |     |     |          | bit 8 |

|        |     |     |     |     |     |          |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| MSK<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7    |       |       |       |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 MSK<9:0>: I2Cx Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

### REGISTER 19-11: PMWADDR: PARALLEL MASTER PORT WRITE ADDRESS REGISTER<sup>(2)</sup>

| R/W-0<br>WCS1 <sup>(1)</sup><br>VADDR14 <sup>(1)</sup><br>R/W-0 | R/W-0<br>R/W-0                                                                                                                                         | R/W-0<br>R/W-0<br>WADE                                                                                                                                                                                                                                                                                                                                                | R/W-0<br>WADD<br>R/W-0<br>DR<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0<br>R<13:8><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0<br>bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VADDR14 <sup>(1)</sup>                                          | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                 | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| R/W-0                                                           | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| R/W-0                                                           | R/W-0                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DAALO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                 | 10000                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                 |                                                                                                                                                        | With DE                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                 |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                 |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                 |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| ,                                                               | N = Writable bi                                                                                                                                        | t                                                                                                                                                                                                                                                                                                                                                                     | U = Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |