Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck64mp206t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33CK256MP508 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1 and Table 2. The following pages show their pinout diagrams.

# TABLE 1: dsPIC33CK256MP508 FAMILY WITH CAN FD

|                   |      |       |          | r          |              |        | 1         |        |              |      | r    |     | 1                |     | 1   |     | r   |                  |                    |            |        |     |            |

|-------------------|------|-------|----------|------------|--------------|--------|-----------|--------|--------------|------|------|-----|------------------|-----|-----|-----|-----|------------------|--------------------|------------|--------|-----|------------|

| Product Pins      | Pins | Flash | Data RAM | ADC Module | ADC Channels | Timers | MCCP/SCCP | CAN FD | DMA Channels | SENT | UART | IdS | I <sup>2</sup> C | GEI | CLC | ЬТG | CRC | PWM (High Speed) | Analog Comparators | 12-Bit DAC | dmA qO | PMP | REFO Clock |

| dsPIC33CK256MP508 | 80   | 256K  | 24K      | 3          | 24           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK256MP506 | 64   | 256K  | 24K      | 3          | 20           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK256MP505 | 48   | 256K  | 24K      | 3          | 19           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK256MP503 | 36   | 256K  | 24K      | 3          | 16           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK256MP502 | 28   | 256K  | 24K      | 3          | 12           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 2      | 0   | 1          |

| dsPIC33CK128MP508 | 80   | 128K  | 16K      | 3          | 24           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK128MP506 | 64   | 128K  | 16K      | 3          | 20           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK128MP505 | 48   | 128K  | 16K      | 3          | 19           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK128MP503 | 36   | 128K  | 16K      | 3          | 16           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK128MP502 | 28   | 128K  | 16K      | 3          | 12           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 2      | 0   | 1          |

| dsPIC33CK64MP508  | 80   | 64k   | 8k       | 3          | 24           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK64MP506  | 64   | 64k   | 8k       | 3          | 20           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK64MP505  | 48   | 64k   | 8k       | 3          | 19           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK64MP503  | 36   | 64k   | 8k       | 3          | 16           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK64MP502  | 28   | 64k   | 8k       | 3          | 12           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 2      | 0   | 1          |

| dsPIC33CK32MP506  | 64   | 32k   | 8k       | 3          | 20           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 1   | 1          |

| dsPIC33CK32MP505  | 48   | 32k   | 8k       | 3          | 19           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK32MP503  | 36   | 32k   | 8k       | 3          | 16           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 3      | 0   | 1          |

| dsPIC33CK32MP502  | 28   | 32k   | 8k       | 3          | 12           | 1      | 1/8       | 1      | 4            | 2    | 3    | 3   | 3                | 2   | 4   | 1   | 1   | 8                | 3                  | 3          | 2      | 0   | 1          |

# Pin Diagrams

| RA1 []<br>RA2 [] 2<br>RA3 [] 3                             | 28 RA0<br>27 MCLR<br>26 RB15  |

|------------------------------------------------------------|-------------------------------|

| RA3 [] 3<br>RA4 [] 4<br>AVDD [] 5<br>AVss [] 6<br>VDD [] 7 | 25 RB14<br>24 RB13            |

| AVss 6<br>VDD 7                                            | 23 RB12<br>22 RB11            |

| VDD 7 7<br>VSS 8 7<br>RB0 9 8<br>RB1 10 10                 | 21 RB10<br>20 VDD<br>19 VSS   |

| RB1 [ 10 ]<br>RB2 [ 11 ]<br>RB3 [ 12 ]                     | <b>8</b> 18   RB9<br>17   RB8 |

| RB4 [ 13<br>RB5 [ 14                                       | 16 RB7<br>15 RB6              |

#### TABLE 3: 28-PIN SSOP

| Pin # | Function                                                     | Pin # | Function                             |

|-------|--------------------------------------------------------------|-------|--------------------------------------|

| 1     | OA1IN-/ANA1/RA1                                              | 15    | PGC3/ <b>RP38</b> /SCL2/RB6          |

| 2     | OA1IN+/AN9/RA2                                               | 16    | TDO/AN2/CMP3A/ <b>RP39</b> /SDA3/RB7 |

| 3     | DACOUT1/AN3/CMP1C/RA3                                        | 17    | PGD1/AN10/ <b>RP40</b> /SCL1/RB8     |

| 4     | AN4/CMP3B/IBIAS3/RA4                                         | 18    | PGC1/AN11/ <b>RP41</b> /SDA1/RB9     |

| 5     | AVdd                                                         | 19    | Vss                                  |

| 6     | AVss                                                         | 20    | VDD                                  |

| 7     | VDD                                                          | 21    | TMS/ <b>RP42</b> /PWM3H/RB10         |

| 8     | Vss                                                          | 22    | TCK/ <b>RP43</b> /PWM3L/RB11         |

| 9     | OSCI/CLKI/AN5/RP32/RB0                                       | 23    | TDI/ <b>RP44</b> /PWM2H/RB12         |

| 10    | OSCO/CLKO/AN6/RP33/RB1                                       | 24    | RP45/PWM2L/RB13                      |

| 11    | OA2OUT/AN1/AN7/ANA0/CMP1D/CMP2D/CMP3D/RP34/<br>SCL3/INT0/RB2 | 25    | <b>RP46</b> /PWM1H/RB14              |

| 12    | PGD2/OA2IN-/AN8/ <b>RP35</b> /RB3                            | 26    | RP47/PWM1L/RB15                      |

| 13    | PGC2/OA2IN+/ <b>RP36</b> /RB4                                | 27    | MCLR                                 |

| 14    | PGD3/ <b>RP37</b> /SDA2/RB5                                  | 28    | OA1OUT/AN0/CMP1A/IBIAS0/RA0          |

Note: RPn represents remappable peripheral functions.

# TABLE 8-8: PORTA REGISTER SUMMARY

| Register | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3 | Bit 2      | Bit 1 | Bit 0 |

|----------|--------|--------|--------|--------|---------|--------|-------|-------|-------|-------|-------|--------------|-------|------------|-------|-------|

| ANSELA   | _      | —      | —      | —      | —       | —      | —     | —     | —     | —     | —     | ANSELA<4:0>  |       |            |       |       |

| TRISA    | _      | _      | _      | _      | —       | —      | —     | _     | —     | —     | —     |              |       | TRISA<4:0> |       |       |

| PORTA    | _      | _      | _      | _      | —       | —      | —     | _     | —     | —     | —     |              |       | RA<4:0>    |       |       |

| LATA     | _      | —      | —      | —      | —       | _      | _     | _     | _     | _     | _     | LATA<4:0>    |       |            |       |       |

| ODCA     | _      | —      | —      | —      | —       | _      | _     | _     | _     | _     | _     | ODCA<4:0>    |       |            |       |       |

| CNPUA    | _      | _      | _      | _      | —       | —      | —     | _     | —     | —     | —     | CNPUA<4:0>   |       |            |       |       |

| CNPDA    | _      | —      | —      | —      | —       | _      | _     | _     | _     | _     | _     |              | (     | CNPDA<4:0  | >     |       |

| CNCONA   | ON     | —      | —      | —      | CNSTYLE | _      | _     | _     | _     | _     | _     |              |       |            | —     |       |

| CNEN0A   |        | _      | _      | _      | _       | _      | —     | —     | —     |       |       | CNEN0A<4:0>  |       |            |       |       |

| CNSTATA  | _      | —      | —      | —      | —       | —      | —     | —     | —     | _     | _     | CNSTATA<4:0> |       |            |       |       |

| CNEN1A   |        | —      | _      | _      | _       | —      | —     | _     | —     |       |       | CNEN1A<4:0>  |       |            |       |       |

| CNFA     |        | _      | _      | _      | _       | _      | _     | _     | _     |       |       | CNFA<4:0>    |       |            |       |       |

# TABLE 8-9: PORTB REGISTER SUMMARY

| Register | Bit 15        | Bit 14      | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1 | Bit 0 |

|----------|---------------|-------------|--------|--------|---------|--------|-------|----------|-------|-------|-------|-------|-------|----------|-------|-------|

| ANSELB   | -             | —           | —      | _      | -       | —      | A     | NSELB<9: | 7>    | —     | —     |       | A     | NSELB<4: | 0>    |       |

| TRISB    |               | TRISB<15:0> |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| PORTB    |               | RB<15:0>    |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| LATB     |               | LATB<15:0>  |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| ODCB     |               | ODCB<15:0>  |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| CNPUB    | CNPUB<15:0>   |             |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| CNPDB    |               |             |        |        |         |        | CN    | PDB<15:0 | >     |       |       |       |       |          |       |       |

| CNCONB   | ON            | —           | —      | -      | CNSTYLE | _      | —     | _        | _     | _     | —     | _     | _     | _        | _     | _     |

| CNEN0B   |               |             |        |        |         |        | CN    | EN0<15:0 | >     |       |       |       |       |          |       |       |

| CNSTATB  | CNSTATB<15:0> |             |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| CNEN1B   | CNEN1B<15:0>  |             |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

| CNFB     | CNFB<15:0>    |             |        |        |         |        |       |          |       |       |       |       |       |          |       |       |

#### REGISTER 8-37: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SS2R7 | SS2R6 | SS2R5 | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |       |       |       | •     |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8

Unimplemented: Read as '0'

bit 7-0

SS2R<7:0>: Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits See Table 8-4.

#### REGISTER 8-38: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| CAN1RXR7 | CAN1RXR6 | CAN1RXR5 | CAN1RXR4 | CAN1RXR3 | CAN1RXR2 | CAN1RXR1 | CAN1RXR0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

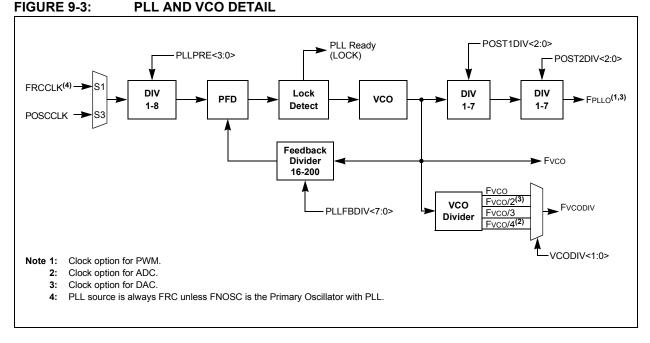

bit 7-0 CAN1RXR<7:0>: Assign CAN1 Input (CAN1RX) to the Corresponding RPn Pin bits See Table 8-4. The Primary Oscillator and internal FRC Oscillator sources can optionally use an on-chip PLL to obtain higher operating speeds. Figure 9-3 illustrates a block diagram of the PLL module. For PLL operation, the following requirements must be met at all times without exception:

- The PLL Input Frequency (FPLLI) must be in the range of 8 MHz to 64 MHz

- The PFD Input Frequency (FPFD) must be in the range of 8 MHz to (FVCO/16) MHz

The VCO Output Frequency (Fvco) must be in the range of 400 MHz to 1600 MHz

# REGISTER 11-23: C1TXATIFH: CAN TRANSMIT ATTEMPT INTERRUPT STATUS REGISTER HIGH<sup>(1)</sup>

| R-0             | R-0                                                                        | R-0              | R-0           | R-0           | R-0            | R-0       | R-0   |

|-----------------|----------------------------------------------------------------------------|------------------|---------------|---------------|----------------|-----------|-------|

|                 |                                                                            |                  | <b>TFATIF</b> | <31:24>       |                |           |       |

| bit 15          |                                                                            |                  |               |               |                |           | bit 8 |

|                 |                                                                            |                  |               |               |                |           |       |

| R-0             | R-0                                                                        | R-0              | R-0           | R-0           | R-0            | R-0       | R-0   |

|                 |                                                                            |                  | <b>TFATIF</b> | <23:16>       |                |           |       |

| bit 7           |                                                                            |                  |               |               |                |           | bit 0 |

|                 |                                                                            |                  |               |               |                |           |       |

| Legend:         |                                                                            |                  |               |               |                |           |       |

| R = Readable    | bit                                                                        | W = Writable bit |               | U = Unimpleme | ented bit, rea | ad as '0' |       |

| -n = Value at F | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                  |               |               |                | iown      |       |

bit 15-0 TFATIF<31:16>: Unimplemented

Note 1: C1TXATIFH: FIFO: TFATIFx (flag needs to be cleared in the FIFO register).

### REGISTER 11-24: C1TXATIFL: CAN TRANSMIT ATTEMPT INTERRUPT STATUS REGISTER LOW<sup>(1)</sup>

| R-0             | R-0 | R-0              | R-0   | R-0                   | R-0            | R-0             | R-0   |

|-----------------|-----|------------------|-------|-----------------------|----------------|-----------------|-------|

|                 |     |                  | TFATI | F<15:8>               |                |                 |       |

| bit 15          |     |                  |       |                       |                |                 | bit 8 |

| R-0             | R-0 | R-0              | R-0   | R-0                   | R-0            | R-0             | R-0   |

|                 |     |                  | TFATI | F<7:0> <sup>(2)</sup> |                |                 |       |

| bit 7           |     |                  |       |                       |                |                 | bit 0 |

| Legend:         |     |                  |       |                       |                |                 |       |

| R = Readable I  | bit | W = Writable bit |       | U = Unimplen          | nented bit, re | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |       | '0' = Bit is clea     | ared           | x = Bit is unki | nown  |

bit 15-8 **TFATIF<15:8>:** Unimplemented

bit 7-0 TFATIF<7:0>: Transmit FIFO/TXQ Attempt Interrupt Pending bits<sup>(2)</sup>

1 = Interrupt is pending

0 = Interrupt is not pending

Note 1: C1TXATIFL: FIFO: TFATIFx (flag needs to be cleared in the FIFO register).

**2:** TFATIF0 is for the transmit queue.

#### REGISTER 11-51: C1FLTCONxL: CAN FILTER CONTROL REGISTER x LOW (x = 0 TO 3; a = 0, 4, 8, 12; b = 1, 5, 9, 13)

|               | a = 0                                             | , 4, 8, 12; D =                                           | 1, 5, 9, 13)     |                  |                  |                 |       |  |

|---------------|---------------------------------------------------|-----------------------------------------------------------|------------------|------------------|------------------|-----------------|-------|--|

| R/W-0         | U-0                                               | U-0                                                       | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |

| FLTENb        | _                                                 | - FbBP4 FbBP3 FbBP2 FbBP1 Fl                              |                  |                  |                  |                 |       |  |

| bit 15        |                                                   |                                                           |                  |                  |                  | ·               | bit 8 |  |

|               |                                                   |                                                           |                  |                  |                  |                 |       |  |

| R/W-0         | U-0                                               | U-0                                                       | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |

| FLTENa        |                                                   | —     —     FaBP4     FaBP3     FaBP2     FaBP1     FaBP0 |                  |                  |                  |                 |       |  |

| bit 7         |                                                   |                                                           |                  |                  |                  |                 | bit 0 |  |

|               |                                                   |                                                           |                  |                  |                  |                 |       |  |

| Legend:       |                                                   |                                                           |                  |                  |                  |                 |       |  |

| R = Readabl   |                                                   | W = Writable                                              |                  | -                | nented bit, read |                 |       |  |

| -n = Value at | POR                                               | '1' = Bit is set                                          |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

| bit 15        | FLTENb: Ena<br>1 = Filter is e<br>0 = Filter is d |                                                           | Accept Messag    | ges bit          |                  |                 |       |  |

| bit 14-13     | Unimplemer                                        | nted: Read as '                                           | 0'               |                  |                  |                 |       |  |

| bit 12-8      | FbBP<4:0>:                                        | Pointer to Obje                                           | ct When Filter   | b Hits bits      |                  |                 |       |  |

|               | 00111 <b>= Me</b> s                               | 000 = Reserved<br>ssage matching<br>ssage matching        | filter is stored |                  |                  |                 |       |  |

|               | 00001 <b>= Me</b> s                               | ssage matching<br>ssage matching<br>served; Object (      | filter is stored | in Object 1      | ceive message    | 25              |       |  |

| bit 7         |                                                   | able Filter a to A                                        |                  |                  |                  |                 |       |  |

|               | 1 = Filter is e<br>0 = Filter is d                | enabled                                                   |                  |                  |                  |                 |       |  |

| bit 6-5       | Unimplemer                                        | nted: Read as '                                           | 0'               |                  |                  |                 |       |  |

| bit 4-0       | FaBP<4:0>:                                        | Pointer to Obje                                           | ct When Filter   | a Hits bits      |                  |                 |       |  |

|               |                                                   | 000 <b>= Reserve</b>                                      |                  |                  |                  |                 |       |  |

|               | 00110 <b>= Me</b> s                               | ssage matching<br>ssage matching                          |                  |                  |                  |                 |       |  |

|               | 00001 <b>= Me</b> s                               | ssage matching<br>ssage matching<br>served; Object (      | filter is stored | in Object 1      | ceive message    | es              |       |  |

|               |                                                   |                                                           |                  |                  |                  |                 |       |  |

#### REGISTER 12-23: PGxPHASE: PWM GENERATOR x PHASE REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0                                  | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|------------------------------------|-------|----------------|----------------------------------------|--------------|-----------------|-----------|-------|

|                                    |       |                | PGxPF                                  | IASE<15:8>   |                 |           |       |

| bit 15                             |       |                |                                        |              |                 |           | bit 8 |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0                                  | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

| -                                  |       |                | PGxP                                   | HASE<7:0>    |                 |           |       |

| bit 7                              |       |                |                                        |              |                 |           | bit 0 |

|                                    |       |                |                                        |              |                 |           |       |

| Legend:                            |       |                |                                        |              |                 |           |       |

| R = Readable                       | e bit | W = Writable b | it                                     | U = Unimplen | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared x = Bit is unknow |              |                 | iown      |       |

bit 15-0 PGxPHASE<15:0>: PWM Generator x Phase Register bits

### REGISTER 12-24: PGxDC: PWM GENERATOR x DUTY CYCLE REGISTER

| R/W-0         | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|---------------|-------|------------------|-------|------------------------|-----------------|-----------------|-------|

|               |       |                  | PGxD  | C<15:8> <sup>(1)</sup> |                 |                 |       |

| bit 15        |       |                  |       |                        |                 |                 | bit 8 |

| R/W-0         | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|               |       |                  | PGxE  | )C<7:0> <sup>(1)</sup> |                 |                 |       |

| bit 7         |       |                  |       |                        |                 |                 | bit 0 |

|               |       |                  |       |                        |                 |                 |       |

| Legend:       |       |                  |       |                        |                 |                 |       |

| R = Readabl   | e bit | W = Writable bit | t     | U = Unimplem           | nented bit, rea | d as '0'        |       |

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is clea      | ared            | x = Bit is unkn | own   |

bit 15-0 **PGxDC<15:0>:** PWM Generator x Duty Cycle Register bits<sup>(1)</sup>

Note 1: Duty cycle values less than '0x0008' should not be used ('0x0020' in High-Resolution mode).

#### REGISTER 13-17: ADEISTATL: ADC EARLY INTERRUPT STATUS REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0          | R/W-0                                | R/W-0         | R/W-0           | R/W-0    | R/W-0 |

|------------------------------------|-------|----------------|--------------------------------------|---------------|-----------------|----------|-------|

|                                    |       |                | EIST                                 | AT<15:8>      |                 |          |       |

| bit 15                             |       |                |                                      |               |                 |          | bit 8 |

|                                    |       |                |                                      |               |                 |          |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0                                | R/W-0         | R/W-0           | R/W-0    | R/W-0 |

|                                    |       |                | EIST                                 | AT<7:0>       |                 |          |       |

| bit 7                              |       |                |                                      |               |                 |          | bit 0 |

|                                    |       |                |                                      |               |                 |          |       |

| Legend:                            |       |                |                                      |               |                 |          |       |

| R = Readable                       | bit   | W = Writable b | bit                                  | U = Unimplerr | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared x = Bit is unkn |               | nown            |          |       |

bit 15-0 EISTAT<15:0>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

#### REGISTER 13-18: ADEISTATH: ADC EARLY INTERRUPT STATUS REGISTER HIGH

| U-0                                | U-0   | U-0            | U-0    | U-0              | U-0              | R/W-0           | R/W-0   |

|------------------------------------|-------|----------------|--------|------------------|------------------|-----------------|---------|

| —                                  | _     | —              | —      | —                | _                | EISTAT          | <25:24> |

| bit 15                             |       |                |        |                  |                  |                 | bit 8   |

|                                    |       |                |        |                  |                  |                 |         |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|                                    |       |                | EISTAT | <23:16>          |                  |                 |         |

| bit 7                              |       |                |        |                  |                  |                 | bit 0   |

|                                    |       |                |        |                  |                  |                 |         |

| Legend:                            |       |                |        |                  |                  |                 |         |

| R = Readable                       | bit   | W = Writable I | bit    | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at POR '1' = Bit is set |       |                |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                                    |       |                |        |                  |                  |                 |         |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 EISTAT<25:16>: Early Interrupt Status for Corresponding Analog Inputs bits

1 = Early interrupt was generated

0 = Early interrupt was not generated since the last ADCBUFx read

# REGISTER 15-10: VELxHLD: VELOCITY x COUNTER HOLD REGISTER<sup>(1)</sup>

|                |       | D 444 0              |       |         | D 44/ 0        |          | D/14/ 0 |

|----------------|-------|----------------------|-------|---------|----------------|----------|---------|

| R/W-0          | R/W-0 | R/W-0                | R/W-0 | R/W-0   | R/W-0          | R/W-0    | R/W-0   |

|                |       |                      | VELHL | D<15:8> |                |          |         |

| bit 15         |       |                      |       |         |                |          | bit 8   |

| R/W-0          | R/W-0 | R/W-0                | R/W-0 | R/W-0   | R/W-0          | R/W-0    | R/W-0   |

|                |       |                      | VELHL | _D<7:0> |                |          |         |

| bit 7          |       |                      |       |         |                |          | bit 0   |

|                |       |                      |       |         |                |          |         |

| Legend:        |       |                      |       |         |                |          |         |

| D - Doodoblo I | hit.  | \// = \//ritable bit |       |         | antad hit raad | l == (0' |         |

|                                    | U = Unimplemented bit, read |                    |

|------------------------------------|-----------------------------|--------------------|

| -n = Value at POR '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 VELHLD<15:0>: Hold for Reading/Writing Velocity Counter Register (VELxCNT) bits

Note 1: This register is not present on all devices.

The SPI module has the ability to generate three interrupts reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- SPIRBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxGIF. This event occurs when:

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 17-1 and Figure 17-2.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1 and SPIxCON2 refer to the control registers for any of the three SPI modules. To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L and SPIxCON1H registers with the MSTEN bit (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 5. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF registers.

- 2. If using interrupts:

- a) Clear the SPIxBUFL and SPIxBUFH registers.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1L<8>) is set, then the SSEN bit (SPIxCON1L<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

#### REGISTER 17-3: SPIxCON2L: SPIx CONTROL REGISTER 2 LOW

| U-0        | U-0                                                                           | U-0                                              | U-0           | U-0               | U-0             | U-0             | U-0   |  |  |

|------------|-------------------------------------------------------------------------------|--------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|--|--|

|            | —                                                                             | —                                                |               | _                 | _               | _               | _     |  |  |

| bit 15     |                                                                               |                                                  |               |                   |                 |                 | bit 8 |  |  |

|            |                                                                               |                                                  |               |                   |                 |                 | ]     |  |  |

| U-0        | U-0                                                                           | U-0                                              | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |

| _          |                                                                               |                                                  |               |                   | _ENGTH<4:0>     |                 |       |  |  |

| bit 7      |                                                                               |                                                  |               |                   |                 |                 | bit 0 |  |  |

|            |                                                                               |                                                  |               |                   |                 |                 |       |  |  |

| Legend:    |                                                                               |                                                  |               |                   |                 |                 |       |  |  |

| R = Reada  | hle hit                                                                       | W = Writable                                     | bit           | II = I Inimplem   | ented bit, read | as '0'          |       |  |  |

| -n = Value |                                                                               | '1' = Bit is se                                  |               | '0' = Bit is clea |                 | x = Bit is unkn | 0.4/0 |  |  |

|            | alfon                                                                         | 1 - Dit 15 50                                    | L             |                   | areu            |                 | OWIT  |  |  |

| hit 15 5   | Unimplana                                                                     | ntad. Dood oo                                    | 'o'           |                   |                 |                 |       |  |  |

| bit 15-5   | -                                                                             | nted: Read as                                    |               | :+- (1 2)         |                 |                 |       |  |  |

| bit 4-0    |                                                                               |                                                  | Word Length b | DITS(1,-)         |                 |                 |       |  |  |

|            | 11111 = 32-<br>11110 = 31-                                                    |                                                  |               |                   |                 |                 |       |  |  |

|            | 1110 <b>–</b> 31-<br>11101 <b>–</b> 30-                                       |                                                  |               |                   |                 |                 |       |  |  |

|            | 11100 <b>= 29</b> -                                                           |                                                  |               |                   |                 |                 |       |  |  |

|            | 11011 = 28-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 11010 <b>= 27</b> -                                                           | -bit data                                        |               |                   |                 |                 |       |  |  |

|            | 11001 <b>= 26</b> -                                                           |                                                  |               |                   |                 |                 |       |  |  |

|            | 11000 = 25-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 10111 = 24-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 10110 <b>= 23</b> -<br>10101 <b>= 22</b> -                                    |                                                  |               |                   |                 |                 |       |  |  |

|            | 10100 = 21-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 10011 = 20-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 10010 <b>= 19</b> -                                                           | -bit data                                        |               |                   |                 |                 |       |  |  |

|            | 10001 = 18-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 10000 = 17-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 01111 = 16-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 01110 = <b>15</b> -<br>01101 = <b>14</b> -                                    |                                                  |               |                   |                 |                 |       |  |  |

|            | 01100 = 13-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 01011 = 12-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 01010 <b>= 11</b> -                                                           | bit data                                         |               |                   |                 |                 |       |  |  |

|            | 01001 = 10-                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 01000 = 9-b                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 00111 = 8-b                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 00110 = 7-b<br>00101 = 6-b                                                    |                                                  |               |                   |                 |                 |       |  |  |

|            | 00101 = 0-1000 = 5-10000 = 5-100000 = 5-1000000000000000000000000000000000000 |                                                  |               |                   |                 |                 |       |  |  |

|            | 00011 = <b>4</b> -b                                                           |                                                  |               |                   |                 |                 |       |  |  |

|            | 00010 = 3-b                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 00001 = 2-b                                                                   |                                                  |               |                   |                 |                 |       |  |  |

|            | 00000 <b>= Se</b>                                                             | 00000 = See MODE<32,16> bits in SPIxCON1L<11:10> |               |                   |                 |                 |       |  |  |

- **Note 1:** These bits are effective when AUDEN = 0 only.

- 2: Varying the length by changing these bits does not affect the depth of the TX/RX FIFO.

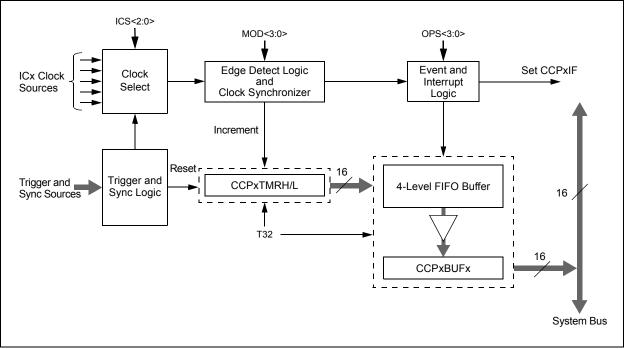

# 22.4 Input Capture Mode

Input Capture mode is used to capture a timer value from an independent timer base, upon an event, on an input pin or other internal trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 22-6 depicts a simplified block diagram of Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 22-3.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                        |  |  |  |

|------------------------------|-----------------------|---------------------------------------|--|--|--|

| 0000                         | 0                     | Edge Detect (16-bit capture)          |  |  |  |

| 0000                         | 1                     | Edge Detect (32-bit capture)          |  |  |  |

| 0001                         | 0                     | Every Rising (16-bit capture)         |  |  |  |

| 0001                         | 1                     | Every Rising (32-bit capture)         |  |  |  |

| 0010                         | 0                     | Every Falling (16-bit capture)        |  |  |  |

| 0010                         | 1                     | Every Falling (32-bit capture)        |  |  |  |

| 0011                         | 0                     | Every Rising/Falling (16-bit capture) |  |  |  |

| 0011                         | 1                     | Every Rising/Falling (32-bit capture) |  |  |  |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)     |  |  |  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)     |  |  |  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture)    |  |  |  |

| 0101                         | 1                     | Every 16th Rising (32-bit capture)    |  |  |  |

TABLE 22-3: INPUT CAPTURE x MODES

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|--------|---------|-------|-------|-------|

|         |       |       | PTGHOL | D<15:8> |       |       |       |

| bit 15  |       |       |        |         |       |       | bit 8 |

|         |       |       |        |         |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | PTGHO  | _D<7:0> |       |       |       |

| bit 7   |       |       |        |         |       |       | bit 0 |

|         |       |       |        |         |       |       |       |

| Legend: |       |       |        |         |       |       |       |

| Legenu.                           |                  |                        |                                    |  |  |  |  |

|-----------------------------------|------------------|------------------------|------------------------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |  |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits This register holds the user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 register using the PTGCOPY command.

Note 1: These bits are read-only when the module is executing Step commands.

# REGISTER 24-6: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0        | R/W-0 | R/W-0 |  |  |  |  |  |  |  |

|----------------|--------------|-------|-------|--|--|--|--|--|--|--|

| PTGT0LIM<15:8> |              |       |       |  |  |  |  |  |  |  |

| bit 15         | bit 15 bit 8 |       |       |  |  |  |  |  |  |  |

|                |              |       |       |  |  |  |  |  |  |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|---------------|-------|-------|-------|-------|--|--|--|--|--|

| PTGT0LIM<7:0> |       |       |       |       |  |  |  |  |  |

| bit 7 bit C   |       |       |       |       |  |  |  |  |  |

| Legend:           |                  |                        |                              |  |  |

|-------------------|------------------|------------------------|------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | implemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown           |  |  |

bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register.

Note 1: These bits are read-only when the module is executing Step commands.

#### 30.2 Device Calibration and Identification

The dsPIC33CK256MP508 devices have two Identification registers, near the end of configuration memory space, that store the Device ID (DEVID) and Device Revision (DEVREV). These registers are used to determine the mask, variant and manufacturing information about the device. These registers are read-only and are shown in Register 30-18 and Register 30-19.

#### REGISTER 30-18: DEVREV: DEVICE REVISION REGISTER

| R       | R                 | R | R      | R            | R          | R | R      |

|---------|-------------------|---|--------|--------------|------------|---|--------|

|         |                   |   | DEVREV | /<23:16>     |            |   |        |

| bit 23  |                   |   |        |              |            |   | bit 16 |

|         |                   |   |        |              |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

|         |                   |   | DEVRE  | V<15:8>      |            |   |        |

| bit 15  |                   |   |        |              |            |   | bit 8  |

|         |                   |   |        |              |            |   |        |

| R       | R                 | R | R      | R            | R          | R | R      |

|         |                   |   | DEVRE  | :V<7:0>      |            |   |        |

| bit 7   |                   |   |        |              |            |   | bit 0  |

|         |                   |   |        |              |            |   |        |

| Legend: | R = Read-only bit |   |        | U = Unimpler | mented bit |   |        |

bit 23-0 **DEVREV<23:0>:** Device Revision bits

#### **REGISTER 30-19: DEVID: DEVICE ID REGISTERS**

| U-1           | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |  |  |

|---------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| _             |     |     | —   | —   | —   |     |     |  |  |

| bit 23 bit 16 |     |     |     |     |     |     |     |  |  |

| R      | R      | R      | R R    |        | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R                   | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> | DEV2 <sup>(1)</sup> | DEV1 <sup>(1)</sup> | DEV0 <sup>(1)</sup> |

| bit 7               |                     |                     |                     |                     |                     |                     | bit 0               |

Legend: R = Read-only bit U = Unimplemented bit

bit 23-16 Unimplemented: Read as '1'

- bit 15-8 **FAMID<7:0>:** Device Family Identifier bits

- 0111 1100 = dsPIC33CK256MP508 family

- bit 7-0 **DEV<7:0>:** Individual Device Identifier bits<sup>(1)</sup>

Note 1: See Table 30-4 for the list of Device Identifier bits.

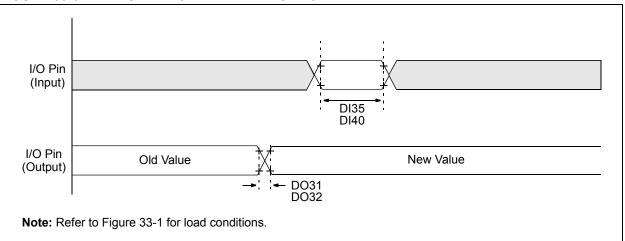

#### TABLE 33-24: I/O TIMING REQUIREMENTS

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |                                      |      |                     |      |       |            |  |  |

|------------------------------------------------------|--------|--------------------------------------|------|---------------------|------|-------|------------|--|--|

| Param<br>No.                                         | Symbol | Characteristic                       | Min. | Тур. <sup>(1)</sup> | Max. | Units | Conditions |  |  |

| DO31                                                 | TIOR   | Port Output Rise Time <sup>(2)</sup> |      | 6.5                 | 9.7  | ns    |            |  |  |

| DO32                                                 | TIOF   | Port Output Fall Time <sup>(2)</sup> | _    | 3.2                 | 4.2  | ns    |            |  |  |

| DI35                                                 | TINP   | INTx Pin High or Low Time (input)    | 20   | —                   | _    | ns    |            |  |  |

| DI40                                                 | Trbp   | CNx High or Low Time (input)         | 2    | _                   | _    | TCY   |            |  |  |

Note 1: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

**2:** This parameter is characterized but not tested in manufacturing.

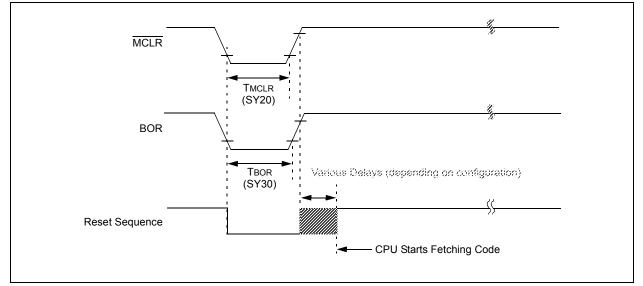

#### FIGURE 33-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

# TABLE 33-25:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

| •            | Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                                |      |                     |      |       |                    |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|---------------------|------|-------|--------------------|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                       | Characteristic <sup>(1)</sup>                                  | Min. | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SY00         | Τρυ                                                                                                                                                                                          | Power-up Period                                                |      | 200                 | _    | μs    | FNOSC<2:0> are FRC |  |  |

| SY10         | Tost                                                                                                                                                                                         | Oscillator Start-up Time                                       |      | 1024 Tosc           |      | _     | Tosc = OSCI period |  |  |

| SY13         | Tioz                                                                                                                                                                                         | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | _    | 1.5                 | —    | μs    |                    |  |  |

| SY20         | TMCLR                                                                                                                                                                                        | MCLR Pulse Width (low)                                         | 2    | _                   |      | μs    |                    |  |  |

| SY30         | TBOR                                                                                                                                                                                         | BOR Pulse Width (low)                                          | 1    | _                   |      | μs    |                    |  |  |

| SY35         | TFSCM                                                                                                                                                                                        | Fail-Safe Clock Monitor<br>Delay                               |      | —                   |      | μs    |                    |  |  |

| SY37         | Toscdfrc                                                                                                                                                                                     | FRC Oscillator Start-up<br>Delay                               | _    | —                   |      | μs    |                    |  |  |

| SY38         | Toscdlprc                                                                                                                                                                                    | LPRC Oscillator Start-up<br>Delay                              | _    | —                   | —    | μs    |                    |  |  |

$\label{eq:Note_1:} \textbf{Note_1:} \quad \textbf{These parameters are characterized but not tested in manufacturing.}$

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated.

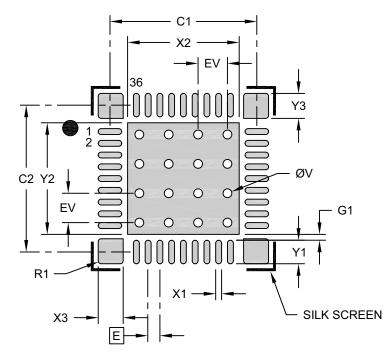

# 36-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M5) - 5x5 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                 | Units    |      |      |      |  |

|---------------------------------|----------|------|------|------|--|

| Dimension                       | n Limits | MIN  | NOM  | MAX  |  |

| Contact Pitch                   | 0.40 BSC |      |      |      |  |

| Optional Center Pad Width       | X2       |      |      | 3.80 |  |

| Optional Center Pad Length      | Y2       |      |      | 3.80 |  |

| Contact Pad Spacing             | C1       |      | 5.00 |      |  |

| Contact Pad Spacing             | C2       |      | 5.00 |      |  |

| Contact Pad Width (X36)         | X1       |      |      | 0.20 |  |

| Contact Pad Length (X36)        | Y1       |      |      | 0.80 |  |

| Corner Pad Width (X4)           | X3       |      |      | 0.20 |  |

| Corner Pad Length (X36)         | Y3       |      |      | 0.85 |  |

| Corner Pad Radius               | R1       |      | 0.10 |      |  |

| Contact Pad to Center Pad (X36) | G1       | 0.20 |      |      |  |

| Thermal Via Diameter            | V        |      | 0.30 |      |  |

| Thermal Via Pitch               | EV       |      | 1.00 |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2436A-M5

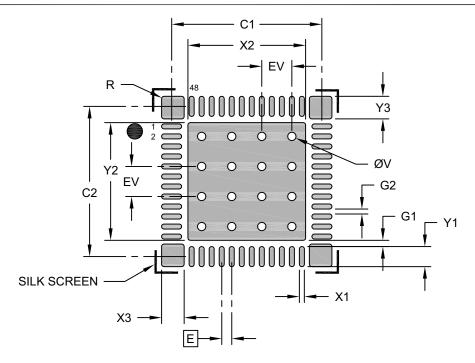

# 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M4) - 6x6 mm Body [UQFN] With Corner Anchors and 4.6x4.6 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

| Units                           |    | MILLIMETERS |      |      |

|---------------------------------|----|-------------|------|------|

| Dimension Limits                |    | MIN         | NOM  | MAX  |

| Contact Pitch                   | Е  | 0.40 BSC    |      |      |

| Center Pad Width                | X2 |             |      | 4.70 |

| Center Pad Length               | Y2 |             |      | 4.70 |

| Contact Pad Spacing             | C1 |             | 6.00 |      |

| Contact Pad Spacing             | C2 |             | 6.00 |      |

| Contact Pad Width (X48)         | X1 |             |      | 0.20 |

| Contact Pad Length (X48)        | Y1 |             |      | 0.80 |

| Corner Anchor Pad Width (X4)    | X3 |             |      | 0.90 |

| Corner Anchor Pad Length (X4)   | Y3 |             |      | 0.90 |

| Pad Corner Radius (X 20)        | R  |             |      | 0.10 |

| Contact Pad to Center Pad (X48) | G1 | 0.25        |      |      |

| Contact Pad to Contact Pad      | G2 | 0.20        |      |      |

| Thermal Via Diameter            | V  |             | 0.33 |      |

| Thermal Via Pitch               | EV |             | 1.20 |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2442A-M4

NOTES: