Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 29                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck64mp503t-i-m5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 4-12: SFR BLOCK B00h

| Register  | Address | All Resets        | Register  | Address | All Resets        | Register  | Address | All Resets        |

|-----------|---------|-------------------|-----------|---------|-------------------|-----------|---------|-------------------|

| ADC       |         |                   | ADCMP1LO  | B44     | 00000000000000000 | ADTRIG2H  | B8A     | 0000000000000000  |

| ADCON1L   | B00     | 000-00000000      | ADCMP1HI  | B46     | 00000000000000000 | ADTRIG3L  | B8C     | 00000000000000000 |

| ADCON1H   | B02     | 011               | ADCMP2ENL | B48     | 00000000000000000 | ADTRIG3H  | B8E     | 00000000000000000 |

| ADCON2L   | B04     | 00-0-00000000000  | ADCMP2ENH | B4A     | 0000000000        | ADTRIG4L  | B90     | 00000000000000000 |

| ADCON2H   | B06     | 00-0000000000000  | ADCMP2LO  | B4C     | 00000000000000000 | ADTRIG4H  | B92     | 00000000000000000 |

| ADCON3L   | B08     | 00000000000000000 | ADCMP2HI  | B4E     | 00000000000000000 | ADTRIG5L  | B94     | 00000000000000000 |

| ADCON3H   | B0A     | 00000000xx        | ADCMP3ENL | B50     | 00000000000000000 | ADTRIG5H  | B96     | 00000000000000000 |

| ADCON4L   | B0C     | xx                | ADCMP3ENH | B52     | 0000000000        | ADTRIG6L  | B98     | 00000000000000000 |

| ADCON4H   | B0E     | 000000            | ADCMP3LO  | B54     | 00000000000000000 | ADCMP0CON | BA0     | 00000000000000000 |

| ADMOD0L   | B10     | 00000000000000000 | ADCMP3HI  | B56     | 00000000000000000 | ADCMP1CON | BA4     | 00000000000000000 |

| ADMOD0H   | B12     | 00000000000000000 | ADFL0DAT  | B68     | 00000000000000000 | ADCMP2CON | BA8     | 00000000000000000 |

| ADMOD1L   | B14     | 00000000000000000 | ADFL0CON  | B6A     | xxx00000000000000 | ADCMP3CON | BAC     | 00000000000000000 |

| ADMOD1H   | B16     | 0000              | ADFL1DAT  | B6C     | 00000000000000000 | ADLVLTRGL | BD0     | 00000000000000000 |

| ADIEL     | B20     | xxxxxxxxxxxxx     | ADFL1CON  | B6E     | xxx00000000000000 | ADLVLTRGH | BD2     | xxxxxxxxx         |

| ADIEH     | B22     | xxxxxxxxx         | ADFL2DAT  | B70     | 00000000000000000 | ADCORE0L  | BD4     | 00000000000000000 |

| ADSTATL   | B30     | 00000000000000000 | ADFL2CON  | B72     | xxx00000000000000 | ADCORE0H  | BD6     | 0000001100000000  |

| ADSTATH   | B32     | 0000000000        | ADFL3DAT  | B74     | 00000000000000000 | ADCORE1L  | BD8     | 00000000000000000 |

| ADCMP0ENL | B38     | 00000000000000000 | ADFL3CON  | B76     | xxx00000000000000 | ADCORE1H  | BDA     | 0000001100000000  |

| ADCMP0ENH | ВЗА     | 0000000000        | ADTRIG0L  | B80     | 00000000000000000 | ADEIEL    | BF0     | xxxxxxxxxxxxx     |

| ADCMP0LO  | B3C     | 00000000000000000 | ADTRIG0H  | B82     | 00000000000000000 | ADEIEH    | BF2     | xxxxxxxxx         |

| ADCMP0HI  | B3E     | 0000000000000000  | ADTRIG1L  | B84     | 00000000000000000 | ADEISTATL | BF8     | xxxxxxxxxxxx      |

| ADCMP1ENL | B40     | 0000000000000000  | ADTRIG1H  | B86     | 00000000000000000 | ADEISTATH | BFA     | xxxxxxxxx         |

| ADCMP1ENH | B42     | 0000000000        | ADTRIG2L  | B88     | 00000000000000000 |           |         |                   |

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

#### 8.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Enable for PORTx register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs, other than VDD, by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

# 8.2 Configuring Analog and Digital Port Pins

The ANSELx registers control the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx registers have a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 8.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 8.3 PORT Control Registers

The following registers are in the PORT module:

- Register 8-1: ANSELx (one per port)

- Register 8-2: TRISx (one per port)

- Register 8-3: PORTx (one per port)

- Register 8-4: LATx (one per port)

- Register 8-5: ODCx (one per port)

- Register 8-6: CNPUx (one per port)

- Register 8-7: CNPDx (one per port)

- Register 8-8: CNCONx (one per port optional)

- Register 8-9: CNEN0x (one per port)

- Register 8-10: CNSTATx (one per port optional)

- Register 8-11: CNEN1x (one per port)

- Register 8-12: CNFx (one per port)

#### REGISTER 8-1: ANSELX: ANALOG SELECT FOR PORTX REGISTER

| R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1   | R/W-1 | R/W-1 | R/W-1 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | ANSEL | x<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-1 | R/W-1       | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | ANSELx<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 |             |       |       |       |       |       | bit 0 |  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **ANSELx<15:0>:** Analog Select for PORTx bits

- 1 = Analog input is enabled and digital input is disabled on the PORTx[n] pin

- 0 = Analog input is disabled and digital input is enabled on the PORTx[n] pin

TABLE 8-13: PPS INPUT CONTROL REGISTERS

| Register | Bit 15    | Bit 14    | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| RPCON    | _         | _         | _         | _         | IOLOCK    | _         | _         | _         | _         | _         | _         | _         | _         | _         | _         | _         |

| RPINR0   | INT1R7    | INT1R6    | INT1R5    | INT1R4    | INT1R3    | INT1R2    | INT1R1    | INT1R0    | _         | _         | _         | _         | _         | _         | _         | _         |

| RPINR1   | INT3R7    | INT3R6    | INT3R5    | INT3R4    | INT3R3    | INT3R2    | INT3R1    | INT3R0    | INT2R7    | INT2R6    | INT2R5    | INT2R4    | INT2R3    | INT2R2    | INT2R1    | INT2R0    |

| RPINR2   | T1CKR7    | T1CKR6    | T1CKR5    | T1CKR4    | T1CKR3    | T1CKR2    | T1CKR1    | T1CKR0    | _         | _         | _         | _         | _         | _         | _         | _         |

| RPINR3   | ICM1R7    | ICM1R6    | ICM1R5    | ICM1R4    | ICM1R3    | ICM1R2    | ICM1R1    | ICM1R0    | TCKI1R7   | TCKI1R6   | TCKI1R5   | TCKI1R4   | TCKI1R3   | TCKI1R2   | TCKI1R1   | TCKI1R0   |

| RPINR4   | ICM2R7    | ICM2R6    | ICM2R5    | ICM2R4    | ICM2R3    | ICM2R2    | ICM2R1    | ICM2R0    | TCKI2R7   | TCKI2R6   | TCKI2R5   | TCKI2R4   | TCKI2R3   | TCKI2R2   | TCKI2R1   | TCKI2R0   |

| RPINR5   | ICM3R7    | ICM3R6    | ICM3R5    | ICM3R4    | ICM3R3    | ICM3R2    | ICM3R1    | ICM3R0    | TCKI3R7   | TCKI3R6   | TCKI3R5   | TCKI3R4   | TCKI3R3   | TCKI3R2   | TCKI3R1   | TCKI3R0   |

| RPINR6   | ICM4R7    | ICM4R6    | ICM4R5    | ICM4R4    | ICM4R3    | ICM4R2    | ICM4R1    | ICM4R0    | TCKI4R7   | TCKI4R    | TCKI4R5   | TCKI4R4   | TCKI4R3   | TCKI4R2   | TCKI4R1   | TCKI4R0   |

| RPINR7   | ICM5R7    | ICM5R6    | ICM5R5    | ICM5R4    | ICM5R3    | ICM5R2    | ICM5R1    | ICM5R0    | TCKI5R7   | TCKI5R6   | TCKI5R5   | TCKI5R4   | TCKI5R3   | TCKI5R2   | TCKI5R1   | TCKI5R0   |

| RPINR8   | ICM6R7    | ICM6R6    | ICM6R5    | ICM6R4    | ICM6R3    | ICM6R2    | ICM6R1    | ICM6R0    | TCKI6R7   | TCKI6R6   | TCKI6R5   | TCKI6R4   | TCKI6R3   | TCKI6R2   | TCKI6R1   | TCKI6R0   |

| RPINR9   | ICM7R7    | ICM7R6    | ICM7R5    | ICM7R4    | ICM7R3    | ICM7R2    | ICM7R1    | ICM7R0    | TCKI7R7   | TCKI7R6   | TCKI7R5   | TCKI7R4   | TCKI7R3   | TCKI7R2   | TCKI7R1   | TCKI7R0   |

| RPINR10  | ICM8R7    | ICM8R6    | ICM8R5    | ICM8R4    | ICM8R3    | ICM8R2    | ICM8R1    | ICM8R0    | TCKI8R7   | TCKI8R6   | TCKI8R5   | TCKI8R4   | TCKI8R3   | TCKI8R2   | TCKI8R1   | TCKI8R0   |

| RPINR11  | OCFBR7    | OCFBR6    | OCFBR5    | OCFBR4    | OCFBR3    | OCFBR2    | OCFBR1    | OCFBR0    | OCFAR7    | OCFAR6    | OCFAR5    | OCFAR4    | OCFAR3    | OCFAR2    | OCFAR1    | OCFAR0    |

| RPINR12  | PCI9R7    | PCI9R6    | PCI9R5    | PCI9R4    | PCI9R3    | PCI9R2    | PCI9R1    | PCI9R0    | PCI8R7    | PCI8R6    | PCI8R5    | PCI8R4    | PCI8R3    | PCI8R2    | PCI8R1    | PCI8R0    |

| RPINR13  | PCI11R7   | PCI11R6   | PCI11R5   | PCI11R4   | PCI11R3   | PCI11R2   | PCI11R1   | PCI11R0   | PCI10R7   | PCI10R6   | PCI10R5   | PCI10R4   | PCI10R3   | PCI10R2   | PCI10R1   | PCI10R0   |

| RPINR14  | QEIB1R7   | QEIB1R6   | QEIB1R5   | QEIB1R4   | QEIB1R3   | QEIB1R2   | QEIB1R1   | QEIB1R0   | QEIA1R7   | QEIA1R6   | QEIA1R5   | QEIA1R4   | QEIA1R3   | QEIA1R2   | QEIA1R1   | QEIA1R0   |

| RPINR15  | QEIHOM1R7 | QEIHOM1R6 | QEIHOM1R5 | QEIHOM1R4 | QEIHOM1R3 | QEIHOM1R2 | QEIHOM1R1 | QEIHOM1R0 | QEINDX1R7 | QEINDX1R6 | QEINDX1R5 | QEINDX1R4 | QEINDX1R3 | QEINDX1R2 | QEINDX1R1 | QEINDX1R0 |

| RPINR16  | QEIB2R7   | QEIB2R6   | QEIB2R5   | QEIB2R4   | QEIB2R3   | QEIB2R2   | QEIB2R1   | QEIB2R0   | QEIA2R7   | QEIA2R6   | QEIA2R5   | QEIA2R4   | QEIA2R3   | QEIA2R2   | QEIA2R1   | QEIA2R0   |

| RPINR17  | QEIHOM2R7 | QEIHOM2R6 | QEIHOM2R5 | QEIHOM2R4 | QEIHOM2R3 | QEIHOM2R2 | QEIHOM2R1 | QEIHOM2R0 | QEINDX2R7 | QEINDX2R6 | QEINDX2R5 | QEINDX2R4 | QEINDX2R3 | QEINDX2R2 | QEINDX2R1 | QEINDX2R0 |

| RPINR18  | U1DSRR7   | U1DSRR6   | U1DSRR5   | U1DSRR4   | U1DSRR3   | U1DSRR2   | U1DSRR1   | U1DSRR0   | U1RXR7    | U1RXR6    | U1RXR5    | U1RXR4    | U1RXR3    | U1RXR2    | U1RXR1    | U1RXR0    |

| RPINR19  | U2DSRR7   | U2DSRR6   | U2DSRR5   | U2DSRR4   | U2DSRR3   | U2DSRR2   | U2DSRR1   | U2DSRR0   | U2RXR7    | U2RXR6    | U2RXR5    | U2RXR4    | U2RXR3    | U2RXR2    | U2RXR1    | U2RXR0    |

| RPINR20  | SCK1R7    | SCK1R6    | SCK1R5    | SCK1R4    | SCK1R3    | SCK1R2    | SCK1R1    | SCK1R0    | SDI1R7    | SDI1R6    | SDI1R5    | SDI1R4    | SDI1R3    | SDI1R2    | SDI1R1    | SDI1R0    |

| RPINR21  | REFOIR7   | REFOIR6   | REFOIR5   | REFOIR4   | REFOIR3   | REFOIR2   | REFOIR1   | REFOIR0   | SS1R7     | SS1R6     | SS1R5     | SS1R4     | SS1R3     | SS1R2     | SS1R1     | SS1R0     |

| RPINR22  | SCK2R7    | SCK2R6    | SCK2R5    | SCK2R4    | SCK2R3    | SCK2R2    | SCK2R1    | SCK2R0    | SDI2R7    | SDI2R6    | SDI2R5    | SDI2R4    | SDI2R3    | SDI2R2    | SDI2R1    | SDI2R0    |

| RPINR23  | _         | _         | _         | _         | _         | _         | _         | _         | SS2R7     | SS2R6     | SS2R5     | SS2R4     | SS2R3     | SS2R2     | SS2R1     | SS2R0     |

| RPINR26  | _         | _         | _         | _         | _         | _         | _         | _         | CAN1RXR7  | CAN1RXR6  | CAN1RXR5  | CAN1RXR4  | CAN1RXR3  | CAN1RXR2  | CAN1RXR1  | CAN1RXR0  |

| RPINR27  | U3DSRR7   | U3DSRR6   | U3DSRR5   | U3DSRR4   | U3DSRR3   | U3DSRR2   | U3DSRR1   | U3DSRR0   | U3RXR7    | U3RXR6    | U3RXR5    | U3RXR4    | U3RXR3    | U3RXR2    | U3RXR1    | U3RXR0    |

| RPINR29  | SCK3R7    | SCK3R6    | SCK3R5    | SCK3R4    | SCK3R3    | SCK3R2    | SCK3R1    | SCK3R0    | SDI3R7    | SDI3R6    | SDI3R5    | SDI3R4    | SDI3R3    | SDI3R2    | SDI3R1    | SDI3R0    |

| RPINR30  | _         | _         | _         | _         | _         | _         | _         | _         | SS3R7     | SS3R6     | SS3R5     | SS3R4     | SS3R3     | SS3R2     | SS3R1     | SS3R0     |

| RPINR32  | TCKI9R7   | TCKI9R6   | TCKI9R5   | TCKI9R4   | TCKI9R3   | TCKI9R2   | TCKI9R1   | TCKI9R0   | _         | _         | _         | _         | _         | _         | _         | _         |

| RPINR33  | _         | _         | _         | _         | _         | _         | _         | _         | ICM9R7    | ICM9R6    | ICM9R5    | ICM9R4    | ICM9R3    | ICM9R2    | ICM9R1    | ICM9R0    |

| RPINR37  | PCI17R7   | PCI17R6   | PCI17R5   | PCI17R4   | PCI17R3   | PCI17R2   | PCI17R1   | PCI17R0   | OCFCR7    | OCFCR6    | OCFCR5    | OCFCR4    | OCFCR3    | OCFCR2    | OCFCR1    | OCFCR0    |

| RPINR38  | _         | _         | _         | _         | _         | _         | _         | _         | PCI18R7   | PCI18R6   | PCI18R5   | PCI18R4   | PCI18R3   | PCI18R2   | PCI18R1   | PCI18R0   |

| RPINR42  | PCI13R7   | PCI13R6   | PCI13R5   | PCI13R4   | PCI13R3   | PCI13R2   | PCI13R1   | PCI13R0   | PCI12R7   | PCI12R6   | PCI12R5   | PCI12R4   | PCI12R3   | PCI12R2   | PCI12R1   | PCI12R0   |

| RPINR43  | PCI15R7   | PCI15R6   | PCI15R5   | PCI15R4   | PCI15R3   | PCI15R2   | PCI15R1   | PCI15R0   | PCI14R7   | PCI14R6   | PCI14R5   | PCI14R4   | PCI14R3   | PCI14R2   | PCI14R1   | PCI14R0   |

| RPINR44  | SENT1R7   | SENT1R6   | SENT1R5   | SENT1R4   | SENT1R3   | SENT1R2   | SENT1R1   | SENT1R0   | PCI16R7   | PCI16R6   | PCI16R5   | PCI16R4   | PCI16R3   | PCI16R2   | PCI16R1   | PCI16R0   |

| RPINR45  | CLCINAR7  | CLCINAR6  | CLCINAR5  | CLCINAR4  | CLCINAR3  | CLCINAR2  | CLCINAR1  | CLCINAR0  | SENT2R7   | SENT2R6   | SENT2R5   | SENT2R4   | SENT2R3   | SENT2R2   | SENT2R1   | SENT2R0   |

| RPINR46  | CLCINCR7  | CLCINCR6  | CLCINCR5  | CLCINCR4  | CLCINCR3  | CLCINCR2  | CLCINCR1  | CLCINCR0  | CLCINBR7  | CLCINBR6  | CLCINBR5  | CLCINBR4  | CLCINBR3  | CLCINBR2  | CLCINBR1  | CLCINBR0  |

| RPINR47  | ADCTRGR7  | ADCTRGR6  | ADCTRGR5  | ADCTRGR4  | ADCTRGR3  | ADCTRGR2  | ADCTRGR1  | ADCTRGR0  | CLCINDR7  | CLCINDR6  | CLCINDR5  | CLCINDR4  | CLCINDR3  | CLCINDR2  | CLCINDR1  | CLCINDR0  |

| RPINR48  | U1CTSR7   | U1CTSR6   | U1CTSR5   | U1CTSR4   | U1CTSR3   | U1CTSR2   | U1CTSR1   | U1CTSR0   | OCFDR7    | OCFDR6    | OCFDR5    | OCFDR4    | OCFDR3    | OCFDR2    | OCFDR1    | OCFDR0    |

| RPINR49  | U3CTSR7   | U3CTSR6   | U3CTSR5   | U3CTSR4   | U3CTSR3   | U3CTSR2   | U3CTSR1   | U3CTSR0   | U2CTSR7   | U2CTSR6   | U2CTSR5   | U2CTSR4   | U2CTSR3   | U2CTSR2   | U2CTSR1   | U2CTSR0   |

**NOTES:**

### REGISTER 11-19: C1RXOVIFH: CAN RECEIVE OVERFLOW INTERRUPT STATUS REGISTER HIGH<sup>(1)</sup>

| R-0    | R-0 | R-0 | R-0     | R-0     | R-0 | R-0 | R-0   |

|--------|-----|-----|---------|---------|-----|-----|-------|

|        |     |     | RFOVIF- | <31:24> |     |     |       |

| bit 15 |     |     |         |         |     |     | bit 8 |

| R-0   | R-0 | R-0 | R-0     | R-0     | R-0 | R-0 | R-0   |

|-------|-----|-----|---------|---------|-----|-----|-------|

|       |     |     | RFOVIF- | <23:16> |     |     |       |

| bit 7 |     |     |         |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 RFOVIF<31:16>: Unimplemented

Note 1: C1RXOVIFH: FIFO: RFOVIFx (flag needs to be cleared in the FIFO register).

#### REGISTER 11-20: C1RXOVIFL: CAN RECEIVE OVERFLOW INTERRUPT STATUS REGISTER LOW<sup>(1)</sup>

| R-0    | R-0 | R-0 | R-0    | R-0    | R-0 | R-0 | R-0   |

|--------|-----|-----|--------|--------|-----|-----|-------|

|        |     |     | RFOVIF | <15:8> |     |     |       |

| bit 15 |     |     |        |        |     |     | bit 8 |

| R-0   | R-0 | R-0 | R-0         | R-0 | R-0 | R-0 | U-0   |

|-------|-----|-----|-------------|-----|-----|-----|-------|

|       |     | 1   | RFOVIF<7:1> |     |     |     | _     |

| bit 7 |     |     |             |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **RFOVIF<15:8>:** Unimplemented

bit 7-1 Receive FIFO Overflow Interrupt Pending bits

1 = Interrupt is pending 0 = Interrupt is not pending

bit 0 **Unimplemented:** Read as '0'

Note 1: C1RXOVIFL: FIFO: RFOVIFx (flag needs to be cleared in the FIFO register).

#### REGISTER 11-30: C1TXQCONL: CAN TRANSMIT QUEUE CONTROL REGISTER LOW

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|--------|-------|-------|

| _      | _   | _   | _   | _   | FRESET | TXREQ | UINC  |

| bit 15 |     |     |     |     |        |       | bit 8 |

| R-0   | U-0 | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

|-------|-----|-----|--------|-----|--------|-----|--------|

| TXEN  | _   | _   | TXATIE | _   | TXQEIE | _   | TXQNIE |

| bit 7 |     |     |        |     |        |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10 FRESET: FIFO Reset bit

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset; user should poll

whether this bit is clear before taking any action

0 = No effect

bit 9 TXREQ: Message Send Request bit

1 = Requests sending a message; the bit will automatically clear when all the messages queued in

the TXQ are successfully sent

0 = Clearing the bit to '0' while set ('1') will request a message abort

bit 8 **UINC:** Increment Head/Tail bit

When this bit is set, the FIFO head will increment by a single message.

bit 7 TXEN: TX Enable bit

bit 6-5 **Unimplemented:** Read as '0'

bit 4 **TXATIE:** Transmit Attempts Exhausted Interrupt Enable bit

1 = Enables interrupt0 = Disables interrupt

bit 3 **Unimplemented:** Read as '0'

bit 2 **TXQEIE:** Transmit Queue Empty Interrupt Enable bit

1 = Interrupt is enabled for TXQ empty0 = Interrupt is disabled for TXQ empty

bit 1 **Unimplemented:** Read as '0'

bit 0 TXQNIE: Transmit Queue Not Full Interrupt Enable bit

1 = Interrupt is enabled for TXQ not full0 = Interrupt is disabled for TXQ not full

#### REGISTER 11-36: C1TEFCONL: CAN TRANSMIT EVENT FIFO CONTROL REGISTER LOW

| U-0    | U-0 | U-0 | U-0 | U-0 | S/HC-0 | U-0 | S/HC-0 |

|--------|-----|-----|-----|-----|--------|-----|--------|

| _      | _   | _   | _   | _   | FRESET | _   | UINC   |

| bit 15 |     |     |     |     |        |     | bit 8  |

| U-0   | U-0 | R/W-0                  | U-0 | R/W-0   | R/W-0  | R/W-0  | R/W-0   |

|-------|-----|------------------------|-----|---------|--------|--------|---------|

| _     | _   | TEFTSEN <sup>(1)</sup> | _   | TEFOVIE | TEFFIE | TEFHIE | TEFNEIE |

| bit 7 |     |                        |     |         |        |        | bit 0   |

| Legend:           | S = Settable bit | HC = Hardware Cleara  | ble bit                            |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15-11 | Unimplemented: Read as '0' |

|-----------|----------------------------|

| bit 10    | FRESET: FIFO Reset bit     |

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset; the user should poll

whether this bit is clear before taking any action

0 = No effect

bit 9 **Unimplemented:** Read as '0'

bit 8 **UINC:** Increment Tail bit

1 = When this bit is set, the FIFO tail will increment by a single message

0 = FIFO tail will not increment

bit 7-6 Unimplemented: Read as '0'

bit 5 **TEFTSEN:** Transmit Event FIFO Timestamp Enable bit<sup>(1)</sup>

1 = Timestamps elements in TEF

0 = Does not timestamp elements in TEF

bit 4 Unimplemented: Read as '0'

bit 3 **TEFOVIE:** Transmit Event FIFO Overflow Interrupt Enable bit

1 = Interrupt is enabled for overflow event0 = Interrupt is disabled for overflow event

bit 2 **TEFFIE:** Transmit Event FIFO Full Interrupt Enable bit

1 = Interrupt is enabled for FIFO full0 = Interrupt is disabled for FIFO full

bit 1 **TEFHIE:** Transmit Event FIFO Half Full Interrupt Enable bit

1 = Interrupt is enabled for FIFO half full 0 = Interrupt is disabled for FIFO half full

bit 0 **TEFNEIE:** Transmit Event FIFO Not Empty Interrupt Enable bit

1 = Interrupt is enabled for FIFO not empty0 = Interrupt is disabled for FIFO not empty

**Note 1:** These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

#### REGISTER 12-6: MPER: MASTER PERIOD REGISTER

| R/W-0                     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| MPER<15:8> <sup>(1)</sup> |       |       |       |       |       |       |       |  |

| bit 15                    |       |       |       |       |       |       |       |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| MPER<7:0>(1) |       |       |       |       |       |       |       |  |

| bit 7        |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR  $(1)^2$  = Bit is set  $(0)^2$  = Bit is cleared  $(0)^2$  = Bit is unknown

bit 15-0 MPER<15:0>: Master Period Register bits<sup>(1)</sup>

This register holds the period value that can be shared by multiple PWM Generators.

**Note 1:** Period values less than '0x0010' should not be used ('0x0080' in High-Resolution mode).

#### REGISTER 12-30: PGxDTL: PWM GENERATOR x DEAD-TIME REGISTER LOW

| U-0    | U-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|--------------------------|-------|-------|-------|-------|--|--|

| _      | _   |       | DTL<13:8> <sup>(1)</sup> |       |       |       |       |  |  |

| bit 15 |     |       |                          |       |       |       | bit 8 |  |  |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|--|

|       | DTL<7:0> |       |       |       |       |       |       |  |  |

| bit 7 |          |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTL<13:0>: PWMxL Dead-Time Delay bits<sup>(1)</sup>

**Note 1:** DTL<13:11> bits are not available when HREN (PGxCONL<7>) = 0.

#### REGISTER 12-31: PGxDTH: PWM GENERATOR x DEAD-TIME REGISTER HIGH

| U-0    | U-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|--------------------------|-------|-------|-------|-------|--|--|

| _      | _   |       | DTH<13:8> <sup>(1)</sup> |       |       |       |       |  |  |

| bit 15 |     |       |                          |       |       |       | bit 8 |  |  |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | DTH<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 |          |       |       |       |       |       | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 **DTH<13:0>:** PWMxH Dead-Time Delay bits<sup>(1)</sup>

Note 1: DTH<13:11> bits are not available when HREN (PGxCONL<7>) = 0.

#### REGISTER 13-11: ADCOREXL: DEDICATED ADC CORE x CONTROL REGISTER LOW (x = 0 TO 1)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0  |

|--------|-----|-----|-----|-----|-----|-------|--------|

| _      | _   | _   | _   | _   | _   | SAMO  | ><9:8> |

| bit 15 |     |     |     |     |     |       | bit 8  |

| R/W-0     | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-----------|-------|-------|-------|-------|-------|-------|--|--|

|           | SAMC<7:0> |       |       |       |       |       |       |  |  |

| bit 7 bit |           |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-0 **SAMC<9:0>:** Dedicated ADC Core x Conversion Delay Selection bits

These bits determine the time between the trigger event and the start of conversion in the number of the Core Clock Periods (TADCORE). During this time, the ADC Core x still continues sampling. This feature is enabled by the SAMCxEN bits in the ADCON4L register.

1111111111 = 1025 TADCORE

. . .

0000000001 = 3 TADCORE 00000000000 = 2 TADCORE

#### REGISTER 15-8: VELXCNT: VELOCITY x COUNTER REGISTER

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|

|        | VELCNT<15:8> |       |       |       |       |       |       |  |  |

| bit 15 |              |       |       |       |       |       | bit 8 |  |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| VELCNT<7:0> |       |       |       |       |       |       |       |

| bit 7       |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **VELCNT<15:0>:** Velocity Counter bits

#### REGISTER 15-9: VELxCNTH: VELOCITY x COUNTER REGISTER HIGH<sup>(1)</sup>

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| VELCNT<31:24> |       |       |       |       |       |       |       |

| bit 15        |       |       |       |       |       |       | bit 8 |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| VELCNT<23:16> |       |       |       |       |       |       |       |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **VELCNT<31:16>:** Velocity Counter bits

Note 1: This register is not present on all devices.

#### 20.3 Control Registers

#### REGISTER 20-1: SENTxCON1: SENTx CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0   | U-0 | R/W-0 | R/W-0              | R/W-0                | R/W-0 |

|--------|-----|---------|-----|-------|--------------------|----------------------|-------|

| SNTEN  | _   | SNTSIDL | _   | RCVEN | TXM <sup>(1)</sup> | TXPOL <sup>(1)</sup> | CRCEN |

| bit 15 |     | •       | •   |       |                    |                      | bit 8 |

| R/W-0 | R/W-0                | U-0 | R/W-0 | U-0 | R/W-0   | R/W-0   | R/W-0   |

|-------|----------------------|-----|-------|-----|---------|---------|---------|

| PPP   | SPCEN <sup>(2)</sup> | _   | PS    | _   | NIBCNT2 | NIBCNT1 | NIBCNT0 |

| bit 7 |                      |     |       |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 SNTEN: SENTx Enable bit

1 = SENTx is enabled

0 = SENTx is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SNTSIDL: SENTx Stop in Idle Mode bit

1 = Discontinues module operation when the device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 **Unimplemented:** Read as '0'

bit 11 RCVEN: SENTx Receive Enable bit

1 = SENTx operates as a receiver

0 = SENTx operates as a transmitter (sensor)

bit 10 **TXM:** SENTx Transmit Mode bit<sup>(1)</sup>

1 = SENTx transmits data frame only when triggered using the SYNCTXEN status bit

0 = SENTx transmits data frames continuously while SNTEN = 1

bit 9 **TXPOL:** SENTx Transmit Polarity bit<sup>(1)</sup>

1 = SENTx data output pin is low in the Idle state

0 = SENTx data output pin is high in the Idle state

bit 8 CRCEN: CRC Enable bit

Module in Receive Mode (RCVEN = 1):

1 = SENTx performs CRC verification on received data using the preferred J2716 method

0 = SENTx does not perform CRC verification on received data

Module in Transmit Mode (RCVEN = 1):

1 = SENTx automatically calculates CRC using the preferred J2716 method

0 = SENTx does not calculate CRC

bit 7 PPP: Pause Pulse Present bit

1 = SENTx is configured to transmit/receive SENT messages with pause pulse

0 = SENTx is configured to transmit/receive SENT messages without pause pulse

bit 6 SPCEN: Short PWM Code Enable bit<sup>(2)</sup>

1 = SPC control from external source is enabled

0 = SPC control from external source is disabled

bit 5 **Unimplemented:** Read as '0'

**Note 1:** This bit has no function in Receive mode (RCVEN = 1).

2: This bit has no function in Transmit mode (RCVEN = 0).

#### REGISTER 24-9: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGC0LIM<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15         |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGC0LIM<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits

This register is used to specify the loop count for the PTGJMPC0 Step command or as a Limit register for the General Purpose Counter 0.

**Note 1:** These bits are read-only when the module is executing Step commands.

### REGISTER 24-10: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGC1LIM<15:8> |       |       |       |       |       |       |       |  |

| bit 15         |       |       |       |       |       |       | bit 8 |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGC1LIM<7:0> |       |       |       |       |       |       |       |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 PTGC1LIM<15:0>: PTG Counter 1 Limit Register bits

This register is used to specify the loop count for the PTGJMPC1 Step command or as a Limit register for the General Purpose Counter 1.

**Note 1:** These bits are read-only when the module is executing step commands.

#### REGISTER 24-13: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------------|-------|-------|

| _     | _   | _   |       |       | PTGQPTR<4:0 | >     |       |

| bit 7 |     |     |       |       |             |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 PTGQPTR<4:0>: PTG Step Queue Pointer Register bits

This register points to the currently active Step command in the Step queue.

**Note 1:** These bits are read-only when the module is executing step commands.

#### REGISTER 24-14: PTGQUEn: PTG STEP QUEUE n POINTER REGISTER (n = 0-15)(1)

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|------------------------|-------|-------|-------|

|        |       |       | STEP2n+ | -1<7:0> <sup>(2)</sup> |       |       |       |

| bit 15 |       |       |         |                        |       |       | bit 8 |

| R/W-0                      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| STEP2n<7:0> <sup>(2)</sup> |       |       |       |       |       |       |       |  |  |

| bit 7                      |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **STEP2n+1<7:0>:** PTG Command 4n+1 bits<sup>(2)</sup>

A queue location for storage of the STEP2n+1 command byte, where 'n' is from PTGQUEn.

bit STEP2n<7:0>: PTG Command 4n+2 bits<sup>(2)</sup>

A queue location for storage of the STEP2n command byte, where 'n' are the odd numbered Step

Queue Pointers.

**Note 1:** These bits are read-only when the module is executing Step commands.

2: Refer to Table 24-1 for the Step command encoding.

#### REGISTER 29-3: PMD3: PERIPHERAL MODULE DISABLE 3 CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | PMPMD |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | U-0 | R/W-0  | U-0 | R/W-0 | R/W-0  | R/W-0  | U-0   |

|-------|-----|--------|-----|-------|--------|--------|-------|

| CRCMD | _   | QEI2MD | _   | U3MD  | I2C3MD | I2C2MD | _     |

| bit 7 |     |        |     |       |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 Unimplemented: Read as '0' bit 8 PMPMD: PMP Module Disable bit 1 = PMP module is disabled 0 = PMP module is enabled bit 7 **CRCMD:** CRC Module Disable bit 1 = CRC module is disabled 0 = CRC module is enabled bit 6 Unimplemented: Read as '0' bit 5 **QEI2MD:** QEI2 Module Disable bit 1 = QEI2 module is disabled 0 = QEI2 module is enabled bit 4 Unimplemented: Read as '0' bit 3 U3MD: UART3 Module Disable bit 1 = UART3 module is disabled 0 = UART3 module is enabled bit 2 I2C3MD: I2C3 Module Disable bit 1 = I2C3 module is disabled 0 = I2C3 module is enabled bit 1 I2C2MD: I2C2 Module Disable bit 1 = I2C2 module is disabled 0 = I2C2 module is enabled Unimplemented: Read as '0' bit 0

#### **REGISTER 30-13: FDMT CONFIGURATION REGISTER**

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   |     | _   |     |        |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | R/PO-1 |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | _   | _   | _   | _   | _   | _   | DMTDIS |

| bit 7 |     |     |     |     |     |     | bit 0  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-1 **Unimplemented:** Read as '1' bit 0 **DMTDIS:** DMT Disable bit

1 = DMT is disabled 0 = DMT is enabled

#### APPENDIX A: REVISION HISTORY

#### **Revision A (December 2017)**

This is the initial version of the document.

#### Revision B (May 2018)

This revision incorporates the following updates:

- · Sections:

- Updated Section 4.2.7 "BIST at Start-up", Section 4.2.8 "BIST at Run Time", Section 15.0 "Quadrature Encoder Interface (QEI)", Section 30.2 "Device Calibration and Identification", Section 30.10 "Code Protection and CodeGuard™ Security" and Section 34.1 "Package Marking Information".

- Added Section 5.3.2 "Error Correcting Code (ECC)" and Section 5.5.4 "ECC Control Registers".

- · Tables:

- Updated Table 4-3, Table 4-9, Table 7-2,

Table 7-3, Table 7-4, Table 8-7, Table 15-1,

Table 24-3, Table 30-3, Table 33-1,

Table 33-3, Table 33-5, Table 33-6 (was Table 33-9), Table 33-7 (was Table 33-11),

Table 33-22, Table 33-37 and Table 33-40.

- Deleted Table 33-6, Table 33-7, Table 33-8 and Table 33-10.

- Added Table 33-10, Table 33-11, Table 33-12 and Table 33-13.

- · Figures:

- Updated Figure 3-1, Figure 4-1, Figure 4-12, Figure 15-2, Figure 30-3 and Figure 30-4.

- · Registers:

- Updated Register 4-1, Register 14-1, Register 14-6, Register 14-7, Register 14-9, Register 15-1, Register 15-2, Register 15-3, Register 15-5, Register 15-6, Register 15-7, Register 15-9, Register 15-11, Register 15-17, Register 27-1, Register 27-2, Register 30-5 and Register 30-7.

- Added Register 5-6, Register 5-7, Register 5-8, Register 5-9, Register 5-10, Register 5-11, Register 15-18 and Register 15-19.

- Deleted Register 15-8, Register 15-12 and Register 15-20.

- · Examples:

- Updated Example 29-1.

- Added Example 29-2.

- · Equations:

- Deleted Equation 4-1.

**NOTES:**

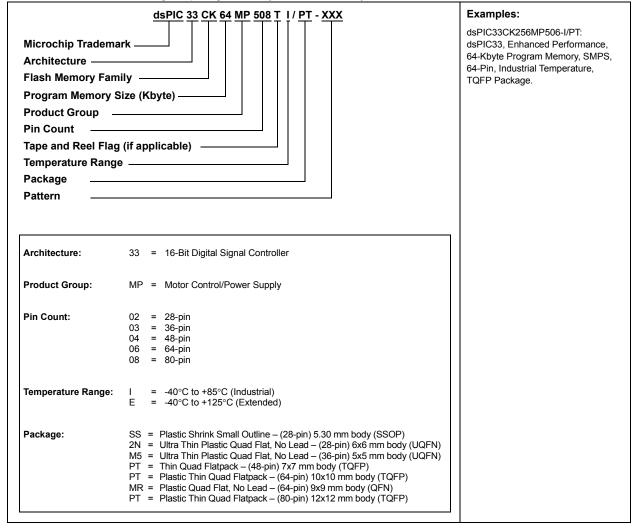

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

**NOTES:**