Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Dectano                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 100MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x12b; D/A 3x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

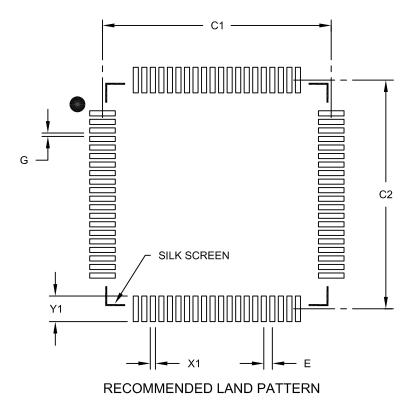

| Mounting Type              | Surface Mount                                                                    |

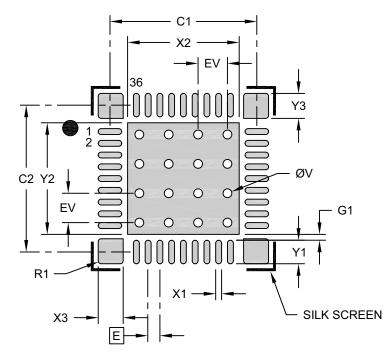

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ck64mp506t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register  | Address | All Resets                              | Register  | Address | All Resets         | Register  | Address | All Resets                              |

|-----------|---------|-----------------------------------------|-----------|---------|--------------------|-----------|---------|-----------------------------------------|

| CAN       |         |                                         | C1TSCONL  | 5D4     | 0000000000         | C1RXOVIFH | 5EA     | 000000000000000000000000000000000000000 |

| C1CONL    | 5C0     | 00011101100000                          | C1TSCONH  | 5D6     | 000                | C1TXATIFL | 5EC     | 000000000000000000000000000000000000000 |

| C1CONH    | 5C2     | 0000010010011000                        | C1VECL    | 5D8     | 00000-1000000      | C1TXATIFH | 5EE     | 000000000000000000000000000000000000000 |

| C1NBTCFGL | 5C4     | 00001111-0001111                        | C1VECH    | 5DA     | 11000000-1000000   | C1TXREQL  | 5F0     | 000000000000000000000000000000000000000 |

| C1NBTCFGH | 5C6     | 000000000111110                         | C1INTL    | 5DC     | 000000000000       | C1TXREQH  | 5F2     | 000000000000000000000000000000000000000 |

| C1DBTCFGL | 5C8     | 00110011                                | C1INTH    | 5DE     | 000000000000       | C1TRECL   | 5F4     | 000000000000000000000000000000000000000 |

| C1DBTCFGH | 5CA     | 000000001110                            | C1RXIFL   | 5E0     | 000000000000000000 | C1TRECH   | 5F6     | 100000                                  |

| C1TDCL    | 5CC     | 00010000000000                          | C1RXIFH   | 5E2     | 000000000000000000 | C1BDIAG0L | 5F8     | 000000000000000000000000000000000000000 |

| C1TDCH    | 5CE     | 10                                      | C1TXIFL   | 5E4     | 0000000000000000-  | C1BDIAG0H | 5FA     | 000000000000000000000000000000000000000 |

| C1TBCL    | 5D0     | 000000000000000000                      | C1TXIFH   | 5E6     | 000000000000000000 | C1BDIAG1L | 5FC     | 000000000000000000000000000000000000000 |

| C1TBCH    | 5D2     | 000000000000000000000000000000000000000 | C1RXOVIFL | 5E8     | 0000000000000000-  | C1BDIAG1H | 5FE     | 00000-000-000000                        |

#### TABLE 4-7: SFR BLOCK 500h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

| Register      | Address | All Resets                              | Register    | Address | All Resets                              | Register    | Address | All Resets                              |

|---------------|---------|-----------------------------------------|-------------|---------|-----------------------------------------|-------------|---------|-----------------------------------------|

| CAN (Continue | d)      |                                         | C1FIFOSTA6  | 65C     | 000000000000000000000000000000000000    | C1FLTOBJ6L  | 6B0     | 000000000000000000000000000000000000000 |

| C1TEFCONL     | 600     | 1-00000                                 | C1FIFOUA6L  | 660     | *****                                   | C1FLTOBJ6H  | 6B2     | 000000000000000000000000000000000000000 |

| C1TEFCONH     | 602     | 00000                                   | C1FIFOUA6H  | 662     | *****                                   | C1MASK6L    | 6B4     | 000000000000000000000000000000000000000 |

| C1TEFSTA      | 604     | 0000                                    | C1FIFOCON7L | 664     | 100x000000                              | C1MASK6H    | 6B6     | 000000000000000000000000000000000000000 |

| C1TEFUAL      | 608     | *****                                   | C1FIFOCON7H | 666     | 0000000-1100000                         | C1FLTOBJ7L  | 7B8     | 000000000000000000000000000000000000000 |

| C1TEFUAH      | 60A     | *****                                   | C1FIFOSTA7  | 668     | 00000000000000000                       | C1FLTOBJ7H  | 6BA     | 000000000000000000000000000000000000000 |

| C1FIFOBAL     | 60C     | 000000000000000000000000000000000000000 | C1FIFOUA7L  | 66C     | *****                                   | C1MASK7L    | 6BC     | 000000000000000000000000000000000000000 |

| C1FIFOBAH     | 60E     | 000000000000000000000000000000000000000 | C1FIFOUA7H  | 66E     | *****                                   | C1MASK7H    | 6BE     | 000000000000000000000000000000000000000 |

| C1TXQCONL     | 610     | 100x000000                              | C1FLTCON0L  | 670     | 00000000000                             | C1FLTOBJ8L  | 6C0     | 000000000000000000000000000000000000000 |

| C1TXQCONH     | 612     | 0000000-1100000                         | C1FLTCON0H  | 672     | 00000000000                             | C1FLTOBJ8H  | 6C2     | 000000000000000000000000000000000000000 |

| C1TXQSTA      | 614     | 00000000-0-0                            | C1FLTCON1L  | 674     | 00000000000                             | C1MASK8L    | 6C4     | 000000000000000000000000000000000000000 |

| C1TXQUAL      | 618     | *****                                   | C1FLTCON1H  | 676     | 00000000000                             | C1MASK8H    | 6C6     | 000000000000000000000000000000000000000 |

| C1TXQUAH      | 61A     | *****                                   | C1FLTCON2L  | 678     | 00000000000                             | C1FLTOBJ9L  | 6C8     | 000000000000000000000000000000000000000 |

| C1FIFOCON1L   | 61C     | 100x000000                              | C1FLTCON2H  | 67A     | 00000000000                             | C1FLTOBJ9H  | 6CA     | 000000000000000000000000000000000000000 |

| C1FIFOCON1H   | 61E     | 0000000-1100000                         | C1FLTCON3L  | 67C     | 00000000000                             | C1MASK9L    | 6CC     | 000000000000000000000000000000000000000 |

| C1FIFOSTA1    | 620     | 0000000000000000                        | C1FLTCON3H  | 67E     | 00000000000                             | C1MASK9H    | 6CE     | 000000000000000000000000000000000000000 |

| C1FIFOUA1L    | 624     | *****                                   | C1FLTOBJ0L  | 680     | 000000000000000000000000000000000000000 | C1FLTOBJ10L | 6D0     | 000000000000000000000000000000000000000 |

| C1FIFOUA1H    | 626     | *****                                   | C1FLTOBJ0H  | 682     | 000000000000000000000000000000000000000 | C1FLTOBJ10H | 6D2     | 000000000000000000000000000000000000000 |

| C1FIFOCON2L   | 628     | 100x000000                              | C1MASK0L    | 684     | 000000000000000000000000000000000000000 | C1MASK10L   | 6D4     | 000000000000000000000000000000000000000 |

| C1FIFOCON2H   | 62A     | 0000000-1100000                         | C1MASK0H    | 686     | 000000000000000000000000000000000000000 | C1MASK10H   | 6D6     | 000000000000000000000000000000000000000 |

| C1FIFOSTA2    | 62C     | 0000000000000000                        | C1FLTOBJ1L  | 688     | 000000000000000000000000000000000000000 | C1FLTOBJ11L | 6D8     | 000000000000000000000000000000000000000 |

| C1FIFOUA2L    | 630     | *****                                   | C1FLTOBJ1H  | 68A     | 000000000000000000000000000000000000000 | C1FLTOBJ11H | 6DA     | 000000000000000000000000000000000000000 |

| C1FIFOUA2H    | 632     | *****                                   | C1MASK1L    | 68C     | 000000000000000000000000000000000000000 | C1MASK11L   | 6DC     | 000000000000000000000000000000000000000 |

| C1FIFOCON3L   | 634     | 100x000000                              | C1MASK1H    | 68E     | 000000000000000000000000000000000000000 | C1MASK11H   | 6DE     | 000000000000000000000000000000000000000 |

| C1FIFOCON3H   | 636     | 0000000-1100000                         | C1FLTOBJ2L  | 690     | 000000000000000000000000000000000000000 | C1FLTOBJ12L | 6E0     | 000000000000000000000000000000000000000 |

| C1FIFOSTA3    | 638     | 0000000000000000                        | C1FLTOBJ2H  | 692     | 000000000000000000000000000000000000000 | C1FLTOBJ12H | 6E2     | 000000000000000000000000000000000000000 |

| C1FIFOUA3L    | 63C     | *****                                   | C1MASK2L    | 694     | 000000000000000000000000000000000000000 | C1MASK12L   | 6E4     | 000000000000000000000000000000000000000 |

| C1FIFOUA3H    | 63E     | *****                                   | C1MASK2H    | 696     | 000000000000000000000000000000000000000 | C1MASK12H   | 6E6     | 000000000000000000000000000000000000000 |

| C1FIFOCON4L   | 640     | 100x000000                              | C1FLTOBJ3L  | 698     | 000000000000000000000000000000000000000 | C1FLTOBJ13L | 6E8     | 000000000000000000000000000000000000000 |

| C1FIFOCON4H   | 642     | 0000000-1100000                         | C1FLTOBJ3H  | 69A     | 000000000000000000000000000000000000000 | C1FLTOBJ13H | 6EA     | 000000000000000000000000000000000000000 |

| C1FIFOSTA4    | 644     | 000000000000000                         | C1MASK3L    | 69C     | 000000000000000000000000000000000000000 | C1MASK13L   | 6EC     | 000000000000000000000000000000000000000 |

| C1FIFOUA4L    | 648     | *****                                   | C1MASK3H    | 69C     | 000000000000000000000000000000000000000 | C1MASK13H   | 6EE     | 000000000000000000000000000000000000000 |

| C1FIFOUA4H    | 64A     | *****                                   | C1FLTOBJ4L  | 6A0     | 000000000000000000000000000000000000000 | C1FLTOBJ14L | 6F0     | 000000000000000000000000000000000000000 |

| C1FIFOCON5L   | 64C     | 100x000000                              | C1FLTOBJ4H  | 6A2     | 000000000000000000000000000000000000000 | C1FLTOBJ14H | 6F2     | 000000000000000000000000000000000000000 |

| C1FIFOCON5H   | 64E     | 0000000-1100000                         | C1MASK4L    | 6A4     | 000000000000000000000000000000000000000 | C1MASK14L   | 6F4     | 000000000000000000000000000000000000000 |

| C1FIFOSTA5    | 650     | 0000000000000000                        | C1MASK4H    | 6A6     | 000000000000000000000000000000000000000 | C1MASK14H   | 6F6     | 000000000000000000000000000000000000000 |

| C1FIFOUA5L    | 654     | *****                                   | C1FLTOBJ5L  | 6A8     | 000000000000000000000000000000000000000 | C1FLTOBJ15L | 6F8     | 000000000000000000000000000000000000000 |

| C1FIFOUA5H    | 656     | *****                                   | C1FLTOBJ5H  | 6AA     | 000000000000000000000000000000000000000 | C1FLTOBJ15H | 6FA     | 000000000000000000000000000000000000000 |

| C1FIFOCON6L   | 658     | 100x000000                              | C1MASK5L    | 6AC     | 000000000000000000000000000000000000000 | C1MASK15L   | 6FC     | 000000000000000000000000000000000000000 |

| C1FIFOCON6H   | 65A     | 0000000-1100000                         | C1MASK5H    | 6AE     | 000000000000000000000000000000000000000 | C1MASK15H   | 6FE     | 000000000000000000000000000000000000000 |

#### TABLE 4-8:SFR BLOCK 600h

Legend: x = unknown or indeterminate value; "-" = unimplemented bits. Address values are in hexadecimal. Reset values are in binary.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Dual Partition Flash Program Memory" (DS70005156) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- **2:** Some registers and associated bits described in this section may not be available on all devices.

The dsPIC33CK256MP508 family devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33CK256MP508 family device to be serially programmed while in the end application circuit. This is done with a Programming Clock and Programming Data (PGCx/PGDx) line, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the Program Executive, to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data with a single program memory word and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

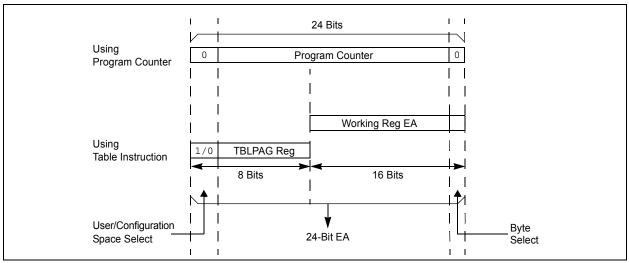

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1. The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes. The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

## 5.2 RTSP Operation

The dsPIC33CK256MP508 family Flash program memory array is organized into rows of 128 instructions or 384 bytes. RTSP allows the user application to erase a single page (8 rows or 1024 instructions) of memory at a time and to program one row at a time. It is possible to program two instructions at a time as well.

The page erase and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 3072 bytes and 384 bytes, respectively. Table 33-18 in **Section 33.0 "Electrical Characteristics"** lists the typical erase and programming times.

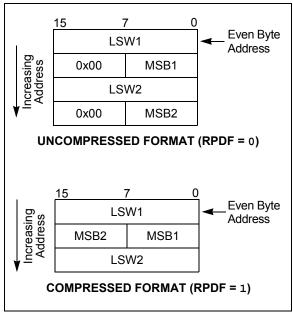

Row programming is performed by loading 384 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADRL/H register. Once the write has been initiated, the device will automatically load the write latches, and increment the NVMSRCADRL/H and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. Refer to Figure 4-1 through Figure 4-5 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation. For example, when performing Flash write operations on the Inactive Partition in Dual Partition mode, where the CPU remains running, it is necessary to wait for the NVM interrupt before programming the next block of Flash program memory.

#### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of Program Flash Memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

## 8.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33CK256MP508 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports with Edge Detect" (DS70005322) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. The PORT registers are located in the SFR.

Some of the key features of the I/O ports are:

- · Individual Output Pin Open-Drain Enable/Disable

- Individual Input Pin Weak Pull-up and Pull-Down

- Monitor Selective Inputs and Generate Interrupt when Change in Pin State is Detected

- Operation during Sleep and Idle modes

## 8.1 Parallel I/O (PIO) Ports

All port pins have 12 registers directly associated with their operation as digital I/Os. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input.

All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch. Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. Table 8-1 shows the pin availability. Table 8-2 shows the 5V input tolerant pins across this device.

## dsPIC33CK256MP508 FAMILY

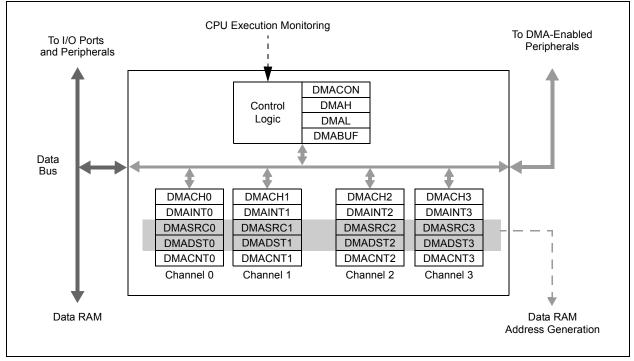

## FIGURE 10-1: DMA FUNCTIONAL BLOCK DIAGRAM

## 10.1 Summary of DMA Operations

The DMA Controller is capable of moving data between addresses according to a number of different parameters. Each of these parameters can be independently configured for any transaction. In addition, any or all of the DMA channels can independently perform a different transaction at the same time. Transactions are classified by these parameters:

- · Source and destination (SFRs and data RAM)

- Data size (byte or word)

- Trigger source

- Transfer mode (One-Shot, Repeated or Continuous)

- Addressing modes (Fixed Address or Address Blocks with or without Address Increment/Decrement)

In addition, the DMA Controller provides channel priority arbitration for all channels.

#### 10.1.1 SOURCE AND DESTINATION

Using the DMA Controller, data may be moved between any two addresses in the Data Space. The SFR space (0000h to 0FFFh) or the data RAM space (1000h to 4FFFh) can serve as either the source or the destination. Data can be moved between these areas in either direction or between addresses in either area. The four different combinations are shown in Figure 10-2.

If it is necessary to protect areas of data RAM, the DMA Controller allows the user to set upper and lower address boundaries for operations in the Data Space above the SFR space. The boundaries are set by the DMAH and DMAL Limit registers. If a DMA channel attempts an operation outside of the address boundaries, the transaction is terminated and an interrupt is generated.

#### 10.1.2 DATA SIZE

The DMA Controller can handle both 8-bit and 16-bit transactions. Size is user-selectable using the SIZE bit (DMACHn<1>). By default, each channel is configured for word-size transactions. When byte-size transactions are chosen, the LSB of the source and/or destination address determines if the data represents the upper or lower byte of the data RAM location.

#### 10.1.3 TRIGGER SOURCE

The DMA Controller can use 82 of the device's interrupt sources to initiate a transaction. The DMA trigger sources occur in reverse order from their natural interrupt priority and are shown in Table 10-1. Since the source and destination addresses for any transaction can be programmed independently of the trigger source, the DMA Controller can use any trigger to perform an operation on any peripheral. This also allows DMA channels to be cascaded to perform more complex transfer operations.

#### 10.1.4 TRANSFER MODE

The DMA Controller supports four types of data transfers, based on the volume of data to be moved for each trigger.

- One-Shot: A single transaction occurs for each trigger.

- Continuous: A series of back-to-back transactions occur for each trigger; the number of transactions is determined by the DMACNTn transaction counter.

- Repeated One-Shot: A single transaction is performed repeatedly, once per trigger, until the DMA channel is disabled.

- Repeated Continuous: A series of transactions are performed repeatedly, one cycle per trigger, until the DMA channel is disabled.

All transfer modes allow the option to have the source and destination addresses, and counter value, automatically reloaded after the completion of a transaction.

#### 10.1.5 ADDRESSING MODES

The DMA Controller also supports transfers between single addresses or address ranges. The four basic options are:

- Fixed-to-Fixed: Between two constant addresses

- Fixed-to-Block: From a constant source address to a range of destination addresses

- Block-to-Fixed: From a range of source addresses to a single, constant destination address

- Block-to-Block: From a range of source addresses to a range of destination addresses

The option to select auto-increment or auto-decrement of source and/or destination addresses is available for Block Addressing modes.

In addition to the four basic modes, the DMA Controller also supports Peripheral Indirect Addressing (PIA) mode, where the source or destination address is generated jointly by the DMA Controller and a PIA-capable peripheral. When enabled, the DMA channel provides a base source and/or destination address, while the peripheral provides a fixed range offset address.

## **REGISTER 11-5:** C1DBTCFGH: CAN DATA BIT TIME CONFIGURATION REGISTER HIGH<sup>(1)</sup>

| R/W-0         | R/W-0              | R/W-0            | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------|------------------|---------------|------------------|------------------|-----------------|--------|

| 1000-0        | 10,00-0            | 10.00-0          | BRP<          |                  | 1000-0           | 1000-0          | 1000-0 |

|               |                    |                  | DRPS          | -7.0-            |                  |                 |        |

| bit 15        |                    |                  |               |                  |                  |                 | bit 8  |

| U-0           | U-0                | U-0              | R/W-0         | R/W-1            | R/W-1            | R/W-1           | R/W-0  |

| _             | _                  | _                |               |                  | TSEG1<4:0>       |                 | -      |

| bit 7         |                    |                  |               |                  |                  |                 | bit 0  |

|               |                    |                  |               |                  |                  |                 |        |

| Legend:       |                    |                  |               |                  |                  |                 |        |

| R = Readabl   | le bit             | W = Writable bi  | t             | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | t POR              | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| <u></u>       |                    |                  |               |                  |                  |                 |        |

| bit 15-8      | BRP<7:0>: E        | Baud Rate Presca | aler bits     |                  |                  |                 |        |

|               | 1111 1111          | = TQ = 256/Fsys  |               |                  |                  |                 |        |

|               |                    |                  |               |                  |                  |                 |        |

|               | 0000 0000          | = TQ = 1/Fsys    |               |                  |                  |                 |        |

| bit 7-5       | Unimplemer         | ted: Read as '0' |               |                  |                  |                 |        |

| bit 4-0       | TSEG1<4:0>         | : Time Segment   | 1 bits (Propa | gation Segmei    | nt + Phase Seg   | ment 1)         |        |

|               | 1 1111 <b>= Le</b> | ngth is 32 x To  |               |                  |                  |                 |        |

|               |                    | •                |               |                  |                  |                 |        |

|               | 0 0000 <b>= Le</b> | ngth is 1 x TQ   |               |                  |                  |                 |        |

**Note 1:** This register can only be modified in Configuration mode (OPMOD<2:0> = 100).

#### REGISTER 11-6: C1DBTCFGL: CAN DATA BIT TIME CONFIGURATION REGISTER LOW<sup>(1)</sup>

| U-0           | U-0         | U-0                               | U-0          | R/W-0             | R/W-0           | R/W-1           | R/W-1 |

|---------------|-------------|-----------------------------------|--------------|-------------------|-----------------|-----------------|-------|

| _             | _           | _                                 |              |                   | TSEG            | 2<3:0>          |       |

| bit 15        |             |                                   |              |                   |                 |                 | bit 8 |

| U-0           | U-0         | U-0                               | U-0          | R/W-0             | R/W-0           | R/W-1           | R/W-1 |

| _             | -           | -                                 | _            |                   | -               | <3:0>           |       |

| bit 7         |             | •                                 |              |                   |                 |                 | bit 0 |

|               |             |                                   |              |                   |                 |                 |       |

| Legend:       |             |                                   |              |                   |                 |                 |       |

| R = Readable  | e bit       | W = Writable bit                  | t            | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at | POR         | '1' = Bit is set                  |              | '0' = Bit is clea | ared            | x = Bit is unki | nown  |

| bit 15-12     | Unimplemen  | ted: Read as '0'                  |              |                   |                 |                 |       |

| bit 11-8      | TSEG2<3:0>  | : Time Segment                    | 2 bits (Phas | se Segment 2)     |                 |                 |       |

|               | 1111 = Leng | •                                 |              |                   |                 |                 |       |

|               |             |                                   |              |                   |                 |                 |       |

|               |             |                                   |              |                   |                 |                 |       |

|               | 0000 = Leng | th is 1 x TQ                      |              |                   |                 |                 |       |

| bit 7-4       | 0           | th is 1 x TQ<br>Ited: Read as '0' |              |                   |                 |                 |       |

1111 = Length is 16 x To

0000 = Length is 1 x TQ

**Note 1:** This register can only be modified in Configuration mode (OPMOD<2:0> = 100).

#### REGISTER 11-34: C1FIFOSTAX: CAN FIFO STATUS REGISTER x (x = 1 TO 7) (CONTINUED)

| bit 2   | TFERFFIF: Transmit/Receive FIFO Empty/Full Interrupt Flag bit                                  |

|---------|------------------------------------------------------------------------------------------------|

|         | TXEN = 1 (FIFO configured as a transmit FIFO):                                                 |

|         | Transmit FIFO Empty Interrupt Flag                                                             |

|         | 1 = FIFO is empty                                                                              |

|         | 0 = FIFO is not empty, at least 1 message is queued to be transmitted                          |

|         | TXEN = 0 (FIFO configured as a receive FIFO):                                                  |

|         | Receive FIFO Full Interrupt Flag                                                               |

|         | 1 = FIFO is full                                                                               |

|         | 0 = FIFO is not full                                                                           |

| bit 1   | TFHRFHIF: Transmit/Receive FIFO Half Empty/Half Full Interrupt Flag bit                        |

|         | TXEN = 1 (FIFO configured as a transmit FIFO):                                                 |

|         | Transmit FIFO Half Empty Interrupt Flag                                                        |

|         | 1 = FIFO is ≤ half full                                                                        |

|         | 0 = FIFO is > half full                                                                        |

|         | TXEN = 0 (FIFO configured as a receive FIFO):                                                  |

|         | Receive FIFO Half Full Interrupt Flag<br>1 = FIFO is > half full                               |

|         | 0 = FIFO is < half full                                                                        |

| bit 0   |                                                                                                |

|         | <b>TFNRFNIF:</b> Transmit/Receive FIFO Not Full/Not Empty Interrupt Flag bit                   |

|         | <u>TXEN = 1 (FIFO configured as a transmit FIFO):</u><br>Transmit FIFO Not Full Interrupt Flag |

|         | 1 = FIFO is not full                                                                           |

|         | 0 = FIFO is full                                                                               |

|         | TXEN = 0 (FIFO configured as a receive FIFO):                                                  |

|         | Receive FIFO Not Empty Interrupt Flag                                                          |

|         | 1 = FIFO is not empty, has at least 1 message                                                  |

|         | 0 = FIFO is empty                                                                              |

| Noto 1: | EIEOCICION gives a zero indexed value to the message in the EIEO. If the EIEO is 4 messages    |

- Note 1: FIFOCI<4:0> gives a zero-indexed value to the message in the FIFO. If the FIFO is 4 messages deep (FSIZE<4:0> = 3), FIFOCIx will take on a value of 0 to 3, depending on the state of the FIFO.

- 2: These bits are updated when a message completes (or aborts) or when the FIFO is reset.

- **3:** This bit is reset on any read of this register or when the TXQ is reset. The bits are cleared when TXREQ is set or using an SPI write.

#### REGISTER 11-46: C1BDIAG0H: CAN BUS DIAGNOSTICS REGISTER 0 HIGH

| R/W-0           | R/W-0          | R/W-0            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|-----------------|----------------|------------------|------------------|-------------------|-----------------|-----------------|----------------|

|                 |                |                  | DTERF            | RCNT<7:0>         |                 |                 |                |

| bit 15          |                |                  |                  |                   |                 |                 | bit 8          |

| DAMA            | <b>D</b> 444 0 | <b>D</b> 444 0   | <b>D</b> # 4 / 0 |                   | <b>D</b> (14) 0 | <b>D</b> #44 0  | <b>D</b> 444 0 |

| R/W-0           | R/W-0          | R/W-0            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|                 |                |                  | DRERF            | RCNT<7:0>         |                 |                 |                |

| bit 7           |                |                  |                  |                   |                 |                 | bit 0          |

| Legend:         |                |                  |                  |                   |                 |                 |                |

| R = Readable    | bit            | W = Writable bit |                  | U = Unimpleme     | ented bit, rea  | ad as '0'       |                |

| -n = Value at I | POR            | '1' = Bit is set |                  | '0' = Bit is clea | red             | x = Bit is unki | nown           |

| bit 15-8 | DTERRCNT<7:0>: Data Bit Rate Transmit Error Counter bits |

|----------|----------------------------------------------------------|

|          |                                                          |

bit 7-0 DRERRCNT<7:0>: Data Bit Rate Receive Error Counter bits

#### REGISTER 11-47: C1BDIAG0L: CAN BUS DIAGNOSTICS REGISTER 0 LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | NTERF | RCNT<7:0>         |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | NRERF | RCNT<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-8 NTERRCNT<7:0>: Nominal Bit Rate Transmit Error Counter bits

bit 7-0 NRERRCNT<7:0>: Nominal Bit Rate Receive Error Counter bits

|                    | R/W-0                                                                                                                                                       | R/W-0                                                                                                                                                                                     | R/W-0                                                                                                                                                   | R/W-0                                                                                                                                                     | R/W-0                                                                                               | R/W-0             | R/W-0              |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------|--------------------|--|--|

| CLMOD              | SWAP                                                                                                                                                        | OVRENH                                                                                                                                                                                    | OVRENL                                                                                                                                                  | OVRDAT1                                                                                                                                                   | OVRDAT0                                                                                             | OSYNC1            | OSYNC0             |  |  |

| bit 15             | •                                                                                                                                                           | ·                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     | •                 | bit 8              |  |  |

| R/W-0              | R/W-0                                                                                                                                                       | R/W-0                                                                                                                                                                                     | R/W-0                                                                                                                                                   | R/W-0                                                                                                                                                     | R/W-0                                                                                               | R/W-0             | R/W-0              |  |  |

| FLTDAT1            | FLTDAT0                                                                                                                                                     | CLDAT1                                                                                                                                                                                    | CLDAT0                                                                                                                                                  | FFDAT1                                                                                                                                                    | FFDAT0                                                                                              | DBDAT1            | DBDAT0             |  |  |

| bit 7              |                                                                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     |                   | bit 0              |  |  |

| Legend:            |                                                                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     |                   |                    |  |  |

| R = Reada          | ble bit                                                                                                                                                     | W = Writable I                                                                                                                                                                            | bit                                                                                                                                                     | U = Unimplem                                                                                                                                              | nented bit, read a                                                                                  | s '0'             |                    |  |  |

| -n = Value         | at POR                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                          |                                                                                                                                                         | '0' = Bit is clea                                                                                                                                         | ared                                                                                                | x = Bit is unkno  | own                |  |  |

| L:4 4 F            |                                                                                                                                                             | vent Linsit Med                                                                                                                                                                           | e Celesthit                                                                                                                                             |                                                                                                                                                           |                                                                                                     |                   |                    |  |  |

| bit 15             |                                                                                                                                                             | rent-Limit Mod                                                                                                                                                                            |                                                                                                                                                         |                                                                                                                                                           | WMxL output sig                                                                                     | nala ara invarta  | d (bit flipping)   |  |  |

|                    |                                                                                                                                                             | CLDAT<1:0> b                                                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     | nais are inverte  | u (bit ilippilig), |  |  |

|                    | 0 = If PCI cu                                                                                                                                               | rrent limit is ac                                                                                                                                                                         | tive, then the (                                                                                                                                        | CLDAT<1:0> bit                                                                                                                                            | s define the PWN                                                                                    | /I output levels  |                    |  |  |

| bit 14             | SWAP: Swap                                                                                                                                                  | PWM Signals                                                                                                                                                                               | to PWMxH ar                                                                                                                                             | nd PWMxL Devi                                                                                                                                             | ice Pins bit                                                                                        |                   |                    |  |  |

|                    |                                                                                                                                                             | •                                                                                                                                                                                         |                                                                                                                                                         | OWMxL pin and<br>r respective pin                                                                                                                         | the PWMxL signal<br>s                                                                               | is connected to t | he PWMxH pin       |  |  |

| bit 13             | OVRENH: Us                                                                                                                                                  | er Override Er                                                                                                                                                                            | hable for PWN                                                                                                                                           | IxH Pin bit                                                                                                                                               |                                                                                                     |                   |                    |  |  |

|                    |                                                                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                         | n the PWMxH p                                                                                                                                             | in                                                                                                  |                   |                    |  |  |

|                    |                                                                                                                                                             | enerator provid                                                                                                                                                                           |                                                                                                                                                         | •                                                                                                                                                         |                                                                                                     |                   |                    |  |  |

| bit 12             | <b>OVRENL:</b> User Override Enable for PWMxL Pin bit<br>1 = OVRDAT0 provides data for output on the PWMxL pin                                              |                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     |                   |                    |  |  |

|                    |                                                                                                                                                             | 0 provides dat<br>enerator provid                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                           | n                                                                                                   |                   |                    |  |  |

| bit 11-10          | OVRDAT<1:0                                                                                                                                                  | )>: Data for PV                                                                                                                                                                           | VMxH/PWMxL                                                                                                                                              | Pins if Overrid                                                                                                                                           | e is Enabled bits                                                                                   |                   |                    |  |  |

|                    |                                                                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                         | s data for PWM<br>s data for PWM                                                                                                                          |                                                                                                     |                   |                    |  |  |

| bit 9-8            | OSYNC<1:0>                                                                                                                                                  | : User Output                                                                                                                                                                             | Override Synd                                                                                                                                           | chronization Co                                                                                                                                           | ntrol bits                                                                                          |                   |                    |  |  |

|                    | 11 = Reserve                                                                                                                                                |                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     |                   |                    |  |  |

|                    |                                                                                                                                                             |                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                                                           | RDAT<1:0> bits                                                                                      | occur when sp     | ecified by the     |  |  |

|                    |                                                                                                                                                             | D<2:0> bits in                                                                                                                                                                            |                                                                                                                                                         |                                                                                                                                                           | RDAT<1:0> bits o                                                                                    | ccur immediate    | lv (as soon as     |  |  |

|                    | possible                                                                                                                                                    | •                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     |                   |                    |  |  |

|                    | 00 = User ou                                                                                                                                                |                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                                                           |                                                                                                     |                   |                    |  |  |

|                    | time bas                                                                                                                                                    | tput overrides v<br>se (next Start-c                                                                                                                                                      |                                                                                                                                                         | IH/L and OVRD                                                                                                                                             | AT<1:0> bits are s                                                                                  | synchronized to   | the local PWM      |  |  |

| bit 7-6            |                                                                                                                                                             | se (next Start-c                                                                                                                                                                          | of-Cycle)                                                                                                                                               |                                                                                                                                                           | AT<1:0> bits are s<br>ent is Active bits                                                            | synchronized to   | the local PWM      |  |  |

| bit 7-6            | FLTDAT<1:0<br>If Fault is acti                                                                                                                              | se (next Start-c<br>>: Data for PW<br>ve, then FLTD                                                                                                                                       | of-Cycle)<br>MxH/PWMxL<br>AT1 provides o                                                                                                                |                                                                                                                                                           | ent is Active bits<br>I.                                                                            | synchronized to   | the local PWM      |  |  |

| bit 7-6<br>bit 5-4 | FLTDAT<1:0<br>If Fault is acti<br>If Fault is acti                                                                                                          | se (next Start-c<br>>: Data for PW<br>ve, then FLTD,<br>ve, then FLTD,                                                                                                                    | f-Cycle)<br>MxH/PWMxL<br>AT1 provides o<br>AT0 provides o                                                                                               | Pins if Fault Ev<br>lata for PWMxH<br>lata for PWMxL                                                                                                      | ent is Active bits<br>I.                                                                            |                   | the local PWM      |  |  |

|                    | FLTDAT<1:0<br>If Fault is acti<br>If Fault is acti<br>CLDAT<1:0><br>If current limit                                                                        | se (next Start-c<br>>: Data for PW<br>ve, then FLTD,<br>ve, then FLTD,<br>: Data for PWM<br>: is active, then                                                                             | f-Cycle)<br>MxH/PWMxL<br>AT1 provides o<br>AT0 provides o<br>MxH/PWMxL F<br>CLDAT1 prov                                                                 | Pins if Fault Ev<br>lata for PWMxH<br>lata for PWMxL                                                                                                      | ent is Active bits<br>I.<br><br>imit Event is Activ<br>WMxH.                                        |                   | the local PWM      |  |  |

| bit 5-4            | FLTDAT<1:0<br>If Fault is acti<br>If Fault is acti<br>CLDAT<1:0><br>If current limit<br>If current limit                                                    | se (next Start-c<br>>: Data for PW<br>ve, then FLTD,<br>ve, then FLTD,<br>: Data for PWN<br>: is active, then<br>: is active, then                                                        | f-Cycle)<br>MxH/PWMxL<br>AT1 provides o<br>AT0 provides o<br>MxH/PWMxL F<br>CLDAT1 prov<br>CLDAT0 prov                                                  | Pins if Fault Ev<br>lata for PWMxH<br>lata for PWMxL<br>Pins if Current-L<br>rides data for P<br>rides data for P                                         | ent is Active bits<br>I.<br><br>imit Event is Activ<br>WMxH.                                        | ve bits           | the local PWM      |  |  |

| bit 5-4            | FLTDAT<1:03<br>If Fault is acti<br>If Fault is acti<br>CLDAT<1:0><br>If current limit<br>If current limit<br>FFDAT<1:0><br>If feed-forwar                   | se (next Start-c<br>>: Data for PW<br>ve, then FLTD,<br>ve, then FLTD,<br>: Data for PWN<br>: is active, then<br>: Data for PWN<br>d is active, the                                       | of-Cycle)<br>MxH/PWMxL<br>AT1 provides of<br>AT0 provides of<br>MxH/PWMxL F<br>CLDAT1 prov<br>CLDAT0 prov<br>MxH/PWMxL F<br>n FFDAT1 pro                | Pins if Fault Ev<br>lata for PWMxH<br>lata for PWMxL<br>Pins if Current-L<br>rides data for P<br>rides data for P                                         | ent is Active bits<br>I.<br><br>imit Event is Activ<br>MMxH.<br>MMxL.<br>ward Event is Act<br>WMxH. | ve bits           | the local PWM      |  |  |

|                    | FLTDAT<1:03<br>If Fault is acti<br>If Fault is acti<br>CLDAT<1:0><br>If current limit<br>If current limit<br>FFDAT<1:0><br>If feed-forwar<br>If feed-forwar | se (next Start-c<br>>: Data for PW<br>ve, then FLTD,<br>ve, then FLTD,<br>: Data for PWN<br>: is active, then<br>: active, then<br>: Data for PWN<br>d is active, the<br>d is active, the | f-Cycle)<br>MxH/PWMxL<br>AT1 provides of<br>AT0 provides of<br>MxH/PWMxL F<br>CLDAT1 prov<br>CLDAT0 prov<br>MxH/PWMxL F<br>n FFDAT1 pro<br>n FFDAT0 pro | Pins if Fault Ev<br>lata for PWMxH<br>data for PWMxL<br>Pins if Current-L<br>rides data for P<br>rides data for P<br>vides data for F<br>vides data for F | ent is Active bits<br>I.<br><br>imit Event is Activ<br>MMxH.<br>MMxL.<br>ward Event is Act<br>WMxH. | ve bits           | the local PWM      |  |  |

## REGISTER 12-15: PGxIOCONL: PWM GENERATOR x I/O CONTROL REGISTER LOW

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| DIFF7   | SIGN7 | DIFF6 | SIGN6 | DIFF5 | SIGN5 | DIFF4 | SIGN4 |

| bit 15  | -     |       |       |       | •     |       | bit 8 |

|         |       |       |       |       |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| DIFF3   | SIGN3 | DIFF2 | SIGN2 | DIFF1 | SIGN1 | DIFF0 | SIGN0 |

| bit 7   |       |       |       |       | •     | •     | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

### REGISTER 13-19: ADMOD0L: ADC INPUT MODE CONTROL REGISTER 0 LOW

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

|                   |                  |                             |                    |

bit 15 through DIFF<1:0>: Differential-Mode for Corresponding Analog Inputs bits

- bit 1 (odd) 1 = Channel is differential

- 0 = Channel is single-ended

bit 14 through **SIGN<1:0>:** Output Data Sign for Corresponding Analog Inputs bits

- bit 0 (even) 1 = Channel output data is signed

- 0 = Channel output data is unsigned

## REGISTER 13-20: ADMOD0H: ADC INPUT MODE CONTROL REGISTER 0 HIGH

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| DIFF15 | SIGN15 | DIFF14 | SIGN14 | DIFF13 | SIGN13 | DIFF12 | SIGN12 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|--------|-------|-------|-------|-------|

| DIFF11 | SIGN11 | DIFF10 | SIGN10 | DIFF9 | SIGN9 | DIFF8 | SIGN8 |

| bit 7  |        |        |        |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 through DIFF<15:8>: Differential-Mode for Corresponding Analog Inputs bits

bit 1 (odd) 1 = Channel is differential

0 = Channel is single-ended

bit 14 through SIGN<15:8>: Output Data Sign for Corresponding Analog Inputs bits

- bit 0 (even) 1 = Channel output data is signed

- 0 = Channel output data is unsigned

#### REGISTER 19-7: PMDIN1: PARALLEL MASTER PORT DATA INPUT/OUTPUT LOW REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | DATA  | IN<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | DATA  | AIN<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 **DATAIN<15:0>:** Input/Output Data Port bits These bits are for 8-bit or 16-bit read/write operations in Master mode and are the input data port for 8-bit write operations in Slave mode.

#### REGISTER 19-8: PMDIN2: PARALLEL MASTER PORT DATA INPUT/OUTPUT HIGH REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | DATAI | N<31:24>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | DATAI | N<23:16>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimplen     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                 |                 |       |

bit 15-0 DATAIN<31:16>: Input/Output Data Port bits

These bits are for 8-bit write operations in Slave mode.

| R/W-0           | R/W-0                                                                                                                                          | R/W-0                                | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|------------------|------------------|-----------------|---------|--|--|--|--|

| PTGCLK2         | PTGCLK1                                                                                                                                        | PTGCLK0                              | PTGDIV4         | PTGDIV3          | PTGDIV2          | PTGDIV1         | PTGDIV0 |  |  |  |  |

| bit 15          |                                                                                                                                                |                                      |                 |                  |                  |                 | bit a   |  |  |  |  |