Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lv51rb2bbc-557 |

|                            |                                                                           |

Table 3.

P89LV51RB2/RC2/RD2 pin description ...continued

| Symbol       | Pin    |        | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------------|--------|--------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              | TQFP44 | PLCC44 |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| P1.3/CEX0    | 43     | 5      | I/O                       | <b>P1.3</b> — Port 1 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | I/O                       | <b>CEX0</b> — Capture/compare external I/O for PCA Module 0. Each capture/compare module connects to a Port 1 pin for external I/O. When not used by the PCA, this pin can handle standard I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| P1.4/SS/CEX1 | 44     | 6      | I/O                       | <b>P1.4</b> — Port 1 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | I                         | SS — Slave port select input for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|              |        |        | I/O                       | CEX1 — Capture/compare external I/O for PCA Module 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P1.5/MOSI/   | 1      | 7      | I/O                       | <b>P1.5</b> — Port 1 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CEX2         |        |        | I/O                       | MOSI — Master Output Slave Input for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|              |        |        | I/O                       | CEX2 — Capture/compare external I/O for PCA Module 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P1.6/MISO/   | 2      | 8      | I/O                       | <b>P1.6</b> — Port 1 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CEX3         |        |        | I/O                       | MISO — Master Input Slave Output for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|              |        |        | I/O                       | CEX3 — Capture/compare external I/O for PCA Module 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P1.7/SPICLK/ | 3      | 9      | I/O                       | <b>P1.7</b> — Port 1 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CEX4         |        |        | I/O                       | SPICLK — Serial clock input/output for SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | I/O                       | CEX4 — Capture/compare external I/O for PCA Module 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P2.0 to P2.7 |        |        | I/O with internal pull-up | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins are pulled HIGH by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 2 pins that are externally pulled LOW will source current (I <sub>IL</sub> ) because of the internal pull-ups. Port 2 sends the high-order address byte during fetches from external program memory and during accesses to external Data Memory that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups when transitioning to '1's. Port 2 also receives some control signals and a partial of high-order address bits during the external host mode programming and verification. |  |  |

| P2.0/A8      | 18     | 24     | I/O                       | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A8 — Address bit 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| P2.1/A9      | 19     | 25     | I/O                       | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A9 — Address bit 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| P2.2/A10     | 20     | 26     | I/O                       | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A10 — Address bit 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P2.3/A11     | 21     | 27     | I/O                       | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A11 — Address bit 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P2.4/A12     | 22     | 28     | I/O                       | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A12 — Address bit 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P2.5/A13     | 23     | 29     | I/O                       | <b>P2.5</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A13 — Address bit 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| P2.6/A14     | 24     | 30     | I/O                       | <b>P2.6</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |        |        | 0                         | A14 — Address bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

Table 3.

P89LV51RB2/RC2/RD2 pin description ...continued

| Symbol       | Pin        |        | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|------------|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | TQFP44     | PLCC44 |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P2.7/A15     | 25         | 31     | I/O                             | <b>P2.7</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        | 0                               | A15 — Address bit 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P3.0 to P3.7 |            |        | I/O with<br>internal<br>pull-up | <b>Port 3</b> : Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins are pulled HIGH by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled LOW will source current (I <sub>IL</sub> ) because of the internal pull-ups. Port 3 also receives some control signals and a partial of high-order address bits during the external host mode programming and verification.                                                                           |

| P3.0/RXD     | 5          | 11     | I                               | <b>P3.0</b> — Port 3 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        | I                               | RXD — Serial input port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P3.1/TXD     | 7          | 13     | 0                               | <b>P3.1</b> — Port 3 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        | 0                               | TXD — Serial output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3.2/INT0    | 8          | 14     |                                 | <b>P3.2</b> — Port 3 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        |                                 | INT0 — External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3.3/INT1    | 9          | 15     |                                 | <b>P3.3</b> — Port 3 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        | I                               | INT1 — External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3.4/T0      | P3.4/T0 10 | 16     | I/O                             | <b>P3.4</b> — Port 3 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        |                                 | T0 — External count input to Timer/counter 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P3.5/T1 11   | 17         | I/O    | <b>P3.5</b> — Port 3 bit 5.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              |            |        | 1                               | T1 — External count input to Timer/counter 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P3.6/WR      | 12         | 18     | 0                               | <b>P3.6</b> — Port 3 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        | 0                               | WR — External data memory write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P3.7/RD      | 13         | 19     | 0                               | <b>P3.7</b> — Port 3 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |            |        | 0                               | RD — External data memory read strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PSEN         | 26         | 32     | I/O                             | Program Store Enable: PSEN is the read strobe for external program memory. When the device is executing from internal program memory, PSEN is inactive (HIGH). When the device is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. A forced HIGH-to-LOW input transition on the PSEN pin while the RST input is continually held HIGH for more than 10 machine cycles will cause the device to enter external host mode programming. |

| RST          | 4          | 10     | I                               | Reset: While the oscillator is running, a HIGH logic state on this pin for two machine cycles will reset the device. If the PSEN pin is driven by a HIGH-to-LOW input transition while the RST input pin is held HIGH, the device will enter the external host mode, otherwise the device will enter the normal operation mode.                                                                                                                                                                                                                                       |

| EA           | 29         | 35     | I                               | <b>External Access Enable</b> : $\overline{EA}$ must be connected to $V_{SS}$ in order to enable the device to fetch code from the external program memory. $\overline{EA}$ must be strapped to $V_{DD}$ for internal program execution. The $\overline{EA}$ pin can tolerate a high voltage of 12 V.                                                                                                                                                                                                                                                                 |

Table 3. P89LV51RB2/RC2/RD2 pin description ...continued

| Symbol          | Pin              | Pin              |     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | TQFP44           | PLCC44           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ALE/PROG        | 27               | 33               | I/O | Address Latch Enable: ALE is the output signal for latching the low byte of the address during an access to external memory. This pin is also the programming pulse input (PROG) for flash programming. Normally the ALE[1] is emitted at a constant rate of ½ the crystal frequency[2] and can be used for external timing and clocking. One ALE pulse is skipped during each access to external data memory. However, if bit AO is set to '1', ALE is disabled. |

| n.c.            | 6, 17, 28,<br>39 | 1, 12, 23,<br>34 | I/O | not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL1           | 15               | 21               | I   | <b>Crystal 1</b> : Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                |

| XTAL2           | 14               | 20               | 0   | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{DD}$        | 38               | 44               | I   | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub> | 16               | 22               | I   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

<sup>[1]</sup> ALE loading issue: When ALE pin experiences higher loading (> 30 pF) during the reset, the microcontroller may accidentally enter into modes other than normal working mode. The solution is to connect a pull-up resistor of 3 k $\Omega$  to 50 k $\Omega$  from pin ALE to V<sub>DD</sub>.

<sup>[2]</sup> For 6-clock mode, ALE is emitted at  $\frac{1}{3}$  of crystal frequency.

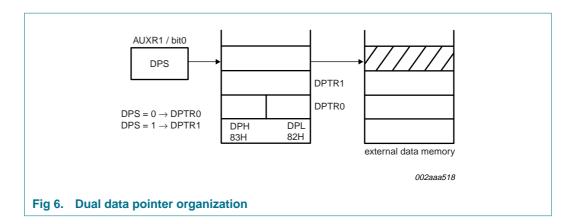

### 6.2.8 Dual data pointers

The device has two 16-bit data pointers. The DPTR Select (DPS) bit in AUXR1 determines which of the two data pointers is accessed. When DPS = 0, DPTR0 is selected; when DPS = 1, DPTR1 is selected. Quickly switching between the two data pointers can be accomplished by a single INC instruction on AUXR1 (see Figure 6).

Table 10. AUXR1 - Auxiliary register 1 (address A2H) bit allocation

Not bit addressable: reset value 00H.

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|--------|---|---|---|---|-----|---|---|-----|

| Symbol | - | - | - | - | GF2 | 0 | - | DPS |

Table 11. AUXR1 - Auxiliary register 1 (address A2H) bit descriptions

| Bit    | Symbol | Description                                                                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 3      | GF2    | General purpose user-defined flag.                                                                                                             |

| 2      | 0      | This bit contains a hard-wired '0'. Allows toggling of the DPS bit by incrementing AUXR1, without interfering with other bits in the register. |

| 1      | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 0      | DPS    | Data pointer select. Chooses one of two Data Pointers for use by the program. See text for details.                                            |

## 6.3 Flash memory IAP

### 6.3.1 Flash organization

The P89LV51RB2/RC2/RD2 program memory consists of a 16/32/64 kB block. ISP capability, in a second 8 kB block, is provided to allow the user code to be programmed in-circuit through the serial port. There are three methods of erasing or programming of the flash memory that may be used. First, the flash may be programmed or erased in the end-user application by calling low-level routines through a common entry point (IAP). Second, the on-chip ISP bootloader may be invoked. This ISP bootloader will, in turn, call low-level routines through the same common entry point that can be used by the end-user application. Third, the flash may be programmed or erased using the parallel method by using a commercially available EPROM programmer which supports this device.

### 6.3.2 Boot block (block 1)

When the microcontroller programs its own flash memory, all of the low level details are handled by code that is contained in block 1. A user program calls the common entry point in the block 1 with appropriate parameters to accomplish the desired operation. Boot block operations include erase user code, program user code, program security bits, etc.

Table 12. ISP hex record formats

|             | nox root a romato                                                                |

|-------------|----------------------------------------------------------------------------------|

| Record type | Command/data function                                                            |

| 00          | Program User Code Memory                                                         |

|             | :nnaaaa00ddddcc                                                                  |

|             | Where:                                                                           |

|             | nn = number of bytes to program                                                  |

|             | aaaa = address                                                                   |

|             | dddd = data bytes                                                                |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :10000000102030405006070809cc                                                    |

| 01          | End of File (EOF), no operation                                                  |

|             | :xxxxxx01cc                                                                      |

|             | Where:                                                                           |

|             | xxxxxx = required field but value is a 'don't care'                              |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :00000001FF                                                                      |

| 02          | Set SoftICE mode                                                                 |

|             | Following the next reset the device will enter the SoftICE mode. Will erase user |

|             | code memory, and erase device serial number.                                     |

|             | :0000002cc<br>Where:                                                             |

|             | 111111111111111111111111111111111111111                                          |

|             | xxxxxx = required field but value is a 'don't care'                              |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :00000002FE                                                                      |

Table 12. ISP hex record formats ...continued

| Table 12. ISP | nex record formatscontinued                                |

|---------------|------------------------------------------------------------|

| Record type   | Command/data function                                      |

| 03            | Miscellaneous Write functions                              |

|               | :nnxxxx03ffssddcc                                          |

|               | Where:                                                     |

|               | nn = number of bytes in the record                         |

|               | xxxx = required field but value is a 'don't care'          |

|               | ff = subfunction code                                      |

|               | ss = selection code                                        |

|               | dd = data (if needed)                                      |

|               | cc = checksum                                              |

|               | Subfunction code = 01 (Erase block 0)                      |

|               | ff = 01                                                    |

|               | Subfunction code = 05 (Program security bit, Double Clock) |

|               | ff = 05                                                    |

|               | ss = 01 program security bit                               |

|               | ss = 05 program double clock bit                           |

|               | Subfunction code = 08 (Erase sector, 128 B)                |

|               | ff = 08                                                    |

|               | ss = high byte of sector address (A15:8)                   |

|               | dd = low byte of sector address (A7, A6:0 ]= 0)            |

|               | Example:                                                   |

|               | :0300000308E000F2 (erase sector at E000H)                  |

| 04            | Display Device Data or Blank Check                         |

|               | :05xxxx04sssseeeeffcc                                      |

|               | Where                                                      |

|               | 05 = number of bytes in the record                         |

|               | xxxx = required field but value is a 'don't care'          |

|               | 04 = function code for display or blank check              |

|               | ssss = starting address, MSB first                         |

|               | eeee = ending address, MSB first                           |

|               | ff = subfunction                                           |

|               | 00 = display data                                          |

|               | 01 = blank check                                           |

|               | cc = checksum                                              |

|               | Subfunction codes:                                         |

|               | Example:                                                   |

|               | :0500000400001FFF00D9 (display from 0000H to 1FFFH)        |

|               |                                                            |

Table 15. TMOD - Timer/counter mode control register (address 89H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                                                  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | T1/T0  | Bits controlling Timer1/Timer0                                                                                                                                                               |

|     | GATE   | Gating control when set. Timer/counter 'x' is enabled only while 'INTx' INTx pin is HIGH and 'TRx' control pin is set. When cleared, Timer 'x' is enabled whenever 'TRx' control bit is set. |

|     | C/T    | Gating Timer or Counter Selector cleared for Timer operation (input from internal system clock). Set for Counter operation (input from 'Tx' input pin).                                      |

Table 16. TMOD - Timer/counter mode control register (address 89H) M1/M0 operating mode

| M1 | MO | Operat | ing mode                                                                                                                                                |

|----|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0      | 8048 timer 'TLx' serves as 5-bit prescaler                                                                                                              |

| 0  | 1  | 1      | 16-bit Timer/counter 'THx' and 'TLx' are cascaded; there is no prescaler.                                                                               |

| 1  | 0  | 2      | 8-bit auto-reload Timer/counter 'THx' holds a value which is to be reloaded into 'TLx' each time it overflows.                                          |

| 1  | 1  | 3      | (Timer 0) TL0 is an 8-bit Timer/counter controlled by the standard Timer 0 control bits. TH0 is an 8-bit timer only controlled by Timer 1 control bits. |

| 1  | 1  | 3      | (Timer 1) Timer/counter 1 stopped.                                                                                                                      |

Table 17. TCON - Timer/counter control register (address 88H) bit allocation

Bit addressable; reset value: 0000 0000B; reset source(s): any reset.

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

### Table 18. TCON - Timer/counter control register (address 88H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                       |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1    | Timer 1 overflow flag. Set by hardware on Timer/counter overflow. Cleared by hardware when the processor vectors to Timer 1 Interrupt routine, or by software.    |

| 6   | TR1    | Timer 1 Run control bit. Set/cleared by software to turn Timer/counter 1 on/off.                                                                                  |

| 5   | TF0    | Timer 0 overflow flag. Set by hardware on Timer/counter overflow. Cleared by hardware when the processor vectors to Timer 0 Interrupt routine, or by software.    |

| 4   | TR0    | Timer 0 Run control bit. Set/cleared by software to turn Timer/counter 0 on/off.                                                                                  |

| 3   | IE1    | Interrupt 1 Edge flag. Set by hardware when external interrupt 1 edge/low level is detected. Cleared by hardware when the interrupt is processed, or by software. |

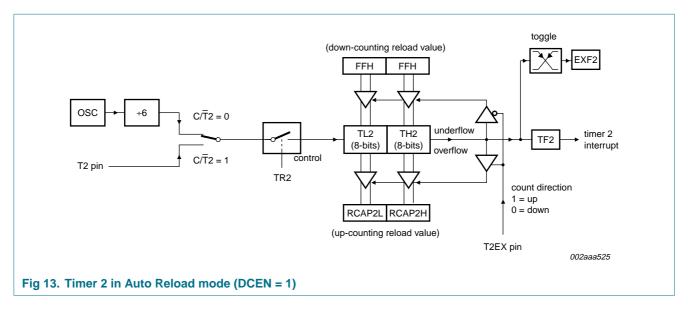

A logic 0 applied at pin T2EX causes Timer 2 to count down. The timer will underflow when TL2 and TH2 become equal to the value stored in RCAP2L and RCAP2H. Timer 2 underflow sets the TF2 flag and causes 0FFFFH to be reloaded into the timer registers TL2 and TH2. The external flag EXF2 toggles when Timer 2 underflows or overflows. This EXF2 bit can be used as a 17th bit of resolution if needed.

### 6.5.3 Programmable clock-out

A 50 % duty cycle clock can be programmed to come out on pin T2 (P1.0). This pin, besides being a I/O pin, has two additional functions. It can be programmed:

- · To input the external clock for Timer/counter 2, or

- To output a 50 % duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency.

To configure the Timer/counter 2 as a clock generator, bit  $C/\overline{T}2$  (in T2CON) must be cleared and bit T2OE in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in Equation 2:

$$\frac{Oscillator\ Frequency}{2 \times (65536 \angle (RCAP2H,\ RCAP2L))} \tag{2}$$

Where (RCAP2H, RCAP2L) = the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator.

### 6.5.4 Baud rate generator mode

Bits TCLK and/or RCLK in T2CON allow the UART transmit and receive baud rates to be derived from either Timer 1 or Timer 2 (See Section 6.6 "UART" on page 37 for details). When TCLK = 0, Timer 1 is used as the UART transmit baud rate generator. When

Table 29. SPCTL - SPI control register (address D5H) bit descriptions ...continued

| Bit | Symbol | Description                                                                                                                                                                         |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

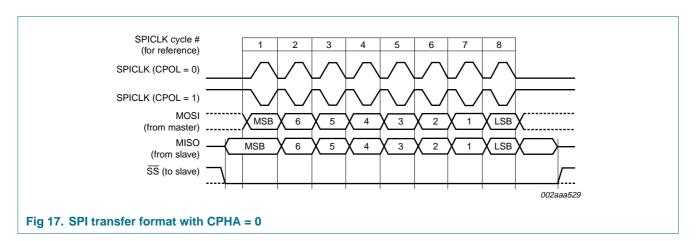

| 2   | СРНА   | Clock Phase control bit. 1 = shift triggered on the trailing edge of the clock; 0 = shift triggered on the leading edge of the clock.                                               |

| 1   | PSC1   | SPI Clock Rate Select bit 1. Along with PSC0 controls the SPICLK rate of the device when a master. PSC1 and PSC0 have no effect on the slave. See <u>Table 30</u> .                 |

| 0   | PSC0   | SPI Clock Rate Select bit 0. Along with PSC1 controls the SPICLK rate of the device when a master. PSC1 and PSC0 have no effect on the slave. See <a href="Table 30">Table 30</a> . |

Table 30. SPCTL - SPI control register (address D5H) clock rate selection

| PSC1 | PSC0 | SPICLK = f <sub>osc</sub> divided by |

|------|------|--------------------------------------|

| 0    | 0    | 4                                    |

| 0    | 1    | 16                                   |

| 1    | 0    | 64                                   |

| 1    | 1    | 128                                  |

Table 31. SPCFG - SPI status register (address AAH) bit allocation

Bit addressable; reset source(s): any reset; reset value: 0000 0000B.

| Bit    | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------|------|---|---|---|---|---|---|

| Symbol | SPIF | WCOL | - | - | - | - | - | - |

Table 32. SPCFG - SPI status register (address AAH) bit descriptions

| Bit    | Symbol | Description                                                                                                                                                            |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | SPIF   | SPI interrupt flag. Upon completion of data transfer, this bit is set to '1'. If SPIE = 1 and ES = 1, an interrupt is then generated. This bit is cleared by software. |

| 6      | WCOL   | Write Collision Flag. Set if the SPI data register is written to during data transfer. This bit is cleared by software.                                                |

| 5 to 0 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                        |

## P89LV51RB2/RC2/RD2

8-bit microcontrollers with 80C51 core

In the CMOD SFR there are three additional bits associated with the PCA. They are CIDL which allows the PCA to stop during Idle mode, WDTE which enables or disables the Watchdog function on module 4, and ECF which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The watchdog timer function is implemented in module 4 of PCA.

The CCON SFR contains the run control bit (CR) for the PCA and the flags for the PCA timer (CF) and each module (CCF4:0). To run the PCA the CR bit (CCON.6) must be set by software. The PCA is shut off by clearing this bit. The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software. Bits 0 through 4 of the CCON register are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags can only be cleared by software. All the modules share one interrupt vector. The PCA interrupt system is shown in Figure 21.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. The registers contain the bits that control the mode that each module operates in.

The ECCFn bit (from CCAPMn.0 where n = 0, 1, 2, 3, or 4 depending on the module) enables the CCFn flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module (see Figure 21).

PWM (CCAPMn.1) enables the pulse width modulation mode.

The TOGn bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register.

The match bit MATn (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

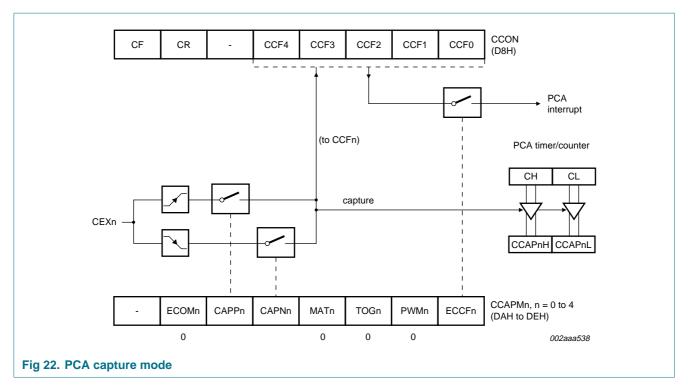

The next two bits CAPNn (CCAPMn.4) and CAPPn (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPPn bit enables the positive edge. If both bits are set, both edges will be enabled and a capture will occur for either transition.

The last bit in the register ECOMn (CCAPMn.6) when set enables the comparator function.

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output.

If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

### 6.9.2 16-bit software timer mode

The PCA modules can be used as software timers (Figure 23) by setting both the ECOMn and MATn bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

## 6.10 Security bit

The Security Bit protects against software piracy and prevents the contents of the flash from being read by unauthorized parties in Parallel Programmer mode. It also protects against code corruption resulting from accidental erasing and programming to the internal flash memory.

When the Security Bit is activated, all parallel programming commands except for Chip-Erase are ignored (thus the device cannot be read). However, ISP reading, writing, or erasing of the user's code can still be performed if the serial number and length has not been programmed. Therefore, when a user requests to program the Security Bit, the programmer should prompt the user and program a serial number into the device.

## 6.11 Interrupt priority and polling sequence

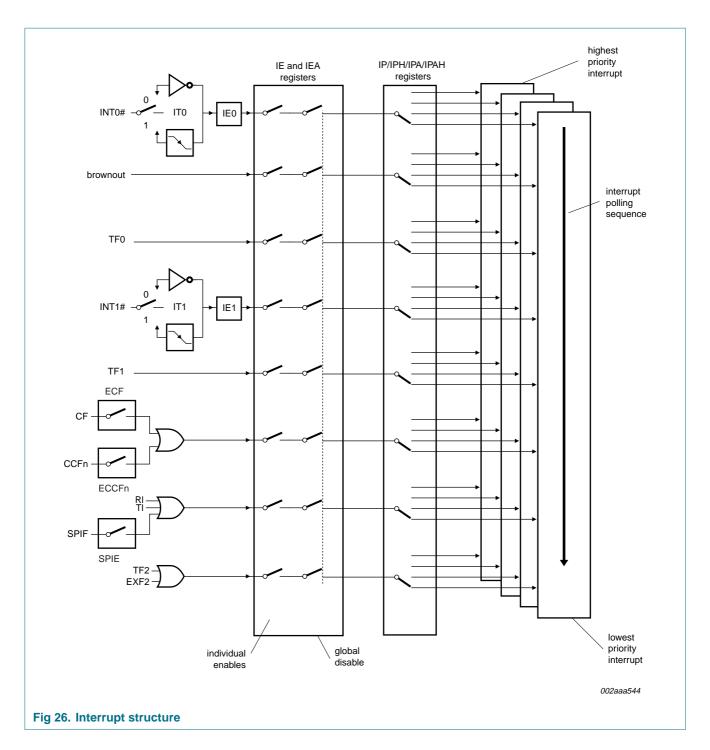

The device supports eight interrupt sources under a four level priority scheme. <u>Table 43</u> summarizes the polling sequence of the supported interrupts. Note that the SPI serial interface and the UART share the same interrupt vector. (See <u>Figure 26</u>).

Table 43. Interrupt polling sequence

| Description          | Interrupt flag | Vector address | Interrupt<br>enable bit | Interrupt<br>priority bit | Service<br>priority | Wake-up<br>power-down |

|----------------------|----------------|----------------|-------------------------|---------------------------|---------------------|-----------------------|

| External interrupt 0 | IE0            | 0003H          | EX0                     | PX0/H                     | 1 (highest)         | yes                   |

| Brownout             | -              | 004BH          | EBO                     | PBO/H                     | 2                   | no                    |

| T0                   | TF0            | 000BH          | ET0                     | PT0/H                     | 3                   | no                    |

| External interrupt 1 | IE1            | 0013H          | EX1                     | PX1/H                     | 4                   | yes                   |

| T1                   | TF1            | 001BH          | ET1                     | PT1/H                     | 5                   | no                    |

| PCA                  | CF/CCFn        | 0033H          | EC                      | PPCH                      | 6                   | no                    |

| UART/SPI             | TI/RI/SPIF     | 0023H          | ES                      | PS/H                      | 7                   | no                    |

| T2                   | TF2, EXF2      | 002BH          | ET2                     | PT2/H                     | 8                   | no                    |

|                      |                |                |                         |                           |                     |                       |

Table 44. IEN0 - Interrupt enable register 0 (address A8H) bit allocation Bit addressable; reset value: 00H.

| Bit    | 7  | 6  | 5   | 4  | 3   | 2   | 1   | 0   |

|--------|----|----|-----|----|-----|-----|-----|-----|

| Symbol | EA | EC | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

Table 51. IP0H - Interrupt priority 0 high register (address B7H) bit descriptions

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | PPCH   | PCA interrupt priority HIGH bit.                                |

| 5   | PT2H   | Timer 2 interrupt priority HIGH bit.                            |

| 4   | PSH    | Serial Port interrupt priority HIGH bit.                        |

| 3   | PT1H   | Timer 1 interrupt priority HIGH bit.                            |

| 2   | PX1H   | External interrupt 1 priority HIGH bit.                         |

| 1   | PT0H   | Timer 0 interrupt priority HIGH bit.                            |

| 0   | PX0H   | External interrupt 0 priority HIGH bit.                         |

## Table 52. IP1 - Interrupt priority 1 register (address F8H) bit allocation

Bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|--------|---|---|---|-----|---|---|---|---|

| Symbol | - | - | - | PBO | - | - | - | - |

Table 53. IP1 - Interrupt priority 1 register (address F8H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBO    | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

# Table 54. IP1H - Interrupt priority 1 high register (address F7H) bit allocation Not bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|--------|---|---|---|------|---|---|---|---|

| Symbol | - | - | - | PBOH | - | - | - | - |

### Table 55. IP1H - Interrupt priority 1 high register (address F7H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBOH   | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

### 6.12 Power-saving modes

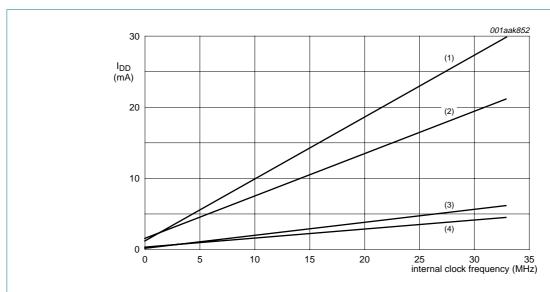

The device provides two power saving modes of operation for applications where power consumption is critical. The two modes are Idle and Power-down, see Table 56.

### 6.12.1 Idle mode

Idle mode is entered by setting the IDL bit in the PCON register. In Idle mode, the Program Counter (PC) is stopped. The system clock continues to run and all interrupts and peripherals remain active. The on-chip RAM and the special function registers hold their data during this mode.

The device exits Idle mode through either a system interrupt or a hardware reset. When exiting Idle mode via system interrupt, the start of the interrupt clears the IDL bit and exits Idle mode. After exiting the Interrupt Service Routine, the interrupted program resumes execution beginning at the instruction immediately following the instruction which invoked the Idle mode. A hardware reset starts the device similar to a power-on reset.

#### 6.12.2 Power-down mode

The Power-down mode is entered by setting the PD bit in the PCON register. In the Power-down mode, the clock is stopped and external interrupts are active for level sensitive interrupts only. SRAM contents are retained during Power-down mode, and the minimum  $V_{DD}$  level is 2.0 V.

The device exits Power-down mode through either an enabled external level sensitive interrupt or a hardware reset. The start of the interrupt clears the PD bit and exits Power-down. Holding the external interrupt pin low restarts the oscillator, the signal must hold low at least 1024 clock cycles before bringing back high to complete the exit. Upon interrupt signal restored to logic  $V_{IH}$ , the interrupt service routine program execution resumes beginning at the instruction immediately following the instruction which invoked Power-down mode. A hardware reset starts the device similar to power-on reset.

To exit properly out of Power-down mode, the reset or external interrupt should not be executed before the  $V_{DD}$  line is restored to its normal operating voltage. Be sure to hold  $V_{DD}$  voltage long enough at its normal operating level for the oscillator to restart and stabilize (normally less than 10 ms).

Table 56. Power-saving modes