Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 33MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lv51rc2fbc-557 |

|                            |                                                                           |

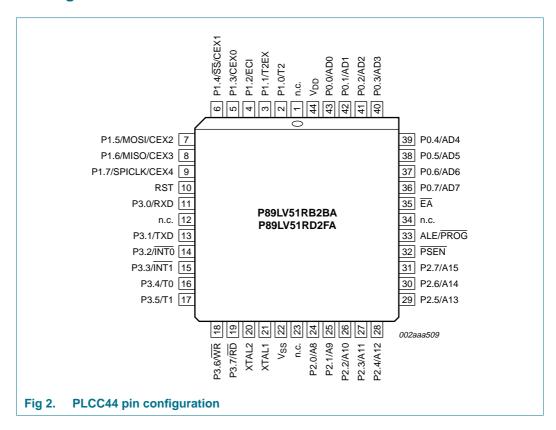

### 5. Pinning information

#### 5.1 Pinning

V<sub>DD</sub> must stay below V<sub>bo</sub> at least four oscillator clock periods before the brownout detection circuit will respond.

Brownout interrupt can be enabled by setting the EBO bit (IEN1.3). If EBO bit is set and a brownout condition occurs, a brownout interrupt will be generated to execute the program at location 004BH. It is required that the EBO bit is cleared by software after the brownout interrupt is serviced. Clearing EBO bit when the brownout condition is active will properly reset the device. If brownout interrupt is not enabled, a brownout condition will reset the program to resume execution at location 0000H. A brownout detect reset will clear the BSEL bit (FCF.0) but will not change the SWR bit (FCF.1) and therefore will not change the banking of the lower 8 kB of user code memory space.

#### 6.2.5 Watchdog reset

Like a brownout detect reset, the watchdog timer reset will clear the BSEL bit (FCF.0) but will not change the SWR bit (FCF.1) and therefore will not change the banking of the lower 8 kB of user code memory space.

The state of the SWR and BSEL bits after different types of resets is shown in <u>Table 6</u>. This results in the code memory bank selections as shown.

Table 6. Effects of reset sources on bank selection

| Reset source          | SWR bit result (FCF.1) | BSEL bit result (FCF.0) | Addresses from 0000H to 1FFFH                                                       | Addresses above<br>1FFFH |  |

|-----------------------|------------------------|-------------------------|-------------------------------------------------------------------------------------|--------------------------|--|

| External reset        | 0                      | 0                       | Boot code (in block 1)                                                              | User code (in block 0)   |  |

| Power-on reset        |                        |                         |                                                                                     |                          |  |

| Watchdog reset        | Х                      | 0                       | Retains state of SWR bit. If                                                        |                          |  |

| Brownout detect reset |                        |                         | SWR, BSEL = 00 then uses<br>boot code. If SWR,<br>BSEL = 10 then uses user<br>code. |                          |  |

| Software reset        | 1                      | 0                       | User code (in block 0)                                                              |                          |  |

#### 6.2.6 Data RAM memory

The data RAM has 1024 B of internal memory. The device can also address up to 64 kB for external data memory.

#### 6.2.7 Expanded data RAM addressing

The P89LV51RB2/RC2/RD2 has 1 kB of RAM. See Figure 5 "Internal and external data memory structure" on page 19.

The device has four sections of internal data memory:

- 1. The lower 128 B of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 B of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 B (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit (see 'Auxiliary function Register' (AUXR) in Table 4 "Special function registers" on page 11).

Since the upper 128 B occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

Table 7. AUXR - Auxiliary register (address 8EH) bit allocation Not bit addressable; reset value 00H.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0  |

|--------|---|---|---|---|---|---|--------|----|

| Symbol | - | - | - | - | - | - | EXTRAM | AO |

Table 8. AUXR - Auxiliary register (address 8EH) bit descriptions

| Bit    | Symbol | Description                                                                                                                                                                                                                                                                                                                                                      |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 2 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                                                                                                                                                                                                                  |

| 1      | EXTRAM | Internal/External RAM access using MOVX-@Ri/@DPTR. When '0', core attempts to access internal XRAM with address specified in MOVX instruction. If address supplied with this instruction exceeds on-chip available XRAM, off-chip XRAM is going to be selected and accessed. When '1', every MOVX-@Ri/@DPTR instruction targets external data memory by default. |

| 0      | AO     | ALE off: disables/enables ALE. AO = 0 results in ALE emitted at a constant rate of $\frac{1}{2}$ the oscillator frequency. In case of AO = 1, ALE is active only during a MOVX or MOVC.                                                                                                                                                                          |

When instructions access addresses in the upper 128 B (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

Indirect access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in '#data' is written to RAM location 90H rather than port 1.

Direct access:

MOV90H, #data; write data to P1

Data in '#data' is written to port 1. Instructions that write directly to the address, write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 B of memory is physically located on the chip and logically occupies the first 768 B of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 ( $\overline{\text{WR}}$ ), P3.7 ( $\overline{\text{RD}}$ ), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

Expanded RAM access (indirect addressing only):

MOVX@DPTR, A DPTR contains 0A0H

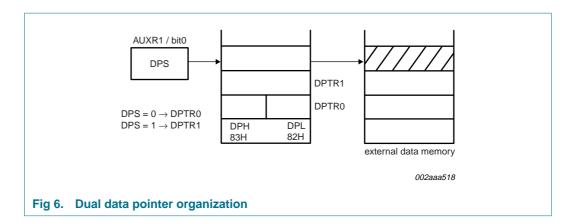

Table 10. AUXR1 - Auxiliary register 1 (address A2H) bit allocation

Not bit addressable: reset value 00H.

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|--------|---|---|---|---|-----|---|---|-----|

| Symbol | - | - | - | - | GF2 | 0 | - | DPS |

Table 11. AUXR1 - Auxiliary register 1 (address A2H) bit descriptions

| Bit    | Symbol | Description                                                                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 3      | GF2    | General purpose user-defined flag.                                                                                                             |

| 2      | 0      | This bit contains a hard-wired '0'. Allows toggling of the DPS bit by incrementing AUXR1, without interfering with other bits in the register. |

| 1      | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 0      | DPS    | Data pointer select. Chooses one of two Data Pointers for use by the program. See text for details.                                            |

#### 6.3 Flash memory IAP

#### 6.3.1 Flash organization

The P89LV51RB2/RC2/RD2 program memory consists of a 16/32/64 kB block. ISP capability, in a second 8 kB block, is provided to allow the user code to be programmed in-circuit through the serial port. There are three methods of erasing or programming of the flash memory that may be used. First, the flash may be programmed or erased in the end-user application by calling low-level routines through a common entry point (IAP). Second, the on-chip ISP bootloader may be invoked. This ISP bootloader will, in turn, call low-level routines through the same common entry point that can be used by the end-user application. Third, the flash may be programmed or erased using the parallel method by using a commercially available EPROM programmer which supports this device.

#### 6.3.2 Boot block (block 1)

When the microcontroller programs its own flash memory, all of the low level details are handled by code that is contained in block 1. A user program calls the common entry point in the block 1 with appropriate parameters to accomplish the desired operation. Boot block operations include erase user code, program user code, program security bits, etc.

Table 12. ISP hex record formats

|             | nox root a romato                                                                |

|-------------|----------------------------------------------------------------------------------|

| Record type | Command/data function                                                            |

| 00          | Program User Code Memory                                                         |

|             | :nnaaaa00ddddcc                                                                  |

|             | Where:                                                                           |

|             | nn = number of bytes to program                                                  |

|             | aaaa = address                                                                   |

|             | dddd = data bytes                                                                |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :10000000102030405006070809cc                                                    |

| 01          | End of File (EOF), no operation                                                  |

|             | :xxxxxx01cc                                                                      |

|             | Where:                                                                           |

|             | xxxxxx = required field but value is a 'don't care'                              |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :00000001FF                                                                      |

| 02          | Set SoftICE mode                                                                 |

|             | Following the next reset the device will enter the SoftICE mode. Will erase user |

|             | code memory, and erase device serial number.                                     |

|             | :0000002cc<br>Where:                                                             |

|             | 111111111111111111111111111111111111111                                          |

|             | xxxxxx = required field but value is a 'don't care'                              |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :00000002FE                                                                      |

Table 12. ISP hex record formats ... continued

| Record type | Command/data function                                                                  |

|-------------|----------------------------------------------------------------------------------------|

| 05          | Miscellaneous Read functions                                                           |

| 03          | :02xxxx05ffsscc                                                                        |

|             | Where:                                                                                 |

|             | 02 = number of bytes in the record                                                     |

|             | xxxx = required field but value is a 'don't care'                                      |

|             | 05 = function code for misc read                                                       |

|             | ffss = subfunction and selection code                                                  |

|             | 0000 = read manufacturer id                                                            |

|             | 0001 = read device id 1                                                                |

|             | 0002 = read boot code version                                                          |

|             | 0700 = read security bit (00 SoftICE serial number match 0 SB 0 Double Clock)          |

|             | cc = checksum                                                                          |

|             | Example:                                                                               |

|             | :020000050000F9 (display manufacturer id)                                              |

| 06          | Direct load of baud rate                                                               |

|             | :02xxxx06HHLLcc                                                                        |

|             | Where:                                                                                 |

|             | 02 = number of bytes in the record                                                     |

|             | xxxx = required field but value is a 'don't care'                                      |

|             | HH = high byte of timer                                                                |

|             | LL = low byte of timer                                                                 |

|             | cc = checksum                                                                          |

|             | Example:                                                                               |

|             | :02000006FFFFcc (load T2 = FFFF)                                                       |

| 07          | Reset serial number, erase user code, clear SoftICE mode                               |

|             | :xxxxxx07cc                                                                            |

|             | Where:                                                                                 |

|             | xxxxxx = required field but value is a 'don't care'  07 = reset serial number function |

|             | cc = checksum                                                                          |

|             | Example:                                                                               |

|             | :0000007F9                                                                             |

| 08          | Verify serial number                                                                   |

|             | :nnxxxx08sssscc                                                                        |

|             | Where:                                                                                 |

|             | xxxxxx = required field but value is a 'don't care'                                    |

|             | 08 = verify serial number function                                                     |

|             | ssss = serial number contents                                                          |

|             | cc = checksum                                                                          |

|             | Example:                                                                               |

|             | :03000008010203EF (verify serial number = 010203)                                      |

|             |                                                                                        |

Table 12. ISP hex record formats ... continued

| Record type | Command/data function                               |

|-------------|-----------------------------------------------------|

| 09          | Write serial number                                 |

|             | :nnxxxx09sssscc                                     |

|             | Where:                                              |

|             | xxxxxx = required field but value is a 'don't care' |

|             | 09 = write serial number function                   |

|             | ssss = serial number contents                       |

|             | cc = checksum                                       |

|             | Example:                                            |

|             | :03000009010203EE (write serial number = 010203)    |

| 0A          | Display serial number                               |

|             | :xxxxxx0Acc                                         |

|             | Where:                                              |

|             | xxxxxx = required field but value is a 'don't care' |

|             | 0A = display serial number function                 |

|             | cc = checksum                                       |

|             | Example:                                            |

|             | :000000AF6                                          |

| 0B          | Reset and run user code                             |

|             | :xxxxxx0Bcc                                         |

|             | Where:                                              |

|             | xxxxxx = required field but value is a 'don't care' |

|             | 0B = reset and run user code                        |

|             | cc = checksum                                       |

|             | Example:                                            |

|             | :0000000BF5                                         |

#### 6.3.5 Using the serial number

This device has the option of storing a 31 B serial number along with the length of the serial number (for a total of 32 B) in a non-volatile memory space. When ISP mode is entered, the serial number length is evaluated to determine if the serial number is in use. If the length of the serial number is programmed to either 00H or FFH, the serial number is considered not in use. If the serial number is in use, reading, programming, or erasing of the user code memory or the serial number is blocked until the user transmits a 'verify serial number' record containing a serial number and length that matches the serial number and length previously stored in the device. The user can reset the serial number to all zeros and set the length to zero by sending the 'reset serial number' record. In addition, the 'reset serial number' record will also erase all user code.

#### 6.3.6 IAP method

Several IAP calls are available for use by an application program to permit selective erasing, reading and programming of flash sectors, security bit, configuration bytes, and device id. All calls are made through a common interface, PGM\_MTP. The programming functions are selected by setting up the microcontroller's registers before making a call to PGM\_MTP at 1FF0H. The IAP calls are shown in Table 13.

Table 13. IAP function calls ... continued

| IAP function                     | IAP call parameters                       |

|----------------------------------|-------------------------------------------|

| Read Security Bit, Double Clock, | Input parameters:                         |

| SoftICE                          | ACC = 07H                                 |

|                                  | Return parameter(s):                      |

|                                  | ACC = 000 S/N-match 0 SB 0 DBL_CLK        |

| Read Security Bit, Double Clock, | Input parameters:                         |

| SoftICE                          | ACC = 07H                                 |

|                                  | Return parameter(s):                      |

|                                  | ACC = 00 SoftICE S/N-match 0 SB 0 DBL_CLK |

| Erase sector                     | Input parameters:                         |

|                                  | R1 = 08H                                  |

|                                  | DPH = sector address high byte            |

|                                  | DPL = sector address low byte             |

|                                  | Return parameter(s):                      |

|                                  | ACC = 00 = pass                           |

|                                  | ACC = !00 = fail                          |

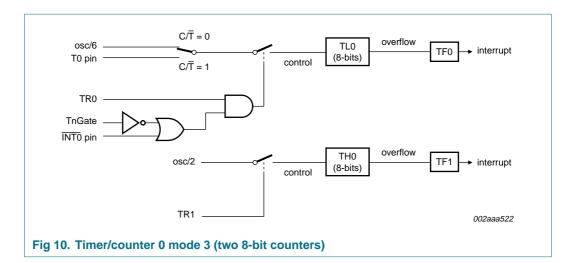

#### 6.4 Timers/counters 0 and 1

The two 16-bit Timer/counter registers: Timer 0 and Timer 1 can be configured to operate either as timers or event counters (see Table 14 and Table 15).

In the 'Timer' function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of six oscillator periods, the count rate is  $\frac{1}{6}$  of the oscillator frequency.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once every machine cycle.

When the samples show a HIGH in one cycle and a LOW in the next cycle, the count is incremented. The new count value appears in the register in the machine cycle following the one in which the transition was detected. Since it takes two machine cycles (12 oscillator periods) for 1-to-0 transition to be recognized, the maximum count rate is 1/12 of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle. In addition to the 'Timer' or 'Counter' selection, Timer 0 and Timer 1 have four operating modes from which to select.

The 'Timer' or 'Counter' function is selected by control bits C/T in the special function register TMOD. These two timer/counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both timers/counters. Mode 3 is different. The four operating modes are described in the following text.

Table 14. TMOD - Timer/counter mode control register (address 89H) bit allocation Not bit addressable; reset value: 0000 0000B; reset source(s): any source.

| Bit    | 7      | 6     | 5    | 4    | 3      | 2     | 1    | 0    |

|--------|--------|-------|------|------|--------|-------|------|------|

| Symbol | T1GATE | T1C/T | T1M1 | T1M0 | T0GATE | T0C/T | T0M1 | T0M0 |

Table 18. TCON - Timer/counter control register (address 88H) bit descriptions ...continued

| Bit | Symbol | Description                                                                                                                                                       |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | IT1    | Interrupt 1 Type control bit. Set/cleared by software to specify falling edge/low level that triggers external interrupt 1.                                       |

| 1   | IE0    | Interrupt 0 Edge flag. Set by hardware when external interrupt 0 edge/low level is detected. Cleared by hardware when the interrupt is processed, or by software. |

| 0   | IT0    | Interrupt 0 Type control bit. Set/cleared by software to specify falling edge/low level that triggers external interrupt 0.                                       |

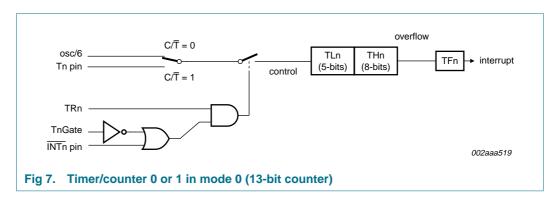

#### 6.4.1 Mode 0

Putting either Timer into mode 0 makes it look like an 8048 Timer, which is an 8-bit counter with a fixed divide-by-32 prescaler. Figure 7 shows mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn. The count input is enabled to the Timer when TRn = 1 and either GATE = 0 or  $\overline{\text{INTn}}$  = 1. Setting GATE = 1 allows the Timer to be controlled by external input  $\overline{\text{INTn}}$ , to facilitate pulse width measurements. TRn is a control bit in the Special Function Register TCON (Figure 6). The GATE bit is in the TMOD register.

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 and Timer 1 (see <u>Figure 7</u>). There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

#### 6.4.2 Mode 1

Mode 1 is the same as mode 0, except that all 16 bits of the timer register (THn and TLn) are used. See Figure 8.

#### 6.5 Timer 2

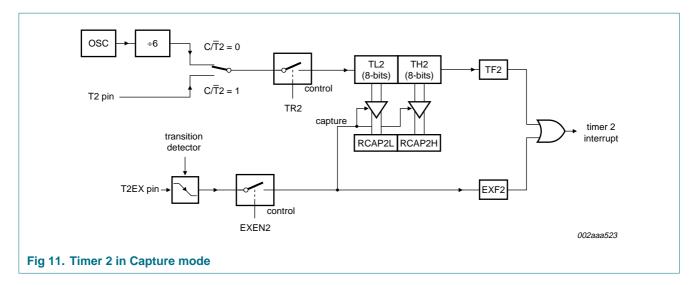

Timer 2 is a 16-bit Timer/counter which can operate as either an event timer or an event counter, as selected by  $C/\overline{12}$  in the special function register T2CON. Timer 2 has four operating modes: Capture, Auto-reload (up or down counting), Clock-out, and Baud Rate Generator which are selected according to  $\underline{\text{Table 19}}$  using T2CON ( $\underline{\text{Table 20}}$  and  $\underline{\text{Table 21}}$ ) and T2MOD ( $\underline{\text{Table 22}}$  and  $\underline{\text{Table 23}}$ ).

Table 19. Timer 2 operating mode

| RCLK + TCLK | CP/RL2 | TR2 | T2OE | Mode                   |

|-------------|--------|-----|------|------------------------|

| 0           | 0      | 1   | 0    | 16-bit auto reload     |

| 0           | 1      | 1   | 0    | 16-bit capture         |

| 0           | 0      | 1   | 1    | programmable clock-out |

| 1           | X      | 1   | 0    | baud rate generator    |

| Χ           | X      | 0   | X    | off                    |

Table 20. T2CON - Timer/counter 2 control register (address C8H) bit allocation Bit addressable; reset value: 00H.

| Bit    | 7   | 6    | 5    | 4    | 3     | 2   | 1    | 0      |

|--------|-----|------|------|------|-------|-----|------|--------|

| Symbol | TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2 | CP/RL2 |

Table 21. T2CON - Timer/counter 2 control register (address C8H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                                                                                                                                   |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF2    | Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when either RCLK or TCLK = 1 or when Timer 2 is in Clock-out mode.                                                                                                       |

| 6   | EXF2   | Timer 2 external flag is set when Timer 2 is in capture, reload or baud-rate mode, EXEN2 = 1 and a negative transition on T2EX occurs. If Timer 2 interrupt is enabled, EXF2 = 1 causes the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software. |

| 5   | RCLK   | Receive clock flag. When set, causes the UART to use Timer 2 overflow pulses for its receive clock in modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the receive clock.                                                                                       |

This bit can be used to generate an interrupt (by enabling the Timer 2 interrupt bit in the IEN0 register). If EXEN2 = 1, Timer 2 operates as described above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively.

In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2 like TF2 can generate an interrupt (which vectors to the same location as Timer 2 overflow interrupt). The Timer 2 interrupt service routine can interrogate TF2 and EXF2 to determine which event caused the interrupt.

There is no reload value for TL2 and TH2 in this mode. Even when a capture event occurs from T2EX, the counter keeps on counting T2 pin transitions or  $f_{\rm osc}$  / 6 pulses. Since once loaded contents of RCAP2L and RCAP2H registers are not protected, once Timer2 interrupt is signalled it has to be serviced before a new capture event on T2EX pin occurs. Otherwise, the next falling edge on T2EX pin will initiate reload of the current value from TL2 and TH2 to RCAP2L and RCAP2H and consequently corrupt their content related to the previously reported interrupt.

#### 6.5.2 Auto-reload mode (up or down counter)

In the 16-bit auto-reload mode, Timer 2 can be configured as either a timer or counter (via  $C/\overline{T}2$  in T2CON), then programmed to count up or down. The counting direction is determined by bit DCEN (Down Counter Enable) which is located in the T2MOD register (see <u>Table 22</u> and <u>Table 23</u>). When reset is applied, DCEN = 0 and Timer 2 will default to counting up. If the DCEN bit is set, Timer 2 can count up or down depending on the value of the T2EX pin.

Figure 12 shows Timer 2 counting up automatically (DCEN = 0).

The following examples help to show the versatility of this scheme.

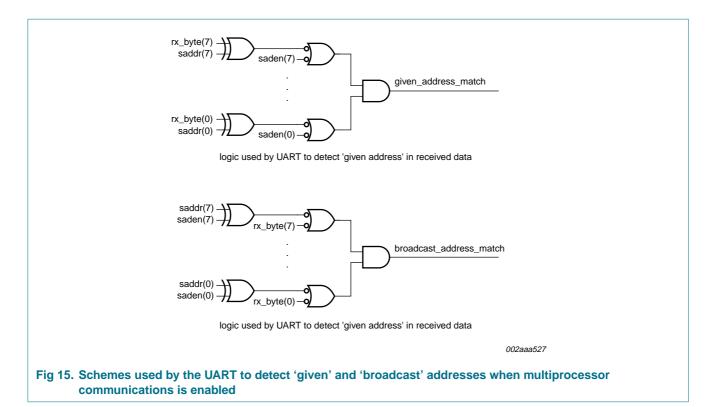

Example 1, slave 0:

SADDR =

$$1100\ 0000$$

$$\frac{\text{SADEN} = 1111\ 1101}{\text{Given} = 1100\ 00X0}$$

(4)

Example 2, slave 1:

SADDR =

$$1100\ 0000$$

$$\frac{\text{SADEN} = 1111\ 1110}{\text{Given} = 1100\ 000X}$$

(5)

In the above example value SADDR is the same and the SADEN data is used to differentiate between the two slaves. Slave 0 requires a '0' in bit 0 and it ignores bit 1. Slave 1 requires a '0' in bit 1 and bit 0 is ignored. A unique address for Slave 0 would be 1100 0010 since slave 1 requires a '0' in bit 1. A unique address for slave 1 would be 1100 0001 since a '1' in bit 0 will exclude slave 0. Both slaves can be selected at the same time by an address which has bit 0 = 0 (for slave 0) and bit 1 = 0 (for slave 1). Thus, both could be addressed with 1100 0000.

46 of 76

Table 33. WDTC - Watchdog control register (address COH) bit allocation Bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4     | 3    | 2    | 1   | 0    |

|--------|---|---|---|-------|------|------|-----|------|

| Symbol | - | - | - | WDOUT | WDRE | WDTS | WDT | SWDT |

Table 34. WDTC - Watchdog control register (address COH) bit descriptions

|        |        | ionacy control regions. (addition confidences                                                                                |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Symbol | Description                                                                                                                  |

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs.                                                              |

| 4      | WDOUT  | Watchdog output enable. When this bit and WDRE are both set, a Watchdog reset will drive the reset pin active for 32 clocks. |

| 3      | WDRE   | Watchdog timer reset enable. When set enables a watchdog timer reset.                                                        |

| 2      | WDTS   | Watchdog timer reset flag, when set indicates that a WDT reset occurred. Reset in software.                                  |

| 1      | WDT    | Watchdog timer refresh. Set by software to force a WDT reset.                                                                |

| 0      | SWDT   | Start watchdog timer, when set starts the WDT. When cleared, stops the WDT.                                                  |

|        |        |                                                                                                                              |

#### 6.9 PCA

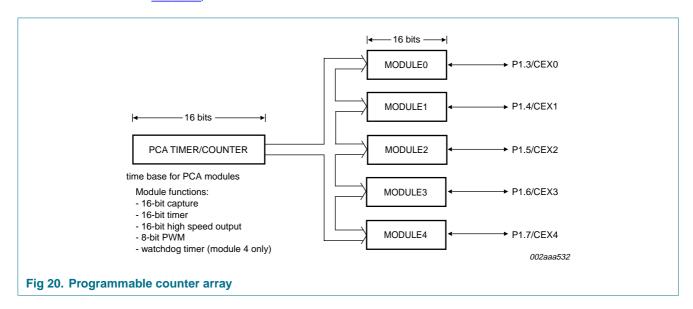

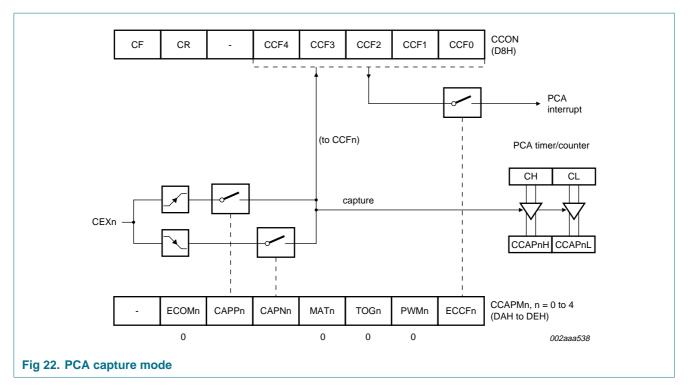

The PCA includes a special 16-bit Timer that has five 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or PWM. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1.4 (CEX1), etc. Registers CH and CL contain the current values of the free running up counting 16-bit PCA timer. The PCA timer is a common time base for all five modules and can be programmed to run at:  $\frac{1}{6}$  the oscillator frequency,  $\frac{1}{2}$  the oscillator frequency, the Timer 0 overflow, or the input on the ECI pin (P1.2). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD SFR (see Table 35) and Table 36).

Table 37. CMOD - PCA counter mode register (address D9H) count pulse select

| CPS1 | CPS0 | Select PCA input                                                       |

|------|------|------------------------------------------------------------------------|

| 0    | 0    | 0 Internal clock, f <sub>osc</sub> / 6                                 |

| 0    | 1    | 1 Internal clock, f <sub>osc</sub> / 2                                 |

| 1    | 0    | 2 Timer 0 overflow                                                     |

| 1    | 1    | 3 External clock at ECI/P1.2 pin (maximum rate = f <sub>osc</sub> / 4) |

## Table 38. CCON - PCA counter control register (address 0D8H) bit allocation Bit addressable; reset value: 00H.

| Bit    | 7  | 6  | 5 | 4    | 3    | 2    | 1    | 0    |

|--------|----|----|---|------|------|------|------|------|

| Symbol | CF | CR | - | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |

Table 39. CCON - PCA counter control register (address 0D8H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                                                                |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF     | PCA Counter Overflow Flag. Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is set. CF may be set by either hardware or software but can only be cleared by software. |

| 6   | CR     | PCA Counter Run Control Bit. Set by software to turn the PCA counter on. Must be cleared by software to turn the PCA counter off.                                                                          |

| 5   | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                                                            |

| 4   | CCF4   | PCA Module 4 Interrupt Flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| 3   | CCF3   | PCA Module 3 Interrupt Flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| 2   | CCF2   | PCA Module 2 Interrupt Flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| 1   | CCF1   | PCA Module 1 Interrupt Flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

| 0   | CCF0   | PCA Module 0 Interrupt Flag. Set by hardware when a match or capture occurs. Must be cleared by software.                                                                                                  |

|     |        |                                                                                                                                                                                                            |

# Table 40. CCAPMn - PCA modules compare/capture register (address CCAPM0: 0DAH, CCAPM1: 0DBH, CCAPM2: 0DCH, CCAPM3: 0DDH, CCAPM4: 0DEH) bit allocation

Not bit addressable; reset value: 00H.

| Bit    | 7 | 6     | 5     | 4     | 3    | 2    | 1    | 0     |

|--------|---|-------|-------|-------|------|------|------|-------|

| Symbol | - | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn |

Table 41. CCAPMn - PCA modules compare/capture register (address CCAPM0: 9DAH, CCAPM1: 0DBH, CCAPM2: 0DCH, CCAPM3: 0DDH, CCAPM4: 0DEH) bit descriptions

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | ECOMn  | Enable Comparator. ECOMn = 1 enables the comparator function.   |

| 5   | CAPPn  | Capture Positive, CAPPn = 1 enables positive edge capture.      |

| 4   | CAPNn  | Capture Negative, CAPNn = 1 enables negative edge capture.      |

If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

#### 6.9.2 16-bit software timer mode

The PCA modules can be used as software timers (Figure 23) by setting both the ECOMn and MATn bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

Table 45. IEN0 - Interrupt enable register 0 (address A8H) bit descriptions

| Bit | Symbol | Description                                                                                     |

|-----|--------|-------------------------------------------------------------------------------------------------|

| 7   | EA     | Interrupt Enable Bit: EA = 1 interrupt(s) can be serviced, EA = 0 interrupt servicing disabled. |

| 6   | EC     | PCA Interrupt Enable bit.                                                                       |

| 5   | ET2    | Timer 2 Interrupt Enable.                                                                       |

| 4   | ES     | Serial Port Interrupt Enable.                                                                   |

| 3   | ET1    | Timer 1 Overflow Interrupt Enable.                                                              |

| 2   | EX1    | External Interrupt 1 Enable.                                                                    |

| 1   | ET0    | Timer 0 Overflow Interrupt Enable.                                                              |

| 0   | EX0    | External Interrupt 0 Enable.                                                                    |

#### Table 46. IEN1 - Interrupt enable register 1 (address E8H) bit allocation

Bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|--------|---|---|---|---|-----|---|---|---|

| Symbol | - | - | - | - | EBO | - | - | - |

#### Table 47. IEN1 - Interrupt enable register 1 (address E8H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 3      | EBO    | Brownout Interrupt Enable. 1 = enable, 0 = disable.             |

| 2 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

# **Table 48. IPO - Interrupt priority 0 low register (address B8H) bit allocation** *Bit addressable; reset value: 00H.*

| Bit    | 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   |

|--------|---|-----|-----|----|-----|-----|-----|-----|

| Symbol | - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 |

#### Table 49. IP0 - Interrupt priority 0 low register (address B8H) bit descriptions

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | PPC    | PCA interrupt priority LOW bit.                                 |

| 5   | PT2    | Timer 2 interrupt priority LOW bit.                             |

| 4   | PS     | Serial Port interrupt priority LOW bit.                         |

| 3   | PT1    | Timer 1 interrupt priority LOW bit.                             |

| 2   | PX1    | External interrupt 1 priority LOW bit.                          |

| 1   | PT0    | Timer 0 interrupt priority LOW bit.                             |

| 0   | PX0    | External interrupt 0 priority LOW bit.                          |

## Table 50. IP0H - Interrupt priority 0 high register (address B7H) bit allocation Not bit addressable; reset value: 00H.

| Bit    | 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|--------|---|------|------|-----|------|------|------|------|

| Symbol | - | PPCH | PT2H | PSH | PT1H | PX1H | PT0H | PX0H |

Table 51. IP0H - Interrupt priority 0 high register (address B7H) bit descriptions

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | PPCH   | PCA interrupt priority HIGH bit.                                |

| 5   | PT2H   | Timer 2 interrupt priority HIGH bit.                            |

| 4   | PSH    | Serial Port interrupt priority HIGH bit.                        |

| 3   | PT1H   | Timer 1 interrupt priority HIGH bit.                            |

| 2   | PX1H   | External interrupt 1 priority HIGH bit.                         |

| 1   | PT0H   | Timer 0 interrupt priority HIGH bit.                            |

| 0   | PX0H   | External interrupt 0 priority HIGH bit.                         |

#### Table 52. IP1 - Interrupt priority 1 register (address F8H) bit allocation

Bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|--------|---|---|---|-----|---|---|---|---|

| Symbol | - | - | - | PBO | - | - | - | - |

Table 53. IP1 - Interrupt priority 1 register (address F8H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBO    | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

### Table 54. IP1H - Interrupt priority 1 high register (address F7H) bit allocation Not bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|--------|---|---|---|------|---|---|---|---|

| Symbol | - | - | - | PBOH | - | - | - | - |

#### Table 55. IP1H - Interrupt priority 1 high register (address F7H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBOH   | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

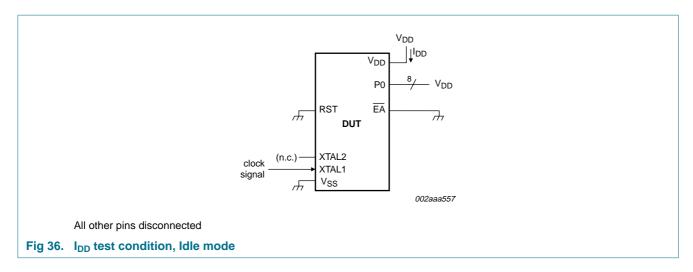

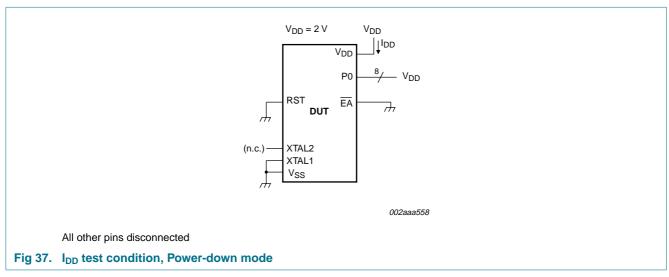

#### 6.12 Power-saving modes

The device provides two power saving modes of operation for applications where power consumption is critical. The two modes are Idle and Power-down, see Table 56.

#### 6.12.1 Idle mode

Idle mode is entered by setting the IDL bit in the PCON register. In Idle mode, the Program Counter (PC) is stopped. The system clock continues to run and all interrupts and peripherals remain active. The on-chip RAM and the special function registers hold their data during this mode.

### 7. Limiting values

#### Table 61. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

| Symbol                 | Parameter                           | Conditions                                                         | Min  | Max                   | Unit |

|------------------------|-------------------------------------|--------------------------------------------------------------------|------|-----------------------|------|

| T <sub>amb(bias)</sub> | bias ambient temperature            |                                                                    | -55  | +125                  | °C   |

| T <sub>stg</sub>       | storage temperature                 |                                                                    | -65  | +150                  | °C   |

| $V_{I}$                | input voltage                       | on $\overline{EA}$ pin to $V_{SS}$                                 | -0.5 | +14                   | V    |

| $V_n$                  | voltage on any other pin            | except $V_{SS}$ ; with respect to $V_{DD}$                         | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| I <sub>OL(I/O)</sub>   | LOW-level output current per        | pins P1.5, P1.6, P1.7                                              | -    | 20                    | mΑ   |

|                        | input/output pin                    | all other pins                                                     | -    | 15                    | mA   |

| P <sub>tot(pack)</sub> | total power dissipation per package | based on package heat<br>transfer, not device power<br>consumption | -    | 1.5                   | W    |

#### 8. Static characteristics

#### Table 62. Static characteristics

$T_{amb} = 0 \,^{\circ}C$  to  $+70 \,^{\circ}C$  or  $-40 \,^{\circ}C$  to  $+85 \,^{\circ}C$ ;  $V_{DD} = 2.7 \,^{\circ}V$  to  $3.6 \,^{\circ}V$ ;  $V_{SS} = 0 \,^{\circ}V$ .

| Symbol                | Parameter                   | Conditions                                                     | Min                   | Max                       | Unit   |

|-----------------------|-----------------------------|----------------------------------------------------------------|-----------------------|---------------------------|--------|

| n <sub>endu(fl)</sub> | endurance of flash memory   | JEDEC Standard A117                                            | 10000                 | -                         | cycles |

| t <sub>ret(fl)</sub>  | flash memory retention time | JEDEC Standard A103                                            | <u>[1]</u> 100        | -                         | years  |

| I <sub>latch</sub>    | I/O latch-up current        | JEDEC Standard 78                                              | 100 + I <sub>DD</sub> | -                         | mA     |

| V <sub>IL</sub>       | LOW-level input voltage     | $2.7 \text{ V} < \text{V}_{DD} < 3.6 \text{ V}$                | -0.5                  | +0.7                      | V      |

| V <sub>IH</sub>       | HIGH-level input voltage    | $2.7 \text{ V} < \text{V}_{DD} < 3.6 \text{ V}$                | 0.2V <sub>DD</sub> +  | 0.9 V <sub>DD</sub> + 0.5 | V      |

|                       |                             | XTAL1, RST                                                     | $0.7V_{DD}$           | $V_{DD} + 0.5$            | V      |

| V <sub>OL</sub>       | LOW-level output voltage    | V <sub>DD</sub> = 2.7 V; ports 1.5, 1.6,<br>1.7                |                       |                           |        |

|                       |                             | I <sub>OL</sub> = 16 mA                                        | -                     | 1.0                       | V      |

|                       |                             | V <sub>DD</sub> = 2.7 V; ports 1, 2, 3, except PSEN, ALE       | [2][3][4]             |                           |        |

|                       |                             | $I_{OL} = 100 \mu\text{A}$                                     | -                     | 0.3                       | V      |

|                       |                             | I <sub>OL</sub> = 1.6 mA                                       | -                     | 0.45                      | V      |

|                       |                             | $I_{OL} = 3.5 \text{ mA}$                                      | -                     | 1.0                       | V      |

|                       |                             | $V_{DD} = 2.7 \text{ V; port 0, } \overline{\text{PSEN}},$ ALE |                       |                           |        |

|                       |                             | $I_{OL} = 200  \mu A$                                          | -                     | 0.3                       | V      |

|                       |                             | I <sub>OL</sub> = 3.2 mA                                       | -                     | 0.45                      | V      |