Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

|                            | Obsolute                                                                 |

| Product Status             | Obsolete                                                                 |

| Core Processor             | 8051                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 33MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lv51rd2ba-512 |

**Product data sheet**

**Table 4. Special function registers** ...continued \* Indicates SFRs that are bit addressable.

| Name   | Description                    | SFR         | Bit functions and addresses |                 |               |           |      |           |           |           |

|--------|--------------------------------|-------------|-----------------------------|-----------------|---------------|-----------|------|-----------|-----------|-----------|

|        |                                | addr.       | MSB                         |                 |               |           |      |           |           | LSB       |

| FST    | Flash Status Register          | B6          | -                           | SB              | -             | -         | EDC  | -         | -         | -         |

|        |                                | Bit address | AF                          | AE              | AD            | AC        | AB   | AA        | <b>A9</b> | <b>A8</b> |

| EN0*   | Interrupt Enable 0             | A8H         | EA                          | EC              | ET2           | ES        | ET1  | EX1       | ET0       | EX0       |

|        |                                | Bit address | EF                          | EE              | ED            | EC        | EB   | EA        | <b>E9</b> | E8        |

| EN1*   | Interrupt Enable 1             | E8H         | -                           | -               | -             | -         | EBO  | -         | -         | -         |

|        |                                | Bit address | BF                          | BE              | BD            | ВС        | BB   | ВА        | B9        | B8        |

| P0*    | Interrupt Priority             | B8H         | -                           | PPC             | PT2           | PS        | PT1  | PX1       | PT0       | PX0       |

| P0H    | Interrupt Priority 0 HIGH      | В7Н         | -                           | PPCH            | PT2H          | PSH       | PT1H | PX1H      | PT0H      | PX0H      |

|        |                                | Bit address | FF                          | FE              | FD            | FC        | FB   | FA        | F9        | F8        |

| P1*    | Interrupt Priority 1           | F8H         | -                           | -               | -             | PBO       | -    | -         | -         | -         |

| P1H    | Interrupt Priority 1 HIGH      | F7H         | -                           | -               | -             | PBOH      | -    | -         | -         | -         |

| FCF    |                                | B1H         | -                           | -               | -             | -         | -    | -         | SWR       | BSEL      |

|        |                                | Bit address | 87                          | 86              | 85            | 84        | 83   | 82        | 81        | 80        |

| >0*    | Port 0                         | 80H         | AD7                         | AD6             | AD5           | AD4       | AD3  | AD2       | AD1       | AD0       |

|        |                                | Bit address | 97                          | 96              | 95            | 94        | 93   | 92        | 91        | 90        |

| P1*    | Port 1                         | 90H         | CEX4/<br>SPICLK             | CEX3/<br>MISO   | CEX2/<br>MOSI | CEX1/SS   | CEX0 | ECI       | T2EX      | T2        |

|        |                                | Bit address | <b>A7</b>                   | <b>A6</b>       | <b>A5</b>     | <b>A4</b> | A3   | <b>A2</b> | <b>A1</b> | A0        |

| P2*    | Port 2                         | A0H         | A15                         | A14             | A13           | A12       | A11  | A10       | A9        | A8        |

|        |                                | Bit address | B7                          | B6              | B5            | B4        | В3   | <b>B2</b> | B1        | В0        |

| ⊃3*    | Port 3                         | B0H         | $\overline{RD}$             | $\overline{WR}$ | T1            | T0        | ĪNT1 | ĪNT0      | TXD       | RXD       |

| PCON   | Power Control Register         | 87H         | SMOD1                       | SMOD0           | BOF           | POF       | GF1  | GF0       | PD        | IDL       |

|        |                                | Bit address | D7                          | D6              | D5            | D4        | D3   | D2        | D1        | D0        |

| PSW*   | Program Status Word            | D0H         | CY                          | AC              | F0            | RS1       | RS0  | OV        | F1        | Р         |

| RCAP2H | Timer2 Capture HIGH            | CBH         |                             |                 |               |           |      |           |           |           |

| RCAP2L | Timer2 Capture LOW             | CAH         |                             |                 |               |           |      |           |           |           |

|        |                                | Bit address | 9F                          | 9E              | 9D            | 9C        | 9B   | 9A        | 99        | 98        |

| SCON*  | Serial Port Control            | 98H         | SM0/FE                      | SM1             | SM2           | REN       | TB8  | RB8       | TI        | RI        |

| SBUF   | Serial Port Data Buffer Regist | ter 99H     |                             |                 |               |           |      |           |           |           |

V<sub>DD</sub> must stay below V<sub>bo</sub> at least four oscillator clock periods before the brownout detection circuit will respond.

Brownout interrupt can be enabled by setting the EBO bit (IEN1.3). If EBO bit is set and a brownout condition occurs, a brownout interrupt will be generated to execute the program at location 004BH. It is required that the EBO bit is cleared by software after the brownout interrupt is serviced. Clearing EBO bit when the brownout condition is active will properly reset the device. If brownout interrupt is not enabled, a brownout condition will reset the program to resume execution at location 0000H. A brownout detect reset will clear the BSEL bit (FCF.0) but will not change the SWR bit (FCF.1) and therefore will not change the banking of the lower 8 kB of user code memory space.

#### 6.2.5 Watchdog reset

Like a brownout detect reset, the watchdog timer reset will clear the BSEL bit (FCF.0) but will not change the SWR bit (FCF.1) and therefore will not change the banking of the lower 8 kB of user code memory space.

The state of the SWR and BSEL bits after different types of resets is shown in <u>Table 6</u>. This results in the code memory bank selections as shown.

Table 6. Effects of reset sources on bank selection

| Reset source          | SWR bit result (FCF.1) | BSEL bit result (FCF.0) | Addresses from 0000H to 1FFFH                                                       | Addresses above<br>1FFFH |  |

|-----------------------|------------------------|-------------------------|-------------------------------------------------------------------------------------|--------------------------|--|

| External reset        | 0                      | 0                       | Boot code (in block 1)                                                              | User code (in block 0)   |  |

| Power-on reset        |                        |                         |                                                                                     |                          |  |

| Watchdog reset        | Х                      | 0                       | Retains state of SWR bit. If                                                        |                          |  |

| Brownout detect reset |                        |                         | SWR, BSEL = 00 then uses<br>boot code. If SWR,<br>BSEL = 10 then uses user<br>code. |                          |  |

| Software reset        | 1                      | 0                       | User code (in block 0)                                                              |                          |  |

#### 6.2.6 Data RAM memory

The data RAM has 1024 B of internal memory. The device can also address up to 64 kB for external data memory.

#### 6.2.7 Expanded data RAM addressing

The P89LV51RB2/RC2/RD2 has 1 kB of RAM. See Figure 5 "Internal and external data memory structure" on page 19.

The device has four sections of internal data memory:

- 1. The lower 128 B of RAM (00H to 7FH) are directly and indirectly addressable.

- 2. The higher 128 B of RAM (80H to FFH) are indirectly addressable.

- 3. The special function registers (80H to FFH) are directly addressable only.

- 4. The expanded RAM of 768 B (00H to 2FFH) is indirectly addressable by the move external instruction (MOVX) and clearing the EXTRAM bit (see 'Auxiliary function Register' (AUXR) in Table 4 "Special function registers" on page 11).

Since the upper 128 B occupy the same addresses as the SFRs, the RAM must be accessed indirectly. The RAM and SFRs space are physically separate even though they have the same addresses.

Table 7. AUXR - Auxiliary register (address 8EH) bit allocation Not bit addressable; reset value 00H.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0  |

|--------|---|---|---|---|---|---|--------|----|

| Symbol | - | - | - | - | - | - | EXTRAM | AO |

Table 8. AUXR - Auxiliary register (address 8EH) bit descriptions

| Bit    | Symbol | Description                                                                                                                                                                                                                                                                                                                                                      |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 2 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                                                                                                                                                                                                                  |

| 1      | EXTRAM | Internal/External RAM access using MOVX-@Ri/@DPTR. When '0', core attempts to access internal XRAM with address specified in MOVX instruction. If address supplied with this instruction exceeds on-chip available XRAM, off-chip XRAM is going to be selected and accessed. When '1', every MOVX-@Ri/@DPTR instruction targets external data memory by default. |

| 0      | AO     | ALE off: disables/enables ALE. AO = 0 results in ALE emitted at a constant rate of $\frac{1}{2}$ the oscillator frequency. In case of AO = 1, ALE is active only during a MOVX or MOVC.                                                                                                                                                                          |

When instructions access addresses in the upper 128 B (above 7FH), the MCU determines whether to access the SFRs or RAM by the type of instruction given. If it is indirect, then RAM is accessed. If it is direct, then an SFR is accessed. See the examples below.

Indirect access:

MOV@R0, #data; R0 contains 90H

Register R0 points to 90H which is located in the upper address range. Data in '#data' is written to RAM location 90H rather than port 1.

Direct access:

MOV90H, #data; write data to P1

Data in '#data' is written to port 1. Instructions that write directly to the address, write to the SFRs.

To access the expanded RAM, the EXTRAM bit must be cleared and MOVX instructions must be used. The extra 768 B of memory is physically located on the chip and logically occupies the first 768 B of external memory (addresses 000H to 2FFH).

When EXTRAM = 0, the expanded RAM is indirectly addressed using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. Accessing the expanded RAM does not affect ports P0, P3.6 ( $\overline{\text{WR}}$ ), P3.7 ( $\overline{\text{RD}}$ ), or P2. With EXTRAM = 0, the expanded RAM can be accessed as in the following example.

Expanded RAM access (indirect addressing only):

MOVX@DPTR, A DPTR contains 0A0H

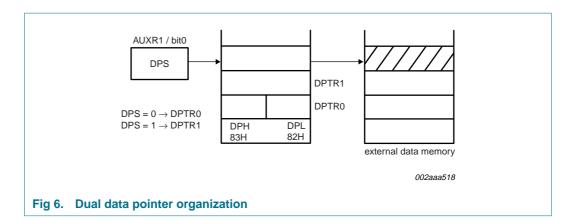

Table 10. AUXR1 - Auxiliary register 1 (address A2H) bit allocation

Not bit addressable: reset value 00H.

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|--------|---|---|---|---|-----|---|---|-----|

| Symbol | - | - | - | - | GF2 | 0 | - | DPS |

Table 11. AUXR1 - Auxiliary register 1 (address A2H) bit descriptions

| Bit    | Symbol | Description                                                                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 4 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 3      | GF2    | General purpose user-defined flag.                                                                                                             |

| 2      | 0      | This bit contains a hard-wired '0'. Allows toggling of the DPS bit by incrementing AUXR1, without interfering with other bits in the register. |

| 1      | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                |

| 0      | DPS    | Data pointer select. Chooses one of two Data Pointers for use by the program. See text for details.                                            |

#### 6.3 Flash memory IAP

#### 6.3.1 Flash organization

The P89LV51RB2/RC2/RD2 program memory consists of a 16/32/64 kB block. ISP capability, in a second 8 kB block, is provided to allow the user code to be programmed in-circuit through the serial port. There are three methods of erasing or programming of the flash memory that may be used. First, the flash may be programmed or erased in the end-user application by calling low-level routines through a common entry point (IAP). Second, the on-chip ISP bootloader may be invoked. This ISP bootloader will, in turn, call low-level routines through the same common entry point that can be used by the end-user application. Third, the flash may be programmed or erased using the parallel method by using a commercially available EPROM programmer which supports this device.

#### 6.3.2 Boot block (block 1)

When the microcontroller programs its own flash memory, all of the low level details are handled by code that is contained in block 1. A user program calls the common entry point in the block 1 with appropriate parameters to accomplish the desired operation. Boot block operations include erase user code, program user code, program security bits, etc.

A chip-erase operation can be performed using a commercially available parallel programer. This operation will erase the contents of this boot block and it will be necessary for the user to reprogram this boot block (block 1) with the NXP-provided ISP/IAP code in order to use the ISP or IAP capabilities of this device. Go to <a href="http://www.nxp.com/support">http://www.nxp.com/support</a> for questions or to obtain the hex file for this device.

#### 6.3.3 ISP

ISP is performed without removing the microcontroller from the system. The ISP facility consists of a series of internal hardware resources coupled with internal firmware to facilitate remote programming of the P89LV51RB2/RC2/RD2 through the serial port. This firmware is provided by NXP and embedded within each P89LV51RB2/RC2/RD2 device. The NXP ISP facility has made in-circuit programming in an embedded application possible with a minimum of additional expense in components and circuit board area. The ISP function uses five pins ( $V_{DD}$ ,  $V_{SS}$ , TXD, RXD, and RST). Only a small connector needs to be available to interface your application to an external circuit in order to use this feature.

#### 6.3.4 Using ISP

The ISP feature allows for a wide range of baud rates to be used in your application, independent of the oscillator frequency. It is also adaptable to a wide range of oscillator frequencies. This is accomplished by measuring the bit-time of a single bit in a received character. This information is then used to program the baud rate in terms of timer counts based on the oscillator frequency. The ISP feature requires that an initial character (an uppercase U) be sent to the P89LV51RB2/RC2/RD2 to establish the baud rate. The ISP firmware provides auto-echo of received characters. Once baud rate initialization has been performed, the ISP firmware will only accept Intel Hex-type records. Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below:

#### :NNAAAARRDD..DDCC<crlf>

In the Intel Hex record, the 'NN' represents the number of data bytes in the record. The P89LV51RB2/RC2/RD2 will accept up to 32 data bytes. The 'AAAA' string represents the address of the first byte in the record. If there are zero bytes in the record, this field is often set to 0000. The 'RR' string indicates the record type. A record type of '00' is a data record. A record type of '01' indicates the end-of-file mark. In this application, additional record types will be added to indicate either commands or data for the ISP facility.

The maximum number of data bytes in a record is limited to 32 (decimal). ISP commands are summarized in <a href="Table 12">Table 12</a>. As a record is received by the P89LV51RB2/RC2/RD2, the information in the record is stored internally and a checksum calculation is performed. The operation indicated by the record type is not performed until the entire record has been received. Should an error occur in the checksum, the P89LV51RB2/RC2/RD2 will send an 'X' out the serial port indicating a checksum error. If the checksum calculation is found to match the checksum in the record, then the command will be executed. In most cases, successful reception of the record will be indicated by transmitting a '.' character out the serial port.

Table 12. ISP hex record formats

|             | nox root a romato                                                                |

|-------------|----------------------------------------------------------------------------------|

| Record type | Command/data function                                                            |

| 00          | Program User Code Memory                                                         |

|             | :nnaaaa00ddddcc                                                                  |

|             | Where:                                                                           |

|             | nn = number of bytes to program                                                  |

|             | aaaa = address                                                                   |

|             | dddd = data bytes                                                                |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :10000000102030405006070809cc                                                    |

| 01          | End of File (EOF), no operation                                                  |

|             | :xxxxxx01cc                                                                      |

|             | Where:                                                                           |

|             | xxxxxx = required field but value is a 'don't care'                              |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :00000001FF                                                                      |

| 02          | Set SoftICE mode                                                                 |

|             | Following the next reset the device will enter the SoftICE mode. Will erase user |

|             | code memory, and erase device serial number.                                     |

|             | :0000002cc<br>Where:                                                             |

|             | 111111111111111111111111111111111111111                                          |

|             | xxxxxx = required field but value is a 'don't care'                              |

|             | cc = checksum                                                                    |

|             | Example:                                                                         |

|             | :00000002FE                                                                      |

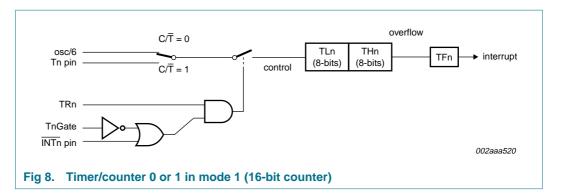

Table 15. TMOD - Timer/counter mode control register (address 89H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                                                  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | T1/T0  | Bits controlling Timer1/Timer0                                                                                                                                                               |

|     | GATE   | Gating control when set. Timer/counter 'x' is enabled only while 'INTx' INTx pin is HIGH and 'TRx' control pin is set. When cleared, Timer 'x' is enabled whenever 'TRx' control bit is set. |

|     | C/T    | Gating Timer or Counter Selector cleared for Timer operation (input from internal system clock). Set for Counter operation (input from 'Tx' input pin).                                      |

Table 16. TMOD - Timer/counter mode control register (address 89H) M1/M0 operating mode

| M1 | MO | Operat | ing mode                                                                                                                                                |

|----|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0      | 8048 timer 'TLx' serves as 5-bit prescaler                                                                                                              |

| 0  | 1  | 1      | 16-bit Timer/counter 'THx' and 'TLx' are cascaded; there is no prescaler.                                                                               |

| 1  | 0  | 2      | 8-bit auto-reload Timer/counter 'THx' holds a value which is to be reloaded into 'TLx' each time it overflows.                                          |

| 1  | 1  | 3      | (Timer 0) TL0 is an 8-bit Timer/counter controlled by the standard Timer 0 control bits. TH0 is an 8-bit timer only controlled by Timer 1 control bits. |

| 1  | 1  | 3      | (Timer 1) Timer/counter 1 stopped.                                                                                                                      |

Table 17. TCON - Timer/counter control register (address 88H) bit allocation

Bit addressable; reset value: 0000 0000B; reset source(s): any reset.

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

#### Table 18. TCON - Timer/counter control register (address 88H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                       |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1    | Timer 1 overflow flag. Set by hardware on Timer/counter overflow. Cleared by hardware when the processor vectors to Timer 1 Interrupt routine, or by software.    |

| 6   | TR1    | Timer 1 Run control bit. Set/cleared by software to turn Timer/counter 1 on/off.                                                                                  |

| 5   | TF0    | Timer 0 overflow flag. Set by hardware on Timer/counter overflow. Cleared by hardware when the processor vectors to Timer 0 Interrupt routine, or by software.    |

| 4   | TR0    | Timer 0 Run control bit. Set/cleared by software to turn Timer/counter 0 on/off.                                                                                  |

| 3   | IE1    | Interrupt 1 Edge flag. Set by hardware when external interrupt 1 edge/low level is detected. Cleared by hardware when the interrupt is processed, or by software. |

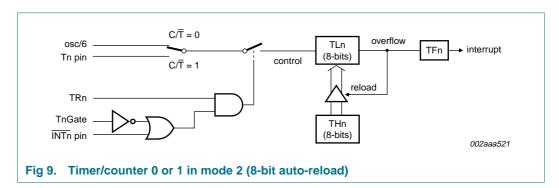

#### 6.4.3 Mode 2

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload, as shown in <u>Figure 9</u>. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which must be preset by software. The reload leaves THn unchanged. Mode 2 operation is the same for Timer 0 and Timer 1.

#### 6.4.4 Mode 3

When timer 1 is in mode 3 it is stopped (holds its count). The effect is the same as setting TR1 = 0.

Timer 0 in mode 3 establishes TL0 and TH0 as two separate 8-bit counters. The logic for mode 3 and Timer 0 is shown in Figure 10. TL0 uses the Timer 0 control bits: T0C/T, T0GATE, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the 'Timer 1' interrupt.

Mode 3 is provided for applications that require an extra 8-bit timer. With Timer 0 in mode 3, the P89LV51RB2/RC2/RD2 can look like it has an additional Timer.

**Note:** When Timer 0 is in mode 3, Timer 1 can be turned on and off by switching it into and out of its own mode 3. It can still be used by the serial port as a baud rate generator, or in any application not requiring an interrupt.

Table 21. T2CON - Timer/counter 2 control register (address C8H) bit descriptions

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                            |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | TCLK   | Transmit clock flag. When set, causes the UART to use Timer 2 overflow pulses for its transmit clock in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock.                                                                                                                                            |

| 3   | EXEN2  | Timer 2 external enable flag. When set, allows a capture or reload to occur as a result of a negative transition on T2EX if Timer 2 is not being used to clock the serial port. EXEN2 = 0 causes Timer 2 to ignore events at T2EX.                                                                                                     |

| 2   | TR2    | Start/stop control for Timer 2. A logic '1' enables the timer to run.                                                                                                                                                                                                                                                                  |

| 1   | C/T2   | Timer or counter select. (Timer 2) $0 = \text{internal timer } (f_{osc} / 6)$ $1 = \text{external event counter (falling edge triggered; external clock's maximum rate} = f_{osc} / 12$                                                                                                                                                |

| 0   | CP/RL2 | Capture/Reload flag. When set, captures will occur on negative transitions at T2EX if EXEN2 = 1. When cleared, auto-reloads will occur either with Timer 2 overflows or negative transitions at T2EX when EXEN2 = 1. When either RCLK = 1 or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow. |

Table 22. T2MOD - Timer 2 mode control register (address C9H) bit allocation

Not bit addressable; Reset value: XX00 0000B.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|--------|---|---|---|---|---|---|------|------|

| Symbol | - | - | - | - | - | - | T2OE | DCEN |

Table 23. T2MOD - Timer 2 mode control register (address C9H) bit descriptions

| Bit    | Symbol | Description                                                                                  |

|--------|--------|----------------------------------------------------------------------------------------------|

| 7 to 2 | -      | Reserved for future use. Should be set to '0' by user programs.                              |

| 1      | T2OE   | Timer 2 Output Enable bit. Used in programmable clock-out mode only.                         |

| 0      | DCEN   | Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/down counter. |

#### 6.5.1 Capture mode

In the Capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter (as selected by  $C/\overline{T}2$  in T2CON) which upon overflowing sets bit TF2, the Timer 2 overflow bit.

The capture mode is illustrated in Figure 11.

TCLK = 1, Timer 2 is used as the UART transmit baud rate generator. RCLK has the same effect for the UART receive baud rate. With these two bits, the serial port can have different receive and transmit baud rates – Timer 1 or Timer 2.

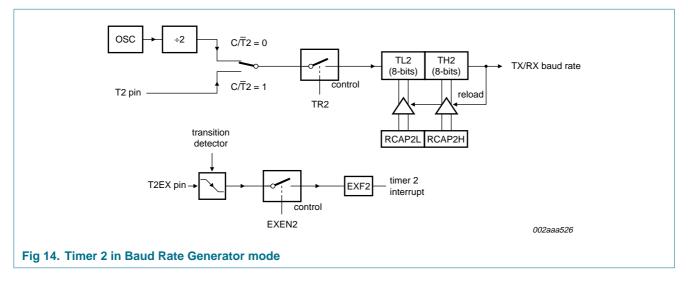

Figure 14 shows Timer 2 in baud rate generator mode.

The baud rate generation mode is like the auto-reload mode, when a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2H and RCAP2L, which are preset by software.

The baud rates in modes 1 and 3 are determined by Timer 2's overflow rate given below:

Modes 1 and 3 baud rates = Timer 2 Overflow Rate / 16

The timer can be configured for either 'timer' or 'counter' operation. In many applications, it is configured for 'timer' operation ( $C/\overline{T}2=0$ ). Timer operation is different for Timer 2 when it is being used as a baud rate generator.

Usually, as a timer it would increment every machine cycle (i.e.,  $\frac{1}{6}$  the oscillator frequency). As a baud rate generator, it increments at the oscillator frequency. Thus the baud rate formula is as follows:

Modes 1 and 3 baud rates =

$$\frac{Oscillator\ Frequency}{(16 \times (65536 - (RCAP2H, RCAP2L)))}$$

(3)

Where: (RCAP2H, RCAP2L) = the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

The Timer 2 as a baud rate generator mode is valid only if RCLK and/or TCLK = 1 in T2CON register. Note that a rollover in TH2 does not set TF2, and will not generate an interrupt. Thus, the Timer 2 interrupt does not have to be disabled when Timer 2 is in the baud rate generator mode. Also if the EXEN2 (T2 external enable flag) is set, a 1-to-0 transition in T2EX (Timer/counter 2 trigger input) will set EXF2 (T2 external flag) but will

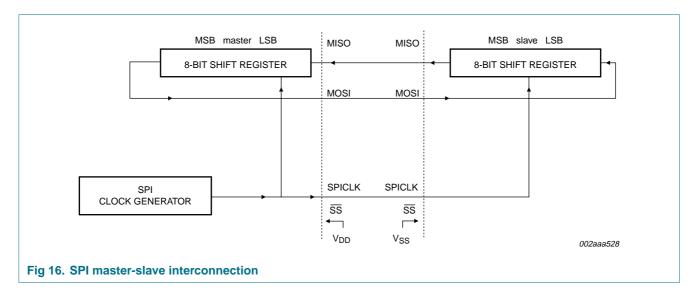

and slave SPI devices. The SPICLK pin is the clock output and input for the master and slave modes, respectively. The SPI clock generator will start following a write to the master devices SPI data register. The written data is then shifted out of the MOSI pin on the master device into the MOSI pin of the slave device. Following a complete transmission of one byte of data, the SPI clock generator is stopped and the SPIF flag is set. An SPI interrupt request will be generated if the SPI Interrupt Enable bit (SPIE) and the Serial Port Interrupt Enable bit (ES) are both set.

An external master drives the Slave Select input pin,  $\overline{SS}/P1[4]$ , low to select the SPI module as a slave. If  $\overline{SS}/P1[4]$  has not been driven low, then the slave SPI unit is not active and the MOSI/P1[5] port can also be used as an input port pin.

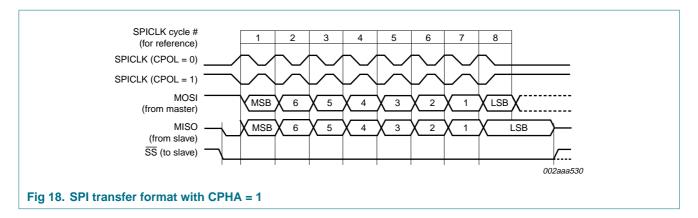

CPHA and CPOL control the phase and polarity of the SPI clock. <u>Figure 17</u> and <u>Figure 18</u> show the four possible combinations of these two bits.

**Table 28. SPCTL - SPI control register (address D5H) bit allocation** *Bit addressable; reset source(s): any reset; reset value: 0000 0000B.*

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| Symbol | SPIE | SPEN | DORD | MSTR | CPOL | CPHA | PSC1 | PSC0 |

Table 29. SPCTL - SPI control register (address D5H) bit descriptions

| Bit | Symbol | Description                                                                                           |

|-----|--------|-------------------------------------------------------------------------------------------------------|

| 7   | SPIE   | If both SPIE and ES are set to one, SPI interrupts are enabled.                                       |

| 6   | SPEN   | SPI enable bit. When set enables SPI.                                                                 |

| 5   | DORD   | Data transmission order. 0 = MSB first; 1 = LSB first in data transmission.                           |

| 4   | MSTR   | Master/slave select. 1 = master mode, 0 = slave mode.                                                 |

| 3   | CPOL   | Clock polarity. 1 = SPICLK is high when idle (active LOW), 0 = SPICLK is low when idle (active HIGH). |

#### 6.8 Watchdog timer

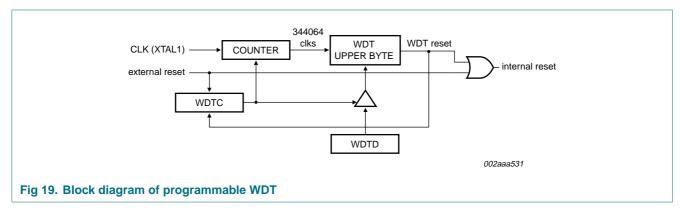

The device offers a programmable Watchdog Timer (WDT) for fail safe protection against software deadlock and automatic recovery.

To protect the system against software deadlock, the user software must refresh the WDT within a user-defined time period. If the software fails to do this periodical refresh, an internal hardware reset will be initiated if enabled (WDRE = 1). The software can be designed such that the WDT times out if the program does not work properly.

The WDT in the device uses the system clock (XTAL1) as its time base. So strictly speaking, it is a Watchdog counter rather than a WDT. The WDT register will increment every 344064 crystal clocks. The upper 8-bits of the time base register (WDTD) are used as the reload register of the WDT.

The WDTS flag bit is set by WDT overflow and is not changed by WDT reset. User software can clear WDTS by writing '1' to it.

<u>Figure 19</u> provides a block diagram of the WDT. Two SFRs (WDTC and WDTD) control WDT operation. During Idle mode, WDT operation is temporarily suspended, and resumes upon an interrupt exit from idle.

The time-out period of the WDT is calculated as follows:

Period =

$$(255 - WDTD) \times 344064 \times 1 / f_{CLK (XTAL1)}$$

where WDTD is the value loaded into the WDTD register and  $f_{\text{osc}}$  is the oscillator frequency.

Table 51. IP0H - Interrupt priority 0 high register (address B7H) bit descriptions

| Bit | Symbol | Description                                                     |

|-----|--------|-----------------------------------------------------------------|

| 7   | -      | Reserved for future use. Should be set to '0' by user programs. |

| 6   | PPCH   | PCA interrupt priority HIGH bit.                                |

| 5   | PT2H   | Timer 2 interrupt priority HIGH bit.                            |

| 4   | PSH    | Serial Port interrupt priority HIGH bit.                        |

| 3   | PT1H   | Timer 1 interrupt priority HIGH bit.                            |

| 2   | PX1H   | External interrupt 1 priority HIGH bit.                         |

| 1   | PT0H   | Timer 0 interrupt priority HIGH bit.                            |

| 0   | PX0H   | External interrupt 0 priority HIGH bit.                         |

### Table 52. IP1 - Interrupt priority 1 register (address F8H) bit allocation

Bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|--------|---|---|---|-----|---|---|---|---|

| Symbol | - | - | - | PBO | - | - | - | - |

Table 53. IP1 - Interrupt priority 1 register (address F8H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBO    | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

# Table 54. IP1H - Interrupt priority 1 high register (address F7H) bit allocation Not bit addressable; reset value: 00H.

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|--------|---|---|---|------|---|---|---|---|

| Symbol | - | - | - | PBOH | - | - | - | - |

#### Table 55. IP1H - Interrupt priority 1 high register (address F7H) bit descriptions

| Bit    | Symbol | Description                                                     |

|--------|--------|-----------------------------------------------------------------|

| 7 to 5 | -      | Reserved for future use. Should be set to '0' by user programs. |

| 4      | PBOH   | Brownout interrupt priority bit.                                |

| 3 to 0 | -      | Reserved for future use. Should be set to '0' by user programs. |

#### 6.12 Power-saving modes

The device provides two power saving modes of operation for applications where power consumption is critical. The two modes are Idle and Power-down, see Table 56.

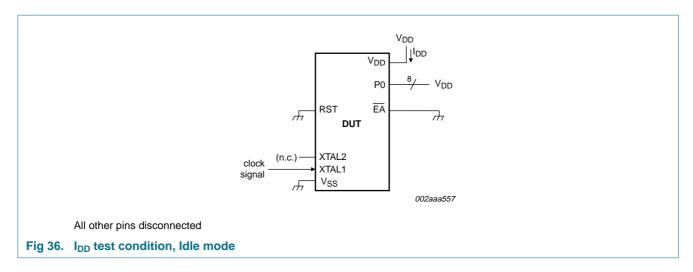

#### 6.12.1 Idle mode

Idle mode is entered by setting the IDL bit in the PCON register. In Idle mode, the Program Counter (PC) is stopped. The system clock continues to run and all interrupts and peripherals remain active. The on-chip RAM and the special function registers hold their data during this mode.

The device exits Idle mode through either a system interrupt or a hardware reset. When exiting Idle mode via system interrupt, the start of the interrupt clears the IDL bit and exits Idle mode. After exiting the Interrupt Service Routine, the interrupted program resumes execution beginning at the instruction immediately following the instruction which invoked the Idle mode. A hardware reset starts the device similar to a power-on reset.

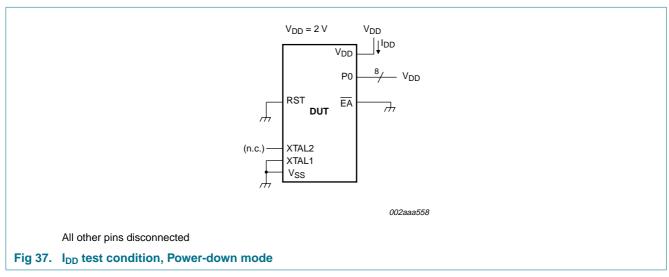

#### 6.12.2 Power-down mode

The Power-down mode is entered by setting the PD bit in the PCON register. In the Power-down mode, the clock is stopped and external interrupts are active for level sensitive interrupts only. SRAM contents are retained during Power-down mode, and the minimum  $V_{DD}$  level is 2.0 V.

The device exits Power-down mode through either an enabled external level sensitive interrupt or a hardware reset. The start of the interrupt clears the PD bit and exits Power-down. Holding the external interrupt pin low restarts the oscillator, the signal must hold low at least 1024 clock cycles before bringing back high to complete the exit. Upon interrupt signal restored to logic  $V_{IH}$ , the interrupt service routine program execution resumes beginning at the instruction immediately following the instruction which invoked Power-down mode. A hardware reset starts the device similar to power-on reset.

To exit properly out of Power-down mode, the reset or external interrupt should not be executed before the  $V_{DD}$  line is restored to its normal operating voltage. Be sure to hold  $V_{DD}$  voltage long enough at its normal operating level for the oscillator to restart and stabilize (normally less than 10 ms).

Table 56. Power-saving modes

| Mode               | Initiated by                                  | State of MCU                                                                                                                                                                                     | Exited by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle mode          | Software (Set IDL bit in PCON) MOV PCON, #01H | Clock is running. Interrupts, serial port and timers/counters are active. Program Counter is stopped. ALE and PSEN signals are HIGH level during Idle. All registers remain unchanged.           | Enabled interrupt or hardware reset. Start of interrupt clears IDL bit and exits Idle mode, after the ISR (Interrupt Service Routine) RETI (Return from Interrupt) instruction, program resumes execution beginning at the instruction following the one that invoked Idle mode. A user could consider placing two or three NOP (No Operation) instructions after the instruction that invokes Idle mode to eliminate any problems. A hardware reset restarts the device similar to a power-on reset. |

| Power-down<br>mode | Software (Set PD bit in PCON) MOV PCON, #02H  | Clock is stopped. On-chip SRAM and SFR data is maintained. ALE and PSEN signals are LOW level during power-down. External Interrupts are only active for level sensitive interrupts, if enabled. | Enabled external level sensitive interrupt or hardware reset. Start of interrupt clears PD bit and exits Power-down mode, after the ISR RETI instruction program resumes execution beginning at the instruction following the one that invoked Power-down mode. A user could consider placing two or three NOP instructions after the instruction that invokes Power-down mode to eliminate any problems. A hardware reset restarts the device similar to a power-on reset.                           |

# 9. Dynamic characteristics

Table 63. Dynamic characteristics

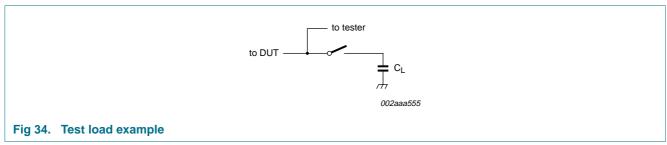

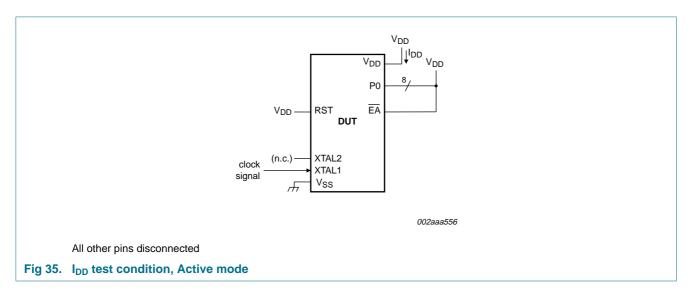

Over operating conditions: load capacitance for Port 0, ALE, and  $\overline{PSEN}$  = 100 pF; load capacitance for all other outputs = 80 pF;  $T_{amb}$  = 0 °C to +70 °C or -40 °C to +85 °C;  $V_{DD}$  = 2.7 V to 3.6 V at 33 MHz;  $V_{SS}$  = 0 V.[1][2]

| Symbol            | Parameter                                                            | Conditions | Min                            | Тур | Max                      | Unit |

|-------------------|----------------------------------------------------------------------|------------|--------------------------------|-----|--------------------------|------|

| f <sub>osc</sub>  | oscillator frequency                                                 | X1 mode    | 0                              | -   | 33                       | MHz  |

|                   |                                                                      | X2 mode    | 0                              | -   | 16                       | MHz  |

|                   |                                                                      | IAP        | 0.25                           | -   | 33                       | MHz  |

| t <sub>LHLL</sub> | ALE pulse width                                                      |            | $2T_{cy(clk)} - 15$            | -   | -                        | ns   |

| t <sub>AVLL</sub> | address valid to ALE LOW time                                        |            | $T_{\text{cy(clk)}} - 25$      | -   | -                        | ns   |

| $t_{LLAX}$        | address hold after ALE LOW time                                      |            | $T_{\text{cy}(\text{clk})}-25$ | -   | -                        | ns   |

| t <sub>LLIV</sub> | ALE LOW to valid instruction in time                                 |            | -                              | -   | $4T_{cy(clk)} - 65$      | ns   |

| $t_{LLPL}$        | ALE LOW to PSEN LOW time                                             |            | $T_{\text{cy(clk)}} - 25$      | -   | -                        | ns   |

| t <sub>PLPH</sub> | PSEN pulse width                                                     |            | $T_{\text{cy(clk)}} - 25$      | -   | -                        | ns   |

| t <sub>PLIV</sub> | PSEN LOW to valid instruction in time                                |            | -                              | -   | $3T_{cy(clk)} - 55$      | ns   |

| t <sub>PXIX</sub> | input instruction hold after $\overline{\text{PSEN}}$ time           |            | 0                              | -   | -                        | ns   |

| t <sub>PXIZ</sub> | input instruction float after $\overline{\text{PSEN}}$ time          |            | -                              | -   | $T_{\text{cy(clk)}} - 5$ | ns   |

| t <sub>PXAV</sub> | PSEN to address valid time                                           |            | $T_{cy(clk)} - 8$              | -   | -                        | ns   |

| t <sub>AVIV</sub> | address to valid instruction in time                                 |            | -                              | -   | $5T_{cy(clk)} - 80$      | ns   |

| t <sub>PLAZ</sub> | PSEN LOW to address float time                                       |            | -                              | -   | 10                       | ns   |

| t <sub>RLRH</sub> | RD LOW pulse width                                                   |            | $6T_{cy(clk)} - 40$            | -   | -                        | ns   |

| $t_{WLWH}$        | WR LOW pulse width                                                   |            | $6T_{cy(clk)} - 40$            | -   | -                        | ns   |

| $t_{RLDV}$        | RD LOW to valid data in time                                         |            | -                              | -   | $5T_{cy(clk)} - 90$      | ns   |

| t <sub>RHDX</sub> | data hold after $\overline{RD}$ time                                 |            | 0                              | -   | -                        | ns   |

| t <sub>RHDZ</sub> | data float after RD time                                             |            | -                              | -   | $2T_{cy(clk)} - 25$      | ns   |

| $t_{LLDV}$        | ALE LOW to valid data in time                                        |            | -                              | -   | $8T_{cy(clk)} - 90$      | ns   |

| $t_{AVDV}$        | address to valid data in time                                        |            | -                              | -   | $9T_{cy(clk)} - 90$      | ns   |

| t <sub>LLWL</sub> | ALE LOW to $\overline{\text{RD}}$ or $\overline{\text{WR}}$ LOW time |            | $3T_{cy(clk)} - 25$            | -   | $3T_{cy(clk)} + 25$      | ns   |

| t <sub>AVWL</sub> | address to $\overline{\text{RD}}$ or $\overline{\text{WR}}$ LOW time |            | $4T_{cy(clk)}-75$              | -   | -                        | ns   |

| t <sub>WHQX</sub> | data hold after WR time                                              |            | $T_{\text{cy(clk)}} - 27$      | -   | -                        | ns   |

| t <sub>QVWH</sub> | data output valid to WR HIGH time                                    |            | $7T_{cy(clk)} - 70$            | -   | -                        | ns   |

| t <sub>RLAZ</sub> | RD LOW to address float time                                         |            | -                              | -   | 0                        | ns   |

| t <sub>WHLH</sub> | RD or WR HIGH to ALE HIGH time                                       |            | T <sub>cy(clk)</sub> – 25      | -   | $T_{cy(clk)} + 25$       | ns   |

<sup>[1]</sup>  $T_{cy(clk)} = 1 / f_{osc}$ .

<sup>[2]</sup> Calculated values are for 6-clock mode only.

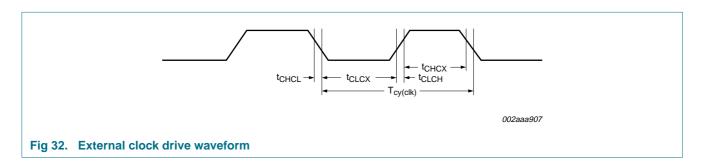

Table 64. External clock drive

| Symbol               | Parameter            | Oscillator |     |                          |                   |     |

|----------------------|----------------------|------------|-----|--------------------------|-------------------|-----|

|                      |                      | 12 MHz     |     | Variable                 |                   |     |

|                      |                      | Min        | Max | Min                      | Max               |     |

| f <sub>osc</sub>     | oscillator frequency | -          | -   | 0                        | 33                | MHz |

| T <sub>cy(clk)</sub> | clock cycle time     | 83         | -   | -                        | -                 | ns  |

| t <sub>CHCX</sub>    | clock HIGH time      | -          | -   | 0.35T <sub>cy(clk)</sub> | $0.65T_{cy(clk)}$ | ns  |

| t <sub>CLCX</sub>    | clock LOW time       | -          | -   | 0.35T <sub>cy(clk)</sub> | $0.65T_{cy(clk)}$ | ns  |

| t <sub>CLCH</sub>    | clock rise time      | -          | 20  | -                        | -                 | ns  |

| t <sub>CHCL</sub>    | clock fall time      | -          | 20  | -                        | -                 | ns  |

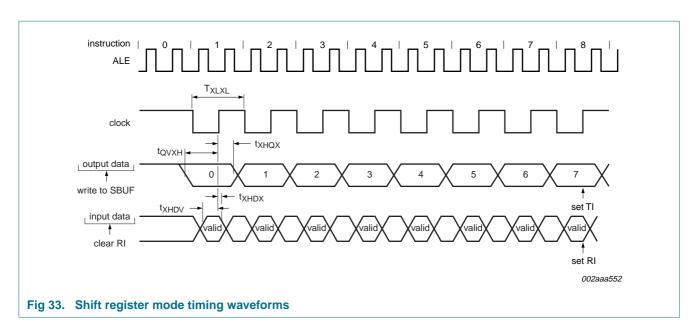

Table 65. Serial port timing

| Symbol            | Parameter                                     | Oscillator |     |                            |                            | Unit |

|-------------------|-----------------------------------------------|------------|-----|----------------------------|----------------------------|------|

|                   |                                               | 12 MHz     |     | Variable                   |                            |      |

|                   |                                               | Min        | Max | Min                        | Max                        |      |

| $T_{XLXL}$        | serial port clock cycle time                  | 1.0        | -   | 12T <sub>cy(clk)</sub>     | -                          | μs   |

| t <sub>QVXH</sub> | output data set-up to clock rising edge time  | 700        | -   | $10T_{\text{cy(clk)}}-133$ | -                          | ns   |

| t <sub>XHQX</sub> | output data hold after clock rising edge time | 50         | -   | $2T_{cy(clk)} - 50$        | -                          | ns   |

| $t_{XHDX}$        | input data hold after clock rising edge time  | 0          | -   | 0                          | -                          | ns   |

| t <sub>XHDV</sub> | input data valid to clock rising edge time    | -          | 700 | -                          | $10T_{\text{cy(clk)}}-133$ | ns   |

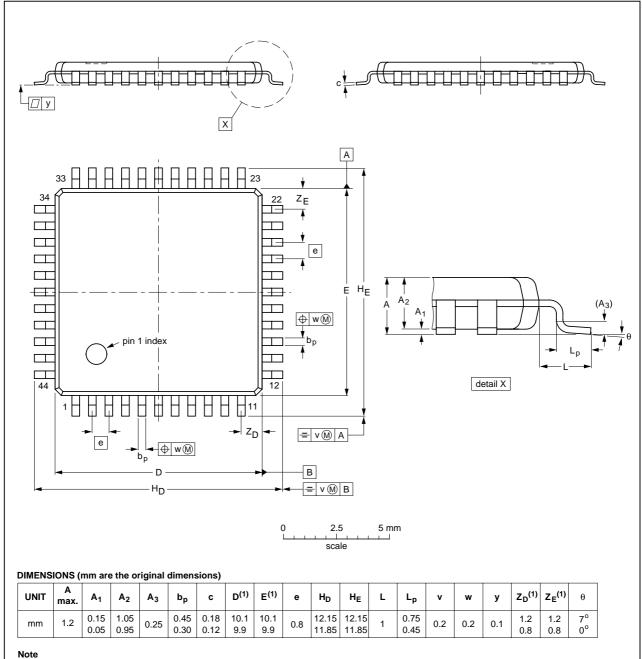

TQFP44: plastic thin quad flat package; 44 leads; body 10 x 10 x 1.0 mm

SOT376-1

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  | OUTLINE REFERENCES |        |       |  | EUROPEAN   | ISSUE DATE                        |  |

|----------|--------------------|--------|-------|--|------------|-----------------------------------|--|

| VERSION  | IEC                | JEDEC  | JEITA |  | PROJECTION | ISSUE DATE                        |  |

| SOT376-1 | 137E08             | MS-026 |       |  |            | <del>-00-01-19-</del><br>02-03-14 |  |

Fig 39. Package outline SOT376-1 (TQFP44)

## 11. Abbreviations

Table 66. Abbreviations

| Acronym | Description                                 |

|---------|---------------------------------------------|

| DUT     | Device Under Test                           |

| EMI     | Electro-Magnetic Interference               |

| IAP     | In-Application Programming                  |

| ISP     | In-System Programming                       |

| MCU     | Microcontroller Unit                        |

| PCA     | Programmable Counter Array                  |

| PWM     | Pulse Width Modulator                       |

| RC      | Resistance-Capacitance                      |

| SFR     | Special Function Register                   |

| SPI     | Serial Peripheral Interface                 |

| TTL     | Transistor-Transistor Logic                 |

| UART    | Universal Asynchronous Receiver/Transmitter |