## E·XFL

### NXP USA Inc. - P87LPC769HD,518 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                   |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                            |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                               |

| Data Converters            | A/D 4x8b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 20-50                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87lpc769hd-518 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### P87LPC769

| ADCON A         | ddress: C0h  | 7                                                                                                                                                                            | 6                                                                                                                                                                                                                                       | 5             | 4            | 3            | 2           | 1          | 0              |  |  |  |

|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|--------------|-------------|------------|----------------|--|--|--|

| Bit addressable | e            | ENADC                                                                                                                                                                        | ENDAC1                                                                                                                                                                                                                                  | ENDAC0        | ADCI         | ADCS         | RCCLK       | AADR1      | AADR0          |  |  |  |

| Reset Value: 0  | Oh           |                                                                                                                                                                              |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

| BIT             | SYMBOL       | FUNCTION                                                                                                                                                                     |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

| ADCON.7         | ENADC        |                                                                                                                                                                              | When ENADC = 1, the A/D is enabled and conversions may take place. Must be set 10 microseconds before a conversion is started. ENADC cannot be cleared while ADCS or ADCI are 1.                                                        |               |              |              |             |            |                |  |  |  |

| ADCON.6         | ENDAC1       |                                                                                                                                                                              | When ENDAC=1, DAC1 is enabled to provide an analog output voltage. Refer to the section Digital to Analog Converter (DAC) Outputs for details.                                                                                          |               |              |              |             |            |                |  |  |  |

| ADCON.5         | ENDAC0       | and ADCI are                                                                                                                                                                 | When ENDAC=1, DAC0 is enabled to provide an analog output voltage. Writable while ADCS and ADCI are 0. Refer to the section Digital to Analog Converter (DAC) Outputs for details. ENADC and ENDAC0 should not be set at the same time. |               |              |              |             |            |                |  |  |  |

| ADCON.4         | ADCI         |                                                                                                                                                                              | A/D conversion complete/interrupt flag. This flag is set when an A/D conversion is completed. This bit will cause a hardware interrupt if enabled and of sufficient priority. Must be cleared by software.                              |               |              |              |             |            |                |  |  |  |

| ADCON.3         | ADCS         | A/D start. Set<br>remains set with<br>completion. W                                                                                                                          | hile the A/                                                                                                                                                                                                                             | D conversion  | n is in prog | gress and is | cleared aut | omatically | •              |  |  |  |

|                 | ADCI, ADCS   | A/D Status                                                                                                                                                                   |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

|                 | 0 0          | A/D not busy,                                                                                                                                                                | a convers                                                                                                                                                                                                                               | ion can be st | arted.       |              |             |            |                |  |  |  |

|                 | 0 1          | A/D busy, the                                                                                                                                                                | A/D busy, the start of a new conversion is blocked.                                                                                                                                                                                     |               |              |              |             |            |                |  |  |  |

|                 | 1 0          | An A/D conversion is complete. ADCI must be cleared prior to starting a new conversion.                                                                                      |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

|                 | 11           | An A/D conve<br>state exists for                                                                                                                                             |                                                                                                                                                                                                                                         |               |              |              |             |            | nversion. This |  |  |  |

| ADCON.2         | RCCLK        | When RCCLK = 0, the CPU clock is used as the A/D clock. When RCCLK = 1, the internal RC oscillator is used as the A/D clock. This bit is writable while ADCS and ADCI are 0. |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

| ADCON.1, 0      | AADR1,0      | Along with AADR0, selects the A/D channel to be converted. These bits can only be written while ADCS and ADCI are 0.                                                         |                                                                                                                                                                                                                                         |               |              |              |             |            | y be written   |  |  |  |

|                 | AADR1, AADR0 | A/D Input Sel                                                                                                                                                                | ected                                                                                                                                                                                                                                   |               |              |              |             |            |                |  |  |  |

|                 | 0 0          | AD0 (P0.3).                                                                                                                                                                  |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

|                 | 0 1          | AD1 (P0.4).                                                                                                                                                                  |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

|                 | 1 0          | AD2 (P0.5).                                                                                                                                                                  |                                                                                                                                                                                                                                         |               |              |              |             |            |                |  |  |  |

|                 | 11           | AD3 (P0.6).                                                                                                                                                                  |                                                                                                                                                                                                                                         |               |              |              |             |            | SU01370        |  |  |  |

#### Figure 2. A/D Control Register (ADCON)

#### A/D Timing

The A/D may be clocked in one of two ways. The default is to use the CPU clock as the A/D clock source. When used in this manner, the A/D completes a conversion in 31 machine cycles. The A/D may be operated up to the maximum CPU clock rate of 20 MHz, giving a conversion time of 9.3  $\mu$ s. The formula for calculating A/D conversion time when the CPU clock runs the A/D is: 186  $\mu$ s / CPU clock rate (in MHZ). To obtain accurate A/D conversion results, the CPU clock must be at least 1 MHz.

The A/D may also be clocked by the on-chip RC oscillator, even if the RC oscillator is not used as the CPU clock. This is accomplished by setting the RCCLK bit in ADCON. This arrangement has several advantages. First, the A/D conversion time is faster at lower CPU clock rates. Also, the CPU may be run at speeds below 1 MHz without affecting A/D accuracy. Finally, the Power Down mode may be used to completely shut down the CPU and its oscillator, along with other peripheral functions, in order to obtain the best possible A/D accuracy. This should not be used if the MCU uses an external clock source greater than 4 MHz.

When the A/D is operated from the RCCLK while the CPU is running from another clock source, 3 or 4 machine cycles are used to synchronize A/D operation. The time can range from a minimum of 3 machine cycles (at the CPU clock rate) + 108 RC clocks to a maximum of 4 machine cycles (at the CPU clock rate) + 112 RC clocks.

Example A/D conversion times at various CPU clock rates are shown in Table 1. In Table 1, maximum times for RCCLK = 1 use an

### P87LPC769

RC clock frequency of 4.5 MHz (6 MHz - 25%). Minimum times for RCCLK = 1 use an RC clock frequency of 7.5 MHz (6 MHz + 25%).

#### Table 1. Example A/D Conversion Times

| CPU Clock Rate | RCCLK = 0 | RCCLK = 1 |         |         |  |  |  |  |  |

|----------------|-----------|-----------|---------|---------|--|--|--|--|--|

|                | KCCLK = 0 | minimum   | nominal | maximum |  |  |  |  |  |

| 32 kHz         | NA        | 563.4 μs  | 659 μs  | 757 μs  |  |  |  |  |  |

| 1 MHz          | 186 µs    | 32.4 μs   | 39.3 μs | 48.9 μs |  |  |  |  |  |

| 4 MHz          | 46.5 μs   | 18.9 μs   | 23.6 µs | 30.1 μs |  |  |  |  |  |

Note: Do not clock ADC from the RC oscillator when MCU clock is greater than 4 MHz.

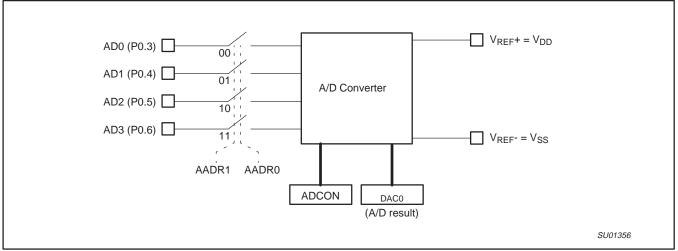

Figure 3. A/D Converter Connections

#### The A/D in Power Down and Idle Modes

While using the CPU clock as the A/D clock source, the Idle mode may be used to conserve power and/or to minimize system noise during the conversion. CPU operation will resume and Idle mode terminate automatically when a conversion is complete if the A/D interrupt is active. In Idle mode, noise from the CPU itself is eliminated, but noise from the oscillator and any other on-chip peripherals that are running will remain.

The CPU may be put into Power Down mode when the A/D is clocked by the on-chip RC oscillator (RCCLK=1). This mode gives the best possible A/D accuracy by eliminating most on-chip noise sources.

If the Power Down mode is entered while the A/D is running from the CPU clock (RCCLK=0), the A/D will abort operation and will not wake up the CPU. The contents of DAC0 will be invalid when operation does resume.

When an A/D conversion is started, Power Down or Idle mode must be activated within two machine cycles in order to have the most accurate A/D result. These two machine cycles are counted at the CPU clock rate. When using the A/D with either Power Down or Idle mode, care must be taken to insure that the CPU is not restarted by another interrupt until the A/D conversion is complete. The possible causes of wakeup are different in Power Down and Idle modes.

Nominal time assume an ideal RC clock frequency of 6 MHz and an

average of 3.5 machine cycles at the CPU clock rate.

A/D accuracy is also affected by noise generated elsewhere in the application, power supply noise, and power supply regulation. Since the P87LPC769 power pins are also used as the A/D reference and supply, the power supply has a very direct affect on the accuracy of A/D readings. Using the A/D without Power Down mode while the clock is divided through the use of CLKR or DIVM has an adverse effect on A/D accuracy.

;

### P87LPC769

#### Code Examples for the A/D

The first piece of sample code shows an example of port configuration for use with the A/D. This example sets up the pins so that all four A/D channels may be used. Port configuration for analog functions is described in the section Analog Functions.

| ; | Set up | port pins for A/D | conversion, without affecting other pins.    |

|---|--------|-------------------|----------------------------------------------|

|   | mov    | PT0AD,#78h        | ; Disable digital inputs on A/D input pins.  |

|   | anl    | P0M2,#87h         | ; Disable digital outputs on A/D input pins. |

|   | orl    | P0M1,#78h         | ; Disable digital outputs on A/D input pins. |

Following is an example of using the A/D with interrupts. The routine ADStart begins an A/D conversion using the A/D channel number supplied in the accumulator. The channel number is not checked for validity. The A/D must previously have been enabled with sufficient time to allow for stabilization.

The interrupt handler routine reads the conversion value and returns it in memory address ADResult. The interrupt should be enabled prior to starting the conversion.

| ; Start A/D conversion.<br>ADStart: |                                                                |

|-------------------------------------|----------------------------------------------------------------|

| orl ADCON, A                        | ; Add in the new channel number.                               |

| setb ADCS                           | ; Start an A/D conversion.                                     |

| ; orl PCON,#01h                     | ; The CPU could be put into Idle mode here.                    |

| ; orl PCON,#02h<br>ret              | ; The CPU could be put into Power Down mode here if RCCLK = 1. |

| ; A/D interrupt handler<br>ADInt:   |                                                                |

| push ACC                            | ; Save accumulator.                                            |

| push | ACC         | ; Save accumulator.              |

|------|-------------|----------------------------------|

| mov  | A,DACO      | ; Get A/D result,                |

| mov  | ADResult,A  | ; and save it in memory.         |

| clr  | ADCI        | ; Clear the A/D completion flag. |

| anl  | ADCON,#0fch | ; Clear the A/D channel number.  |

| pop  | ACC         | ; Restore accumulator.           |

| reti |             |                                  |

Following is an example of using the A/D with polling. An A/D conversion is started using the channel number supplied in the accumulator. The channel number is not checked for validity. The A/D must previously have been enabled with sufficient time to allow for stabilization. The conversion result is returned in the accumulator.

| ADRead: |             |                                  |

|---------|-------------|----------------------------------|

| orl     | ADCON, A    | ; Add in the new channel number. |

| setb    | ADCS        | ; Start A/D conversion.          |

| ADChk:  |             |                                  |

| jnb     | ADCI, ADChk | ; Wait for ADCI to be set.       |

| mov     | A,DACO      | ; Get A/D result.                |

| clr     | ADCI        | ; Clear the A/D completion flag. |

| anl     | ADCON,#0fch | ; Clear the A/D channel number.  |

| ret     |             |                                  |

### P87LPC769

#### **Analog Comparators**

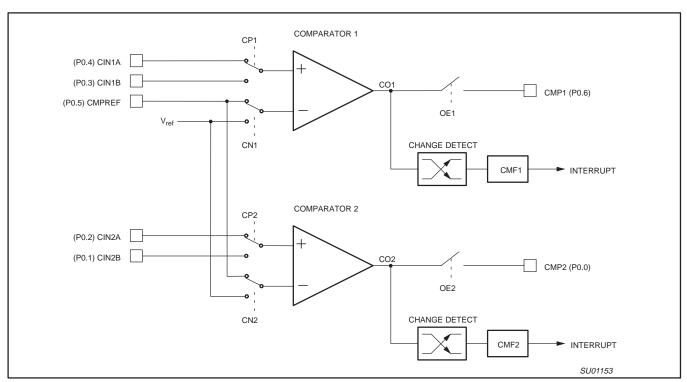

Two analog comparators are provided on the P87LPC769. Input and output options allow use of the comparators in a number of different configurations. Comparator operation is such that the output is a logical one (which may be read in a register and/or routed to a pin) when the positive input (one of two selectable pins) is greater than the negative input (selectable from a pin or an internal reference voltage). Otherwise the output is a zero. Each comparator may be configured to cause an interrupt when the output value changes.

#### **Comparator Configuration**

Each comparator has a control register, CMP1 for comparator 1 and CMP2 for comparator 2. The control registers are identical and are shown in Figure 5.

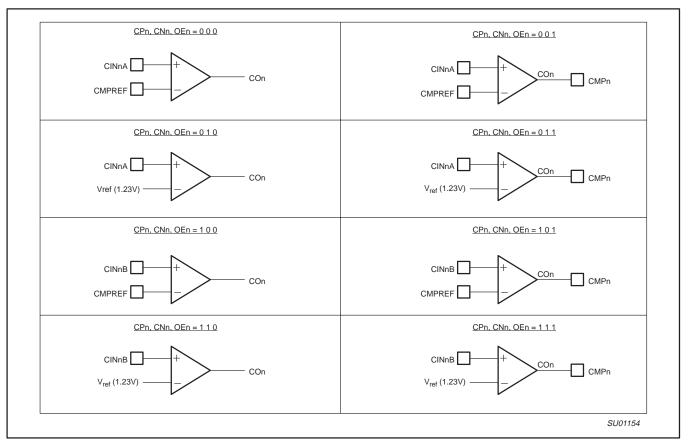

The overall connections to both comparators are shown in Figure 6. There are eight possible configurations for each comparator, as determined by the control bits in the corresponding CMPn register: CPn, CNn, and OEn. These configurations are shown in Figure 7.

When each comparator is first enabled, the comparator output and interrupt flag are not guaranteed to be stable for 10 microseconds. The corresponding comparator interrupt should not be enabled during that time, and the comparator interrupt flag must be cleared before the interrupt is enabled in order to prevent an immediate interrupt service.

| CMPn | Address: ACh for CMP1, ADh for CMP2 Reset Value: 00h |             |        |                                                                                                                                                                                                                                                           |            |          |                          |            |            |      |                          |

|------|------------------------------------------------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------------------------|------------|------------|------|--------------------------|

|      | Not Bit                                              | Addressable | e      |                                                                                                                                                                                                                                                           |            |          |                          |            |            |      |                          |

|      |                                                      |             | 7      | 6                                                                                                                                                                                                                                                         | 5          | 4        | 3                        | 2          | 1          | 0    |                          |

|      |                                                      |             | _      | —                                                                                                                                                                                                                                                         | CEn        | CPn      | CNn                      | OEn        | COn        | CMFn |                          |

|      |                                                      |             |        |                                                                                                                                                                                                                                                           |            |          |                          |            |            |      |                          |

| B    | T                                                    | SYMBOL      | FUNG   | CTION                                                                                                                                                                                                                                                     |            |          |                          |            |            |      |                          |

| CI   | MPn.7, 6                                             | _           | Rese   | rved for fu                                                                                                                                                                                                                                               | uture use. | Should n | ot be set t              | o 1 by use | er progran | ns.  |                          |

| CI   | MPn.5                                                | CEn         |        | Comparator enable. When set by software, the corresponding comparator function is enabled.<br>Comparator output is stable 10 microseconds after CEn is first set.                                                                                         |            |          |                          |            |            |      |                          |

| CI   | MPn.4                                                | CPn         |        | Comparator positive input select. When 0, CINnA is selected as the positive comparator input. When 1, CINnB is selected as the positive comparator input.                                                                                                 |            |          |                          |            |            |      |                          |

| CI   | MPn.3                                                | CNn         | the ne | Comparator negative input select. When 0, the comparator reference pin CMPREF is selected as the negative comparator input. When 1, the internal comparator reference $V_{ref}$ is selected as the negative comparator input.                             |            |          |                          |            |            |      |                          |

| CI   | MPn.2                                                | OEn         |        |                                                                                                                                                                                                                                                           |            |          | arator outp<br>asynchror |            |            |      | pin if the comparator is |

| CI   | MPn.1                                                | COn         |        | Comparator output, synchronized to the CPU clock to allow reading by software. Cleared when the comparator is disabled (CEn = 0).                                                                                                                         |            |          |                          |            |            |      |                          |

| CI   | MPn.0                                                | CMFn        | state. | Comparator interrupt flag. This bit is set by hardware whenever the comparator output COn changes tate. This bit will cause a hardware interrupt if enabled and of sufficient priority. Cleared by oftware and when the comparator is disabled (CEn = 0). |            |          |                          |            |            |      |                          |

|      |                                                      |             |        |                                                                                                                                                                                                                                                           |            |          |                          |            |            |      | SU01152                  |

Figure 5. Comparator Control Registers (CMP1 and CMP2)

P87LPC769

## Low power, low price, low pin count (20 pin) microcontroller with 4 kB OTP 8-bit A/D, and DAC

Figure 6. Comparator Input and Output Connections

Figure 7. Comparator Configurations

| I2CON | Addres  | ss: D8h                |       |                                                                                                                                                     |             |              |             |             |                |             | Reset Value: 81h |

|-------|---------|------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-------------|-------------|----------------|-------------|------------------|

|       | Bit Add | dressable <sup>1</sup> | 7     | 6                                                                                                                                                   | 5           | 4            | 3           | 2           | 1              | 0           |                  |

|       |         | READ                   | RDAT  | ATN                                                                                                                                                 | DRDY        | ARL          | STR         | STP         | MASTER         | _           |                  |

|       |         | WRITE                  | CXA   | IDLE                                                                                                                                                | CDR         | CARL         | CSTR        | CSTP        | XSTR           | XSTP        |                  |

| В     | ΙТ      | SYMBOL                 | FUN   | CTION                                                                                                                                               |             |              |             |             |                |             | -                |

| 12    | CON.7   | RDAT                   | Read  | : the mos                                                                                                                                           | t recently  | received o   | data bit.   |             |                |             |                  |

|       | "       | CXA                    | Write | : clears th                                                                                                                                         | e transmi   | t active fla | g.          |             |                |             |                  |

| 12    | CON.6   | ATN                    | Read  | : ATN = 1                                                                                                                                           | if any of t | he flags D   | RDY, AR     | L, STR, o   | r STP = 1.     |             |                  |

|       | "       | IDLE                   |       | Write: in the I <sup>2</sup> C slave mode, writing a 1 to this bit causes the I <sup>2</sup> C hardware to ignore the bus until it is needed again. |             |              |             |             |                |             |                  |

| 12    | CON.5   | DRDY                   | Read  | : Data Re                                                                                                                                           | ady flag,   | set when t   | here is a   | rising edg  | e on SCL.      |             |                  |

|       | "       | CDR                    | Write | : writing a                                                                                                                                         | 1 to this I | oit clears t | he DRDY     | flag.       |                |             |                  |

| 12    | CON.4   | ARL                    | Read  | : Arbitrati                                                                                                                                         | on Loss fl  | ag, set wh   | en arbitra  | tion is los | t while in the | e transmit  | mode.            |

|       | "       | CARL                   | Write | : writing a                                                                                                                                         | 1 to this I | oit clears t | he CARL     | flag.       |                |             |                  |

| 12    | CON.3   | STR                    | Read  | : Start fla                                                                                                                                         | g, set whe  | n a start o  | ondition is | s detected  | d at a maste   | r or non-ie | dle slave.       |

|       | "       | CSTR                   | Write | : writing a                                                                                                                                         | 1 to this I | oit clears t | he STR fl   | ag.         |                |             |                  |

| 12    | CON.2   | STP                    | Read  | : Stop flag                                                                                                                                         | g, set whe  | n a stop c   | ondition is | s detected  | l at a maste   | r or non-io | dle slave.       |

|       | "       | CSTP                   | Write | : writing a                                                                                                                                         | 1 to this I | oit clears t | he STP fla  | ag.         |                |             |                  |

| 12    | CON.1   | MASTER                 | Read  | : indicate                                                                                                                                          | s whether   | this devic   | e is curre  | ntly as bu  | s master.      |             |                  |

|       | "       | XSTR                   | Write | Write: writing a 1 to this bit causes a repeated start condition to be generated.                                                                   |             |              |             |             |                |             |                  |

| 12    | CON.0   | _                      | Read  | : undefine                                                                                                                                          | ed.         |              |             |             |                |             |                  |

|       | "       | XSTP                   | Write | : writing a                                                                                                                                         | 1 to this I | oit causes   | a stop co   | ndition to  | be generate    | ed.         | SU01155          |

#### Figure 9. I<sup>2</sup>C Control Register (I2CON)

| I2DAT | Address: D9h      |       |                                                                                                                                                            |   |   |   |   |   |   | Reset Value: xxh |

|-------|-------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|------------------|

|       | Not Bit Addressat | ble   |                                                                                                                                                            |   |   |   |   |   |   |                  |

|       |                   | 7     | 6                                                                                                                                                          | 5 | 4 | 3 | 2 | 1 | 0 |                  |

|       | READ              | RDAT  | _                                                                                                                                                          | _ | _ | _ | _ | _ | _ |                  |

|       | WRITE             | XDAT  | _                                                                                                                                                          | _ | _ | _ | _ | _ | _ |                  |

| BIT   | SYMBOL            | . FUN | CTION                                                                                                                                                      |   |   |   |   |   |   |                  |

| I2DA  | AT.7 RDAT         |       | Read: the most recently received data bit, captured from SDA at every rising edge of SCL. Reading<br>I2DAT also clears DRDY and the Transmit Active state. |   |   |   |   |   |   |                  |

| "     | XDAT              |       | Write: sets the data for the next transmitted bit. Writing I2DAT also clears DRDY and sets the Transmit Active state.                                      |   |   |   |   |   |   |                  |

| I2DA  | AT.6—0 —          | Unus  | ed.                                                                                                                                                        |   |   |   |   |   |   | SU01             |

#### Figure 10. I<sup>2</sup>C Data Register (I2DAT)

#### **Checking ATN and DRDY**

When a program detects ATN = 1, it should next check DRDY. If DRDY = 1, then if it receives the last bit, it should capture the data from RDAT (in I2DAT or I2CON). Next, if the next bit is to be sent, it should be written to I2DAT. One way or another, it should clear DRDY and then return to monitoring ATN. Note that if any of ARL,

STR, or STP is set, clearing DRDY will not release SCL to high, so that the  $I^2C$  will not go on to the next bit. If a program detects ATN = 1, and DRDY = 0, it should go on to examine ARL, STR, and STP.

### P87LPC769

#### External Interrupt Inputs

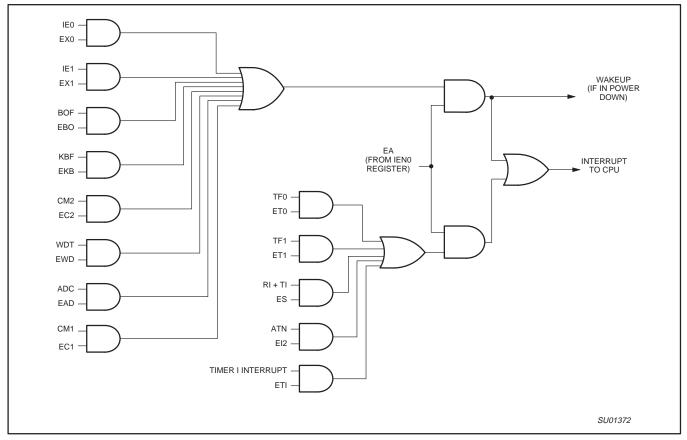

The P87LPC769 has two individual interrupt inputs as well as the Keyboard Interrupt function. The latter is described separately elsewhere in this section. The two interrupt inputs are identical to those present on the standard 80C51 microcontroller.

The external sources can be programmed to be level-activated or transition-activated by setting or clearing bit IT1 or IT0 in Register TCON. If ITn = 0, external interrupt n is triggered by a detected low at the  $\overline{\rm INTn}$  pin. If ITn = 1, external interrupt n is edge triggered. In this mode if successive samples of the  $\overline{\rm INTn}$  pin show a high in one cycle and a low in the next cycle, interrupt request flag IEn in TCON is set, causing an interrupt request.

Since the external interrupt pins are sampled once each machine cycle, an input high or low should hold for at least 6 CPU Clocks to ensure proper sampling. If the external interrupt is

transition-activated, the external source has to hold the request pin high for at least one machine cycle, and then hold it low for at least one machine cycle. This is to ensure that the transition is seen and that interrupt request flag IEn is set. IEn is automatically cleared by the CPU when the service routine is called.

If the external interrupt is level-activated, the external source must hold the request active until the requested interrupt is actually generated. If the external interrupt is still asserted when the interrupt service routine is completed another interrupt will be generated. It is not necessary to clear the interrupt flag IEn when the interrupt is level sensitive, it simply tracks the input pin level.

If an external interrupt is enabled when the P87LPC769 is put into Power Down or Idle mode, the interrupt will cause the processor to wake up and resume operation. Refer to the section on Power Reduction Modes for details.

Figure 12. Interrupt Sources, Interrupt Enables, and Power Down Wakeup Sources

## P87LPC769

#### I/O Ports

The P87LPC769 has 3 I/O ports, port 0, port 1, and port 2. The exact number of I/O pins available depend upon the oscillator and reset options chosen. At least 15 pins of the P87LPC769 may be used as I/Os when a two-pin external oscillator and an external reset circuit are used. Up to 18 pins may be available if fully on-chip oscillator and reset configurations are chosen.

All but three I/O port pins on the P87LPC769 may be software configured to one of four types on a bit-by-bit basis, as shown in Table 4. These are: quasi-bidirectional (standard 80C51 port outputs), push-pull, open drain, and input only. Two configuration registers for each port choose the output type for each port pin.

#### Table 5. Port Output Configuration Settings

| PxM1.y | PxM2.y | Port Output Mode            |

|--------|--------|-----------------------------|

| 0      | 0      | Quasi-bidirectional         |

| 0      | 1      | Push-Pull                   |

| 1      | 0      | Input Only (High Impedance) |

| 1      | 1      | Open Drain                  |

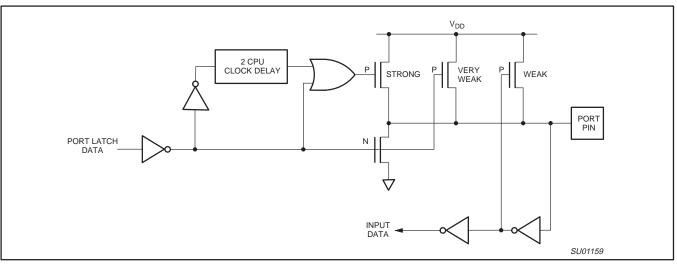

#### **Quasi-Bidirectional Output Configuration**

The default port output configuration for standard P87LPC769 I/O ports is the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an

input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes.

One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The very weak pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the "weak" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the weak pull-up turns off, and only the very weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the weak pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The quasi-bidirectional port configuration is shown in Figure 13.

Figure 13. Quasi-Bidirectional Output

## P87LPC769

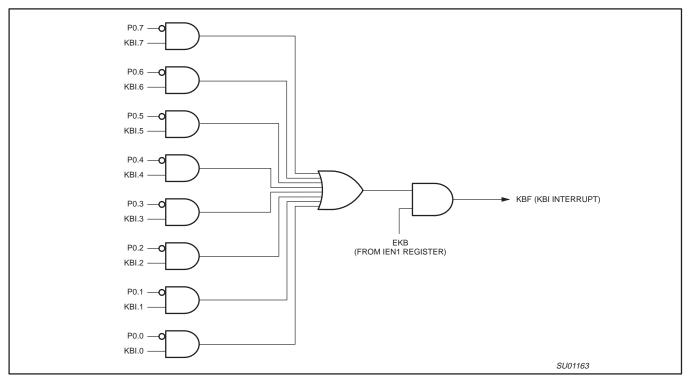

Figure 17. Keyboard Interrupt

| Not B | it Addressable |               |            |             |            |             |             |             |                       |

|-------|----------------|---------------|------------|-------------|------------|-------------|-------------|-------------|-----------------------|

|       |                |               |            |             |            |             |             |             |                       |

|       | 7              | 6             | 5          | 4           | 3          | 2           | 1           | 0           |                       |

|       | KBI.           | 7 KBI.6       | KBI.5      | KBI.4       | KBI.3      | KBI.2       | KBI.1       | KBI.0       |                       |

| BIT   | SYMBOL         | FUNCTION      |            |             |            |             |             |             |                       |

| KBI.7 | KBI.7          | When set, ena |            |             |            | board Int   | orrupt      |             |                       |

|       |                |               |            |             |            |             |             |             |                       |

| KBI.6 | KBI.6          | When set, ena |            |             |            |             |             |             |                       |

| KBI.5 | KBI.5          | When set, ena | bles P0.5  | as a caus   | e of a Key | board Inte  | errupt.     |             |                       |

| KBI.4 | KBI.4          | When set, ena | bles P0.4  | as a caus   | e of a Key | board Inte  | errupt.     |             |                       |

| KBI.3 | KBI.3          | When set, ena | bles P0.3  | as a caus   | e of a Key | board Inte  | errupt.     |             |                       |

| KBI.2 | KBI.2          | When set, ena | bles P0.2  | as a caus   | e of a Key | board Inte  | errupt.     |             |                       |

| KBI.1 | KBI.1          | When set, ena | bles P0.1  | as a caus   | e of a Key | board Inte  | errupt.     |             |                       |

| KBI.0 | KBI.0          | When set, ena | bles P0.0  | as a caus   | e of a Key | /board Inte | errupt.     |             |                       |

|       | Keyboard Inter |               | bled in or | der for the | e settings | of the KBI  | register to | be effectiv | e. The interrupt flag |

Figure 18. Keyboard Interrupt Register (KBI)

### P87LPC769

#### Oscillator

The P87LPC769 provides several user selectable oscillator options, allowing optimization for a range of needs from high precision to lowest possible cost. These are configured when the EPROM is

programmed. Basic oscillator types that are supported include: low, medium, and high speed crystals, covering a range from 20 kHz to 10 MHz; ceramic resonators; and on-chip RC oscillator.

#### Low Frequency Oscillator Option

This option supports an external crystal in the range of 20 kHz to 100 kHz.

Table 6 shows capacitor values that may be used with a quartz crystal in this mode.

#### Table 6. Recommended oscillator capacitors for use with the low frequency oscillator option

| Oscillator |             | V <sub>DD</sub> = 4.5 to 5.5 V |             |  |  |  |  |  |

|------------|-------------|--------------------------------|-------------|--|--|--|--|--|

| Frequency  | Lower Limit | Optimal Value                  | Upper Limit |  |  |  |  |  |

| 20 kHz     | 33 pF       | 33 pF                          | 47 pF       |  |  |  |  |  |

| 32 kHz     | 33 pF       | 33 pF                          | 47 pF       |  |  |  |  |  |

| 100 kHz    | 15 pF       | 15 pF                          | 33 pF       |  |  |  |  |  |

#### **Medium Frequency Oscillator Option**

This option supports an external crystal in the range of 100 kHz to 4 MHz. Ceramic resonators are also supported in this configuration.

Table 7 shows capacitor values that may be used with a quartz crystal in this mode.

#### Table 7. Recommended oscillator capacitors for use with the medium frequency oscillator option

| Oscillator Frequency |             | V <sub>DD</sub> = 4.5 to 5.5 V |             |  |  |  |  |  |

|----------------------|-------------|--------------------------------|-------------|--|--|--|--|--|

| Oscillator Frequency | Lower Limit | Optimal Value                  | Upper Limit |  |  |  |  |  |

| 100 kHz              | 33 pF       | 33 pF                          | 47 pF       |  |  |  |  |  |

| 1 MHz                | 15 pF       | 15 pF                          | 33 pF       |  |  |  |  |  |

| 4 MHz                | 15 pF       | 15 pF                          | 33 pF       |  |  |  |  |  |

#### **High Frequency Oscillator Option**

This option supports an external crystal in the range of 4 to 10 MHz. Ceramic resonators are also supported in this configuration.

Table 8 shows capacitor values that may be used with a quartz crystal in this mode.

#### Table 8. Recommended oscillator capacitors for use with the high frequency oscillator option

| Oscillator |             | V <sub>DD</sub> = 4.5 to 5.5 V |             |  |  |  |  |  |

|------------|-------------|--------------------------------|-------------|--|--|--|--|--|

| Frequency  | Lower Limit | Optimal Value                  | Upper Limit |  |  |  |  |  |

| 4 MHz      | 15 pF       | 33 pF                          | 68 pF       |  |  |  |  |  |

| 8 MHz      | 15 pF       | 33 pF                          | 47 pF       |  |  |  |  |  |

#### **On-Chip RC Oscillator Option**

The on-chip RC oscillator option has a typical frequency of 6 MHz and can be divided down for slower operation through the use of the DIVM register. Note that the on-chip oscillator has a  $\pm 25\%$  frequency tolerance and for that reason may not be suitable for use in some applications. A clock output on the X2/P2.0 pin may be enabled when the on-chip RC oscillator is used.

#### **External Clock Input Option**

In this configuration, the processor clock is input from an external source driving the X1/P2.1 pin. The rate may be from 0 Hz up to 10 MHz. When the external clock input mode is used, the X2/P2.0 pin may be used as a standard port pin. A clock output on the X2/P2.0 pin may be enabled when the external clock input is used.

#### **Clock Output**

The P87LPC769 supports a clock output function when either the on-chip RC oscillator or external clock input options are selected. This allows external devices to synchronize to the P87LPC769. When enabled, via the ENCLK bit in the P2M1 register, the clock output appears on the X2/CLKOUT pin whenever the on-chip oscillator is running, including in Idle mode. The frequency of the clock output is 1/6 of the CPU clock rate. If the clock output is not needed in Idle mode, it may be turned off prior to entering Idle, saving additional power. The clock output may also be enabled when the external clock input option is selected.

### P87LPC769

For correct activation of Brownout Detect, the V<sub>DD</sub> fall time must be no faster than 50 mV/ $\mu$ s. When V<sub>DD</sub> is restored, is should not rise faster than 2 mV/ $\mu$ s in order to insure a proper reset.

The brownout voltage (BOV) bit in the EPROM configuration register UCFG1 must be programmed to a zero.

If the Brownout Detect function is not required in an application, it may be disabled, thus saving power. Brownout Detect is disabled by setting the control bit BOD in the AUXR1 register (AUXR1.6).

#### Power On Detection

The Power On Detect has a function similar to the Brownout Detect, but is designed to work as power comes up initially, before the power supply voltage reaches a level where Brownout Detect can work. When this feature is activated, the POF flag in the PCON register is set to indicate an initial power up condition. The POF flag will remain set until cleared by software.

#### **Power Reduction Modes**

The P87LPC769 supports Idle and Power Down modes of power reduction.

#### Idle Mode

The Idle mode leaves peripherals running in order to allow them to activate the processor when an interrupt is generated. Any enabled interrupt source or Reset may terminate Idle mode. Idle mode is entered by setting the IDL bit in the PCON register (see Figure 22).

#### Power Down Mode

The Power Down mode stops the oscillator in order to absolutely minimize power consumption. Power Down mode is entered by setting the PD bit in the PCON register (see Figure 22).

The processor can be made to exit Power Down mode via Reset or one of the interrupt sources shown in Table 5. This will occur if the interrupt is enabled and its priority is higher than any interrupt currently in progress.

In Power Down mode, the power supply voltage may be reduced to the RAM keep-alive voltage V<sub>RAM</sub>. This retains the RAM contents at the point where Power Down mode was entered. SFR contents are not guaranteed after V<sub>DD</sub> has been lowered to V<sub>RAM</sub>, therefore it is recommended to wake up the processor via Reset in this case. V<sub>DD</sub> must be raised to within the operating range before the Power Down mode is exited. Since the watchdog timer has a separate oscillator, it may reset the processor upon overflow if it is running during Power Down.

Note that if the Brownout Detect reset is enabled, the processor will be put into reset as soon as  $V_{DD}$  drops below the brownout voltage. If Brownout Detect is configured as an interrupt and is enabled, it will wake up the processor from Power Down mode when  $V_{DD}$  drops below the brownout voltage.

When the processor wakes up from Power Down mode, it will start the oscillator immediately and begin execution when the oscillator is stable. Oscillator stability is determined by counting 1024 CPU clocks after start-up when one of the crystal oscillator configurations is used, or 256 clocks after start-up for the internal RC or external clock input configurations.

Some chip functions continue to operate and draw power during Power Down mode, increasing the total power used during Power Down. These include the Brownout Detect, Watchdog Timer, Comparators, and A/D converter.

| PCON |       | ss: 87h<br>t Addressable |                                  |            |              |              |            | Reset Val    | • 20      | h for a Power On reset<br>h for a Brownout reset<br>h for other reset sources |

|------|-------|--------------------------|----------------------------------|------------|--------------|--------------|------------|--------------|-----------|-------------------------------------------------------------------------------|

|      |       | 7                        | 6                                | 5          | 4            | 3            | 2          | 1            | 0         | _                                                                             |

|      |       | SMO                      | D1 SMOD0                         | BOF        | POF          | GF1          | GF0        | PD           | IDL       |                                                                               |

| В    | п     | SYMBOL                   | FUNCTION                         |            |              |              |            |              |           |                                                                               |

| P    | CON.7 | SMOD1                    | When set, this                   | bit double | es the UAI   | RT baud ra   | ate for mo | des 1, 2, ar | nd 3.     |                                                                               |

| P    | CON.6 | SMOD0                    | This bit selects SCON.7 is the   |            |              |              |            |              |           | the SM0 bit. When 1, ation.                                                   |

| P    | CON.5 | BOF                      |                                  |            |              |              |            |              |           | occurred. Also set at<br>ection for additional                                |

| P    | CON.4 | POF                      | Power On Flag<br>to the Power N  |            |              |              |            |              |           | eared by software. Refer                                                      |

| P    | CON.3 | GF1                      | General purpo                    | se flag 1. | May be re    | ad or writ   | ten by use | er software, | but has r | o effect on operation.                                                        |

| P    | CON.2 | GF0                      | General purpo                    | se flag 0. | May be re    | ad or writ   | ten by use | er software, | but has r | o effect on operation.                                                        |

| P    | CON.1 | PD                       | Power Down c<br>Power Down m     |            |              |              | ates Pow   | er Down mo   | ode opera | tion. Cleared when the                                                        |

| P    | CON.0 | IDL                      | Idle mode cont<br>terminated (se |            | tting this t | oit activate | es Idle mo | de operatio  | n. Cleare | d when the Idle mode is<br>SU01168                                            |

Figure 22. Power Control Register (PCON)

### P87LPC769

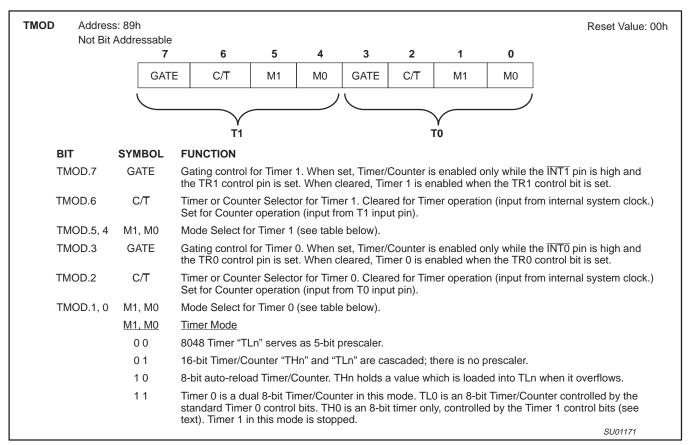

#### **Timer/Counters**

The P87LPC769 has two general purpose counter/timers which are upward compatible with the standard 80C51 Timer 0 and Timer 1. Both can be configured to operate either as timers or event counters (see Figure 25). An option to automatically toggle the T0 and/or T1 pins upon timer overflow has been added.

In the "Timer" function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of 6 CPU clock periods, the count rate is 1/6 of the CPU clock frequency. Refer to the section Enhanced CPU for a description of the CPU clock.

In the "Counter" function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once during every machine cycle. When the samples of the pin state show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (12 CPU clocks) to recognize a 1-to-0 transition, the maximum count rate is 1/6 of the CPU clock frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

The "Timer" or "Counter" function is selected by control bits C/T in the Special Function Register TMOD. In addition to the "Timer" or "Counter" selection, Timer 0 and Timer 1 have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text.

Figure 25. Timer/Counter Mode Control Register (TMOD)

### P87LPC769

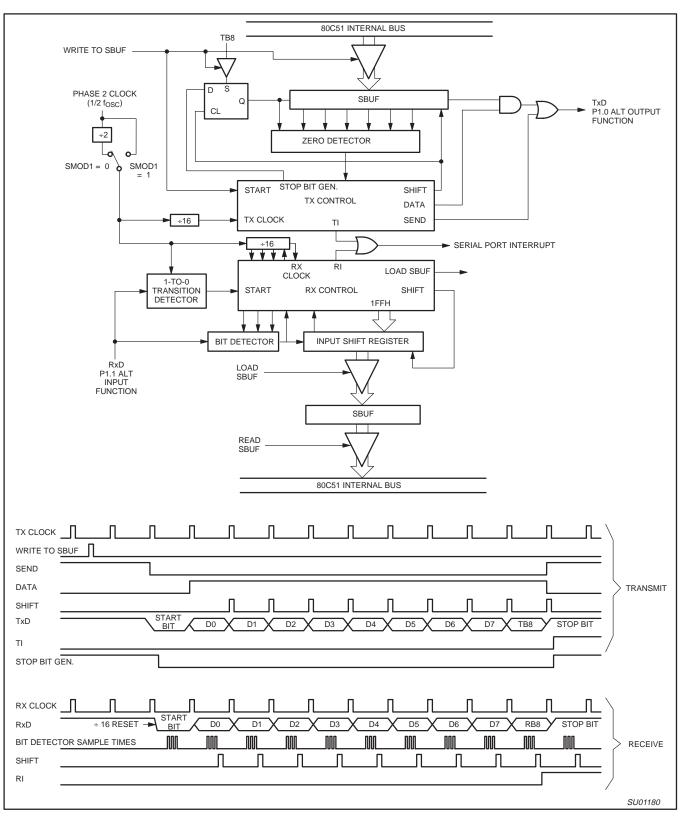

#### **Baud Rates**

The baud rate in Mode 0 is fixed: Mode 0 Baud Rate = CPU clock/6. The baud rate in Mode 2 depends on the value of bit SMOD1 in Special Function Register PCON. If SMOD1 = 0 (which is the value on reset), the baud rate is 1/32 of the CPU clock frequency. If SMOD1 = 1, the baud rate is 1/16 of the CPU clock frequency.

Mode 2 Baud Rate =

$$\frac{1 + \text{SMOD1}}{32} \times \text{CPU}$$

clock frequency

#### Using Timer 1 to Generate Baud Rates

When Timer 1 is used as the baud rate generator, the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate and the value of SMOD1. The Timer 1 interrupt should be disabled in this

application. The Timer itself can be configured for either "timer" or "counter" operation, and in any of its 3 running modes. In the most typical applications, it is configured for "timer" operation, in the auto-reload mode (high nibble of TMOD = 0010b). In that case the baud rate is given by the formula:

Mode 1, 3 Baud Rate =  $\frac{\begin{array}{c} \text{CPU clock frequency/} \\ 192 \text{ (or 96 if SMOD1 } = 1) \\ \hline 256 - \text{ (TH1)} \end{array}}$

Tables 6 and 7 list various commonly used baud rates and how they can be obtained using Timer 1 as the baud rate generator.

#### Table 10. Baud Rates, Timer Values, and CPU Clock Frequencies for SMOD1 = 0

| Timer Count |          |          | Baud Rate |          |          |

|-------------|----------|----------|-----------|----------|----------|

| Timer Count | 2400     | 4800     | 9600      | 19.2k    | 38.4k    |

| -1          | 0.4608   | 0.9216   | * 1.8432  | * 3.6864 | * 7.3728 |

| -2          | 0.9216   | 1.8432   | * 3.6864  | * 7.3728 | -        |

| -3          | 1.3824   | 2.7648   | 5.5296    | -        | -        |

| -4          | * 1.8432 | * 3.6864 | * 7.3728  | -        | -        |

| -5          | 2.3040   | 4.6080   | 9.2160    | -        | -        |

| -6          | 2.7648   | 5.5296   | -         | -        | -        |

| -7          | 3.2256   | 6.4512   | -         | -        | -        |

| -8          | * 3.6864 | * 7.3728 | -         | -        | -        |

| -9          | 4.1472   | 8.2944   | -         | _        | -        |

| -10         | 4.6080   | 9.2160   | -         | -        | -        |

### P87LPC769

| Timer Count |          |          | Baud     | Rate     |          |        |

|-------------|----------|----------|----------|----------|----------|--------|

| Timer Count | 2400     | 4800     | 9600     | 19.2k    | 38.4k    | 57.6k  |

| -1          | 0.2304   | 0.4608   | 0.9216   | * 1.8432 | * 3.6864 | 5.5296 |

| -2          | 0.4608   | 0.9216   | * 1.8432 | * 3.6864 | * 7.3728 | -      |

| -3          | 0.6912   | 1.3824   | 2.7648   | 5.5296   | -        | -      |

| -4          | 0.9216   | * 1.8432 | * 3.6864 | * 7.3728 | -        | -      |

| -5          | 1.1520   | 2.3040   | 4.6080   | 9.2160   | -        | -      |

| -6          | 1.3824   | 2.7648   | 5.5296   | -        | -        | -      |

| -7          | 1.6128   | 3.2256   | 6.4512   | -        | -        | -      |

| -8          | * 1.8432 | * 3.6864 | * 7.3728 | -        | -        | -      |

| -9          | 2.0736   | 4.1472   | 8.2944   | -        | -        | -      |

| -10         | 2.3040   | 4.6080   | 9.2160   | -        | -        | -      |

| -11         | 2.5344   | 5.0688   | -        | -        | -        | -      |

| -12         | 2.7648   | 5.5296   | -        | -        | -        | -      |

| –13         | 2.9952   | 5.9904   | -        | -        | -        | -      |

| -14         | 3.2256   | 6.4512   | -        | -        | -        | -      |

| –15         | 3.4560   | 6.9120   | -        | -        | -        | -      |

| -16         | * 3.6864 | * 7.3728 | -        | -        | -        | -      |

| -17         | 3.9168   | 7.8336   | -        | -        | -        | -      |

| -18         | 4.1472   | 8.2944   | -        | -        | -        | -      |

| –19         | 4.3776   | 8.7552   | -        | -        | -        | -      |

| -20         | 4.6080   | 9.2160   | -        | -        | -        | -      |

| -21         | 4.8384   | 9.6768   | -        | -        | -        | -      |

#### Table 11. Baud Rates, Timer Values, and CPU Clock Frequencies for SMOD1 = 1

#### NOTES TO TABLES 10 AND 11:

Tables 6 and 7 apply to UART modes 1 and 3 (variable rate modes), and show CPU clock rates in MHz for standard baud rates.

Table 6 shows timer settings and CPU clock rates with the SMOD1 bit in the PCON register = 0 (the default after reset), while Table 7 reflects the SMOD1 bit = 1.

3. The tables show all potential CPU clock frequencies up to 10 MHz that may be used for baud rates. Other CPU clock frequencies that would give only lower baud rates are not shown.

4. Table entries marked with an asterisk (\*) indicate standard crystal and ceramic resonator frequencies that may be obtained from many sources without special ordering.

Figure 34. Serial Port Mode 2

### P87LPC769

#### Additional Features

The AUXR1 register contains several special purpose control bits that relate to several chip features. AUXR1 is described in Figure 38.

#### Software Reset

The SRST bit in AUXR1 allows software the opportunity to reset the processor completely, as if an external reset or watchdog reset had occurred. If a value is written to AUXR1 that contains a 1 at bit position 3, all SFRs will be initialized and execution will resume at program address 0000. Care should be taken when writing to AUXR1 to avoid accidental software resets.

#### **Dual Data Pointers**

The dual Data Pointer (DPTR) adds to the ways in which the processor can specify the address used with certain instructions. The DPS bit in the AUXR1 register selects one of the two Data Pointers. The DPTR that is not currently selected is not accessible to software unless the DPS bit is toggled.

Specific instructions affected by the Data Pointer selection are:

- INC DPTR Increments the Data Pointer by 1.

- JMP @A+DPTR Jump indirect relative to DPTR value.

- MOV DPTR, #data16 Load the Data Pointer with a 16-bit constant.

MOVC A, @A+DPTR Move code byte relative to DPTR to the accumulator.

MOVX A, @DPTR Move data byte the accumulator to data memory relative to DPTR.

- MOVX @DPTR, A Move data byte from data memory relative to DPTR to the accumulator.

Also, any instruction that reads or manipulates the DPH and DPL registers (the upper and lower bytes of the current DPTR) will be affected by the setting of DPS. The MOVX instructions have limited application for the P87LPC769 since the part does not have an external data bus. However, they may be used to access EPROM configuration information (see EPROM Characteristics section).

Bit 2 of AUXR1 is permanently wired as a logic 0. This is so that the DPS bit may be toggled (thereby switching Data Pointers) simply by incrementing the AUXR1 register, without the possibility of inadvertently altering other bits in the register.

| Not Bit | Addressable |      |           |             |                               |                             |            |              |             |                                          |

|---------|-------------|------|-----------|-------------|-------------------------------|-----------------------------|------------|--------------|-------------|------------------------------------------|

|         | _           | 7    | 6         | 5           | 4                             | 3                           | 2          | 1            | 0           |                                          |

|         |             | KBF  | BOD       | BOI         |                               | SRST                        | 0          | —            | DPS         |                                          |

| BIT     | SYMBOL      | FUN  |           |             |                               |                             |            |              |             |                                          |

| AUXR1.7 | KBF         |      |           |             |                               | any pin of p<br>by software |            | t is enabled | for the Ke  | yboard Interrupt                         |

| AUXR1.6 | BOD         |      |           |             | en set, turns<br>ction for de |                             | out detec  | tion and sa  | ves power.  | See Power                                |

| AUXR1.5 | BOI         | the  |           | detect fun  |                               |                             |            |              |             | chip reset and allows<br>oring Functions |

| AUXR1.4 | —           | Res  | erved. Us | ser code sh | ould alway                    | s write a ze                | ro to this | bit position |             |                                          |

| AUXR1.3 | SRST        | Soft | ware Res  | set. When s | set by softw                  | are, resets                 | the P87L   | PC769 as     | if a hardwa | re reset occurred.                       |

| AUXR1.2 | —           |      |           |             | wired 0. All<br>s in the regi |                             | g of the [ | OPS bit by i | ncrementir  | ng AUXR1, without                        |

| AUXR1.1 | —           | Res  | erved for | future use  | . Should no                   | t be set to 1               | by user    | programs.    |             |                                          |

| AUXR1.0 | DPS         | Data | a Pointer | Select. Ch  | ooses one o                   | of two Data                 | Pointers   | for use by   | the prograi | n. See text for details                  |

Figure 38. AUXR1 Register

## P87LPC769

### COMPARATOR ELECTRICAL CHARACTERISTICS

$V_{DD}$  = 3.0 V to 6.0 V unless otherwise specified;  $T_{amb}$  = -40 °C to +125 °C, unless otherwise specified

| SYMBOL          | PARAMETER                                     | TEST CONDITIONS       |   | UNIT |                      |      |

|-----------------|-----------------------------------------------|-----------------------|---|------|----------------------|------|

| STWBUL          | PARAMETER                                     | ER TEST CONDITIONS    |   | TYP  | MAX                  | UNIT |

| V <sub>IO</sub> | Offset voltage comparator inputs <sup>1</sup> |                       |   |      | ±10                  | mV   |

| V <sub>CR</sub> | Common mode range comparator inputs           |                       | 0 |      | V <sub>DD</sub> -0.3 | V    |

| CMRR            | Common mode rejection ratio <sup>1</sup>      |                       |   |      | -50                  | dB   |

|                 | Response time                                 |                       |   | 250  | 500                  | ns   |

|                 | Comparator enable to output valid             |                       |   |      | 10                   | μs   |

| ۱ <sub>IL</sub> | Input leakage current, comparator             | $0 < V_{IN} < V_{DD}$ |   |      | ±10                  | μΑ   |

NOTE:

1. This parameter is guaranteed by characterization, but not tested in production.

#### A/D CONVERTER DC ELECTRICAL CHARACTERISTICS

Vdd = 2.7 V to 6.0 V unless otherwise specified; Tamb = -40 °C to +125 °C, unless otherwise specified.

| SYMBOL           | PARAMETER                                     | TEST CONDITIONS | LIN                   | IITS                  | UNIT |

|------------------|-----------------------------------------------|-----------------|-----------------------|-----------------------|------|

| STMBOL           | FARAMETER                                     | TEST CONDITIONS | MIN                   | MAX                   | UNIT |

| AV <sub>IN</sub> | Analog input voltage                          |                 | V <sub>SS</sub> - 0.2 | V <sub>DD</sub> + 0.2 | V    |

| R <sub>REF</sub> | Resistance between $V_{DD}$ and $V_{SS}$      | A/D enabled     | tbd                   | tbd                   | kΩ   |

| CIA              | Analog input capacitance                      |                 |                       | 15                    | pF   |

| DLe              | Differential non-linearity <sup>1,2,3</sup>   |                 |                       | ±1                    | LSB  |

| IL <sub>e</sub>  | Integral non-linearity <sup>1,4</sup>         |                 |                       | ±1                    | LSB  |

| OS <sub>e</sub>  | Offset error <sup>1,5</sup>                   |                 |                       | ±2                    | LSB  |

| G <sub>e</sub>   | Gain error <sup>1,6</sup>                     |                 | 1                     | ±1                    | %    |

| A <sub>e</sub>   | Absolute voltage error <sup>1,7</sup>         |                 |                       | ±1                    | LSB  |

| M <sub>CTC</sub> | Channel-to-channel matching                   |                 |                       | ±1                    | LSB  |

| Ct               | Crosstalk between inputs of port <sup>8</sup> | 0 - 100kHz      |                       | -60                   | dB   |

| -                | Input slew rate                               |                 |                       | 100                   | V/ms |

| -                | Input source impedance                        |                 | 1                     | 10                    | kΩ   |

NOTES:

1. Conditions:  $V_{SS} = 0V$ ;  $V_{DD} = 5.12V$ . 2. The A/D is monotonic, there are no missing codes

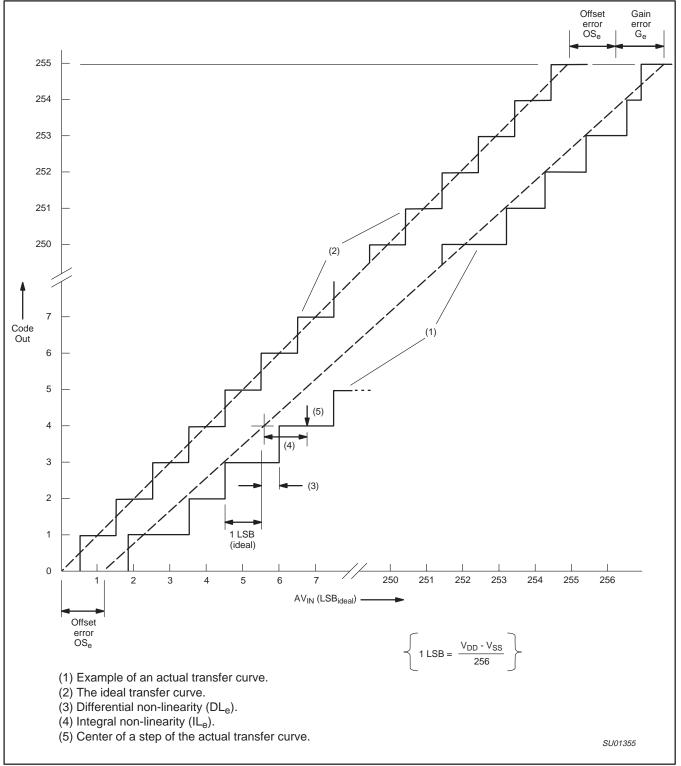

3. The differential non-linearity ( $DL_e$ ) is the difference between the actual step width and the ideal step width. See Figure 41.

4. The integral non-linearity (ILe) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See Figure 41.

The offset error (OSe) is the absolute difference between the straight line which fits the actual transfer curve (after removing gain error), and 5. the straight line which fits the ideal transfer curve. See Figure 41.

The gain error (Ge) is the relative difference in percent between the straight line fitting the actual transfer curve (after removing offset error), 6. and the straight line which fits the ideal transfer curve. Gain error is constant at every point on the transfer curve. See Figure 41.

The absolute voltage error (Ae) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve.

8. This should be considered when both analog and digital signals are input simultaneously to A/D pins.

9. Changing the input voltage faster than this may cause erroneous readings.

10. A source impedance higher than this driving an A/D input may result in loss of precision and erroneous readings.

P87LPC769

## Low power, low price, low pin count (20 pin) microcontroller with 4 kB OTP 8-bit A/D, and DAC

Figure 41. A/D Conversion Characteristics

### P87LPC769

#### **REVISION HISTORY**

| Date        | CPCN           | Description                                                                                    |

|-------------|----------------|------------------------------------------------------------------------------------------------|

| 2002 Mar 12 | 9397 750 09559 | <ul> <li>Added revision history</li> </ul>                                                     |

|             |                | <ul> <li>Interrupt section: BOF is the Interrupt Flag for Brownout Detect (not BOD)</li> </ul> |

|             |                | - Updated Reset section                                                                        |

| 2001 Jan 11 | 9397 750 07923 | Previous release                                                                               |

### P87LPC769

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status