Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | AVR                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 32KB (16K x 16)                                                        |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 44-VQFN (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega32a-mu |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 11.4.2. EEPROM Write during Power-down Sleep Mode

When entering Power-down sleep mode while an EEPROM write operation is active, the EEPROM write operation will continue, and will complete before the Write Access time has passed. However, when the write operation is completed, the Oscillator continues running, and as a consequence, the device does not enter Power-down entirely. It is therefore recommended to verify that the EEPROM write operation is completed before entering Power-down.

## 11.4.3. Preventing EEPROM Corruption

During periods of low  $V_{CC}$ , the EEPROM data can be corrupted because the supply voltage is too low for the CPU and the EEPROM to operate properly. These issues are the same as for board level systems using EEPROM, and the same design solutions should be applied.

An EEPROM data corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Second, the CPU itself can execute instructions incorrectly, if the supply voltage is too low.

EEPROM data corruption can easily be avoided by following this design recommendation:

Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD). If the detection level of the internal BOD does not match the needed detection level, an external low  $V_{CC}$  Reset Protection circuit can be used. If a reset occurs while a write operation is in progress, the write operation will be completed provided that the power supply voltage is sufficient.

# 11.5. I/O Memory

The I/O space definition of the ATmega32A is shown in Register Summary.

All ATmega32A I/Os and peripherals are placed in the I/O space. The I/O locations are accessed by the IN and OUT instructions, transferring data between the 32 general purpose working registers and the I/O space. I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set section for more details. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

The I/O and Peripherals Control Registers are explained in later sections.

## **Related Links**

Register Summary on page 399

# 11.6. Register Description

## 13.9.1. MCUCR – MCU Control Register

The MCU Control Register contains control bits for power management.

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:MCUCROffset:0x35Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x55

| Bit    | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|--------|-----|-----|-----|-----|---|---|---|---|

| [      | SE  | SM2 | SM1 | SM0 |   |   |   |   |

| Access | R/W | R/W | R/W | R/W |   |   |   |   |

| Reset  | 0   | 0   | 0   | 0   |   |   |   |   |

#### Bit 7 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmer's purpose, it is recommended to set the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up.

## Bits 6:4 – SMn: Sleep Mode n Select Bits [n = 2:0]

These bits select between the six available sleep modes as shown in the table.

| SM2 | SM1 | SM0 | Sleep Mode                      |

|-----|-----|-----|---------------------------------|

| 0   | 0   | 0   | Idle                            |

| 0   | 0   | 1   | ADC Noise Reduction             |

| 0   | 1   | 0   | Power-down                      |

| 0   | 1   | 1   | Power-save                      |

| 1   | 0   | 0   | Reserved                        |

| 1   | 0   | 1   | Reserved                        |

| 1   | 1   | 0   | Standby <sup>(1)</sup>          |

| 1   | 1   | 1   | Extended Standby <sup>(1)</sup> |

#### Table 13-2. Sleep Mode Select

Note: 1. Standby mode is only available with external crystals or resonators.

# 17.3.3. Alternate Functions of Port C

The Port C pins with alternate functions are shown in the table below. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

| Port Pin | Alternate Function                               |  |  |

|----------|--------------------------------------------------|--|--|

| PC7      | TOSC2 (Timer Oscillator Pin 2)                   |  |  |

| PC6      | OSC1 (Timer Oscillator Pin 1)                    |  |  |

| PC5      | TDI (JTAG Test Data In)                          |  |  |

| PC4      | TDO (JTAG Test Data Out)                         |  |  |

| PC3      | TMS (JTAG Test Mode Select)                      |  |  |

| PC2      | TCK (JTAG Test Clock)                            |  |  |

| PC1      | SDA (Two-wire Serial Bus Data Input/Output Line) |  |  |

| PC0      | SCL (Two-wire Serial Bus Clock Line)             |  |  |

#### Table 17-9. Port C Pins Alternate Functions

The alternate pin configuration is as follows:

#### • TOSC2 - Port C, Bit 7

TOSC2, Timer Oscillator pin 2: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC7 is disconnected from the port, and becomes the inverting output of the Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TOSC1 – Port C, Bit 6

TOSC1, Timer Oscillator pin 1: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a Crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

#### • TDI – Port C, Bit 5

TDI, JTAG Test Data In: Serial input data to be shifted in to the Instruction Register or Data Register (scan chains). When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TDO – Port C, Bit 4

TDO, JTAG Test Data Out: Serial output data from Instruction Register or Data Register. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

The TD0 pin is tri-stated unless TAP states that shifts out data are entered.

#### • TMS – Port C, Bit 3

TMS, JTAG Test Mode Select: This pin is used for navigating through the TAP-controller state machine. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • TCK – Port C, Bit 2

TCK, JTAG Test Clock: JTAG operation is synchronous to TCK. When the JTAG interface is enabled, this pin can not be used as an I/O pin.

#### • SDA – Port C, Bit 1

SDA, Two-wire Serial Interface Data: When the TWEN bit in TWCR is set (one) to enable the Two-wire Serial Interface, pin PC1 is disconnected from the port and becomes the Serial Data I/O pin for the Two-wire Serial Interface. In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal, and the pin is driven by an open drain driver with slew-rate limitation. When this pin is used by the Two-wire Serial Interface, the pull-up can still be controlled by the PORTC1 bit.

## • SCL - Port C, Bit 0

SCL, Two-wire Serial Interface Clock: When the TWEN bit in TWCR is set (one) to enable the Two-wire Serial Interface, pin PC0 is disconnected from the port and becomes the Serial Clock I/O pin for the Two-wire Serial Interface. In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal, and the pin is driven by an open drain driver with slew-rate limitation. When this pin is used by the Two-wire Serial Interface, the pull-up can still be controlled by the PORTC0 bit.

The tables below relate the alternate functions of Port C to the overriding signals shown in Alternate Port Functions.

| Signal<br>Name | PC7/TOSC2       | PC6/TOSC1      | PC5/TDI | PC4/TDO                |

|----------------|-----------------|----------------|---------|------------------------|

| PUOE           | AS2             | AS2            | JTAGEN  | JTAGEN                 |

| PUOV           | 0               | 0              | 1       | 0                      |

| DDOE           | AS2             | AS2            | JTAGEN  | JTAGEN                 |

| DDOV           | 0               | 0              | 0       | SHIFT_IR +<br>SHIFT_DR |

| PVOE           | 0               | 0              | 0       | JTAGEN                 |

| PVOV           | 0               | 0              | 0       | TDO                    |

| DIEOE          | AS2             | AS2            | JTAGEN  | JTAGEN                 |

| DIEOV          | 0               | 0              | 0       | 0                      |

| DI             | -               | -              | -       | _                      |

| AIO            | T/C2 OSC OUTPUT | T/C2 OSC INPUT | TDI     | -                      |

#### Table 17-10. Overriding Signals for Alternate Functions in PC7:PC4

Table 17-11. Overriding Signals for Alternate Functions in PC3:PC0<sup>(1)</sup>

| Signal<br>Name | PC3/TMS | PC2/TCK | PC1/SDA      | PC0/SCL      |

|----------------|---------|---------|--------------|--------------|

| PUOE           | JTAGEN  | JTAGEN  | TWEN         | TWEN         |

| PUOV           | 1       | 1       | PORTC1 • PUD | PORTCO • PUD |

| DDOE           | JTAGEN  | JTAGEN  | TWEN         | TWEN         |

| DDOV           | 0       | 0       | SDA_OUT      | SCL_OUT      |

| PVOE           | 0       | 0       | TWEN         | TWEN         |

| PVOV           | 0       | 0       | 0            | 0            |

| DIEOE          | JTAGEN  | JTAGEN  | 0            | 0            |

## 17.4.5. PORTB – The Port B Data Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:PORTBOffset:0x18Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x38

| Bit    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| [      | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 |

| Access | R/W    |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Bits 7:0 – PORTBn: Port B Data [n = 7:0]

## 17.4.12. DDRD – The Port D Data Direction Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:DDRDOffset:0x11Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x31

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

|        | DDD7 | DDD6 | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Bits 7:0 – DDDn: Port D Data Direction [n = 7:0]

## 17.4.13. PIND – The Port D Input Pins Address

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:PINDOffset:0x10Reset:N/AProperty:When addressing I/O Registers as data space the offset address is 0x30

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 |

| Access | R     | R     | R     | R     | R     | R     | R     | R     |

| Reset  | х     | х     | х     | х     | х     | х     | х     | x     |

Bits 7:0 – PINDn: Port D Input Pins Address [n = 7:0]

| Table 19-3. | Compare | Output | Mode, | Fast PWM <sup>(1)</sup> | ) |

|-------------|---------|--------|-------|-------------------------|---|

|-------------|---------|--------|-------|-------------------------|---|

| COM1A1/<br>COM1B1 | COM1A0/<br>COM1B0 | Description                                                                                                                                                        |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 0                 | Normal port operation, OC1A/OC1B disconnected.                                                                                                                     |

| 0                 | 1                 | WGM13:0 = 15: Toggle OC1A on Compare Match, OC1B disconnected (normal port operation). For all other WGM1 settings, normal port operation, OC1A/OC1B disconnected. |

| 1                 | 0                 | Clear OC1A/OC1B on Compare Match, set OC1A/OC1B at BOTTOM (non-inverting mode)                                                                                     |

| 1                 | 1                 | Set OC1A/OC1B on Compare Match, clear OC1A/OC1B at BOTTOM (inverting mode)                                                                                         |

**Note:** 1. A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. In this case the compare match is ignored, but the set or clear is done at BOTTOM. Refer to Fast PWM Mode for details.

The table below shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to the phase correct or the phase and frequency correct, PWM mode.

| COM1A1/<br>COM1B1 | COM1A0/<br>COM1B0 | Description                                                                                                                                                             |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 0                 | Normal port operation, OC1A/OC1B disconnected.                                                                                                                          |

| 0                 | 1                 | WGM13:0 = 9 or 14: Toggle OC1A on Compare Match, OC1B disconnected (normal port operation). For all other WGM1 settings, normal port operation, OC1A/OC1B disconnected. |

| 1                 | 0                 | Clear OC1A/OC1B on Compare Match when up-counting. Set OC1A/OC1B on Compare Match when down-counting.                                                                   |

| 1                 | 1                 | Set OC1A/OC1B on Compare Match when up-counting. Clear OC1A/OC1B on Compare Match when down-counting.                                                                   |

Table 19-4. Compare Output Mode, Phase Correct and Phase and Frequency Correct PWM<sup>(1)</sup>

**Note:** 1. A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. Refer to Phase Correct PWM Mode for details.

## Bit 3 – FOC1A: Force Output Compare for channel A

## Bit 2 – FOC1B: Force Output Compare for channel B

The FOC1A/FOC1B bits are only active when the WGM13:0 bits specifies a non-PWM mode. However, for ensuring compatibility with future devices, these bits must be set to zero when TCCR1A is written when operating in a PWM mode. When writing a logical one to the FOC1A/FOC1B bit, an immediate Compare Match is forced on the waveform generation unit. The OC1A/OC1B output is changed according to its COM1x1:0 bits setting. Note that the FOC1A/FOC1B bits are implemented as strobes. Therefore it is the value present in the COM1x1:0 bits that determine the effect of the forced compare.

A FOC1A/FOC1B strobe will not generate any interrupt nor will it clear the timer in Clear Timer on Compare Match (CTC) mode using OCR1A as TOP.

The FOC1A/FOC1B bits are always read as zero.

## 20.11.4. ASSR – Asynchronous Status Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:ASSROffset:0x22Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x42

| Bit    | 7 | 6 | 5 | 4 | 3   | 2      | 1      | 0      |

|--------|---|---|---|---|-----|--------|--------|--------|

|        |   |   |   |   | AS2 | TCN2UB | OCR2UB | TCR2UB |

| Access |   |   |   |   | R/W | R      | R      | R      |

| Reset  |   |   |   |   | 0   | 0      | 0      | 0      |

## Bit 3 – AS2: Asynchronous Timer/Counter2

When AS2 is written to zero, Timer/Counter 2 is clocked from the I/O clock,  $clk_{I/O}$ . When AS2 is written to one, Timer/Counter 2 is clocked from a crystal Oscillator connected to the Timer Oscillator 1 (TOSC1) pin. When the value of AS2 is changed, the contents of TCNT2, OCR2, and TCCR2 might be corrupted.

#### Bit 2 – TCN2UB: Timer/Counter2 Update Busy

When Timer/Counter2 operates asynchronously and TCNT2 is written, this bit becomes set. When TCNT2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCNT2 is ready to be updated with a new value.

## Bit 1 – OCR2UB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2 is written, this bit becomes set. When OCR2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2 is ready to be updated with a new value.

#### Bit 0 – TCR2UB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2 is written, this bit becomes set. When TCCR2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2 is ready to be updated with a new value.

If a write is performed to any of the three Timer/Counter2 Registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur.

The mechanisms for reading TCNT2, OCR2, and TCCR2 are different. When reading TCNT2, the actual timer value is read. When reading OCR2 or TCCR2, the value in the temporary storage register is read.

```

ldi r16,(1<<URSEL) | (1<<USBS) | (1<<UCSZ1)

out UCSRC,r16

..

C Code Example(1)

..

/* Set UBRRH to 2 */

UBRRH = 0x02;

..

/* Set the USBS and the UCSZ1 bit to one, and */

/* the remaining bits to zero. */

UCSRC = (1<<URSEL) | (1<<USBS) | (1<<UCSZ1);

..</pre>

```

Note: 1. See About Code Examples.

As the code examples illustrate, write accesses of the two registers are relatively unaffected of the sharing of I/O location.

#### **Related Links**

About Code Examples on page 19

#### 23.10.2. Read Access

Doing a read access to the UBRRH or the UCSRC Register is a more complex operation. However, in most applications, it is rarely necessary to read any of these registers.

The read access is controlled by a timed sequence. Reading the I/O location once returns the UBRRH Register contents. If the register location was read in previous system clock cycle, reading the register in the current clock cycle will return the UCSRC contents. Note that the timed sequence for reading the UCSRC is an atomic operation. Interrupts must therefore be controlled (e.g., by disabling interrupts globally) during the read operation.

The following code example shows how to read the UCSRC Register contents.

```

Assembly Code Example<sup>(1)</sup>

USART_ReadUCSRC:

; Read UCSRC

in r16,UBRRH

in r16,UCSRC

ret

C Code Example<sup>(1)</sup>

unsigned char USART_ReadUCSRC( void )

{

unsigned char ucsrc;

/* Read UCSRC */

ucsrc = UBRRH;

ucsrc = UCSRC;

return ucsrc;

}

```

#### Note: 1. See About Code Examples.

The assembly code example returns the UCSRC value in r16.

Reading the UBRRH contents is not an atomic operation and therefore it can be read as an ordinary register, as long as the previous instruction did not access the register location.

**Related Links**

## 23.11.3. UCSRB – USART Control and Status Register B

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:

UCSRB

Offset:

0x0A

Reset:

0x00

Property:

When addressing I/O Registers as data space the offset address is 0x2A

| Bit    | 7     | 6     | 5     | 4    | 3    | 2     | 1    | 0    |

|--------|-------|-------|-------|------|------|-------|------|------|

|        | RXCIE | TXCIE | UDRIE | RXEN | TXEN | UCSZ2 | RXB8 | TXB8 |

| Access | R/W   | R/W   | R/W   | R/W  | R/W  | R/W   | R    | R/W  |

| Reset  | 0     | 0     | 0     | 0    | 0    | 0     | 0    | 0    |

## Bit 7 – RXCIE: RX Complete Interrupt Enable

Writing this bit to one enables interrupt on the RXC Flag. A USART Receive Complete interrupt will be generated only if the RXCIE bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXC bit in UCSRA is set.

## Bit 6 – TXCIE: TX Complete Interrupt Enable

Writing this bit to one enables interrupt on the TXC Flag. A USART Transmit Complete interrupt will be generated only if the TXCIE bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXC bit in UCSRA is set.

## Bit 5 – UDRIE: USART Data Register Empty Interrupt Enable

Writing this bit to one enables interrupt on the UDRE Flag. A Data Register Empty interrupt will be generated only if the UDRIE bit is written to one, the Global Interrupt Flag in SREG is written to one and the UDRE bit in UCSRA is set.

## Bit 4 – RXEN: Receiver Enable

Writing this bit to one enables the USART Receiver. The Receiver will override normal port operation for the RxD pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FE, DOR and PE Flags.

## Bit 3 – TXEN: Transmitter Enable

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxD pin when enabled. The disabling of the Transmitter (writing TXEN to zero) will not become effective until ongoing and pending transmissions are completed (i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted). When disabled, the Transmitter will no longer override the TxD port.

## Bit 2 – UCSZ2: Character Size

The UCSZ2 bits combined with the UCSZ1:0 bit in UCSRC sets the number of data bits (Character Size) in a frame the Receiver and Transmitter use.

## Bit 1 – RXB8: Receive Data Bit 8

RXB8 is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDR.

| Baud<br>Rate<br>[bps] | f <sub>osc</sub> = 1.0000MHz       |              |          | f <sub>osc</sub> = 1.8432MHz |        |                 |         | f <sub>osc</sub> = 2.0000MHz |         |        |         |       |

|-----------------------|------------------------------------|--------------|----------|------------------------------|--------|-----------------|---------|------------------------------|---------|--------|---------|-------|

|                       | U2X = 0                            |              | U2X = 1  |                              | U2X= 0 |                 | U2X = 1 |                              | U2X = 0 |        | U2X = 1 |       |

|                       | UBRR                               | Error        | UBRR     | Error                        | UBRR   | Error           | UBRR    | Error                        | UBRR    | Error  | UBRR    | Error |

| 28.8k                 | 1                                  | 8.5%         | 3        | 8.5%                         | 3      | 0.0%            | 7       | 0.0%                         | 3       | 8.5%   | 8       | -3.5% |

| 38.4k                 | 1                                  | -18.6%       | 2        | 8.5%                         | 2      | 0.0%            | 5       | 0.0%                         | 2       | 8.5%   | 6       | -7.0% |

| 57.6k                 | 0                                  | 8.5%         | 1        | 8.5%                         | 1      | 0.0%            | 3       | 0.0%                         | 1       | 8.5%   | 3       | 8.5%  |

| 76.8k                 | -                                  | _            | 1        | -18.6%                       | 1      | -25.0%          | 2       | 0.0%                         | 1       | -18.6% | 2       | 8.5%  |

| 115.2k                | -                                  | -            | 0        | 8.5%                         | 0      | 0.0%            | 1       | 0.0%                         | 0       | 8.5%   | 1       | 8.5%  |

| 230.4k                | -                                  | -            | -        | -                            | -      | -               | 0       | 0.0%                         | -       | -      | -       | -     |

| 250k                  | -                                  | _            | _        | -                            | -      | -               | -       | -                            | -       | -      | 0       | 0.0%  |

| Max <sup>(1)</sup>    | ax <sup>(1)</sup> 62.5kbps 125kbps |              | 115.2kbp | 115.2kbps 230.4kbps          |        | 125kbps 250kbps |         |                              |         |        |         |       |

| Note: 1               | I. UBRR =                          | = 0, Error = | = 0.0%   |                              |        |                 |         |                              |         |        |         |       |

| Table 22-10 | Examples of UBI | DD Sattings for | Commonly | Ilead Oecillator | Fraguancias  | (Continued) |

|-------------|-----------------|-----------------|----------|------------------|--------------|-------------|

|             | LAINPIES OF UDI | IN Settings IOF | Commonly |                  | i requencies | (Continueu) |

| Baud                | f <sub>osc</sub> = 3. | 6864MH | z       |       | f <sub>osc</sub> = 4.0000MHz |                 |      |         | f <sub>osc</sub> = 7.3728MHz |         |      |         |  |

|---------------------|-----------------------|--------|---------|-------|------------------------------|-----------------|------|---------|------------------------------|---------|------|---------|--|

| Rate<br>[bps]       | U2X = 0               |        | U2X = 1 |       | U2X = 0                      | U2X = 0         |      | U2X = 1 |                              | U2X = 0 |      | U2X = 1 |  |

| [000]               | UBRR                  | Error  | UBRR    | Error | UBRR                         | Error           | UBRR | Error   | UBRR                         | Error   | UBRR | Error   |  |

| 2400                | 95                    | 0.0%   | 191     | 0.0%  | 103                          | 0.2%            | 207  | 0.2%    | 191                          | 0.0%    | 383  | 0.0%    |  |

| 4800                | 47                    | 0.0%   | 95      | 0.0%  | 51                           | 0.2%            | 103  | 0.2%    | 95                           | 0.0%    | 191  | 0.0%    |  |

| 9600                | 23                    | 0.0%   | 47      | 0.0%  | 25                           | 0.2%            | 51   | 0.2%    | 47                           | 0.0%    | 95   | 0.0%    |  |

| 14.4k               | 15                    | 0.0%   | 31      | 0.0%  | 16                           | 2.1%            | 34   | -0.8%   | 31                           | 0.0%    | 63   | 0.0%    |  |

| 19.2k               | 11                    | 0.0%   | 23      | 0.0%  | 12                           | 0.2%            | 25   | 0.2%    | 23                           | 0.0%    | 47   | 0.0%    |  |

| 28.8k               | 7                     | 0.0%   | 15      | 0.0%  | 8                            | -3.5%           | 16   | 2.1%    | 15                           | 0.0%    | 31   | 0.0%    |  |

| 38.4k               | 5                     | 0.0%   | 11      | 0.0%  | 6                            | -7.0%           | 12   | 0.2%    | 11                           | 0.0%    | 23   | 0.0%    |  |

| 57.6k               | 3                     | 0.0%   | 7       | 0.0%  | 3                            | 8.5%            | 8    | -3.5%   | 7                            | 0.0%    | 15   | 0.0%    |  |

| 76.8k               | 2                     | 0.0%   | 5       | 0.0%  | 2                            | 8.5%            | 6    | -7.0%   | 5                            | 0.0%    | 11   | 0.0%    |  |

| 115.2k              | 1                     | 0.0%   | 3       | 0.0%  | 1                            | 8.5%            | 3    | 8.5%    | 3                            | 0.0%    | 7    | 0.0%    |  |

| 230.4k              | 0                     | 0.0%   | 1       | 0.0%  | 0                            | 8.5%            | 1    | 8.5%    | 1                            | 0.0%    | 3    | 0.0%    |  |

| 250k                | 0                     | -7.8%  | 1       | -7.8% | 0                            | 0.0%            | 1    | 0.0%    | 1                            | -7.8%   | 3    | -7.8%   |  |

| 0.5M                | -                     | -      | 0       | -7.8% | -                            | -               | 0    | 0.0%    | 0                            | -7.8%   | 1    | -7.8%   |  |

| 1M                  | -                     | -      | -       | -     | -                            | -               | -    | -       | -                            | -       | 0    | -7.8%   |  |

| Max. <sup>(1)</sup> | 230.4kb               | ps     | 460.8kb | os    | 250kbps                      | 250kbps 0.5Mbps |      |         | 460.8kbps 921.6kbps          |         |      |         |  |

## 24.8.2. TWCR – TWI Control Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

The TWCR is used to control the operation of the TWI. It is used to enable the TWI, to initiate a Master access by applying a START condition to the bus, to generate a Receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the bus are written to the TWDR. It also indicates a write collision if data is attempted written to TWDR while the register is inaccessible.

Name:TWCROffset:0x36Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x56

| Bit    | 7     | 6    | 5     | 4     | 3    | 2    | 1 | 0    |

|--------|-------|------|-------|-------|------|------|---|------|

|        | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN |   | TWIE |

| Access | R/W   | R/W  | R/W   | R/W   | R    | R/W  |   | R/W  |

| Reset  | 0     | 0    | 0     | 0     | 0    | 0    |   | 0    |

## Bit 7 – TWINT: TWI Interrupt Flag

This bit is set by hardware when the TWI has finished its current job and expects application software response. If the I-bit in SREG and TWIE in TWCR are set, the MCU will jump to the TWI Interrupt Vector. While the TWINT Flag is set, the SCL low period is stretched. The TWINT Flag must be cleared by software by writing a logic one to it.

Note that this flag is not automatically cleared by hardware when executing the interrupt routine. Also note that clearing this flag starts the operation of the TWI, so all accesses to the TWI Address Register (TWAR), TWI Status Register (TWSR), and TWI Data Register (TWDR) must be complete before clearing this flag.

# Bit 6 – TWEA: TWI Enable Acknowledge

The TWEA bit controls the generation of the acknowledge pulse. If the TWEA bit is written to one, the ACK pulse is generated on the TWI bus if the following conditions are met:

- 1. The device's own slave address has been received.

- 2. A general call has been received, while the TWGCE bit in the TWAR is set.

- 3. A data byte has been received in Master Receiver or Slave Receiver mode.

By writing the TWEA bit to zero, the device can be virtually disconnected from the 2-wire Serial Bus temporarily. Address recognition can then be resumed by writing the TWEA bit to one again.

## Bit 5 – TWSTA: TWI START Condition

The application writes the TWSTA bit to one when it desires to become a Master on the 2-wire Serial Bus. The TWI hardware checks if the bus is available, and generates a START condition on the bus if it is free. However, if the bus is not free, the TWI waits until a STOP condition is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted.

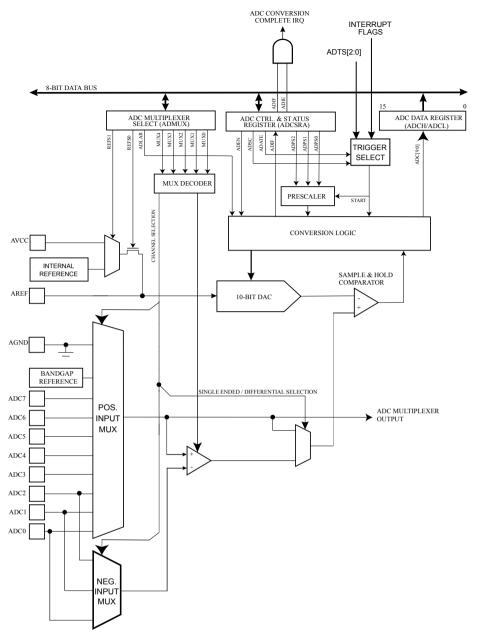

Figure 26-1. Analog to Digital Converter Block Schematic Operation

The ADC converts an analog input voltage to a 10-bit digital value through successive approximation. The minimum value represents GND and the maximum value represents the voltage on the AREF pin minus 1 LSB. Optionally, AVCC or an internal 2.56V reference voltage may be connected to the AREF pin by writing to the REFSn bits in the ADMUX Register. The internal voltage reference may thus be decoupled by an external capacitor at the AREF pin to improve noise immunity.

The analog input channel and differential gain are selected by writing to the MUX bits in ADMUX. Any of the ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected as single ended inputs to the ADC. A selection of ADC input pins can be selected as positive and negative inputs to the differential gain amplifier.

If differential channels are selected, the differential gain stage amplifies the voltage difference between the selected input channel pair by the selected gain factor. This amplified value then becomes the analog input to the ADC. If single ended channels are used, the gain amplifier is bypassed altogether.

# Atmel

## 26.8.5. ADCL – ADC Data Register Low (ADLAR=1)

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:ADCLOffset:0x04Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x24

| Bit    | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------|------|---|---|---|---|---|---|

|        | ADC1 | ADC0 |   |   |   |   |   |   |

| Access | R    | R    |   |   |   |   |   |   |

| Reset  | 0    | 0    |   |   |   |   |   |   |

Bit 7 – ADC1: ADC Conversion Result Refer to ADCL

Bit 6 – ADC0: ADC Conversion Result

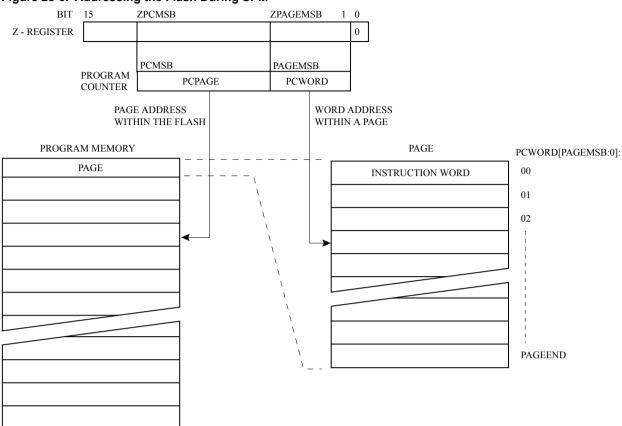

# Figure 28-3. Addressing the Flash During SPM<sup>(1)</sup>

#### Note:

- 1. Fo the different variables used in the figure, see the table of the different variables used and the Mapping to the Z-pointer in the boot loader parameters section.

- 2. PCPAGE and PCWORD are listed in table *Number of Words in a Page and number of Pages in the Flash* in the *Signal Names* section.

#### **Related Links**

Signal Names on page 331 ATmega32A Boot Loader Parameters on page 323

# 28.8. Self-Programming the Flash

The program memory is updated in a page by page fashion. Before programming a page with the data stored in the temporary page buffer, the page must be erased. The temporary page buffer is filled one word at a time using SPM and the buffer can be filled either before the Page Erase command or between a Page Erase and a Page Write operation:

#### Alternative 1, fill the buffer before a Page Erase

- Fill temporary page buffer

- Perform a Page Erase

- Perform a Page Write

## Alternative 2, fill the buffer after Page Erase

Perform a Page Erase

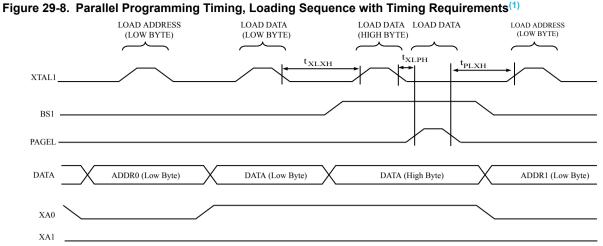

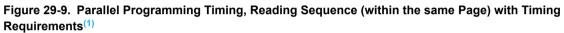

**Note:** 1. The timing requirements shown in the first figure in this section (i.e.,  $t_{DVXH}$ ,  $t_{XHXL}$ , and  $t_{XLDX}$ ) also apply to loading operation.

**Note:** 1. The timing requirements shown in the first figure in this section (i.e.,  $t_{DVXH}$ ,  $t_{XHXL}$ , and  $t_{XLDX}$ ) also apply to reading operation.

Table 29-13. Parallel Programming Characteristics, VCC = 5V ± 10%

| Symbol            | Parameter                                | Min  | Тур | Max  | Units |

|-------------------|------------------------------------------|------|-----|------|-------|

| V <sub>PP</sub>   | Programming Enable Voltage               | 11.5 |     | 12.5 | V     |

| I <sub>PP</sub>   | Programming Enable Current               |      |     | 250  | μA    |

| t <sub>DVXH</sub> | Data and Control Valid before XTAL1 High | 67   |     |      | ns    |

| t <sub>XLXH</sub> | XTAL1 Low to XTAL1 High                  | 200  |     |      | ns    |

| t <sub>XHXL</sub> | XTAL1 Pulse Width High                   | 150  |     |      | ns    |

| t <sub>XLDX</sub> | Data and Control Hold after XTAL1 Low    | 67   |     |      | ns    |

| t <sub>XLWL</sub> | XTAL1 Low to WR Low                      | 0    |     |      | ns    |

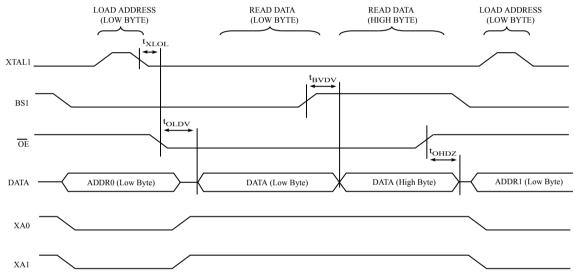

Figure 29-15. State Machine Sequence for Changing/Reading the Data Word

#### 29.10.11. Virtual Flash Page Load Register

The Virtual Flash Page Load Register is a virtual scan chain with length equal to the number of bits in one Flash page. Internally the Shift Register is 8-bit, and the data are automatically transferred to the Flash page buffer byte by byte. Shift in all instruction words in the page, starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page. This provides an efficient way to load the entire Flash page buffer before executing Page Write.

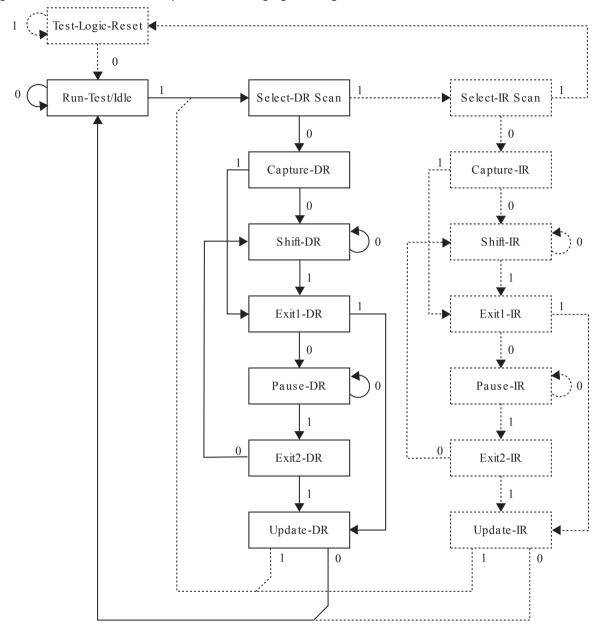

Figure 31-36. Calibrated 8MHz RC Oscillator Frequency vs. VCC

CALIBRATED 8 MHz RC OSCILLATOR FREQUENCY vs. V<sub>CC</sub>

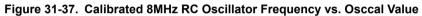

CALIBRATED 8 MHz RC OSCILLATOR FREQUENCY vs. OSCCAL VALUE

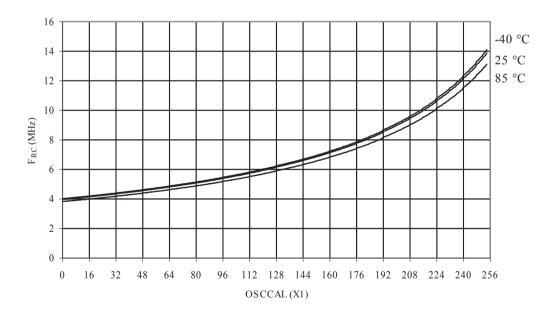

# 34.2. 40-pin PDIP

# Atmel