Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 32KB (16K x 16)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 44-VQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega32a-mur |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 13.8.3. Brown-out Detector

If the Brown-out Detector is not needed in the application, this module should be turned off. If the Brownout Detector is enabled by the BODEN Fuse, it will be enabled in all sleep modes, and hence, always consume power. In the deeper sleep modes, this will contribute significantly to the total current consumption. Refer to *Brown-out Detection* for details on how to configure the Brown-out Detector.

#### **Related Links**

Brown-out Detection on page 56

#### 13.8.4. Internal Voltage Reference

The Internal Voltage Reference will be enabled when needed by the Brown-out Detector, the Analog Comparator or the ADC. If these modules are disabled as described in the sections above, the internal voltage reference will be disabled and it will not be consuming power. When turned on again, the user must allow the reference to start up before the output is used. If the reference is kept on in sleep mode, the output can be used immediately. Refer to *Internal Voltage Reference* for details on the start-up time.

#### **Related Links**

Internal Voltage Reference on page 57

#### 13.8.5. Watchdog Timer

If the Watchdog Timer is not needed in the application, this module should be turned off. If the Watchdog Timer is enabled, it will be enabled in all sleep modes, and hence, always consume power. In the deeper sleep modes, this will contribute significantly to the total current consumption. Refer to *Watchdog Timer* for details on how to configure the Watchdog Timer.

#### **Related Links**

Watchdog Timer on page 57

#### 13.8.6. Port Pins

When entering a sleep mode, all port pins should be configured to use minimum power. The most important thing is then to ensure that no pins drive resistive loads. In sleep modes where the both the I/O clock ( $clk_{I/O}$ ) and the ADC clock ( $clk_{ADC}$ ) are stopped, the input buffers of the device will be disabled. This ensures that no power is consumed by the input logic when not needed. In some cases, the input logic is needed for detecting wake-up conditions, and it will then be enabled. Refer to the section *Digital Input Enable and Sleep Modes* for details on which pins are enabled. If the input buffer is enabled and the input signal is left floating or have an analog signal level close to  $V_{CC}/2$ , the input buffer will use excessive power.

#### **Related Links**

Digital Input Enable and Sleep Modes on page 78

#### 13.8.7. JTAG Interface and On-chip Debug System

If the On-chip debug system is enabled by the OCDEN Fuse and the chip enter Power down or Power save sleep mode, the main clock source remains enabled. In these sleep modes, this will contribute significantly to the total current consumption. There are three alternative ways to avoid this:

- Disable OCDEN Fuse.

- Disable JTAGEN Fuse.

- Write one to the JTD bit in MCUCSR.

The TDO pin is left floating when the JTAG interface is enabled while the JTAG TAP controller is not shifting data. If the hardware connected to the TDO pin does not pull up the logic level, power consumption will increase. Note that the TDI pin for the next device in the scan chain contains a pull-up

## 16.1.2. MCUCSR – MCU Control and Status Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:MCUCSROffset:0x34Reset:0Property:When addressing I/O Registers as data space the offset address is 0x54

| Bit    | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|------|---|---|---|---|---|---|

|        |   | ISC2 |   |   |   |   |   |   |

| Access |   | R/W  |   |   |   |   |   |   |

| Reset  |   | 0    |   |   |   |   |   |   |

## Bit 6 – ISC2: ISC2: Interrupt Sense Control 2

The Asynchronous External Interrupt 2 is activated by the external pin INT2 if the SREG I-bit and the corresponding interrupt mask in GICR are set. If ISC2 is written to zero, a falling edge on INT2 activates the interrupt. If ISC2 is written to one, a rising edge on INT2 activates the interrupt. Edges on INT2 are registered asynchronously. Pulses on INT2 wider than the minimum pulse width given in the table below will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. When changing the ISC2 bit, an interrupt can occur. Therefore, it is recommended to first disable INT2 by clearing its Interrupt Enable bit in the GICR Register. Then, the ISC2 bit can be changed. Finally, the INT2 Interrupt Flag should be cleared by writing a logical one to its Interrupt Flag bit (INTF2) in the GIFR Register before the interrupt is re-enabled.

| Table 16-3. As | synchronous External | I Interrupt Characteristics | 5 |

|----------------|----------------------|-----------------------------|---|

|----------------|----------------------|-----------------------------|---|

| Symbol           | Parameter                                                               | Condition | Min | Тур | Мах | Units |

|------------------|-------------------------------------------------------------------------|-----------|-----|-----|-----|-------|

| t <sub>INT</sub> | Minimum<br>pulse width<br>for<br>asynchronou<br>s external<br>interrupt |           |     | 50  |     | ns    |

**Note:** 1. For the assembly program, two temporary registers are used to minimize the time from pull-ups are set on pins 0, 1, 6, and 7, until the direction bits are correctly set, defining bit 2 and 3 as low and redefining bits 0 and 1 as strong high drivers.

#### 17.2.3. Digital Input Enable and Sleep Modes

As shown in figure Figure 17-2, the digital input signal can be clamped to ground at the input of the Schmitt Trigger. The signal denoted SLEEP in the figure, is set by the MCU Sleep Controller in Power-down mode, Power-save mode, and Standby mode to avoid high power consumption if some input signals are left floating, or have an analog signal level close to  $V_{CC}/2$ .

SLEEP is overridden for port pins enabled as external interrupt pins. If the external interrupt request is not enabled, SLEEP is active also for these pins. SLEEP is also overridden by various other alternate functions as described in Alternate Port Functions.

If a logic high level ("one") is present on an Asynchronous External Interrupt pin configured as "Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin" while the external interrupt is *not* enabled, the corresponding External Interrupt Flag will be set when resuming from the above mentioned sleep modes, as the clamping in these sleep modes produces the requested logic change.

#### 17.2.4. Unconnected Pins

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

The simplest method to ensure a defined level of an unused pin, is to enable the internal pull-up. In this case, the pull-up will be disabled during reset. If low power consumption during reset is important, it is recommended to use an external pull-up or pull-down. Connecting unused pins directly to  $V_{CC}$  or GND is not recommended, since this may cause excessive currents if the pin is accidentally configured as an output.

## 17.3. Alternate Port Functions

Most port pins have alternate functions in addition to being general digital I/Os. The following figure shows how the port pin control signals from the simplified Figure 17-2 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family.

#### 17.4.10. PINC – The Port C Input Pins Address

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

In ATmega103 compatibility mode, DDRC and PINC Registers are initialized to being Push-Pull Zero Output. The port pins assumes their initial value, even if the clock is not running. Note that the DDRC and PINC Registers are available in ATmega103 compatibility mode, and should not be used for 100% backward compatibility.

Name:PINCOffset:0x13Reset:N/AProperty:When addressing I/O Registers as data space the offset address is 0x33

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | PINC7 | PINC6 | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 |

| Access | R     | R     | R     | R     | R     | R     | R     | R     |

| Reset  | 0     | x     | x     | x     | x     | x     | x     | x     |

Bits 7:0 – PINCn: Port C Input Pins Address [n = 7:0]

#### 17.4.11. PORTD – The Port D Data Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:PORTDOffset:0x12Reset:0x00Property:When addressing I/O Registers as data space the offset address is 0x32

| Bit    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| [      | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 |

| Access | R/W    |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Bits 7:0 – PORTDn: Port D Data [n = 7:0]

## 19.11.5. OCR1AL - Output Compare Register 1 A Low byte

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:

OCR1AL

Offset:

0x2A

Reset:

0x00

Property:

When addressing I/O Registers as data space the offset address is 0x4A

| Bit    | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----|-------------|-----|-----|-----|-----|-----|-----|--|

| Γ      |     | OCR1AL[7:0] |     |     |     |     |     |     |  |

| Access | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   |  |

## Bits 7:0 – OCR1AL[7:0]: Output Compare 1 A Low byte

The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNT1). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC1x pin.

The Output Compare Registers are 16-bit in size. To ensure that both the high and low bytes are written simultaneously when the CPU writes to these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. Refer to Accessing 16-bit Registers for details.

#### 20.2.1. Registers

The Timer/Counter (TCNT2) and Output Compare Register (OCR2) are 8-bit registers. Interrupt request (shorten as Int.Req.) signals are all visible in the Timer Interrupt Flag Register (TIFR). All interrupts are individually masked with the Timer Interrupt Mask Register (TIMSK). TIFR and TIMSK are not shown in the figure since these registers are shared by other timer units.

The Timer/Counter can be clocked internally, via the prescaler, or asynchronously clocked from the TOSC1/2 pins, as detailed later in this section. The asynchronous operation is controlled by the Asynchronous Status Register (ASSR). The Clock Select logic block controls which clock source the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the clock select logic is referred to as the timer clock ( $clk_{T2}$ ).

The double buffered Output Compare Register (OCR2) is compared with the Timer/Counter value at all times. The result of the compare can be used by the waveform generator to generate a PWM or variable frequency output on the Output Compare Pin (OC2). For details, see <u>Output Compare Unit</u>. The Compare Match event will also set the Compare Flag (OCF2) which can be used to generate an Output Compare interrupt request.

#### 20.2.2. Definitions

Many register and bit references in this document are written in general form. A lower case "n" replaces the Timer/Counter number, in this case 2. However, when using the register or bit defines in a program, the precise form must be used (i.e., TCNT2 for accessing Timer/Counter2 counter value and so on).

The definitions in the following table are also used extensively throughout the document.

| воттом | The counter reaches the BOTTOM when it becomes zero (0x00).                                                                                                                                                                                                  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFF (decimal 255).                                                                                                                                                                                          |

| TOP    | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR2 Register. The assignment is dependent on the mode of operation. |

#### Table 20-1. Definitions

## 20.3. Timer/Counter Clock Sources

The Timer/Counter can be clocked by an internal synchronous or an external asynchronous clock source. The clock source  $clk_{T2}$  is by default equal to the MCU clock,  $clk_{I/O}$ . When the AS2 bit in the ASSR Register is written to logic one, the clock source is taken from the Timer/Counter Oscillator connected to TOSC1 and TOSC2. For details on asynchronous operation, refer to Asynchronous Operation of the Timer/Counter. For details on clock sources and prescaler, refer to Timer/Counter Prescaler.

#### **Related Links**

Timer/Counter0 and Timer/Counter1 Prescalers on page 102

# 20.4. Counter Unit

The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. The following figure shows a block diagram of the counter and its surrounding environment.

## 23.2.1. AVR USART vs. AVR UART – Compatibility

The USART is fully compatible with the AVR UART regarding:

- Bit locations inside all USART Registers.

- Baud Rate Generation.

- Transmitter Operation.

- Transmit Buffer Functionality.

- Receiver Operation.

However, the receive buffering has two improvements that will affect the compatibility in some special cases:

- A second Buffer Register has been added. The two Buffer Registers operate as a circular FIFO buffer. Therefore the UDR must only be read once for each incoming data! More important is the fact that the Error Flags (FE and DOR) and the ninth data bit (RXB8) are buffered with the data in the receive buffer. Therefore the status bits must always be read before the UDR Register is read. Otherwise the error status will be lost since the buffer state is lost.

- The Receiver Shift Register can now act as a third buffer level. This is done by allowing the received data to remain in the serial Shift Register (see Block Diagram in previous section) if the Buffer Registers are full, until a new start bit is detected. The USART is therefore more resistant to Data OverRun (DOR) error conditions.

The following control bits have changed name, but have same functionality and register location:

- CHR9 is changed to UCSZ2.

- OR is changed to DOR.

## 23.3. Clock Generation

The clock generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: normal asynchronous, double speed asynchronous, Master synchronous and Slave Synchronous mode. The UMSEL bit in USART Control and Status Register C (UCSRC) selects between asynchronous and synchronous operation. Double speed (Asynchronous mode only) is controlled by the U2X found in the UCSRA Register. When using Synchronous mode (UMSEL = 1), the Data Direction Register for the XCK pin (DDR\_XCK) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCK pin is only active when using Synchronous mode.

Below is a block diagram of the clock generation logic.

## 23.6.3. Transmitter Flags and Interrupts

The USART Transmitter has two flags that indicate its state: USART Data Register Empty (UDRE) and Transmit Complete (TXC). Both flags can be used for generating interrupts.

The Data Register Empty (UDRE) Flag indicates whether the transmit buffer is ready to receive new data. This bit is set when the transmit buffer is empty, and cleared when the transmit buffer contains data to be transmitted that has not yet been moved into the Shift Register. For compatibility with future devices, always write this bit to zero when writing the UCSRA Register.

When the Data Register empty Interrupt Enable (UDRIE) bit in UCSRB is written to one, the USART Data Register Empty Interrupt will be executed as long as UDRE is set (provided that global interrupts are enabled). UDRE is cleared by writing UDR. When interrupt-driven data transmission is used, the Data Register empty Interrupt routine must either write new data to UDR in order to clear UDRE or disable the Data Register empty Interrupt, otherwise a new interrupt will occur once the interrupt routine terminates.

The Transmit Complete (TXC) Flag bit is set one when the entire frame in the transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer. The TXC Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXC Flag is useful in half-duplex communication interfaces (like the RS485 standard), where a transmitting application must enter Receive mode and free the communication bus immediately after completing the transmission.

When the Transmit Compete Interrupt Enable (TXCIE) bit in UCSRB is set, the USART Transmit Complete Interrupt will be executed when the TXC Flag becomes set (provided that global interrupts are enabled). When the transmit complete interrupt is used, the interrupt handling routine does not have to clear the TXC Flag, this is done automatically when the interrupt is executed.

#### 23.6.4. Parity Generator

The Parity Generator calculates the parity bit for the serial frame data. When parity bit is enabled (UPM1 = 1), the Transmitter control logic inserts the parity bit between the last data bit and the first stop bit of the frame that is sent.

#### 23.6.5. Disabling the Transmitter

The disabling of the Transmitter (setting the TXEN to zero) will not become effective until ongoing and pending transmissions are completed (i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted). When disabled, the Transmitter will no longer override the TxD pin.

# 23.7. Data Reception – The USART Receiver

The USART Receiver is enabled by writing the Receive Enable (RXEN) bit in the UCSRB Register to one. When the Receiver is enabled, the normal pin operation of the RxD pin is overridden by the USART and given the function as the Receiver's serial input. The baud rate, mode of operation and frame format must be set up once before any serial reception can be done. If synchronous operation is used, the clock on the XCK pin will be used as transfer clock.

## 23.7.1. Receiving Frames with 5 to 8 Data Bits

The Receiver starts data reception when it detects a valid start bit. Each bit that follows the start bit will be sampled at the baud rate or XCK clock, and shifted into the Receive Shift Register until the first stop bit of a frame is received. A second stop bit will be ignored by the Receiver. When the first stop bit is received (i.e., a complete serial frame is present in the Receive Shift Register), the contents of the Shift Register will be moved into the receive buffer. The receive buffer can then be read by reading the UDR I/O location.

| Baud                | f <sub>osc</sub> = 8.0 | 0000MH | z       |       | f <sub>osc</sub> = 11 | .0592MH             | MHz f <sub>osc</sub> = 14.7456MHz |       |          |       |         |       |

|---------------------|------------------------|--------|---------|-------|-----------------------|---------------------|-----------------------------------|-------|----------|-------|---------|-------|

| Rate<br>[bps]       | U2X = 0                |        | U2X = 1 |       | U2X = 0               | = 0 U2X = 1 U2X = 0 |                                   |       | U2X = 1  |       |         |       |

| [wbo]               | UBRR                   | Error  | UBRR    | Error | UBRR                  | Error               | UBRR                              | Error | UBRR     | Error | UBRR    | Error |

| 2400                | 207                    | 0.2%   | 416     | -0.1% | 287                   | 0.0%                | 575                               | 0.0%  | 383      | 0.0%  | 767     | 0.0%  |

| 4800                | 103                    | 0.2%   | 207     | 0.2%  | 143                   | 0.0%                | 287                               | 0.0%  | 191      | 0.0%  | 383     | 0.0%  |

| 9600                | 51                     | 0.2%   | 103     | 0.2%  | 71                    | 0.0%                | 143                               | 0.0%  | 95       | 0.0%  | 191     | 0.0%  |

| 14.4k               | 34                     | -0.8%  | 68      | 0.6%  | 47                    | 0.0%                | 95                                | 0.0%  | 63       | 0.0%  | 127     | 0.0%  |

| 19.2k               | 25                     | 0.2%   | 51      | 0.2%  | 35                    | 0.0%                | 71                                | 0.0%  | 47       | 0.0%  | 95      | 0.0%  |

| 28.8k               | 16                     | 2.1%   | 34      | -0.8% | 23                    | 0.0%                | 47                                | 0.0%  | 31       | 0.0%  | 63      | 0.0%  |

| 38.4k               | 12                     | 0.2%   | 25      | 0.2%  | 17                    | 0.0%                | 35                                | 0.0%  | 23       | 0.0%  | 47      | 0.0%  |

| 57.6k               | 8                      | -3.5%  | 16      | 2.1%  | 11                    | 0.0%                | 23                                | 0.0%  | 15       | 0.0%  | 31      | 0.0%  |

| 76.8k               | 6                      | -7.0%  | 12      | 0.2%  | 8                     | 0.0%                | 17                                | 0.0%  | 11       | 0.0%  | 23      | 0.0%  |

| 115.2k              | 3                      | 8.5%   | 8       | -3.5% | 5                     | 0.0%                | 11                                | 0.0%  | 7        | 0.0%  | 15      | 0.0%  |

| 230.4k              | 1                      | 8.5%   | 3       | 8.5%  | 2                     | 0.0%                | 5                                 | 0.0%  | 3        | 0.0%  | 7       | 0.0%  |

| 250k                | 1                      | 0.0%   | 3       | 0.0%  | 2                     | -7.8%               | 5                                 | -7.8% | 3        | -7.8% | 6       | 5.3%  |

| 0.5M                | 0                      | 0.0%   | 1       | 0.0%  | -                     | -                   | 2                                 | -7.8% | 1        | -7.8% | 3       | -7.8% |

| 1M                  | -                      | -      | 0       | 0.0%  | -                     | -                   | -                                 | -     | 0        | -7.8% | 1       | -7.8% |

| Max. <sup>(1)</sup> | 0.5Mbps                |        | 1Mbps   |       | 691.2kbp              | os                  | 1.3824M                           | bps   | 921.6kbp | os    | 1.8432M | bps   |

| Table 23-11. Examples of UBRR Settings for Commonly Used Oscillator Frequenc | ies (Continued) |

|------------------------------------------------------------------------------|-----------------|

|------------------------------------------------------------------------------|-----------------|

**Note:** 1. UBRR = 0, Error = 0.0%

#### Table 23-12. Examples of UBRR Settings for Commonly Used Oscillator Frequencies (Continued)

| Baud          | f <sub>osc</sub> = 16 | .0000MH | Ιz      |       | f <sub>osc</sub> = 18 | .4320MH | 1Hz f <sub>osc</sub> = 20.00 |         |      | .0000MI | 0000MHz |         |  |

|---------------|-----------------------|---------|---------|-------|-----------------------|---------|------------------------------|---------|------|---------|---------|---------|--|

| Rate<br>[bps] | U2X = 0               |         | U2X = 1 |       | U2X = 0               | U2X = 0 |                              | U2X = 1 |      | U2X = 0 |         | U2X = 1 |  |

|               | UBRR                  | Error   | UBRR    | Error | UBRR                  | Error   | UBRR                         | Error   | UBRR | Error   | UBRR    | Error   |  |

| 2400          | 416                   | -0.1%   | 832     | 0.0%  | 479                   | 0.0%    | 959                          | 0.0%    | 520  | 0.0%    | 1041    | 0.0%    |  |

| 4800          | 207                   | 0.2%    | 416     | -0.1% | 239                   | 0.0%    | 479                          | 0.0%    | 259  | 0.2%    | 520     | 0.0%    |  |

| 9600          | 103                   | 0.2%    | 207     | 0.2%  | 119                   | 0.0%    | 239                          | 0.0%    | 129  | 0.2%    | 259     | 0.2%    |  |

| 14.4k         | 68                    | 0.6%    | 138     | -0.1% | 79                    | 0.0%    | 159                          | 0.0%    | 86   | -0.2%   | 173     | -0.2%   |  |

| 19.2k         | 51                    | 0.2%    | 103     | 0.2%  | 59                    | 0.0%    | 119                          | 0.0%    | 64   | 0.2%    | 129     | 0.2%    |  |

| 28.8k         | 34                    | -0.8%   | 68      | 0.6%  | 39                    | 0.0%    | 79                           | 0.0%    | 42   | 0.9%    | 86      | -0.2%   |  |

| 38.4k         | 25                    | 0.2%    | 51      | 0.2%  | 29                    | 0.0%    | 59                           | 0.0%    | 32   | -1.4%   | 64      | 0.2%    |  |

| 57.6k         | 16                    | 2.1%    | 34      | -0.8% | 19                    | 0.0%    | 39                           | 0.0%    | 21   | -1.4%   | 42      | 0.9%    |  |

| 76.8k         | 12                    | 0.2%    | 25      | 0.2%  | 14                    | 0.0%    | 29                           | 0.0%    | 15   | 1.7%    | 32      | -1.4%   |  |

Atmel

|   | Assembly Code Example                                                                                | C Example                                                                                                             | Comments                                                                                                          |

|---|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 6 | wait3:<br>in r16,TWCR<br>sbrs r16,TWINT<br>rjmp wait3                                                | <pre>while (!(TWCR &amp;     (1&lt;<twint)));< pre=""></twint)));<></pre>                                             | Wait for TWINT Flag set. This indicates<br>that the DATA has been transmitted, and<br>ACK/NACK has been received. |

| 7 | in r16,TWSR<br>andi r16, 0xF8<br>cpi r16, MT_DATA_ACK<br>brne ERROR                                  | <pre>if ((TWSR &amp; 0xF8) !=</pre>                                                                                   | Check value of TWI Status Register.<br>Mask prescaler bits. If status different<br>from MT_DATA_ACK go to ERROR.  |

|   | ldi r16, (1< <twint) (1<<twen) <br>(1&lt;<twsto)<br>out TWCR, r16</twsto)<br></twint) (1<<twen) <br> | TWCR = (1< <twint)  <br="">(1&lt;<twen) (1<<twsto);<="" td=""  =""><td>Transmit STOP condition.</td></twen)></twint)> | Transmit STOP condition.                                                                                          |

## 24.6.1. Transmission Modes

The TWI can operate in one of four major modes:

- Master Transmitter (MT)

- Master Receiver (MR)

- Slave Transmitter (ST)

- Slave Receiver (SR)

Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM. If other masters are present in the system, some of these might transmit data to the TWI, and then SR mode would be used. It is the application software that decides which modes are legal.

The following sections describe each of these modes. Possible status codes are described along with figures detailing data transmission in each of the modes. These figures use the following abbreviations:

| S    | START condition                         |

|------|-----------------------------------------|

| Rs   | REPEATED START condition                |

| R    | Read bit (high level at SDA)            |

| W    | Write bit (low level at SDA)            |

| А    | Acknowledge bit (low level at SDA)      |

| Ā    | Not acknowledge bit (high level at SDA) |

| Data | 8-bit data byte                         |

| Ρ    | STOP condition                          |

| SLA  | Slave Address                           |

Circles are used to indicate that the TWINT Flag is set. The numbers in the circles show the status code held in TWSR, with the prescaler bits masked to zero. At these points, actions must be taken by the application to continue or complete the TWI transfer. The TWI transfer is suspended until the TWINT Flag is cleared by software.

When the TWINT Flag is set, the status code in TWSR is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given below in the Status Code table for each mode. Note that the prescaler bits are masked to zero in these tables.

| MUX[4:0] | Single Ended Input       | Positive Differential<br>Input | Negative Differential<br>Input | Gain |

|----------|--------------------------|--------------------------------|--------------------------------|------|

| 11110    | 1.22V (V <sub>BG</sub> ) | N/A                            |                                |      |

| 11111    | 0V (GND)                 | N/A                            |                                |      |

**Note:** 1. Can be used for offset calibration.

- 2 Single Program Memory break points + 1 Program Memory break point with mask ("range break point")

- 2 Single Program Memory break points + 1 Data Memory break point with mask ("range break point")

A debugger, like the Atmel Studio<sup>®</sup>, may however use one or more of these resources for its internal purpose, leaving less flexibility to the end-user.

A list of the On-chip Debug specific JTAG instructions is given in On-chip Debug Specific JTAG Instructions.

The JTAGEN fuse must be programmed to enable the JTAG Test Access Port. In addition, the OCDEN fuse must be programmed and no Lock bits must be set for the On-chip Debug system to work. As a security feature, the On-chip Debug system is disabled when any Lock bits are set. Otherwise, the On-chip Debug system would have provided a back-door into a secured device.

The Atmel Studio enables the user to fully control execution of programs on an AVR device with On-chip Debug capability, AVR In-Circuit Emulator, or the built-in AVR Instruction Set Simulator. Atmel Studio supports source level execution of Assembly programs assembled with Atmel Corporation's AVR Assembler and C programs compiled with third party vendors' compilers.

For a full description of the Atmel Studio, please refer to the **Atmel Studio User Guide** found in the Online Help in Atmel Studio. Only highlights are presented in this document.

All necessary execution commands are available in Atmel Studio, both on source level and on disassembly level. The user can execute the program, single step through the code either by tracing into or stepping over functions, step out of functions, place the cursor on a statement and execute until the statement is reached, stop the execution, and reset the execution target. In addition, the user can have an unlimited number of code break points (using the BREAK instruction) and up to two data memory break points, alternatively combined as a mask (range) break point.

# 27.7. On-chip Debug Specific JTAG Instructions

The On-chip debug support is considered being private JTAG instructions, and distributed within ATMEL and to selected third-party vendors only. Instruction opcodes are listed for reference.

#### PRIVATE0; 0x8

Private JTAG instruction for accessing On-chip Debug system.

#### PRIVATE1; 0x9

Private JTAG instruction for accessing On-chip Debug system.

#### PRIVATE2; 0xA

Private JTAG instruction for accessing On-chip Debug system.

#### PRIVATE3; 0xB

Private JTAG instruction for accessing On-chip Debug system.

## 27.8. Using the JTAG Programming Capabilities

Programming of AVR parts via JTAG is performed via the four-pin JTAG port, TCK, TMS, TDI, and TDO. These are the only pins that need to be controlled/observed to perform JTAG programming (in addition to power pins). It is not required to apply 12V externally. The JTAGEN fuse must be programmed and the JTD bit in the MCUCSR Register must be cleared to enable the JTAG Test Access Port.

| Bit Number | Signal Name | Module |

|------------|-------------|--------|

| 111        | MUXEN_6     | ADC    |

| 110        | MUXEN_5     |        |

| 109        | MUXEN_4     |        |

| 108        | MUXEN_3     |        |

| 107        | MUXEN_2     |        |

| 106        | MUXEN_1     |        |

| 105        | MUXEN_0     |        |

| 104        | NEGSEL_2    |        |

| 103        | NEGSEL_1    |        |

| 102        | NEGSEL_0    |        |

| 101        | PASSEN      |        |

| 100        | PRECH       |        |

| 99         | SCTEST      |        |

| 98         | ST          |        |

| 97         | VCCREN      |        |

|                          | Instruction Format | t         |           |           |                                                                                                    |

|--------------------------|--------------------|-----------|-----------|-----------|----------------------------------------------------------------------------------------------------|

| Instruction              | Byte 1             | Byte 2    | Byte 3    | Byte 4    | Operation                                                                                          |

| Write Fuse Bits          | 1010 1100          | 1010 0000 | ****      | iiii iiii | Set bits = "0" to program, "1" to<br>unprogram. See Table 29-4 for<br>details.                     |

| Write Fuse High<br>Bits  | 1010 1100          | 1010 1000 | ****      | iiii iiii | Set bits = "0" to program, "1" to<br>unprogram. See Table 29-3 for<br>details.                     |

| Read Fuse Bits           | 0101 0000          | 0000 0000 | XXXX XXXX | 0000 0000 | Read Fuse Bits. "0" = programmed,<br>"1" = unprogrammed. See table<br>Table 29-4 for details.      |

| Read Fuse High<br>Bits   | 0101 1000          | 0000 1000 | XXXX XXXX | 0000 0000 | Read Fuse high bits. "0" =<br>programmed, "1" = unprogrammed.<br>See table Table 29-3 for details. |

| Read Calibration<br>Byte | 0011 1000          | XXXX XXXX | dd00 0000 | 0000 0000 | Read Calibration Byte o at address b.                                                              |

#### Note:

- a = address high bits

- b = address low bits

- H = 0 Low byte, 1 High byte

- o = data out

- i = data in

- **x** = don't care

#### 29.9.4. SPI Serial Programming Characteristics

For characteristics of the SPI module, see SPI Timing Characteristics.

#### Related Links

SPI Timing Characteristics on page 365

# 29.10. Programming Via the JTAG Interface

Programming through the JTAG interface requires control of the four JTAG specific pins: TCK, TMS, TDI, and TDO. Control of the Reset and clock pins is not required.

To be able to use the JTAG interface, the JTAGEN fuse must be programmed. The device is default shipped with the Fuse programmed. In addition, the JTD bit in MCUCSR must be cleared. Alternatively, if the JTD bit is set, the external reset can be forced low. Then, the JTD bit will be cleared after two chip clocks, and the JTAG pins are available for programming. This provides a means of using the JTAG pins as normal port pins in running mode while still allowing In-System Programming via the JTAG interface. Note that this technique can not be used when using the JTAG pins for Boundary-scan or On-chip Debug. In these cases the JTAG pins must be dedicated for this purpose.

As a definition in this data sheet, the LSB is shifted in and out first of all Shift Registers.

#### 29.10.1. Programming Specific JTAG Instructions

The instruction register is 4-bit wide, supporting up to 16 instructions. The JTAG instructions useful for Programming are listed below.

# 31.5. Standby Supply Current

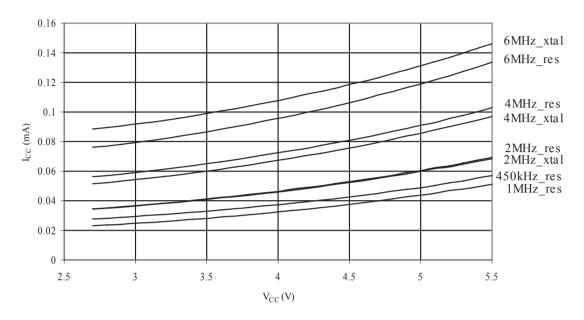

#### Figure 31-16. Standby Supply Current vs. VCC (WDT Disabled)

STANDBY SUPPLY CURRENT vs. V<sub>CC</sub> WATCHDOG TIMER DIS ABLED

## 31.6. Pin Pull-up

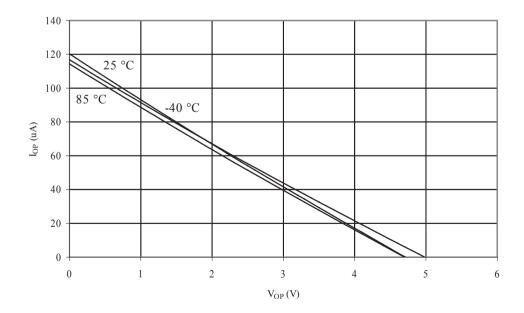

# Figure 31-17. I/O Pin Pull-up Resistor Current vs. Input Voltage (VCC = 5V)

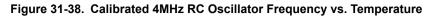

CALIBRATED 4 MHz RC OSCILLATOR FREQUENCY vs. TEMPERATURE

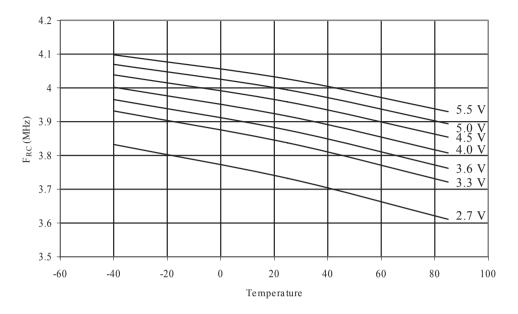

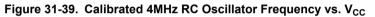

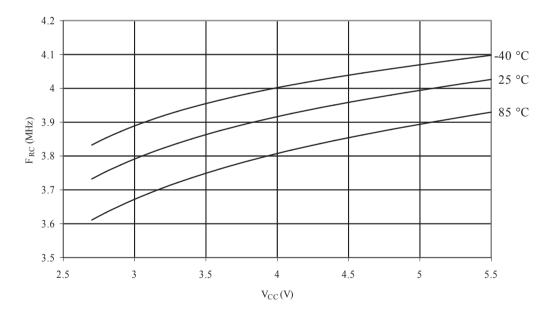

CALIBRATED 4 MHz RC OSCILLATOR FREQUENCY vs.  $V_{\mbox{CC}}$

| Address     | Name   | Bit 7                                       | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|-------------|--------|---------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| 0x15 (0x35) | PORTC  | PORTC7                                      | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 |

| 0x14 (0x34) | DDRC   | DDC7                                        | DDC6   | DDC5   | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   |

| 0x13 (0x33) | PINC   | PINC7                                       | PINC6  | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  |

| 0x12 (0x32) | PORTD  | PORTD7                                      | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 |

| 0x11 (0x31) | DDRD   | DDD7                                        | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   |

| 0x10 (0x30) | PIND   | PIND7                                       | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  |

| 0x0F (0x2F) | SPDR   | SPI Data Register                           |        |        |        |        |        |        |        |

| 0x0E (0x2E) | SPSR   | SPIF                                        | WCOL   | -      | -      | -      | -      | -      | SPI2X  |

| 0x0D (0x2D) | SPCR   | SPIE                                        | SPE    | DORD   | MSTR   | CPOL   | CPHA   | SPR1   | SPR0   |

| 0x0C (0x2C) | UDR    | USART I/O Data Register                     |        |        |        |        |        |        |        |

| 0x0B (0x2B) | UCSRA  | RXC                                         | TXC    | UDRE   | FE     | DOR    | PE     | U2X    | MPCM   |

| 0x0A (0x2A) | UCSRB  | RXCIE                                       | TXCIE  | UDRIE  | RXEN   | TXEN   | UCSZ2  | RXB8   | TXB8   |

| 0x09 (0x29) | UBRRL  | USART Baud Rate Register Low byte           |        |        |        |        |        |        |        |

| 0x08 (0x28) | ACSR   | ACD                                         | ACBG   | ACO    | ACI    | ACIE   | ACIC   | ACIS1  | ACIS0  |

| 0x07 (0x27) | ADMUX  | REFS1                                       | REFS0  | ADLAR  | MUX4   | MUX3   | MUX2   | MUX1   | MUX0   |

| 0x06 (0x26) | ADCSRA | ADEN                                        | ADSC   | ADATE  | ADIF   | ADIE   | ADPS2  | ADPS1  | ADPS0  |

| 0x05 (0x25) | ADCH   | ADC Data Register High byte                 |        |        |        |        |        |        |        |

| 0x04 (0x24) | ADCL   | ADC Data Register Low byte                  |        |        |        |        |        |        |        |

| 0x03 (0x23) | TWDR   | Two-wire Serial Interface Data Register     |        |        |        |        |        |        |        |

| 0x02 (0x22) | TWAR   | TWA6                                        | TWA5   | TWA4   | TWA3   | TWA2   | TWA1   | TWA0   | TWGCE  |

| 0x01 (0x21) | TWSR   | TWS7                                        | TWS6   | TWS5   | TWS4   | TWS3   | -      | TWPS1  | TWPS0  |

| 0x00 (0x20) | TWBR   | Two-wire Serial Interface Bit Rate Register |        |        |        |        |        |        |        |

#### Note:

- When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debugger specific documentation for details on how to use the OCDR Register.

- 2. Refer to the USART description for details on how to access UBRRH and UCSRC.

- 3. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 4. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

| DATA TRANSFER INSTRUCTIONS |          |                                  |                                              |       |         |  |

|----------------------------|----------|----------------------------------|----------------------------------------------|-------|---------|--|

| Mnemonics                  | Operands | Description                      | Operation                                    | Flags | #Clocks |  |

| LD                         | Rd, Y+   | Load Indirect and Post-Inc.      | $Rd \gets (Y),  Y \gets Y + 1$               | None  | 2       |  |

| LD                         | Rd, - Y  | Load Indirect and Pre-Dec.       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$      | None  | 2       |  |

| LDD                        | Rd,Y+q   | Load Indirect with Displacement  | $Rd \gets (Y + q)$                           | None  | 2       |  |

| LD                         | Rd, Z    | Load Indirect                    | $Rd \leftarrow (Z)$                          | None  | 2       |  |

| LD                         | Rd, Z+   | Load Indirect and Post-Inc.      | $Rd \leftarrow (Z), Z \leftarrow Z\text{+}1$ | None  | 2       |  |

| LD                         | Rd, -Z   | Load Indirect and Pre-Dec.       | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$      | None  | 2       |  |

| LDD                        | Rd, Z+q  | Load Indirect with Displacement  | $Rd \gets (Z + q)$                           | None  | 2       |  |

| LDS                        | Rd, k    | Load Direct from SRAM            | $Rd \leftarrow (k)$                          | None  | 2       |  |

| ST                         | X, Rr    | Store Indirect                   | $(X) \leftarrow Rr$                          | None  | 2       |  |

| ST                         | X+, Rr   | Store Indirect and Post-Inc.     | $(X) \gets Rr, X \gets X + 1$                | None  | 2       |  |

| ST                         | - X, Rr  | Store Indirect and Pre-Dec.      | $X \leftarrow X - 1,  (X) \leftarrow Rr$     | None  | 2       |  |

| ST                         | Y, Rr    | Store Indirect                   | (Y) ¬ Rr                                     | None  | 2       |  |

| ST                         | Y+, Rr   | Store Indirect and Post-Inc.     | $(Y) \leftarrow Rr,  Y \leftarrow Y + 1$     | None  | 2       |  |

| ST                         | - Y, Rr  | Store Indirect and Pre-Dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$      | None  | 2       |  |

| STD                        | Y+q,Rr   | Store Indirect with Displacement | (Y + q) ← Rr                                 | None  | 2       |  |

| ST                         | Z, Rr    | Store Indirect                   | (Z) ← Rr                                     | None  | 2       |  |

| ST                         | Z+, Rr   | Store Indirect and Post-Inc.     | $(Z) \leftarrow Rr,  Z \leftarrow Z + 1$     | None  | 2       |  |

| ST                         | - Z, Rr  | Store Indirect and Pre-Dec.      | $Z \leftarrow Z - 1$ , (Z) $\leftarrow Rr$   | None  | 2       |  |

| STD                        | Z+q,Rr   | Store Indirect with Displacement | $(Z + q) \leftarrow Rr$                      | None  | 2       |  |

| STS                        | k, Rr    | Store Direct to SRAM             | (k) ← Rr                                     | None  | 2       |  |

| LPM                        |          | Load Program Memory              | R0 ← (Z)                                     | None  | 3       |  |

| LPM                        | Rd, Z    | Load Program Memory              | $Rd \leftarrow (Z)$                          | None  | 3       |  |

| LPM                        | Rd, Z+   | Load Program Memory and Post-Inc | $Rd \leftarrow (Z), Z \leftarrow Z\text{+}1$ | None  | 3       |  |

| SPM                        |          | Store Program Memory             | (Z) ← R1:R0                                  | None  | -       |  |

| IN                         | Rd, P    | In Port                          | $Rd \gets P$                                 | None  | 1       |  |

| OUT                        | P, Rr    | Out Port                         | P ← Rr                                       | None  | 1       |  |

| PUSH                       | Rr       | Push Register on Stack           | $STACK \gets Rr$                             | None  | 2       |  |

| POP                        | Rd       | Pop Register from Stack          | $Rd \gets STACK$                             | None  | 2       |  |

# Atmel

## 36.8. 8155B - 07/2009

- 1. Updated Errata.

- 2. Updated the last page with Atmel's new addresses.

## 36.9. 8155A - 06/2008

1. Initial revision (Based on the ATmega32/L datasheet 2503N-AVR-06/08)

Changes done compared ATmega32/L datasheet 2503N-AVR-06/08:

- Updated description in Stack Pointer.

- All Electrical characteristics is moved to Electrical Characteristics.

- Register descriptions are moved to sub sections at the end of each chapter.

- Test limits of Reset Pull-up Resistor (R<sub>RST</sub>) in DC Characteristics.

- New graphs in Typical Characteristics.

- New Ordering Information.