Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | AVR                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 32KB (16K x 16)                                                        |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega32a-pn |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

as an address pointer for look up tables in Flash Program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

The Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every Program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot program section and the Application program section. Both sections have dedicated Lock Bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are executed). The Stack Pointer SP is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F.

# 10.2. ALU – Arithmetic Logic Unit

The high-performance Atmel AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

# 10.3. Status Register

The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.

# 12.3. Default Clock Source

The device is shipped with CKSEL = "0001" and SUT = "10". The default clock source setting is therefore the Internal RC Oscillator with longest startup time. This default setting ensures that all users can make their desired clock source setting using an In-System or Parallel Programmer.

# 12.4. Crystal Oscillator

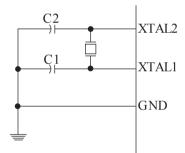

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in the figure below. Either a quartz crystal or a ceramic resonator may be used. The CKOPT Fuse selects between two different Oscillator amplifier modes. When CKOPT is programmed, the Oscillator output will oscillate a full rail-to-rail swing on the output. This mode is suitable when operating in a very noisy environment or when the output from XTAL2 drives a second clock buffer. This mode has a wide frequency range. When CKOPT is unprogrammed, the Oscillator has a smaller output swing. This reduces power consumption considerably. This mode has a limited frequency range and it cannot be used to drive other clock buffers.

For resonators, the maximum frequency is 8MHz with CKOPT unprogrammed and 16MHz with CKOPT programmed. C1 and C2 should always be equal for both crystals and resonators. The optimal value of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for choosing capacitors for use with crystals are given in the next table. For ceramic resonators, the capacitor values given by the manufacturer should be used.

## Figure 12-2. Crystal Oscillator Connections

The Oscillator can operate in three different modes, each optimized for a specific frequency range. The operating mode is selected by the fuses CKSEL3:1 as shown in the following table.

| Table 12-3. | Crystal | Oscillator | Operating | Modes |

|-------------|---------|------------|-----------|-------|

|-------------|---------|------------|-----------|-------|

| CKOPT <sup>(1)</sup> | CKSEL3:1           | Frequency Range(MHz) | Recommended Range for Capacitors C1 and C2 for Use with Crystals (pF) |

|----------------------|--------------------|----------------------|-----------------------------------------------------------------------|

| 1                    | 101 <sup>(2)</sup> | 0.4 - 0.9            | -                                                                     |

| 1                    | 110                | 0.9 - 3.0            | 12 - 22                                                               |

| 1                    | 111                | 3.0 - 8.0            | 12 - 22                                                               |

| 0                    | 101, 110, 111      | 1.0 -16.0            | 12 - 22                                                               |

## Note:

- 1. When CKOPT is programmed (0), the oscillator output will be a full rail-to-rail swing on the output.

- 2. This option should not be used with crystals, only with ceramic resonators.

# C Code Example

```

void Move_interrupts(void)

{

/* Enable change of Interrupt Vectors */

GICR = (1<<IVCE);

/* Move interrupts to boot Flash section */

GICR = (1<<IVSEL);

}</pre>

```

# 16. External Interrupts

The External Interrupts are triggered by the INT0, INT1, and INT2 pins. Observe that, if enabled, the interrupts will trigger even if the INT0:2 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level (INT2 is only an edge triggered interrupt). This is set up as indicated in the specification for the MCU Control Register – MCUCR – and MCU Control and Status Register – MCUCSR. When the external interrupt is enabled and is configured as level triggered (only INT0/INT1), the interrupt will trigger as long as the pin is held low. Note that recognition of falling or rising edge interrupts on INT0 and INT1 requires the presence of an I/O clock, described in "Clock Systems and their Distribution" on page 25. Low level interrupts can be used for waking the part also from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. This makes the MCU less sensitive to noise. The changed level is sampled twice by the Watchdog Oscillator clock. The period of the Watchdog Oscillator is 1  $\mu$ s (nominal) at 5.0V and 25°C. The frequency of the Watchdog Oscillator is voltage dependent as shown in "Electrical Characteristics" on page 296. The MCU will wake up if the input has the required level during this sampling or if it is held until the end of the start-up time. The start-up time is defined by the SUT fuses as described in "System Clock and Clock Options" on page 25. If the level is sampled twice by the Watchdog Oscillator clock but disappears before the end of the startup time, the MCU will still wake up, but no interrupt will be generated. The required level must be held long enough for the MCU to complete the wake up to trigger the level interrupt.

# **Related Links**

Clock Systems and their Distribution on page 39 Electrical Characteristics on page 359 System Clock and Clock Options on page 39

# 16.1. Register Description

**Note:** 1. For the assembly program, two temporary registers are used to minimize the time from pull-ups are set on pins 0, 1, 6, and 7, until the direction bits are correctly set, defining bit 2 and 3 as low and redefining bits 0 and 1 as strong high drivers.

#### 17.2.3. Digital Input Enable and Sleep Modes

As shown in figure Figure 17-2, the digital input signal can be clamped to ground at the input of the Schmitt Trigger. The signal denoted SLEEP in the figure, is set by the MCU Sleep Controller in Power-down mode, Power-save mode, and Standby mode to avoid high power consumption if some input signals are left floating, or have an analog signal level close to  $V_{CC}/2$ .

SLEEP is overridden for port pins enabled as external interrupt pins. If the external interrupt request is not enabled, SLEEP is active also for these pins. SLEEP is also overridden by various other alternate functions as described in Alternate Port Functions.

If a logic high level ("one") is present on an Asynchronous External Interrupt pin configured as "Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin" while the external interrupt is *not* enabled, the corresponding External Interrupt Flag will be set when resuming from the above mentioned sleep modes, as the clamping in these sleep modes produces the requested logic change.

#### 17.2.4. Unconnected Pins

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

The simplest method to ensure a defined level of an unused pin, is to enable the internal pull-up. In this case, the pull-up will be disabled during reset. If low power consumption during reset is important, it is recommended to use an external pull-up or pull-down. Connecting unused pins directly to  $V_{CC}$  or GND is not recommended, since this may cause excessive currents if the pin is accidentally configured as an output.

# 17.3. Alternate Port Functions

Most port pins have alternate functions in addition to being general digital I/Os. The following figure shows how the port pin control signals from the simplified Figure 17-2 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family.

| Signal Name | Full Name                               | Description                                                                                                                                                                                                                                                                          |

|-------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDOE        | Data Direction<br>Override Enable       | If this signal is set, the Output Driver Enable is controlled by the DDOV signal. If this signal is cleared, the Output driver is enabled by the DDxn Register bit.                                                                                                                  |

| DDOV        | Data Direction<br>Override Value        | If DDOE is set, the Output Driver is enabled/disabled when DDOV is set/cleared, regardless of the setting of the DDxn Register bit.                                                                                                                                                  |

| PVOE        | Port Value Override<br>Enable           | If this signal is set and the Output Driver is enabled, the port value is controlled by the PVOV signal. If PVOE is cleared, and the Output Driver is enabled, the port Value is controlled by the PORTxn Register bit.                                                              |

| PVOV        | Port Value Override<br>Value            | If PVOE is set, the port value is set to PVOV, regardless of the setting of the PORTxn Register bit.                                                                                                                                                                                 |

| DIEOE       | Digital Input Enable<br>Override Enable | If this bit is set, the Digital Input Enable is controlled by the DIEOV signal. If this signal is cleared, the Digital Input Enable is determined by MCU state (Normal mode, sleep mode).                                                                                            |

| DIEOV       | Digital Input Enable<br>Override Value  | If DIEOE is set, the Digital Input is enabled/disabled when DIEOV is set/<br>cleared, regardless of the MCU state (Normal mode, sleep mode).                                                                                                                                         |

| DI          | Digital Input                           | This is the Digital Input to alternate functions. In the figure, the signal is connected to the output of the Schmitt Trigger but before the synchronizer. Unless the Digital Input is used as a clock source, the module with the alternate function will use its own synchronizer. |

| AIO         | Analog Input/Output                     | This is the Analog Input/output to/from alternate functions. The signal is connected directly to the pad, and can be used bi-directionally.                                                                                                                                          |

The following subsections shortly describe the alternate functions for each port, and relate the overriding signals to the alternate function. Refer to the alternate function description for further details.

# 17.3.1. Alternate Functions of Port A

Port A has an alternate function as analog input for the ADC as shown in the table below. If some Port A pins are configured as outputs, it is essential that these do not switch when a conversion is in progress. This might corrupt the result of the conversion.

Table 17-3. Port A Pins Alternate Functions

| Port Pin | Alternate Functions        |

|----------|----------------------------|

| PA7      | ADC7 (ADC input channel 7) |

| PA6      | ADC6 (ADC input channel 6) |

| PA5      | ADC5 (ADC input channel 5) |

| PA4      | ADC4 (ADC input channel 4) |

| PA3      | ADC3 (ADC input channel 3) |

| PA2      | ADC2 (ADC input channel 2) |

| PA1      | ADC1 (ADC input channel 1) |

| PA0      | ADC0 (ADC input channel 0) |

# 19.7.2. Compare Match Blocking by TCNTn Write

All CPU writes to the TCNTn Register will block any Compare Match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCRnx to be initialized to the same value as TCNTn without triggering an interrupt when the Timer/Counter clock is enabled.

## 19.7.3. Using the Output Compare Unit

Since writing TCNTn in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNTn when using any of the Output Compare channels, independent of whether the Timer/Counter is running or not. If the value written to TCNTn equals the OCRnx value, the Compare Match will be missed, resulting in incorrect waveform generation. Do not write the TCNTn equal to TOP in PWM modes with variable TOP values. The Compare Match for the TOP will be ignored and the counter will continue to 0xFFFF. Similarly, do not write the TCNTn value equal to BOTTOM when the counter is downcounting.

The setup of the OCnx should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OCnx value is to use the Force Output Compare (FOCnx) strobe bits in Normal mode. The OCnx Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COMnx1:0 bits are not double buffered together with the compare value. Changing the COMnx1:0 bits will take effect immediately.

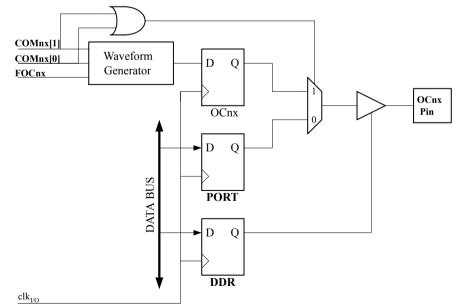

# 19.8. Compare Match Output Unit

The Compare Output mode (COMnx1:0) bits have two functions. The waveform generator uses the COMnx1:0 bits for defining the Output Compare (OCnx) state at the next Compare Match. Secondly the COMnx1:0 bits control the OCnx pin output source. The figure below shows a simplified schematic of the logic affected by the COMnx1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COMnx1:0 bits are shown. When referring to the OCnx state, the reference is for the internal OCnx Register, not the OCnx pin. If a System Reset occur, the OCnx Register is reset to "0".

#### Figure 19-5. Compare Match Output Unit, Schematic

**Atmel**

## 19.11.3. TCNT1L – Timer/Counter1 Low byte

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:

TCNT1L

Offset:

0x2C

Reset:

0x00

Property:

When addressing I/O Registers as data space the offset address is 0x4C

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

| Γ      |     |     |     | TCNT | 1L[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

## Bits 7:0 – TCNT1L[7:0]: Timer/Counter 1 Low byte

The two *Timer/Counter* I/O locations (TCNT1H and TCNT1L, combined TCNT1) give direct access, both for read and for write operations, to the Timer/Counter unit 16-bit counter. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. Refer to Accessing 16-bit Registers for details.

Modifying the counter (TCNT1) while the counter is running introduces a risk of missing a compare match between TCNT1 and one of the OCR1x Registers.

Writing to the TCNT1 Register blocks (removes) the compare match on the following timer clock for all compare units.

small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2 and TCNT2.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches MAX. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

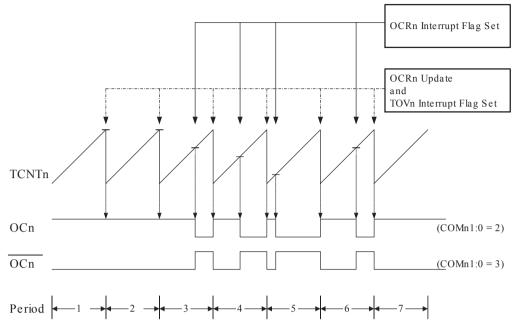

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2 pin. Setting the COM21:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM21:0 to 3. The actual OC2 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2 Register at the Compare Match between OCR2 and TCNT2, and clearing (or setting) the OC2 Register at the timer clock cycle the counter is cleared (changes from MAX to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{\rm OCnPWM} = \frac{f_{\rm clk\_I/O}}{N \cdot 256}$$

The N variable represents the prescaler factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2 Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2 is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2 equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM21:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2 to toggle its logical level on each Compare Match (COM21:0 = 1). The waveform generated will have a maximum frequency of  $f_{oc2} = f_{clk_l/O}/2$  when OCR2 is set to zero. This feature is similar to the OC2 toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

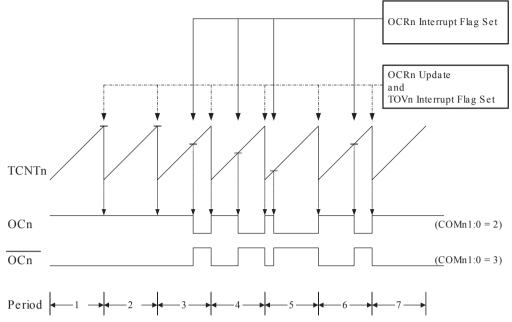

# 20.7.4. Phase Correct PWM Mode

The phase correct PWM mode (WGM21:0 = 1) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to MAX and then from MAX to BOTTOM. In non-inverting Compare Output

Figure 21-6. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV0) is set each time the counter reaches MAX. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC0 pin. Setting the COM01:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM01:0 to 3 (see Table 21-4). The actual OC0 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC0 Register at the Compare Match between OCR0 and TCNT0, and clearing (or setting) the OC0 Register at the timer clock cycle the counter is cleared (changes from MAX to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{\rm OCnPWM} = \frac{f_{\rm clk\_I/O}}{N \cdot 256}$$

The N variable represents the prescaler factor (1, 8, 32, 64, 128, 256 or 1024).

The extreme values for the OCR0 Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR0 is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR0 equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM01:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC0 to toggle its logical level on each Compare Match (COM01:0 = 1). The waveform generated will have a maximum frequency of  $f_{oc0} = f_{clk_l/O}/2$  when OCR0 is set to zero. This feature is similar to the OC0 toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

# 21.7.4. Phase Correct PWM Mode

The phase correct PWM mode (WGM01:0 = 1) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to MAX and then from MAX to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC0) is cleared on the Compare Match between TCNT0 and OCR0 while upcounting, and set on the Compare Match while downcounting. In inverting Output Compare mode, the

```

Assembly Code Example<sup>(1)</sup>

SPI SlaveInit:

; Set MISO output, all others input

ldi r17, (1<<DD MISO)

out DDR_SPI, r17

; Enable SPI

ldi r17, (1<<SPE)

out SPCR, r17

ret

SPI SlaveReceive:

; Wait for reception complete

sbis SPSR,SPIF

rjmp SPI_SlaveReceive

; Read received data and return

r16,SPDR

in

ret

C Code Example<sup>(1)</sup>

void SPI SlaveInit(void)

{

/* Set MISO output, all others input */

DDR SPI = (1<<DD MISO);

/* Enable SPI */

SPCR = (1 < < SPE);

char SPI SlaveReceive (void)

{

/* Wait for reception complete */

while(!(SPSR & (1<<SPIF)))</pre>

/* Return Data Register */

return SPDR;

}

```

Note: 1. See About Code Examples.

## **Related Links**

Pin Configurations on page 13 Alternate Functions of Port B on page 81 Alternate Port Functions on page 78 About Code Examples on page 19

# 22.3. SS Pin Functionality

# 22.3.1. Slave Mode

When the SPI is configured as a Slave, the Slave Select ( $\overline{SS}$ ) pin is always input. When  $\overline{SS}$  is held low, the SPI is activated, and MISO becomes an output if configured so by the user. All other pins are inputs. When  $\overline{SS}$  is driven high, all pins are inputs, and the SPI is passive, which means that it will not receive incoming data. The SPI logic will be reset once the  $\overline{SS}$  pin is driven high.

The  $\overline{SS}$  pin is useful for packet/byte synchronization to keep the slave bit counter synchronous with the master clock generator. When the  $\overline{SS}$  pin is driven high, the SPI slave will immediately reset the send and receive logic, and drop any partially received data in the Shift Register.

## 22.3.2. Master Mode

When the SPI is configured as a Master (MSTR in SPCR is set), the user can determine the direction of the  $\overline{SS}$  pin.

| Table 23-1 | . Equations for | Calculating Baud | Rate Register Setting |

|------------|-----------------|------------------|-----------------------|

|------------|-----------------|------------------|-----------------------|

| Operating Mode                              | Equation for Calculating Baud<br>Rate <sup>(1)</sup> | Equation for Calculating UBRR<br>Value                         |

|---------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|

| Asynchronous Normal<br>mode (U2X = 0)       | $BAUD = \frac{f_{OSC}}{16(UBRR + 1)}$                | $\mathbf{UBRR} = \frac{f_{\mathrm{OSC}}}{16\mathrm{BAUD}} - 1$ |

| Asynchronous Double<br>Speed mode (U2X = 1) | $BAUD = \frac{f_{OSC}}{8(UBRR + 1)}$                 | $\mathbf{UBRR} = \frac{f_{\mathrm{OSC}}}{8\mathrm{BAUD}} - 1$  |

| Synchronous Master mode                     | $BAUD = \frac{f_{OSC}}{2(UBRR+1)}$                   | $\mathbf{UBRR} = \frac{f_{\mathrm{OSC}}}{2\mathrm{BAUD}} - 1$  |

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps).

BAUD Baud rate (in bits per second, bps).

fosc System oscillator clock frequency.

**UBRR** Contents of the UBRRH and UBRRL Registers, (0-4095).

Some examples of UBRR values for some system clock frequencies are found in Table 23-9.

# 23.3.2. Double Speed Operation (U2X)

The transfer rate can be doubled by setting the U2X bit in UCSRA. Setting this bit only has effect for the asynchronous operation. Set this bit to zero when using synchronous operation.

Setting this bit will reduce the divisor of the baud rate divider from 16 to 8, effectively doubling the transfer rate for asynchronous communication. Note however that the Receiver will in this case only use half the number of samples (reduced from 16 to 8) for data sampling and clock recovery, and therefore a more accurate baud rate setting and system clock are required when this mode is used.

For the Transmitter, there are no downsides.

# 23.3.3. External Clock

External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 23-2.

External clock input from the XCK pin is sampled by a synchronization register to minimize the chance of meta-stability. The output from the synchronization register must then pass through an edge detector before it can be used by the Transmitter and Receiver. This process introduces a two CPU clock period delay and therefore the maximum external XCK clock frequency is limited by the following equation:

$$f_{\rm XCK} < \frac{f_{\rm OSC}}{4}$$

The value of  $f_{osc}$  depends on the stability of the system clock source. It is therefore recommended to add some margin to avoid possible loss of data due to frequency variations.

# 23.3.4. Synchronous Clock Operation

When Synchronous mode is used (UMSEL = 1), the XCK pin will be used as either clock input (Slave) or clock output (Master). The dependency between the clock edges and data sampling or data change is the same. The basic principle is that data input (on RxD) is sampled at the opposite XCK clock edge of the edge the data output (TxD) is changed.

# 23.11.3. UCSRB – USART Control and Status Register B

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses.

Name:UCSRBOffset:0x0AReset:0x00Property:When addressing I/O Registers as data space the offset address is 0x2A

| Bit    | 7     | 6     | 5     | 4    | 3    | 2     | 1    | 0    |

|--------|-------|-------|-------|------|------|-------|------|------|

|        | RXCIE | TXCIE | UDRIE | RXEN | TXEN | UCSZ2 | RXB8 | TXB8 |

| Access | R/W   | R/W   | R/W   | R/W  | R/W  | R/W   | R    | R/W  |

| Reset  | 0     | 0     | 0     | 0    | 0    | 0     | 0    | 0    |

## Bit 7 – RXCIE: RX Complete Interrupt Enable

Writing this bit to one enables interrupt on the RXC Flag. A USART Receive Complete interrupt will be generated only if the RXCIE bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXC bit in UCSRA is set.

## Bit 6 – TXCIE: TX Complete Interrupt Enable

Writing this bit to one enables interrupt on the TXC Flag. A USART Transmit Complete interrupt will be generated only if the TXCIE bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXC bit in UCSRA is set.

## Bit 5 – UDRIE: USART Data Register Empty Interrupt Enable

Writing this bit to one enables interrupt on the UDRE Flag. A Data Register Empty interrupt will be generated only if the UDRIE bit is written to one, the Global Interrupt Flag in SREG is written to one and the UDRE bit in UCSRA is set.

## Bit 4 – RXEN: Receiver Enable

Writing this bit to one enables the USART Receiver. The Receiver will override normal port operation for the RxD pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FE, DOR and PE Flags.

## Bit 3 – TXEN: Transmitter Enable

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxD pin when enabled. The disabling of the Transmitter (writing TXEN to zero) will not become effective until ongoing and pending transmissions are completed (i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted). When disabled, the Transmitter will no longer override the TxD port.

## Bit 2 – UCSZ2: Character Size

The UCSZ2 bits combined with the UCSZ1:0 bit in UCSRC sets the number of data bits (Character Size) in a frame the Receiver and Transmitter use.

## Bit 1 – RXB8: Receive Data Bit 8

RXB8 is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDR.

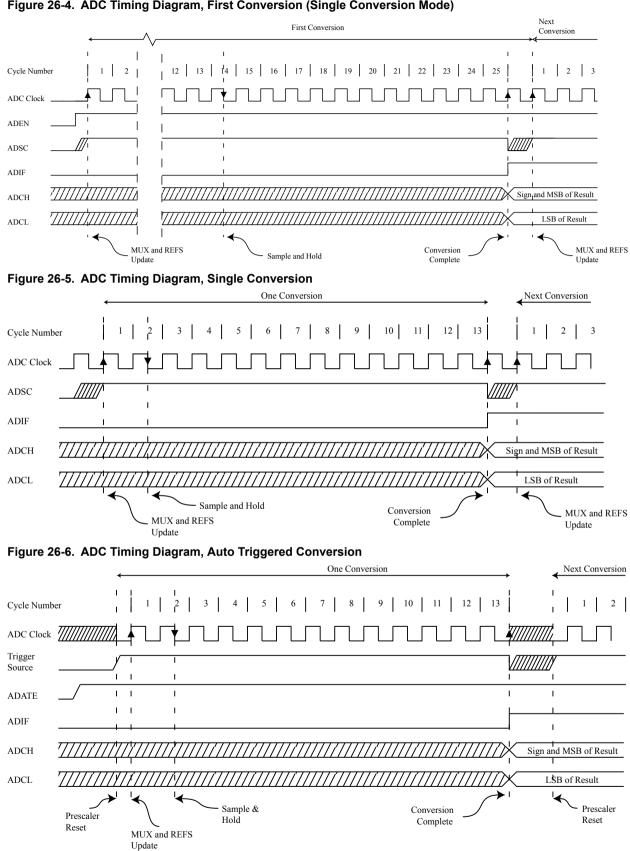

#### Figure 26-4. ADC Timing Diagram, First Conversion (Single Conversion Mode)

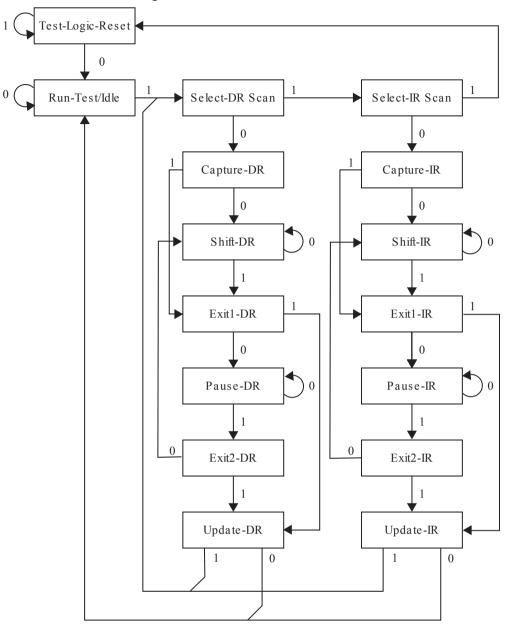

Figure 27-2. TAP Controller State Diagram

# 27.4. TAP Controller

The TAP controller is a 16-state finite state machine that controls the operation of the Boundary-scan circuitry, JTAG programming circuitry, or On-chip Debug system. The state transitions depicted in Figure 27-2 depend on the signal present on TMS (shown adjacent to each state transition) at the time of the rising edge at TCK. The initial state after a Power-on Reset is Test-Logic-Reset.

As a definition in this document, the LSB is shifted in and out first for all Shift Registers.

Assuming Run-Test/Idle is the present state, a typical scenario for using the JTAG interface is:

• At the TMS input, apply the sequence 1, 1, 0, 0 at the rising edges of TCK to enter the Shift Instruction Register – Shift-IR state. While in this state, shift the 4 bits of the JTAG instructions into the JTAG instruction register from the TDI input at the rising edge of TCK. The TMS input must be

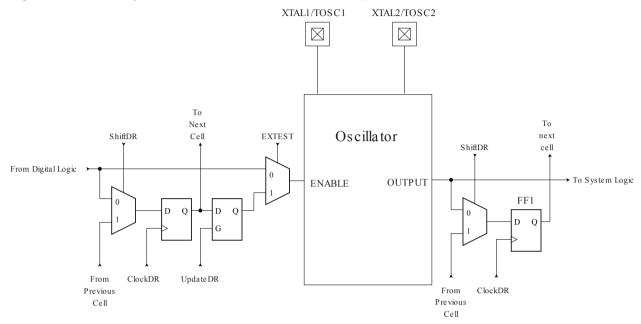

The figure below shows how each Oscillator with external connection is supported in the scan chain. The Enable signal is supported with a general boundary-scan cell, while the Oscillator/Clock output is attached to an observe-only cell. In addition to the main clock, the Timer Oscillator is scanned in the same way. The output from the internal RC Oscillator is not scanned, as this Oscillator does not have external connections.

#### Figure 27-9. Boundary-scan Cells for Oscillators and Clock Options

The following table summaries the scan registers for the external clock pin XTAL1, oscillators with XTAL1/ XTAL2 connections as well as 32kHz Timer Oscillator.

Table 27-3. Scan Signals for the Oscillators<sup>(1)(2)(3)</sup>

| Enable signal | Scanned Clock Line | Clock Option                                   | Scanned Clock Line when not<br>Used |

|---------------|--------------------|------------------------------------------------|-------------------------------------|

| EXTCLKEN      | EXTCLK (XTAL1)     | External Clock                                 | 0                                   |

| OSCON         | OSCCK              | External Crystal<br>External Ceramic Resonator | 0                                   |

| RCOSCEN       | RCCK               | External RC                                    | 1                                   |

| OSC32EN       | OSC32CK            | Low Freq. External Crystal                     | 0                                   |

| TOSKON        | TOSCK              | 32kHz Timer Oscillator                         | 0                                   |

#### Note:

- 1. Do not enable more than one clock source as main clock at a time.

- 2. Scanning an Oscillator output gives unpredictable results as there is a frequency drift between the Internal Oscillator and the JTAG TCK clock. If possible, scanning an external clock is preferred.

- 3. The clock configuration is programmed by fuses. As a fuse does not change run-time, the clock configuration is considered fixed for a given application. The user is advised to scan the same clock option as to be used in the final system. The enable signals are supported in the scan chain because the system logic can disable clock options in sleep modes, thereby disconnecting the Oscillator pins from the scan path if not provided. The INTCAP fuses are not supported in the scan-

#### 28.8.12. Simple Assembly Code Example for a Boot Loader

```

;-the routine writes one page of data from RAM to Flash

; the first data location in RAM is pointed to by the Y pointer

; the first data location in Flash is pointed to by the Z-pointer

;-error handling is not included

;-the routine must be placed inside the boot space

; (at least the Do spm sub routine). Only code inside NRWW section can

; be read during self-programming (page erase and page write).

;-registers used: r0, r1, temp1 (r16), temp2 (r17), looplo (r24),

; loophi (r25), spmcrval (r20)

; storing and restoring of registers is not included in the routine

; register usage can be optimized at the expense of code size

;-It is assumed that either the interrupt table is moved to the Boot

; loader section or that the interrupts are disabled.

.equ PAGESIZEB = PAGESIZE*2 ; PAGESIZEB is page size in BYTES, not words

.org SMALLBOOTSTART

Write page:

; Page Erase

ldi spmcrval, (1<<PGERS) | (1<<SPMEN)</pre>

rcall Do spm

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre>

rcall Do spm

; transfer data from RAM to Flash page buffer

ldi looplo, low(PAGESIZEB) ;init loop variable

ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256</pre>

Wrloop:

ld r0, Y+

ld r1, Y+

ldi spmcrval, (1<<SPMEN)</pre>

rcall Do spm

adiw ZH:ZL, 2

sbiw loophi:looplo, 2 ;use subi for PAGESIZEB<=256</pre>

brne Wrloop

; execute Page Write

subi ZL, low(PAGESIZEB) ;restore pointer

sbci ZH, high(PAGESIZEB) ;not required for PAGESIZEB<=256</pre>

ldi spmcrval, (1<<PGWRT) | (1<<SPMEN)</pre>

rcall Do spm

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre>

```

```

sbic EECR, EEWE

rjmp Wait_ee

; SPM timed sequence

out SPMCR, spmcrval

spm

; restore SREG (to enable interrupts if originally enabled)

out SREG, temp2

ret

```

# 28.8.13. ATmega32A Boot Loader Parameters

In the following tables, the parameters used in the description of the self programming are given.

| BOOTSZ1 | BOOTSZ0 | Boot<br>Size  | Pages | Application<br>Flash Section | Boot<br>Loader<br>Flash<br>Section | End<br>Application<br>Section | Boot Reset<br>Address<br>(Start Boot<br>Loader<br>Section) |

|---------|---------|---------------|-------|------------------------------|------------------------------------|-------------------------------|------------------------------------------------------------|

| 1       | 1       | 256<br>words  | 4     | 0x0000 -<br>0x3EFF           | 0x3F00 -<br>0x3FFF                 | 0xEFF                         | 0x3F00                                                     |

| 1       | 0       | 512<br>words  | 8     | 0x0000 -<br>0x3DFF           | 0x3E00 -<br>0x3FFF                 | 0x3DFF                        | 0x3E00                                                     |

| 0       | 1       | 1024<br>words | 16    | 0x0000 -<br>0x3BFF           | 0x3C00 -<br>0x3FFF                 | 0x3BFF                        | 0x3C00                                                     |

| 0       | 0       | 2048<br>words | 32    | 0x0000 -<br>0x37FF           | 0x3800 -<br>0x3FFF                 | 0x37FF                        | 0x3800                                                     |

Table 28-6. Boot Size Configuration, ATmega32A

Note: The different BOOTSZ Fuse configurations are shown in Figure 28-2.

#### Table 28-7. Read-While-Write Limit, ATmega32A

| Section                            | Pages | Address         |

|------------------------------------|-------|-----------------|

| Read-While-Write section (RWW)     | 224   | 0x0000 - 0x37FF |

| No Read-While-Write section (NRWW) | 32    | 0x3800 - 0x3FFF |

**Note:** For details about these two section, see NRWW – No Read-While-Write Section and RWW – Read-While-Write Section.

Register is selected as Data Register. Note that the reset will be active as long as there is a logic 'one' in the Reset Chain. The output from this chain is not latched.

The active states are:

• Shift-DR: The Reset Register is shifted by the TCK input.

# 29.10.3. PROG\_ENABLE (0x4)

The AVR specific public JTAG instruction for enabling programming via the JTAG port. The 16-bit Programming Enable Register is selected as data register. The active states are the following:

- Shift-DR: the programming enable signature is shifted into the data register.

- Update-DR: the programming enable signature is compared to the correct value, and Programming mode is entered if the signature is valid.

# 29.10.4. PROG\_COMMANDS (0x5)

The AVR specific public JTAG instruction for entering programming commands via the JTAG port. The 15bit Programming Command Register is selected as data register. The active states are the following:

- Capture-DR: the result of the previous command is loaded into the data register.

- Shift-DR: the data register is shifted by the TCK input, shifting out the result of the previous command and shifting in the new command.

- Update-DR: the programming command is applied to the Flash inputs.

- Run-Test/Idle: one clock cycle is generated, executing the applied command.

# 29.10.5. PROG\_PAGELOAD (0x6)

The AVR specific public JTAG instruction to directly load the Flash data page via the JTAG port. The 1024-bit Virtual Flash Page Load Register is selected as data register. This is a virtual scan chain with length equal to the number of bits in one Flash page. Internally the Shift Register is 8-bit. Unlike most JTAG instructions, the Update-DR state is not used to transfer data from the Shift Register. The data are automatically transferred to the Flash page buffer byte by byte in the Shift-DR state by an internal state machine. This is the only active state:

• Shift-DR: Flash page data are shifted in from TDI by the TCK input, and automatically loaded into the Flash page one byte at a time.

**Note:** 1. The JTAG instruction PROG\_PAGELOAD can only be used if the AVR device is the first device in JTAG scan chain. If the AVR cannot be the first device in the scan chain, the byte-wise programming algorithm must be used.

## 29.10.6. PROG\_PAGEREAD (0x7)

The AVR specific public JTAG instruction to read one full Flash data page via the JTAG port. The 1032-bit Virtual Flash Page Read Register is selected as data register. This is a virtual scan chain with length equal to the number of bits in one Flash page plus 8. Internally the Shift Register is 8-bit. Unlike most JTAG instructions, the Capture-DR state is not used to transfer data to the Shift Register. The data are automatically transferred from the Flash page buffer byte by byte in the Shift-DR state by an internal state machine. This is the only active state:

• Shift-DR: Flash data are automatically read one byte at a time and shifted out on TDO by the TCK input. The TDI input is ignored.

**Note:** 1. The JTAG instruction PROG\_PAGEREAD can only be used if the AVR device is the first device in JTAG scan chain. If the AVR cannot be the first device in the scan chain, the byte-wise programming algorithm must be used.

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash write using programming instruction 2a.

- 3. Load address high byte using programming instruction 2b.

- 4. Load address low byte using programming instruction 2c.

- 5. Load data using programming instructions 2d, 2e and 2f.

- 6. Repeat steps 4 and 5 for all instruction words in the page.

- 7. Write the page using programming instruction 2g.

- Poll for Flash write complete using programming instruction 2h, or wait for t<sub>WLRH</sub> (refer to table Parallel Programming Characteristics, VCC = 5V ±10% in chapter Parallel Programming Characteristics).

- 9. Repeat steps 3 to 7 until all data have been programmed.

A more efficient data transfer can be achieved using the PROG\_PAGELOAD instruction:

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash write using programming instruction 2a.

- 3. Load the page address using programming instructions 2b and 2c. PCWORD (refer to Table 29-10) is used to address within one page and must be written as 0.

- 4. Enter JTAG instruction PROG\_PAGELOAD.

- 5. Load the entire page by shifting in all instruction words in the page, starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page.

- 6. Enter JTAG instruction PROG\_COMMANDS.

- 7. Write the page using programming instruction 2g.

- Poll for Flash write complete using programming instruction 2h, or wait for t<sub>WLRH</sub> (refer to table Parallel Programming Characteristics, VCC = 5V ±10% in chapter Parallel Programming Characteristics).

- 9. Repeat steps 3 to 8 until all data have been programmed.

## Related Links

Parallel Programming Characteristics on page 339

## 29.10.18. Reading the Flash

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash read using programming instruction 3a.

- 3. Load address using programming instructions 3b and 3c.

- 4. Read data using programming instruction 3d.

- 5. Repeat steps 3 and 4 until all data have been read.

A more efficient data transfer can be achieved using the PROG\_PAGEREAD instruction:

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash read using programming instruction 3a.

- 3. Load the page address using programming instructions 3b and 3c. PCWORD (refer to table *Command Byte Bit Coding* in section *Parallel Programming Parameters, Pin Mapping, and Commands*) is used to address within one page and must be written as 0.

- 4. Enter JTAG instruction PROG\_PAGEREAD.

- 5. Read the entire page by shifting out all instruction words in the page, starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page. Remember that the first 8 bits shifted out should be ignored.