Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

## Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

## Details

| Product Status          | Obsolete                                                               |

|-------------------------|------------------------------------------------------------------------|

| Туре                    | Fixed/Floating Point                                                   |

| Interface               | Host Interface, Link Port, Multi-Processor                             |

| Clock Rate              | 250MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 768kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | -40°C ~ 85°C (TC)                                                      |

| Mounting Type           | Surface Mount                                                          |

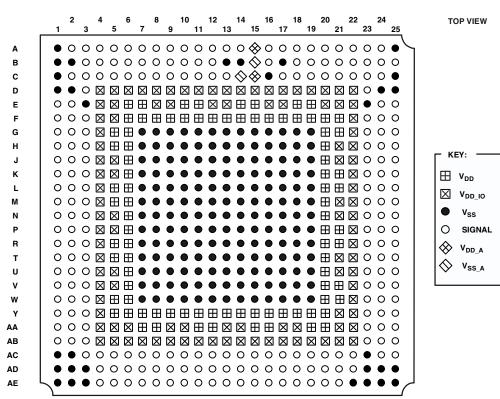

| Package / Case          | 484-BFBGA                                                              |

| Supplier Device Package | 484-PBGA (19x19)                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-ts101sab2-000 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Debugging both C/C++ and assembly programs with the VisualDSP++ debugger, programmers can:

- View mixed C/C++ and assembly code (interleaved source and object information)

- Insert breakpoints

- Set conditional breakpoints on registers, memory, and stacks

- Trace instruction execution

- Perform linear or statistical profiling of program execution

- Fill, dump, and graphically plot the contents of memory

- Perform source level debugging

- · Create custom debugger windows

The VisualDSP++ integrated development and debugging environment (IDDE) lets programmers define and manage DSP software development. Its dialog boxes and property pages let programmers configure and manage all of the TigerSHARC development tools, including the color syntax highlighting in the VisualDSP++ editor. This capability permits programmers to:

- Control how the development tools process inputs and generate outputs

- Maintain a one-to-one correspondence with the tool's command-line switches

The VisualDSP++ Kernel (VDK) incorporates scheduling and resource management tailored specifically to address the memory and timing constraints of DSP programming. These capabilities enable engineers to develop code more effectively, eliminating the need to start from the very beginning, when developing new application code. The VDK features include threads, critical and unscheduled regions, semaphores, events, and device flags. The VDK also supports priority-based, preemptive, cooperative, and time-sliced scheduling approaches. In addition, the VDK was designed to be scalable. If the application does not use a specific feature, the support code for that feature is excluded from the target system.

Because the VDK is a library, a developer can decide whether to use it or not. The VDK is integrated into the VisualDSP++ development environment, but can also be used via standard command-line tools. When the VDK is used, the development environment assists the developer with many error-prone tasks and assists in managing system resources, automating the generation of various VDK-based objects, and visualizing the system state, when debugging an application that uses the VDK.

Use the Expert Linker to visually manipulate the placement of code and data on the embedded system. View memory utilization in a color-coded graphical form, easily move code and data to different areas of the DSP or external memory with a drag of the mouse, examine run-time stack and heap usage. The Expert Linker is fully compatible with existing linker definition file (LDF), allowing the developer to move between the graphical and textual environments.

Analog Devices DSP emulators use the IEEE 1149.1 JTAG Test Access Port of the ADSP-TS101S processor to monitor and control the target board processor during emulation. The emulator provides full speed emulation, allowing inspection and modification of memory, registers, and processor stacks. Nonintrusive in-circuit emulation is assured by the use of the processor's JTAG interface—the emulator does not affect target system loading or timing.

In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the TigerSHARC processor family. Hardware tools include TigerSHARC processor PC plug-in cards. Third-party software tools include DSP libraries, realtime operating systems, and block diagram design tools.

## DESIGNING AN EMULATOR-COMPATIBLE DSP BOARD (TARGET)

The Analog Devices family of emulators are tools that every DSP developer needs to test and debug hardware and software systems. Analog Devices has supplied an IEEE 1149.1 JTAG test access port (TAP) on each JTAG DSP. The emulator uses the TAP to access the internal features of the DSP, allowing the developer to load code, set breakpoints, observe variables, observe memory, and examine registers. The DSP must be halted to send data and commands, but once an operation has been completed by the emulator, the DSP system is set running at full speed with no impact on system timing.

To use these emulators, the target board must include a header that connects the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, multiprocessor scan chains, signal buffering, signal termination, and emulator pod logic, see *EE-68: Analog Devices JTAG Emulation Technical Reference* on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

## **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-TS101S processor's architecture and functionality. For detailed information on the ADSP-TS101S processor's core architecture and instruction set, see the ADSP-TS101 TigerSHARC Processor Programming Reference and the ADSP-TS101 TigerSHARC Processor Hardware Reference. For detailed information on the development tools for this processor, see the VisualDSP++ User's Guide.

## **PIN FUNCTION DESCRIPTIONS**

While most of the ADSP-TS101S processor's input pins are normally synchronous—tied to a specific clock—a few are asynchronous. For these asynchronous signals, an on-chip synchronization circuit prevents metastability problems. The synchronous ac specification for asynchronous signals is used only when predictable cycle-by-cycle behavior is required.

All inputs are sampled by a clock reference, therefore input specifications (asynchronous minimum pulse widths or synchronous input setup and hold) must be met to guarantee recognition.

## **PIN STATES AT RESET**

The output pins can be three-stated during normal operation. The DSP three-states all outputs during reset, allowing these pins to get to their internal pull-up or pull-down state. Some output pins (control signals) have a pull-up or pull-down that maintains a known value during transitions between different drivers.

## **PIN DEFINITIONS**

The Type column in the following pin definitions tables describes the pin type, when the pin is used in the system. The Term (for termination) column describes the pin termination type if the pin is not used by the system. Note that some pins are always used (indicated with au symbol).

| Signal                  | Туре    | Term | Description                                                                                                                                                                                                                   |

|-------------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCLK_N                  | 1       | au   | Local Clock Reference. Connect this pin to $V_{REF}$ as shown in Figure 6.                                                                                                                                                    |

| LCLK_P                  | I       | au   | Local Clock Input. DSP clock input. The instruction cycle rate = n × LCLK, where n is user-<br>programmable to 2, 2.5, 3, 3.5, 4, 5, or 6. For more information, see Clock Domains on Page 9.                                 |

| LCLKRAT2-0 <sup>1</sup> | l (pd²) | au   | LCLK Ratio. The DSP's core clock (instruction cycle rate) = $n \times LCLK$ , where n is user-programmable to 2, 2.5, 3, 3.5, 4, 5, or 6 as shown in Table 4. These pins must have a constant value while the DSP is powered. |

| SCLK_N                  | 1       | au   | System Clock Reference. Connect this pin to V <sub>REF</sub> as shown in Figure 6.                                                                                                                                            |

| SCLK_P                  | I       | au   | System Clock Input. The DSP's system input clock for cluster bus. This pin must be connected to the same clock source as LCLK_P. For more information, see Clock Domains on Page 9.                                           |

| SCLKFREQ <sup>3</sup>   | l (pu²) | au   | SCLK Frequency. SCLKFREQ = 1 is required. The SCLKFREQ pin must have a constant value while the DSP is powered.                                                                                                               |

| RESET                   | I/A     | au   | Reset. Sets the DSP to a known state and causes program to be in idle state. RESET must be asserted at specified time according to the type of reset operation. For details, see Reset and Booting on Page 9.                 |

## Table 3. Pin Definitions—Clocks and Reset

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup> The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

<sup>2</sup>See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

<sup>3</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

### Table 4. LCLK Ratio

| LCLK | (RAT2-0   | Ratio    |

|------|-----------|----------|

| 000  | (default) | 2        |

| 001  |           | 2.5      |

| 010  |           | 3        |

| 011  |           | 3.5      |

| 100  |           | 4        |

| 101  |           | 5        |

| 110  |           | 6        |

| 111  |           | Reserved |

| Signal            | Туре        | Term | Description                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSH <sup>2</sup>  | O/T (pu³)   | nc   | Memory Select Host. $\overline{\text{MSH}}$ is asserted whenever the DSP accesses the host address space (ADDR31:28 $\neq$ 0b0000). $\overline{\text{MSH}}$ is a decoded memory address pin that changes concurrently with ADDR pins. In a multiprocessor system, the bus master DSP drives $\overline{\text{MSH}}$ .                                                          |

| BRST <sup>2</sup> | l/O/T (pu³) | nc   | Burst. The current bus master (DSP or host) asserts this pin to indicate that it is reading or writing data associated with consecutive addresses. A slave device can ignore addresses after the first one and increment an internal address counter after each transfer. For host-to-DSP burst accesses, the DSP increments the address automatically while BRST is asserted. |

Table 5. Pin Definitions—External Port Bus Controls (Continued)

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup> The address and data buses may float for several cycles during bus mastership transitions between a TigerSHARC processor and a host. Floating in this case means that these inputs are not driven by any source and that dc-biased terminations are not present. It is not necessary to add pull-ups as there are no reliability issues and the worst-case power consumption for these floating inputs is negligible. Unconnected address pins may require pull-ups or pull-downs to avoid erroneous slave accesses, depending on the system. Unconnected data pins may be left floating.

<sup>2</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

<sup>3</sup>See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

<sup>4</sup> The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

| Signal                      | Туре                   | Term | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR7-0                       | I/O                    | epu  | Multiprocessing Bus Request Pins. Used by the DSPs in a multiprocessor system to arbitrate for bus mastership. Each DSP drives its own BRx line (corresponding to the value of its ID2–0 inputs) and monitors all others. In systems with fewer than eight DSPs, set the unused BRx pins high.                                                                                                                                                                                                                                                      |

| ID2-0 <sup>1</sup>          | l (pd²)                | au   | Multiprocessor ID. Indicates the DSP's ID. From the ID, the DSP determines its order in a multiprocessor system. These pins also indicate to the DSP which bus request ( $\overline{BR0}-\overline{BR7}$ ) to assert when requesting the bus: $000 = \overline{BR0}$ , $001 = \overline{BR1}$ , $010 = \overline{BR2}$ , $011 = \overline{BR3}$ , $100 = \overline{BR4}$ , $101 = \overline{BR5}$ , $110 = \overline{BR6}$ , or $111 = \overline{BR7}$ . ID2–0 must have a constant value during system operation and can change during reset only. |

| <b>B</b> M <sup>1</sup>     | O (pd <sup>2</sup> )   | au   | Bus Master. The current bus master DSP asserts BM. For debugging only. At reset this is a strap pin. For more information, see Table 16 on Page 19.                                                                                                                                                                                                                                                                                                                                                                                                 |

| BOFF                        | I                      | epu  | Back Off. A deadlock situation can occur when the host and a DSP try to read from each other's bus at the same time. When deadlock occurs, the host can assert BOFF to force the DSP to relinquish the bus before completing its outstanding transaction, but only if the outstanding transaction is to host memory space (MSH).                                                                                                                                                                                                                    |

| <b>BUSLOCK</b> <sup>3</sup> | O/T (pu <sup>2</sup> ) | nc   | Bus Lock Indication. Provides an indication that the current bus master has locked the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HBR                         | I                      | epu  | Host Bus Request. A host must assert HBR to request control of the DSP's external bus. When HBR is asserted in a multiprocessing system, the bus master relinquishes the bus and asserts HBG once the outstanding transaction is finished.                                                                                                                                                                                                                                                                                                          |

#### Table 6. Pin Definitions-External Port Arbitration

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

| Table 6. | Pin Definitions- | -External Port | Arbitration | (Continued) |

|----------|------------------|----------------|-------------|-------------|

|----------|------------------|----------------|-------------|-------------|

| Signal           | Туре        | Term                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HBG <sup>3</sup> | I/O/T (pu²) | nc                    | Host Bus Grant. Acknowledges HBR and indicates that the host can take control of the external<br>bus. When relinquishing the bus, the master DSP three-states the ADDR31–0, DATA63–0, MSH,<br>MSSD, MS1–0, RD, WRL, WRH, BMS, BRST, FLYBY, IOEN, RAS, CAS, SDWE, SDA10, SDCKE, LDQM<br>and HDQM pins, and the DSP puts the SDRAM in self-refresh mode. The DSP asserts HBG until<br>the host deasserts HBR. In multiprocessor systems, the current bus master DSP drives HBG, and<br>all slave DSPs monitor HBG.                                                                                 |

| CPA              | I/O (o/d)   | See<br>next<br>column | Core Priority Access. Asserted while the DSP's core accesses external memory. This pin enables a slave DSP to interrupt a master DSP's background DMA transfers and gain control of the external bus for core-initiated transactions. CPA is an open drain output, connected to all DSPs in the system. The CPA pin has an internal 500 $\Omega$ pull-up resistor, which is only enabled on the DSP with ID2–0 = 0. If ID0 is not used, terminate this pin as either epu or nc. If ID7–1 is not used, terminate this pin as epu.                                                                 |

| DPA              | I/O (o/d)   | See<br>next<br>column | DMA Priority Access. Asserted while a high-priority DSP DMA channel accesses external memory. This pin enables a high-priority DMA channel on a slave DSP to interrupt transfers of a normal-priority DMA channel on a master DSP and gain control of the external bus for DMA initiated transactions. DPA is an open drain output, connected to all DSPs in the system. The DPA pin has an internal 500 $\Omega$ pull-up resistor, which is only enabled on the DSP with ID2–0 = 0 If ID0 is not used, terminate this pin as either epu or nc. If ID7–1 is not used, terminate this pin as epu. |

pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup>The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

<sup>2</sup>See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

<sup>3</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

| Signal                   | Туре                   | Term | Description                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMAR3-0                  | I/A                    | epu  | DMA Request Pins. Enable external I/O devices to request DMA services from the DSP. In response to DMARx, the DSP performs DMA transfers according to the DMA channel's initialization. The DSP ignores DMA requests from uninitialized channels.                                                                                             |

| FLYBY <sup>1</sup>       | O/T (pu²)              | nc   | Flyby Mode. When a DSP DMA channel is initiated in FLYBY mode, it generates flyby transactions on the external bus. During flyby transactions, the DSP asserts FLYBY, which signals the source or destination I/O device to latch the next data or strobe the current data, respectively, and to prepare for the next data on the next cycle. |

| <b>IOEN</b> <sup>1</sup> | O/T (pu <sup>2</sup> ) | nc   | I/O Device Output Enable. Enables the output buffers of an external I/O device for flyby trans-<br>actions between the device and external memory. Active on flyby transactions.                                                                                                                                                              |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

<sup>2</sup> See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

### Table 9. Pin Definitions—JTAG Port (Continued)

| Signal            | Туре                   | Term            | Description                                                                                 |

|-------------------|------------------------|-----------------|---------------------------------------------------------------------------------------------|

| TDO               | O/T                    | nc <sup>1</sup> | Test Data Output (JTAG). A serial data output of the scan path.                             |

| TMS <sup>2</sup>  | l (pu³)                | nc <sup>1</sup> | Test Mode Select (JTAG). Used to control the test state machine.                            |

| TRST <sup>2</sup> | I/A (pu <sup>3</sup> ) | au              | Test Reset (JTAG). Resets the test state machine. TRST must be asserted or pulsed low after |

|                   |                        |                 | power-up for proper device operation.                                                       |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup>See the reference Page 11 to the JTAG emulation technical reference EE-68.

<sup>2</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

<sup>3</sup>See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

#### Table 10. Pin Definitions-Flags, Interrupts, and Timer

| Signal               | Туре                     | Term | Description                                                                                                                                                                                                                                                         |

|----------------------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLAG3-0 <sup>1</sup> | I/O/A (pd <sup>2</sup> ) | nc   | FLAG pins. Bidirectional input/output pins can be used as program conditions. Each pin can be configured individually for input or for output. FLAG3–0 are inputs after power-up and reset.                                                                         |

| IRQ3-0 <sup>3</sup>  | I/A (pu²)                | nc   | Interrupt Request. When asserted, the DSP generates an interrupt. Each of the IRQ3–0 pins can be independently set for edge triggered or level sensitive operation. After reset, these pins are disabled unless the IRQ3–0 strap option is initialized for booting. |

| TMR0E <sup>1</sup>   | O (pd <sup>2</sup> )     | au   | Timer 0 expires. This output pulses for four SCLK cycles whenever timer 0 expires. At reset this is a strap pin. For additional information, see Table 16 on Page 19.                                                                                               |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup>The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

<sup>2</sup> See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

<sup>3</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

| Signal                                                                                                                        | Туре | Term | Description                              |  |

|-------------------------------------------------------------------------------------------------------------------------------|------|------|------------------------------------------|--|

| L0DAT7-01                                                                                                                     | I/O  | nc   | Link0 Data 7–0                           |  |

| L1DAT7-0 <sup>1</sup>                                                                                                         | I/O  | nc   | Link1 Data 7–0                           |  |

| L2DAT7-0 <sup>1</sup>                                                                                                         | I/O  | nc   | Link2 Data 7–0                           |  |

| L3DAT7-0 <sup>1</sup>                                                                                                         | I/O  | nc   | Link3 Data 7–0                           |  |

| LOCLKOUT                                                                                                                      | 0    | nc   | Link0 Clock/Acknowledge Output           |  |

| L1CLKOUT                                                                                                                      | 0    | nc   | Link1 Clock/Acknowledge Output           |  |

| L2CLKOUT                                                                                                                      | 0    | nc   | Link2 Clock/Acknowledge Output           |  |

| L3CLKOUT                                                                                                                      | 0    | nc   | Link3 Clock/Acknowledge Output           |  |

| LOCLKIN                                                                                                                       | I/A  | epu  | Link0 Clock/Acknowledge Input            |  |

| L1CLKIN                                                                                                                       | I/A  | epu  | Link1 Clock/Acknowledge Input            |  |

| L2CLKIN                                                                                                                       | I/A  | epu  | Link2 Clock/Acknowledge Input            |  |

| L3CLKIN                                                                                                                       | I/A  | epu  | Link3 Clock/Acknowledge Input            |  |

| LODIR                                                                                                                         | 0    | nc   | Link0 Direction. (0 = input, 1 = output) |  |

| <b>Type column symbols:</b> $A = asynchronous: G = around: I = input: Q = output: o/d = open drain output: P = power supply:$ |      |      |                                          |  |

### Table 11. Pin Definitions—Link Ports

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

### Table 11. Pin Definitions—Link Ports (Continued)

| Туре                                                                                                                        | Term                                                                       | Description                                                                  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| 0                                                                                                                           | nc                                                                         | Link1 Direction. (0 = input, 1 = output)                                     |  |  |  |  |

| O (pd <sup>3</sup> )                                                                                                        | au                                                                         | Direction. (0 = input, 1 = output)                                           |  |  |  |  |

|                                                                                                                             |                                                                            | At reset this is a strap pin. For more information, see Table 16 on Page 19. |  |  |  |  |

| O (pd <sup>3</sup> )                                                                                                        | nc                                                                         | Link3 Direction. (0 = input, 1 = output)                                     |  |  |  |  |

| <b>Type column symbols:</b> A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; |                                                                            |                                                                              |  |  |  |  |

|                                                                                                                             | O<br>O (pd <sup>3</sup> )<br>O (pd <sup>3</sup> )<br><b>bols:</b> A = asyn | O (pd <sup>3</sup> ) au<br>O (pd <sup>3</sup> ) nc                           |  |  |  |  |

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup> The link port data pins, if connected or floated for extended periods (for example, token slave with no token master), do not require pull-ups or pull-downs as there are no reliability issues and the worst-case power consumption for these floating inputs is negligible. Floating in this case means that these inputs are not driven by any source and that dc-biased terminations are not present.

<sup>2</sup> The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

<sup>3</sup>See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

#### Table 12. Pin Definitions—Impedance and Drive Strength Control

| Signal                                                 | Туре                                         | Term     | Description                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------|----------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROLIMP2–1 <sup>1</sup><br>CONTROLIMP0 <sup>2</sup> | l (pu <sup>3</sup> )<br>l (pd <sup>3</sup> ) | au<br>au | Impedance Control. For ADC (Address/Data/Controls) and LINK (all link port outputs) signals, the CONTROLIMP2–0 pins control impedance as shown in Table 13. These pins enable or disable                                                                                                         |

|                                                        | r (pu )                                      | uu       | dig_ctrl mode. When dig_ctrl:<br>0 = Disabled (maximum drive strength)<br>1 = Enabled (use DS2–0 drive strength selection)                                                                                                                                                                       |

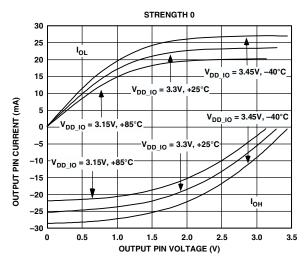

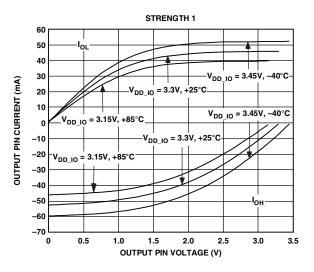

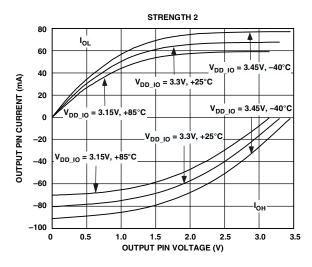

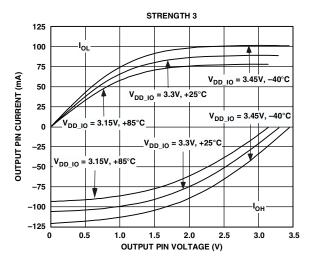

| DS2-0 <sup>1</sup>                                     | l (pu³)                                      | au       | Digital Drive Strength Selection. Selected as shown in Table 14. For drive strength calculation, see Output Drive Currents on Page 32. The drive strength for some pins is preset, not controlled by the DS2–0 pins. The pins that are always at drive strength 7 (100%) are: CPA, DPA, and EMU. |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

<sup>1</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

<sup>2</sup> The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

<sup>3</sup> See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

#### Table 13. Control Impedance Selection

| CONTROLIMP2-0 | ADC dig_ctrl | LINK dig_ctrl |

|---------------|--------------|---------------|

| 000           | 0            | 0             |

| 001           | 0            | 0             |

| 010           | 0            | 1             |

| 011           | reserved     | reserved      |

| 100           | 1            | 0             |

| 101           | reserved     | reserved      |

| 110 (default) | 1            | 1             |

| 111           | reserved     | reserved      |

#### Table 14. Drive Strength Selection

| DS2-0         | Drive Strength |  |

|---------------|----------------|--|

| 000           | Strength 0     |  |

| 001           | Strength 1     |  |

| 010           | Strength 2     |  |

| 011           | Strength 3     |  |

| 100           | Strength 4     |  |

| 101           | Strength 5     |  |

| 110           | Strength 6     |  |

| 111 (default) | Strength 7     |  |

## **SPECIFICATIONS**

Note that component specifications are subject to change without notice.

## **OPERATING CONDITIONS**

| Paramet                    | er                                                                  | Test Conditions                                                         | Min  | Тур | Max                 | Unit |

|----------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|------|-----|---------------------|------|

| V <sub>DD</sub>            | Internal Supply Voltage                                             |                                                                         | 1.14 |     | 1.26                | V    |

| $V_{DD_A}$                 | Analog Supply Voltage                                               |                                                                         | 1.14 |     | 1.26                | V    |

| $V_{\text{DD}\_\text{IO}}$ | I/O Supply Voltage                                                  |                                                                         | 3.15 |     | 3.45                | V    |

| T <sub>CASE</sub>          | Case Operating Temperature                                          |                                                                         | -40  |     | +85                 | °C   |

| V <sub>IH</sub>            | High Level Input Voltage <sup>1</sup>                               | $@V_{DD}, V_{DD_{IO}} = max$                                            | 2    |     | $V_{DD_{IO}} + 0.5$ | V    |

| V <sub>IL</sub>            | Low Level Input Voltage <sup>1</sup>                                | $@V_{DD}, V_{DD_{IO}} = min$                                            | -0.5 |     | +0.8                | v    |

| I <sub>DD</sub>            | V <sub>DD</sub> Supply Current for Typical Activity <sup>2</sup>    | @ CCLK = 250 MHz, V <sub>DD</sub> = 1.25 V,<br>T <sub>CASE</sub> = 25°C |      | 1.2 |                     | A    |

| I <sub>DD</sub>            | V <sub>DD</sub> Supply Current for Typical Activity <sup>2</sup>    | @ CCLK = 300 MHz, V <sub>DD</sub> = 1.25 V,<br>T <sub>CASE</sub> = 25°C |      | 1.5 |                     | A    |

| IDDIDLELP                  | V <sub>DD</sub> Supply Current for IDLELP<br>Instruction Execution  | @ CCLK = 300 MHz, V <sub>DD</sub> = 1.20 V,<br>T <sub>CASE</sub> = 25°C |      | 173 |                     | mA   |

| $I_{DD_{10}}$              | V <sub>DD_IO</sub> Supply Current for Typical Activity <sup>2</sup> | @ SCLK = 100 MHz, $V_{DD_{-10}}$ = 3.3 V,<br>T <sub>CASE</sub> = 25°C   |      | 137 |                     | mA   |

| I <sub>DD_A</sub>          | V <sub>DD_A</sub> Supply Current                                    | @ V <sub>DD</sub> = 1.25 V, T <sub>CASE</sub> = 25°C                    |      | 25  | 31.25               | mA   |

| $V_{\text{REF}}$           | Voltage Reference                                                   |                                                                         | 1.4  |     | 1.6                 | V    |

<sup>1</sup> Applies to input and bidirectional pins.

<sup>2</sup> For details on internal and external power estimation, including: power vector definitions, current usage descriptions, and formulas, see *EE-169, Estimating Power for the ADSP-TS101S* on the Analog Devices website—use site search on "EE-169" (www.analog.com). This document is updated regularly to keep pace with silicon revisions.

## **ELECTRICAL CHARACTERISTICS**

| Param             | eter                                               | Test Conditions                                                                  | Min  | Max  | Unit |

|-------------------|----------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|

| V <sub>OH</sub>   | High Level Output Voltage <sup>1</sup>             | $@V_{DD_{IO}} = min, I_{OH} = -2 mA$                                             | 2.4  |      | V    |

| $V_{OL}$          | Low Level Output Voltage <sup>1</sup>              | $@V_{DD_{LO}} = min, I_{OL} = 4 mA$                                              |      | 0.4  | V    |

| I <sub>IH</sub>   | High Level Input Current <sup>2</sup>              | $@V_{DD_{IO}} = max, V_{IN} = V_{DD_{IO}} max$                                   |      | 10   | μA   |

| I <sub>IHP</sub>  | High Level Input Current (pd) <sup>2</sup>         | $@V_{DD_{IO}} = max, V_{IN} = V_{DD_{IO}} max$                                   | 17.2 | 44.5 | μA   |

| I <sub>IL</sub>   | Low Level Input Current <sup>3</sup>               | $@V_{DD_{IO}} = max, V_{IN} = 0 V$                                               |      | 10   | μA   |

| I <sub>ILP</sub>  | Low Level Input Current (pu) <sup>4</sup>          | $@V_{DD_{IO}} = max, V_{IN} = 0 V$                                               | -69  | -23  | μA   |

| I <sub>OZH</sub>  | Three-State Leakage Current High <sup>5, 6</sup>   | $@V_{DD_{IO}} = max, V_{IN} = V_{DD_{IO}} max$                                   |      | 10   | μA   |

| <b>I</b> OZHP     | Three-State Leakage Current High (pd) <sup>7</sup> | $@V_{DD_{IO}} = max, V_{IN} = V_{DD_{IO}} max$                                   | 17.2 | 44.5 | μA   |

| I <sub>OZL</sub>  | Three-State Leakage Current Low <sup>8</sup>       | $@V_{DD_{IO}} = max, V_{IN} = 0 V$                                               |      | 10   | μA   |

| I <sub>OZLP</sub> | Three-State Leakage Current Low (pu)9              | $@V_{DD_{IO}} = max, V_{IN} = 0 V$                                               | -69  | -23  | μA   |

| I <sub>OZLO</sub> | Three-State Leakage Current Low (od) <sup>7</sup>  | $@V_{DD_{IO}} = max, V_{IN} = 0 V$                                               | -9.8 | -4.6 | mA   |

| C <sub>IN</sub>   | Input Capacitance <sup>10, 11</sup>                | $@f_{IN} = 1 \text{ MHz}, T_{CASE} = 25^{\circ}\text{C}, V_{IN} = 2.5 \text{ V}$ |      | 5    | pF   |

<sup>1</sup> Applies to output and bidirectional pins.

<sup>2</sup> Applies to input pins with internal pull-downs (pd).

<sup>3</sup> Applies to input pins without internal pull-ups (pu).

<sup>4</sup> Applies to input pins with internal pull-ups (pu).

<sup>5</sup> Applies to three-stateable pins without internal pull-downs (pd).

<sup>6</sup> Applies to open drain (od) pins with 500  $\Omega$  pull-ups (pu).

<sup>7</sup> Applies to three-stateable pins with internal pull-downs (pd).

<sup>8</sup> Applies to three-stateable pins without internal pull-ups (pu).

<sup>9</sup> Applies to three-stateable pins with internal pull-ups (pu).

<sup>10</sup>Applies to all signals.

<sup>11</sup>Guaranteed but not tested.

## **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed in Table 19 may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 17. Absolute Maximum Ratings

| Parameter                                            | Rating                                                                         |

|------------------------------------------------------|--------------------------------------------------------------------------------|

| Internal (Core) Supply Voltage (V <sub>DDINT</sub> ) | –0.3 V to +1.40 V                                                              |

| Analog (PLL) Supply Voltage ( $V_{DD_A}$ )           | –0.3 V to +1.40 V                                                              |

| External (I/O) Supply Voltage (V <sub>DDEXT</sub> )  | –0.3 V to +4.6 V                                                               |

| Input Voltage                                        | $-0.5$ V to V <sub>DD_IO</sub> + 0.5 V                                         |

| Output Voltage Swing                                 | $-0.5$ V to V <sub>DD_IO</sub> + 0.5 V<br>-0.5 V to V <sub>DD_IO</sub> + 0.5 V |

| Storage Temperature Range                            | –65°C to +150°C                                                                |

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## **PACKAGE INFORMATION**

The information presented in Figure 7 provide details about the package branding for the ADSP-TS101S processors. For a complete listing of product availability, see Ordering Guide on Page 45.

| ANALOG<br>DEVICES              |

|--------------------------------|

| ADSP-TS101S                    |

| tppZ-ccc                       |

| LLLLLLLL-L 2.0                 |

| yyww country_of_origin         |

| TIGER SHARC <sup>®</sup> VVVVV |

Figure 7. Typical Package Brand

| Table 18. | Package Brand | Information |

|-----------|---------------|-------------|

|-----------|---------------|-------------|

| Brand Key  | Field Description           |

|------------|-----------------------------|

| t          | Temperature Range           |

| рр         | Package Type                |

| Z          | Lead Free Option (optional) |

| ссс        | See Ordering Guide          |

| LLLLLLLL-L | Silicon Lot Number          |

| R.R        | Silicon Revision            |

| yyww       | Date Code                   |

| VVVVV      | Assembly Lot Code           |

## TIMING SPECIFICATIONS

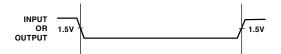

With the exception of link port, IRQ3–0, DMAR3–0, TMR0E, FLAG3–0 (input), and TRST pins, all ac timing for the ADSP-TS101S is relative to a reference clock edge. Because input setup/hold, output valid/hold, and output enable/disable times are relative to a clock edge, the timing data for the ADSP-TS101S has few calculated (formula-based) values. For information on ac timing, see General AC Timing. For information on link port transfer timing, see Link Ports Data Transfer and Token Switch Timing on Page 29.

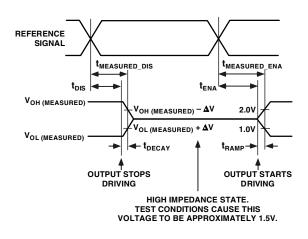

## **General AC Timing**

Timing is measured on signals when they cross the 1.5 V level as described in Figure 16 on Page 28. All delays (in nanoseconds) are measured between the point that the first signal reaches 1.5 V and the point that the second signal reaches 1.5 V.

The ac asynchronous timing data for the  $\overline{IRQ3-0}$ ,  $\overline{DMAR3-0}$ , TMR0E, FLAG3-0 (input), and  $\overline{TRST}$  pins appears in Table 21.

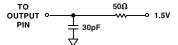

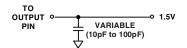

The general ac timing data appears in Table 21, Table 29, and Table 30. All ac specifications are measured with the load specified in Figure 8, and with the output drive strength set to strength 4. Output valid and hold are based on standard capacitive loads: 30 pF on all pins. The delay and hold specifications given should be derated by a drive strength related factor for loads other than the nominal value of 30 pF.

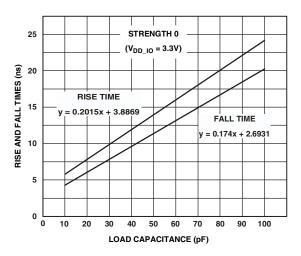

In order to calculate the output valid and hold times for different load conditions and/or output drive strengths, refer to Figure 32 on Page 34 through Figure 39 on Page 36 (Rise and Fall Time vs. Load Capacitance) and Figure 40 on Page 36 (Output Valid vs. Load Capacitance and Drive Strength).

Figure 8. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

For power-up sequencing, power-up reset, and normal reset (hot reset) timing requirements, refer to Table 26 and Figure 13, Table 27 and Figure 14, and Table 28, and Figure 15 respectively.

Table 19. AC Asynchronous Signal Specifications (All values in this table are in nanoseconds)

| Name                    | Description             | Pulse Width Low (min)         | Pulse Width High (min)   |

|-------------------------|-------------------------|-------------------------------|--------------------------|

| IRQ3–0 <sup>1</sup>     | Interrupt request input | t <sub>CCLK</sub> + 3 ns      |                          |

| DMAR3-0 <sup>1</sup>    | DMA request input       | t <sub>CCLK</sub> + 4 ns      | t <sub>CCLK</sub> + 4 ns |

| TMR0E <sup>2</sup>      | Timer 0 expired output  |                               | $4 \times t_{SCLK}  ns$  |

| FLAG3-0 <sup>1, 3</sup> | Flag pins input         | $3 \times t_{\text{CCLK}}$ ns | $3 \times t_{CCLK}  ns$  |

| TRST                    | JTAG test reset input   | 1 ns                          |                          |

<sup>1</sup>These input pins do not need to be synchronized to a clock reference.

<sup>2</sup> This pin is a strap option. During reset, an internal resistor pulls the pin low.

<sup>3</sup> For output specifications, see Table 29 and Table 30.

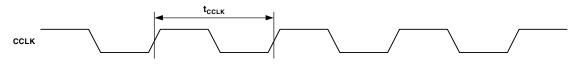

### Table 20. Reference Clocks—Core Clock (CCLK) Cycle Time

|                                |                       | Grade = 100 (300 MHz) |      | Grade = 000 (250 MHz) |      |      |

|--------------------------------|-----------------------|-----------------------|------|-----------------------|------|------|

| Parameter                      | Description           | Min                   | Max  | Min                   | Max  | Unit |

| t <sub>CCLK</sub> <sup>1</sup> | Core Clock Cycle Time | 3.3                   | 12.5 | 4.0                   | 12.5 | ns   |

<sup>1</sup> CCLK is the internal processor clock or instruction cycle time. The period of this clock is equal to the system clock period (t<sub>SCLK</sub>) divided by the system clock ratio (SCLKRAT2–0). For information on available part numbers for different internal processor clock rates, see the Ordering Guide on Page 45.

Figure 9. Reference Clocks—Core Clock (CCLK) Cycle Time

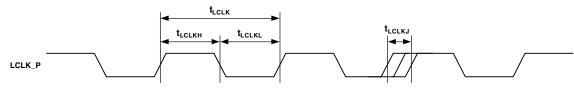

#### Table 21. Reference Clocks—Local Clock (LCLK) Cycle Time

| Parameter                               | Description                  | Min                   | Max                   | Unit |

|-----------------------------------------|------------------------------|-----------------------|-----------------------|------|

| t <sub>LCLK</sub> <sup>1, 2, 3, 4</sup> | Local Clock Cycle Time       | 10                    | 25                    | ns   |

| t <sub>LCLKH</sub>                      | Local Clock Cycle High Time  | $0.4 \times t_{LCLK}$ | $0.6 \times t_{LCLK}$ | ns   |

| t <sub>LCLKL</sub>                      | Local Clock Cycle Low Time   | $0.4 \times t_{LCLK}$ | $0.6 \times t_{LCLK}$ | ns   |

| t <sub>LCLKJ</sub> <sup>5, 6</sup>      | Local Clock Jitter Tolerance |                       | 500                   | ps   |

<sup>1</sup> For more information, see Table 3 on Page 12.

<sup>2</sup> For more information, see Clock Domains on Page 9.

<sup>3</sup>LCLK\_P and SCLK\_P must be connected to the same source.

$^4$  The value of (t\_{\rm LCLK} / LCLKRAT2-0) must not violate the specification for t\_{\rm CCLK}.

<sup>5</sup> Actual input jitter should be combined with ac specifications for accurate timing analysis.

<sup>6</sup> Jitter specification is maximum peak-to-peak time interval error (TIE) jitter.

Figure 10. Reference Clocks—Local Clock (LCLK) Cycle Time

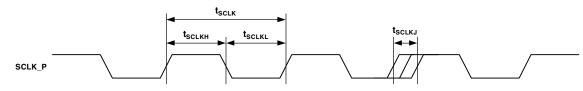

| Table 22. | Reference | Clocks-S | ystem Clock | (SCLK) | Cycle Time |

|-----------|-----------|----------|-------------|--------|------------|

|-----------|-----------|----------|-------------|--------|------------|

| Parameter                               | Description                   | Min                   | Max                   | Unit |

|-----------------------------------------|-------------------------------|-----------------------|-----------------------|------|

| t <sub>SCLK</sub> <sup>1, 2, 3, 4</sup> | System Clock Cycle Time       | 10                    | 25                    | ns   |

| t <sub>sclkh</sub>                      | System Clock Cycle High Time  | $0.4 \times t_{SCLK}$ | $0.6 \times t_{SCLK}$ | ns   |

| t <sub>sclkl</sub>                      | System Clock Cycle Low Time   | $0.4 \times t_{SCLK}$ | $0.6 \times t_{SCLK}$ | ns   |

| t <sub>SCLKJ</sub> <sup>5, 6</sup>      | System Clock Jitter Tolerance |                       | 500                   | ps   |

<sup>1</sup> For more information, see Table 3 on Page 12.

<sup>2</sup> For more information, see Clock Domains on Page 9.

<sup>3</sup> LCLK\_P and SCLK\_P must be connected to the same source.

$^4$  The value of (t<sub>SCLK</sub> / LCLKRAT2-0) must not violate the specification for t<sub>CCLK</sub>.

<sup>5</sup> Actual input jitter should be combined with ac specifications for accurate timing analysis.

<sup>6</sup> Jitter specification is maximum peak-to-peak time interval error (TIE) jitter.

Figure 11. Reference Clocks—System Clock (SCLK) Cycle Time

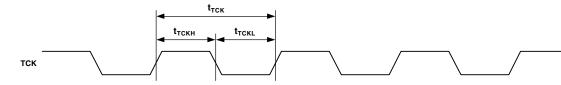

## Table 23. Reference Clocks—Test Clock (TCK) Cycle Time

| Parameter         | Description                       | Min                                  | Max | Unit |

|-------------------|-----------------------------------|--------------------------------------|-----|------|

| t <sub>TCK</sub>  | Test Clock (JTAG) Cycle Time      | Greater of 30 or $t_{CCLK} \times 4$ |     | ns   |

| t <sub>TCKH</sub> | Test Clock (JTAG) Cycle High Time | 12.5                                 |     | ns   |

| t <sub>TCKL</sub> | Test Clock (JTAG) Cycle Low Time  | 12.5                                 |     | ns   |

Figure 12. Reference Clocks—Test Clock (TCK) Cycle Time

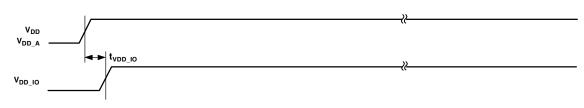

## Table 24. Power-Up Timing<sup>1</sup>

| Parameter           |                                                                                                                                                        | Min | Мах | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Timing Requi        | irement                                                                                                                                                |     |     |      |

| $t_{\text{VDD_IO}}$ | $V_{\text{DD}_{-}\text{IO}}$ Stable and Within Specification After $V_{\text{DD}}$ and $V_{\text{DD}_{-}\text{A}}$ Are Stable and Within Specification | >0  |     | ms   |

<sup>1</sup>For information about power supply sequencing and monitoring solutions, please visit http://www.analog.com/sequencing.

Figure 13. Power-Up Sequencing Timing

<sup>1</sup> The output valid (max) value in this column applies for the standard 30 pF capacitive load used in testing. To see how output valid varies with capacitive loading, see Figure 40 on Page 36.

<sup>2</sup> The external port protocols employ bus IDLE cycles for bus mastership transitions as well as slave address boundary crossings to avoid any potential bus contention. The apparent driver overlap, due to output disables being larger than output enables, is not actual.

${}^{3}\overline{\text{CPA}}$  and  $\overline{\text{DPA}}$  pins are open drains and have 0.5 k $\Omega$  internal pull-ups.

<sup>4</sup> These input pins have Schmitt triggers and therefore do not need to be synchronized to a clock reference. These synchronous specifications only apply for recognition in the current clock reference cycle.

<sup>5</sup> This pin is a strap option. During reset, an internal resistor pulls the pin low.

<sup>6</sup> For input specifications, see Table 21.

<sup>7</sup> For additional requirement details, see Reset and Booting on Page 9.

<sup>8</sup> TCK\_FE indicates TCK falling edge.

$^9$  These pins may change only during reset; recommend connecting it to  $V_{\text{DD}\_\text{IO}}/V_{\text{SS}}$

<sup>10</sup>Reference clock depends on function.

<sup>11</sup>System inputs are: IRQ3-0, BMS, LCLKRAT2-0, SCLKFREQ, BM, TMR0E, FLAG3-0, ID2-0, BRST, WRH, WRL, RD, MSSD, SDCKE, SDWE, CAS, RAS, ADDR31-0, DATA63-0, DPA, CPA, HBG, BOFF, HBR, ACK, BR7-0, L0CLKIN, L0DAT7-0, L1CLKIN, L1DAT7-0, L2CLKIN, L2DAT7-0, L2DIR, L3CLKIN, L3DAT7-0, DS2-0, CONTROLIMP2-0, RESET, DMAR3-0.

<sup>12</sup>System outputs are: BMS, BM, BUSLOCK, TMR0E, FLAG3-0, FLYBY, IOEN, MSH, BRST, WRH, WRL, RD, MS1-0, HDQM, LDQM, MSSD, SDCKE, SDWE, CAS, RAS, ADDR31-0, DATA63-0, DPA, CPA, HBG, ACK, BR7-0, L0CLKOUT, L0DAT7-0, L0DIR, L1CLKOUT, L1DAT7-0, L1DIR, L2CLKOUT, L2DAT7-0, L2DIR, L3CLKOUT, L3DAT7-0, L3DIR, EMU.

### Table 28. AC Signal Specifications (for 16.7 ns <SCLK <25 ns) (All values in this table are in nanoseconds)

| Name                       | Description                     | Input Setup<br>(min) | Input Hold<br>(min) | Output Valid<br>(max) <sup>1</sup> | Output Hold<br>(min) | Output Enable<br>(min) <sup>2</sup> | Output Disable<br>(max) <sup>2</sup> | Reference<br>Clock |

|----------------------------|---------------------------------|----------------------|---------------------|------------------------------------|----------------------|-------------------------------------|--------------------------------------|--------------------|

| ADDR31-0                   | External Address Bus            | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| DATA63-0                   | External Data Bus               | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| MSH                        | Memory Select Host Line         |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| MSSD                       | Memory Select SDRAM Line        | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| MS1-0                      | Memory Select for Static Blocks |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| RD                         | Memory Read                     | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| WRL                        | Write Low Word                  | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| WRH                        | Write High Word                 | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| ACK                        | Acknowledge for Data            | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| SDCKE                      | SDRAM Clock Enable              | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| RAS                        | Row Address Select              | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| CAS                        | Column Address Select           | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| SDWE                       | SDRAM Write Enable              | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| LDQM                       | Low Word SDRAM Data Mask        |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| HDQM                       | High Word SDRAM Data Mask       |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| SDA10                      | SDRAM ADDR10                    |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| HBR                        | Host Bus Request                | 2.8                  | 0.5                 |                                    |                      |                                     |                                      | SCLK               |

| HBG                        | Host Bus Grant                  | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| BOFF                       | Back Off Request                | 2.8                  | 0.5                 |                                    |                      |                                     |                                      | SCLK               |

| BUSLOCK                    | Bus Lock                        |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| BRST                       | Burst Access                    | 2.8                  | 0.5                 | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| BR7-0                      | Multiprocessing Bus Request     | 2.8                  | 0.5                 | 4.2                                | 0.8                  |                                     |                                      | SCLK               |

| FLYBY                      | Flyby Mode Selection            |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| IOEN                       | Flyby Mode I/O Enable           |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| CPA 3, 4                   | Core Priority Access            | 2.8                  | 0.5                 | 5.8                                |                      |                                     | 2.5                                  | SCLK               |

| <b>DPA</b> <sup>3, 4</sup> | DMA Priority Access             | 2.8                  | 0.5                 | 5.8                                |                      |                                     | 2.5                                  | SCLK               |

| BMS <sup>5</sup>           | Boot Memory Select              |                      |                     | 4.2                                | 0.8                  | 0.3                                 | 2.5                                  | SCLK               |

| FLAG3-0 <sup>6</sup>       | FLAG Pins                       |                      |                     | 4.2                                | 1.0                  | 1.0                                 | 4.0                                  | SCLK               |

| Name                       | Description                  | Input Setup<br>(min) | Input Hold<br>(min) | Output Valid<br>(max) <sup>1</sup> | Output Hold<br>(min) | Output Enable<br>(min) <sup>2</sup> | Output Disable<br>(max) <sup>2</sup> | Reference<br>Clock  |

|----------------------------|------------------------------|----------------------|---------------------|------------------------------------|----------------------|-------------------------------------|--------------------------------------|---------------------|

| RESET <sup>4, 7</sup>      | Global Reset                 |                      |                     |                                    |                      |                                     |                                      | SCLK                |

| TMS <sup>4</sup>           | Test Mode Select (JTAG)      | 1.5                  | 1.0                 |                                    |                      |                                     |                                      | ТСК                 |

| TDI <sup>4</sup>           | Test Data Input (JTAG)       | 1.5                  | 1.0                 |                                    |                      |                                     |                                      | ТСК                 |

| TDO                        | Test Data Output (JTAG)      |                      |                     | 6.0                                | 1.0                  | 1.0                                 | 5.0                                  | TCK_FE <sup>8</sup> |

| TRST <sup>4, 7, 9</sup>    | Test Reset (JTAG)            |                      |                     |                                    |                      |                                     |                                      | ТСК                 |

| BM⁵                        | Bus Master Debug Aid Only    |                      |                     | 4.2                                | 0.8                  |                                     |                                      | SCLK                |

| EMU <sup>10</sup>          | Emulation                    |                      |                     | 5.5                                |                      |                                     | 5.0                                  | TCK or LCLK         |

| JTAG_SYS_IN <sup>11</sup>  | System Input                 | 1.5                  | 11.0                |                                    |                      |                                     |                                      | ТСК                 |

| JTAG_SYS_OUT <sup>12</sup> | System Output                |                      |                     | 16.0                               |                      |                                     |                                      | TCK_FE <sup>8</sup> |

| ID2-0 <sup>9</sup>         | Chip ID—Must Be Constant     |                      |                     |                                    |                      |                                     |                                      |                     |

| CONTROLIMP2-09             | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                     |                                      |                     |

| DS2-0 <sup>9</sup>         | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                     |                                      |                     |

| LCLKRAT2-0 <sup>9</sup>    | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                     |                                      |                     |

| SCLKFREQ <sup>9</sup>      | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                     |                                      |                     |

Table 28. AC Signal Specifications (for 16.7 ns <SCLK <25 ns) (All values in this table are in nanoseconds) (Continued)

<sup>1</sup>The output valid (max) value in this column applies for the standard 30 pF capacitive load used in testing. To see how output valid varies with capacitive loading, see Figure 40 on Page 36.

<sup>2</sup> The external port protocols employ bus IDLE cycles for bus mastership transitions as well as slave address boundary crossings to avoid any potential bus contention. The apparent driver overlap, due to output disables being larger than output enables, is not actual.

$^3\overline{\text{CPA}}$  and  $\overline{\text{DPA}}$  pins are open drains and have 0.5 k $\Omega$  internal pull-ups.

<sup>4</sup> These input pins have Schmitt triggers and therefore do not need to be synchronized to a clock reference. These synchronous specifications only apply for recognition in the current clock reference cycle.

<sup>5</sup> This pin is a strap option. During reset, an internal resistor pulls the pin low.

<sup>6</sup> For input specifications, see Table 21.

<sup>7</sup> For additional requirement details, see Reset and Booting on Page 9.

<sup>8</sup> TCK\_FE indicates TCK falling edge.

$^9$  These pins may change only during reset; recommend connecting it to  $V_{\rm DD\_IO}/V_{\rm SS}.$

<sup>10</sup>Reference clock depends on function.

<sup>11</sup>System inputs are: IRQ3-0, BMS, LCLKRAT2-0, SCLKFREQ, BM, TMR0E, FLAG3-0, ID2-0, BRST, WRH, WRL, RD, MSSD, SDCKE, SDWE, CAS, RAS, ADDR31-0, DATA63-0, DPA, CPA, HBG, BOFF, HBR, ACK, BR7-0, L0CLKIN, L0DAT7-0, L1CLKIN, L1DAT7-0, L2CLKIN, L2DAT7-0, L2DIR, L3CLKIN, L3DAT7-0, DS2-0, CONTROLIMP2-0, RESET, DMAR3-0.

<sup>12</sup>System outputs are: BMS, BM, BUSLOCK, TMR0E, FLAG3-0, FLYBY, IOEN, MSH, BRST, WRH, WRL, RD, MS1-0, HDQM, LDQM, MSSD, SDCKE, SDWE, CAS, RAS, ADDR31-0, DATA63-0, DPA, CPA, HBG, ACK, BR7-0, L0CLKOUT, L0DAT7-0, L0DIR, L1CLKOUT, L1DAT7-0, L1DIR, L2CLKOUT, L2DAT7-0, L2DIR, L3CLKOUT, L3DAT7-0, L3DIR, EMU.

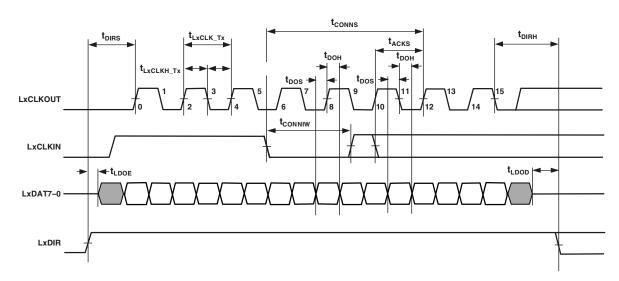

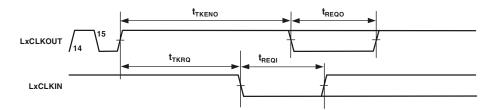

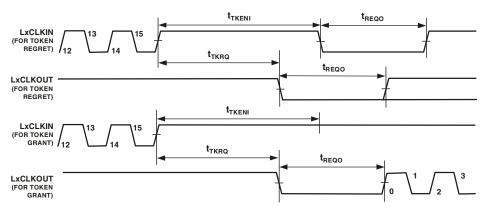

#### Link Ports Data Transfer and Token Switch Timing

Table 31, Table 32, Table 33, and Table 34 with Figure 17, Figure 18, Figure 19, and Figure 20 provide the timing specifications for the link ports data transfer and token switch.