Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Active                                                                 |

| Туре                    | Fixed/Floating Point                                                   |

| Interface               | Host Interface, Link Port, Multi-Processor                             |

| Clock Rate              | 300MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 768kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | -40°C ~ 85°C (TC)                                                      |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 484-BFBGA                                                              |

| Supplier Device Package | 484-PBGA (19x19)                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-ts101sab2z100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Data Sheet**

ADSP-TS101S: TigerSHARC Embedded Processor, 300 MHz, 6 Mbits, Data Sheet

#### **Evaluation Kit Manuals**

ADSP-TS101S EZ-KIT Lite® Manual

### **Integrated Circuit Anomalies**

ADSP-TS101S TigerSHARC Anomaly List for Revision(s) 0.2, 0.4

#### **Processor Manuals**

- ADSP-TS101 TigerSHARC Processor Hardware Reference

- ADSP-TS101 TigerSHARC Processor Programming Reference

- TigerSHARC Processors: Manuals

## **Product Highlight**

• General-Purpose TigerSHARC Processor Product Brief

### **Software Manuals**

- VisualDSP++® 5.0 Assembler and Preprocessor Manual

- VisualDSP++<sup>®</sup> 5.0 C/C++ Compiler and Library Manual for **TigerSHARC Processors**

- VisualDSP++<sup>®</sup> 5.0 Kernel (VDK) Users Guide

- VisualDSP++<sup>®</sup> 5.0 Licensing Guide

- VisualDSP++

<sup>®</sup> 5.0 Linker and Utilities Manual

- VisualDSP++<sup>®</sup> 5.0 Loader and Utilities Manual

- VisualDSP++<sup>®</sup> 5.0 Product Release Bulletin

- VisualDSP++

<sup>®</sup> 5.0 Quick Installation Reference Card

- VisualDSP++<sup>®</sup> 5.0 Users Guide

## SOFTWARE AND SYSTEMS REQUIREMENTS •

TigerSHARC Evaluation Kits

## TOOLS AND SIMULATIONS $\Box$

- ADSP-TS101 TigerSHARC BSDL File 19x19mm PBGA Package for Revision 0.4, (11/2006)

- ADSP-TS101 TigerSHARC BSDL File 27x27mm PBGA Package for Revision 0.4, (11/2006)

- ADSP-TS101: 19x19mm PBGA Silicon Revision 0.0 and 0.1 [BSDL Original File], 02/08/2001

- ADSP-TS101: 19x19mm PBGA Package Silicon Revision 0.2, [BSDL Original File], 09/09/2003

- ADSP-TS101: 27x27 PBGA Package Siicon Revision 0.2, [BSDL Original File], 09/09/2003

- ADSP-TS101: 27x27 PBGA Package Silicon Revision 0.0 and 0.1 [BSDL Original File], 10/12/2001

- · Designing with BGA

- TigerSHARC Processors: Software and Tools

- ADSP-TS101S IBIS Datafile BGA Package

## REFERENCE MATERIALS !-

### **Product Selection Guide**

· ADI Complementary Parts Guide - Supervisory Devices and DSP Processors

#### **Technical Articles**

- A Software Solution for Chip Rate Processing in CDMA Wireless Infrastructure

- ADSP-TS101S MP System Simulation and Analysis

- Continuous Real-Time Signal Processing -- Comparing TigerSHARC and PowerPC Via Continuous cFFTs

- Rethinking Base Station, Baseband Processing for Wireless Communication

- SHARC Bites Back The Memory Inside: TigerSHARC Swallows Its DRAM

#### **White Papers**

ADSP-TS101S MP System Simulation and Analysis

# DESIGN RESOURCES $\Box$

- ADSP-TS101S Material Declaration

- PCN-PDN Information

- Quality And Reliability

- · Symbols and Footprints

## **DISCUSSIONS**

View all ADSP-TS101S EngineerZone Discussions.

# SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

DOCUMENT FEEDBACK 🖳

Submit a technical question or find your regional support number.

Submit feedback for this data sheet.

The ADSP-TS101S, in most cases, has a two-cycle arithmetic execution pipeline that is fully interlocked, so whenever a computation result is unavailable for another operation dependent on it, the DSP automatically inserts one or more stall cycles as needed. Efficient programming with dependency-free instructions can eliminate most computational and memory transfer data dependencies.

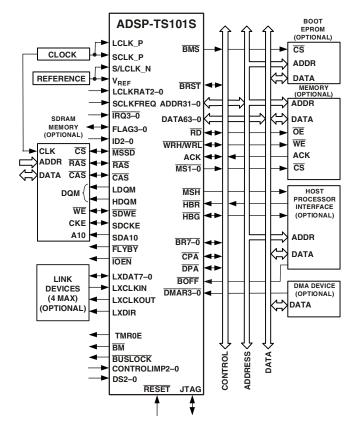

Figure 2. Single-Processor System with External SDRAM

In addition, the ADSP-TS101S supports SIMD operations two ways—SIMD compute blocks and SIMD computations. The programmer can direct both compute blocks to operate on the same data (broadcast distribution) or on different data (merged distribution). In addition, each compute block can execute four 16-bit or eight 8-bit SIMD computations in parallel.

## **DUAL COMPUTE BLOCKS**

The ADSP-TS101S has compute blocks that can execute computations either independently or together as a SIMD engine. The DSP can issue up to two compute instructions per compute block each cycle, instructing the ALU, multiplier, or shifter to perform independent, simultaneous operations.

The compute blocks are referred to as X and Y in assembly syntax, and each block contains three computational units—an ALU, a multiplier, a 64-bit shifter, and a 32-word register file.

- Register file—each compute block has a multiported 32-word, fully orthogonal register file used for transferring data between the computation units and data buses and for storing intermediate results. Instructions can access the registers in the register file individually (word aligned), or in sets of two (dual aligned) or four (quad aligned).

- ALU—the ALU performs a standard set of arithmetic operations in both fixed- and floating-point formats. It also performs logic operations.

- Multiplier—the multiplier performs both fixed- and floating-point multiplication and fixed-point multiply and accumulate.

- Shifter—the 64-bit shifter performs logical and arithmetic shifts, bit and bit stream manipulation, and field deposit and extraction operations.

- Accelerator—128-bit unit for trellis decoding (for example, Viterbi and turbo decoders) and complex correlations for communication applications.

Using these features, the compute blocks can:

- Provide 8 MACs per cycle peak and 7.1 MACs per cycle sustained 16-bit performance and provide 2 MACs per cycle peak and 1.8 MACs per cycle sustained 32-bit performance (based on FIR)

- Execute six single-precision, floating-point or execute 24 fixed-point (16-bit) operations per cycle, providing 1,800 MFLOPS or 7.3 GOPS performance

- Perform two complex 16-bit MACs per cycle

- Execute eight trellis butterflies in one cycle

### **DATA ALIGNMENT BUFFER (DAB)**

The DAB is a quad word FIFO that enables loading of quad word data from nonaligned addresses. Normally, load instructions must be aligned to their data size so that quad words are loaded from a quad-aligned address. Using the DAB significantly improves the efficiency of some applications, such as FIR filters.

#### **DUAL INTEGER ALUS (IALUS)**

The ADSP-TS101S has two IALUs that provide powerful address generation capabilities and perform many general-purpose integer operations. Each of the IALUs:

- Provides memory addresses for data and update pointers

- Supports circular buffering and bit-reverse addressing

- Performs general-purpose integer operations, increasing programming flexibility

- Includes a 31-word register file for each IALU

As address generators, the IALUs perform immediate or indirect (pre- and post-modify) addressing. They perform modulus and bit-reverse operations with no constraints placed on memory addresses for the modulus data buffer placement. Each IALU can specify either a single, dual, or quad word access from memory.

Debugging both C/C++ and assembly programs with the VisualDSP++ debugger, programmers can:

- View mixed C/C++ and assembly code (interleaved source and object information)

- · Insert breakpoints

- Set conditional breakpoints on registers, memory, and stacks

- · Trace instruction execution

- Perform linear or statistical profiling of program execution

- Fill, dump, and graphically plot the contents of memory

- · Perform source level debugging

- · Create custom debugger windows

The VisualDSP++ integrated development and debugging environment (IDDE) lets programmers define and manage DSP software development. Its dialog boxes and property pages let programmers configure and manage all of the TigerSHARC development tools, including the color syntax highlighting in the VisualDSP++ editor. This capability permits programmers to:

- Control how the development tools process inputs and generate outputs

- Maintain a one-to-one correspondence with the tool's command-line switches

The VisualDSP++ Kernel (VDK) incorporates scheduling and resource management tailored specifically to address the memory and timing constraints of DSP programming. These capabilities enable engineers to develop code more effectively, eliminating the need to start from the very beginning, when developing new application code. The VDK features include threads, critical and unscheduled regions, semaphores, events, and device flags. The VDK also supports priority-based, preemptive, cooperative, and time-sliced scheduling approaches. In addition, the VDK was designed to be scalable. If the application does not use a specific feature, the support code for that feature is excluded from the target system.

Because the VDK is a library, a developer can decide whether to use it or not. The VDK is integrated into the VisualDSP++ development environment, but can also be used via standard command-line tools. When the VDK is used, the development environment assists the developer with many error-prone tasks and assists in managing system resources, automating the generation of various VDK-based objects, and visualizing the system state, when debugging an application that uses the VDK.

Use the Expert Linker to visually manipulate the placement of code and data on the embedded system. View memory utilization in a color-coded graphical form, easily move code and data to different areas of the DSP or external memory with a drag of the mouse, examine run-time stack and heap usage. The Expert Linker is fully compatible with existing linker definition file (LDF), allowing the developer to move between the graphical and textual environments.

Analog Devices DSP emulators use the IEEE 1149.1 JTAG Test Access Port of the ADSP-TS101S processor to monitor and control the target board processor during emulation. The emulator provides full speed emulation, allowing inspection and modification of memory, registers, and processor stacks. Nonintrusive in-circuit emulation is assured by the use of the processor's JTAG interface—the emulator does not affect target system loading or timing.

In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the TigerSHARC processor family. Hardware tools include TigerSHARC processor PC plug-in cards. Third-party software tools include DSP libraries, real-time operating systems, and block diagram design tools.

# DESIGNING AN EMULATOR-COMPATIBLE DSP BOARD (TARGET)

The Analog Devices family of emulators are tools that every DSP developer needs to test and debug hardware and software systems. Analog Devices has supplied an IEEE 1149.1 JTAG test access port (TAP) on each JTAG DSP. The emulator uses the TAP to access the internal features of the DSP, allowing the developer to load code, set breakpoints, observe variables, observe memory, and examine registers. The DSP must be halted to send data and commands, but once an operation has been completed by the emulator, the DSP system is set running at full speed with no impact on system timing.

To use these emulators, the target board must include a header that connects the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, multiprocessor scan chains, signal buffering, signal termination, and emulator pod logic, see *EE-68*: *Analog Devices JTAG Emulation Technical Reference* on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

## **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-TS101S processor's architecture and functionality. For detailed information on the ADSP-TS101S processor's core architecture and instruction set, see the ADSP-TS101 TigerSHARC Processor Programming Reference and the ADSP-TS101 TigerSHARC Processor Hardware Reference. For detailed information on the development tools for this processor, see the VisualDSP++ User's Guide.

## PIN FUNCTION DESCRIPTIONS

While most of the ADSP-TS101S processor's input pins are normally synchronous—tied to a specific clock—a few are asynchronous. For these asynchronous signals, an on-chip synchronization circuit prevents metastability problems. The synchronous ac specification for asynchronous signals is used only when predictable cycle-by-cycle behavior is required.

All inputs are sampled by a clock reference, therefore input specifications (asynchronous minimum pulse widths or synchronous input setup and hold) must be met to guarantee recognition.

### **PIN STATES AT RESET**

The output pins can be three-stated during normal operation. The DSP three-states all outputs during reset, allowing these pins to get to their internal pull-up or pull-down state. Some output pins (control signals) have a pull-up or pull-down that maintains a known value during transitions between different drivers.

## **PIN DEFINITIONS**

The Type column in the following pin definitions tables describes the pin type, when the pin is used in the system. The Term (for termination) column describes the pin termination type if the pin is not used by the system. Note that some pins are always used (indicated with au symbol).

Table 3. Pin Definitions—Clocks and Reset

| Signal                  | Туре    | Term | Description                                                                                                                                                                                                                   |  |  |  |  |

|-------------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LCLK_N                  | 1       | au   | Local Clock Reference. Connect this pin to V <sub>REF</sub> as shown in Figure 6.                                                                                                                                             |  |  |  |  |

| LCLK_P                  | I       | au   | Local Clock Input. DSP clock input. The instruction cycle rate = $n \times LCLK$ , where n is user-programmable to 2, 2.5, 3, 3.5, 4, 5, or 6. For more information, see Clock Domains on Page 9.                             |  |  |  |  |

| LCLKRAT2-0 <sup>1</sup> | I (pd²) | au   | LCLK Ratio. The DSP's core clock (instruction cycle rate) = $n \times LCLK$ , where n is user-programmable to 2, 2.5, 3, 3.5, 4, 5, or 6 as shown in Table 4. These pins must have a constant value while the DSP is powered. |  |  |  |  |

| SCLK_N                  | 1       | au   | System Clock Reference. Connect this pin to V <sub>REF</sub> as shown in Figure 6.                                                                                                                                            |  |  |  |  |

| SCLK_P                  | I       | au   | System Clock Input. The DSP's system input clock for cluster bus. This pin must be connected to the same clock source as LCLK_P. For more information, see Clock Domains on Page 9.                                           |  |  |  |  |

| SCLKFREQ <sup>3</sup>   | I (pu²) | au   | SCLK Frequency. SCLKFREQ = 1 is required. The SCLKFREQ pin must have a constant value while the DSP is powered.                                                                                                               |  |  |  |  |

| RESET                   | I/A     | au   | Reset. Sets the DSP to a known state and causes program to be in idle state. RESET must be asserted at specified time according to the type of reset operation. For details, see Reset and Booting on Page 9.                 |  |  |  |  |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

Table 4. LCLK Ratio

| LCLKRAT2-0    | Ratio    |

|---------------|----------|

| 000 (default) | 2        |

| 001           | 2.5      |

| 010           | 3        |

| 011           | 3.5      |

| 100           | 4        |

| 101           | 5        |

| 110           | 6        |

| 111           | Reserved |

<sup>&</sup>lt;sup>1</sup>The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

<sup>&</sup>lt;sup>2</sup> See Electrical Characteristics on Page 20 for maximum and minimum current consumption for pull-up and pull-down resistances.

<sup>&</sup>lt;sup>3</sup> The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

Table 5. Pin Definitions—External Port Bus Controls

| Signal                | Туре            | Term | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR31-0 <sup>1</sup> | I/O/T           | nc   | Address Bus. The DSP issues addresses for accessing memory and peripherals on these pins. In a multiprocessor system, the bus master drives addresses for accessing internal memory or I/O processor registers of other ADSP-TS101S processors. The DSP inputs addresses when a host or another DSP accesses its internal memory or I/O processor registers.                                                                                                                                                                                                                                   |

| DATA63-0 <sup>1</sup> | I/O/T           | nc   | External Data Bus. Data and instructions are received, and driven by the DSP, on these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RD <sup>2</sup>       | I/O/T (pu³)     | nc   | Memory Read. $\overline{RD}$ is asserted whenever the DSP reads from any slave in the system, excluding SDRAM. When the DSP is a slave, $\overline{RD}$ is an input and indicates read transactions that access its internal memory or universal registers. In a multiprocessor system, the bus master drives $\overline{RD}$ . The $\overline{RD}$ pin changes concurrently with ADDR pins.                                                                                                                                                                                                   |

| WRL <sup>2</sup>      | I/O/T (pu³)     | nc   | Write Low. WRL is asserted in two cases: When the ADSP-TS101S writes to an even address word of external memory or to another external bus agent; and when the ADSP-TS101S writes to a 32-bit zone (host, memory, or DSP programmed to 32-bit bus). An external master (host or DSP) asserts WRL for writing to a DSP's low word of internal memory. In a multiprocessor system, the bus master drives WRL. The WRL pin changes concurrently with ADDR pins. When the DSP is a slave, WRL is an input and indicates write transactions that access its internal memory or universal registers. |

| WRH <sup>2</sup>      | I/O/T (pu³)     | nc   | Write High. WRH is asserted when the ADSP-TS101S writes a long word (64 bits) or writes to an odd address word of external memory or to another external bus agent on a 64-bit data bus. An external master (host or another DSP) must assert WRH for writing to a DSP's high word of 64-bit data bus. In a multiprocessing system, the bus master drives WRH. The WRH pin changes concurrently with ADDR pins. When the DSP is a slave, WRH is an input and indicates write transactions that access its internal memory or universal registers.                                              |

| ACK                   | I/O/T           | epu  | Acknowledge. External slave devices can deassert ACK to add wait states to external memory accesses. ACK is used by I/O devices, memory controllers, and other peripherals on the data phase. The DSP can deassert ACK to add wait states to read accesses of its internal memory. The ADSP-TS101S does not drive ACK during slave writes. Therefore, an external (approximately $10~\mathrm{k}\Omega$ ) pull-up is required.                                                                                                                                                                  |

| BMS <sup>2,4</sup>    | O/T<br>(pu/pd³) | au   | Boot Memory Select. BMS is the chip select for boot EPROM or flash memory. During reset, the DSP uses BMS as a strap pin (EBOOT) for EPROM boot mode. When the DSP is configured to boot from EPROM, BMS is active during the boot sequence. Pull-down enabled during RESET (asserted); pull-up enabled after RESET (deasserted). In a multiprocessor system, the DSP bus master drives BMS. For details see Reset and Booting on Page 9 and the EBOOT signal description in Table 16 on Page 19.                                                                                              |

| MS1-0 <sup>2</sup>    | O/T (pu³)       | nc   | Memory Select. $\overline{\text{MS0}}$ or $\overline{\text{MS1}}$ is asserted whenever the DSP accesses memory banks 0 or 1, respectively. $\overline{\text{MS1-0}}$ are decoded memory address pins that change concurrently with ADDR pins. When ADDR31:26 = 0b000011, $\overline{\text{MS0}}$ is asserted. When ADDR31:26 = 0b000011, $\overline{\text{MS1}}$ is asserted. In multiprocessor systems, the master DSP drives $\overline{\text{MS1-0}}$ .                                                                                                                                     |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

Table 15. Pin Definitions—Power, Ground, and Reference

| Signal          | Туре | Term | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | Р    | au   | V <sub>DD</sub> pins for internal logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $V_{DD\_A}$     | P    | au   | V <sub>DD</sub> pins for analog circuits. Pay critical attention to bypassing this supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{DD\_IO}$    | P    | au   | V <sub>DD</sub> pins for I/O buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{REF}$       | 1    | au   | Reference voltage defines the trip point for all input buffers, except $\overline{RESET}$ , $\overline{IRQ3-0}$ , $\overline{DMAR3-0}$ , $ID2-0$ , $CONTROLIMP2-0$ , $TCK$ , $TDI$ , $TMS$ , and $\overline{TRST}$ . The value is 1.5 V $\pm$ 100 mV (which is the $TTL$ trip point). $V_{REF}$ can be connected to a power supply or set by a voltage divider circuit. The voltage divider should have an HF decoupling capacitor (1 nF HF SMD) connected to $V_{SS}$ . Tie the decoupling capacitor between $V_{REF}$ input and $V_{SS}$ , as close to the DSP's pins as possible. For more information, see Filtering Reference Voltage and Clocks on Page 10. |

| $V_{SS}$        | G    | au   | Ground pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $V_{SS\_A}$     | G    | au   | Ground pins for analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NC              |      |      | No connect. Do not connect these pins to anything (not to any supply, signal, or each other), because they are reserved and must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**Type column symbols:** A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply; pd = internal pull-down approximately 100 k $\Omega$ ; pu = internal pull-up approximately 100 k $\Omega$ ; T = three-state

**Term (for termination) column symbols:** epd = external pull-down approximately 10 k $\Omega$  to V<sub>SS</sub>; epu = external pull-up approximately 10 k $\Omega$  to V<sub>DD-IO</sub>, nc = not connected; au = always used.

## STRAP PIN FUNCTION DESCRIPTIONS

Some pins have alternate functions at reset. Strap options set DSP operating modes. During reset, the DSP samples the strap option pins. Strap pins have an approximately  $100~k\Omega$  pulldown for the default value. If a strap pin is not connected to an external pull-up or logic load, the DSP samples the default value during reset. If strap pins are connected to logic inputs, a stronger external pull-down may be required to ensure default value

depending on leakage and/or low level input current of the logic load. To set a mode other than the default mode, connect the strap pin to a sufficiently stronger external pull-up. In a multiprocessor system, up to eight DSPs may be connected on the cluster bus, resulting in parallel combination of strap pin pull-down resistors. Table 16 lists and describes each of the DSP's strap pins.

Table 16. Pin Definitions—I/O Strap Pins

| Signal | On Pin | Description                                                                                                                                                                                                                                                                   |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EBOOT  | BMS    | EPROM boot.  0 = boot from EPROM immediately after reset (default)  1 = idle after reset and wait for an external device to boot DSP through the external port or a link port                                                                                                 |

| IRQEN  | ВМ     | Interrupt Enable. $0 = \text{disable and set } \frac{\overline{IRQ3-0}}{\overline{IRQ3-0}}$ interrupts to level sensitive after reset (default) $1 = \text{enable and set } \frac{\overline{IRQ3-0}}{\overline{IRQ3-0}}$ interrupts to edge sensitive immediately after reset |

| TM1    | L2DIR  | Test Mode 1.  0 = required setting during reset.  1 = reserved.                                                                                                                                                                                                               |

| TM2    | TMR0E  | Test Mode 2.  0 = required setting during reset.  1 = reserved.                                                                                                                                                                                                               |

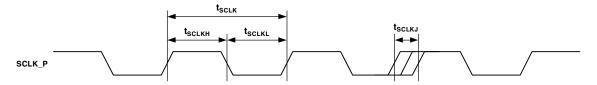

Table 22. Reference Clocks—System Clock (SCLK) Cycle Time

| Parameter                               | Description                   | Min                   | Max                   | Unit |

|-----------------------------------------|-------------------------------|-----------------------|-----------------------|------|

| t <sub>SCLK</sub> <sup>1, 2, 3, 4</sup> | System Clock Cycle Time       | 10                    | 25                    | ns   |

| t <sub>SCLKH</sub>                      | System Clock Cycle High Time  | $0.4 \times t_{SCLK}$ | $0.6 \times t_{SCLK}$ | ns   |

| t <sub>SCLKL</sub>                      | System Clock Cycle Low Time   | $0.4 \times t_{SCLK}$ | $0.6 \times t_{SCLK}$ | ns   |

| t <sub>SCLKJ</sub> 5, 6                 | System Clock Jitter Tolerance |                       | 500                   | ps   |

<sup>&</sup>lt;sup>1</sup> For more information, see Table 3 on Page 12.

<sup>&</sup>lt;sup>6</sup> Jitter specification is maximum peak-to-peak time interval error (TIE) jitter.

Figure 11. Reference Clocks—System Clock (SCLK) Cycle Time

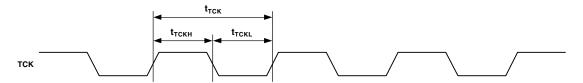

Table 23. Reference Clocks—Test Clock (TCK) Cycle Time

| Parameter         | Description                       | Min                                  | Max | Unit |

|-------------------|-----------------------------------|--------------------------------------|-----|------|

| t <sub>TCK</sub>  | Test Clock (JTAG) Cycle Time      | Greater of 30 or $t_{CCLK} \times 4$ |     | ns   |

| $t_{TCKH}$        | Test Clock (JTAG) Cycle High Time | 12.5                                 |     | ns   |

| t <sub>TCKL</sub> | Test Clock (JTAG) Cycle Low Time  | 12.5                                 |     | ns   |

Figure 12. Reference Clocks—Test Clock (TCK) Cycle Time

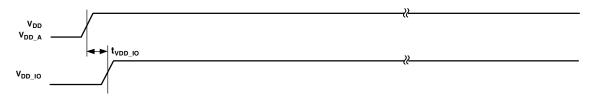

Table 24. Power-Up Timing<sup>1</sup>

| Parameter      |                                                                                                                 | Min | Max | Unit |

|----------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Timing Require | rment                                                                                                           |     |     |      |

| $t_{VDD\_IO}$  | $V_{DD\_IO}$ Stable and Within Specification After $V_{DD}$ and $V_{DD\_A}$ Are Stable and Within Specification | >0  |     | ms   |

<sup>&</sup>lt;sup>1</sup> For information about power supply sequencing and monitoring solutions, please visit http://www.analog.com/sequencing.

Figure 13. Power-Up Sequencing Timing

<sup>&</sup>lt;sup>2</sup> For more information, see Clock Domains on Page 9.

<sup>&</sup>lt;sup>3</sup>LCLK\_P and SCLK\_P must be connected to the same source.

$<sup>^4</sup>$  The value of (t<sub>SCLK</sub> / LCLKRAT2-0) must not violate the specification for t<sub>CCLK</sub>.

$<sup>^{\</sup>rm 5}$  Actual input jitter should be combined with ac specifications for accurate timing analysis.

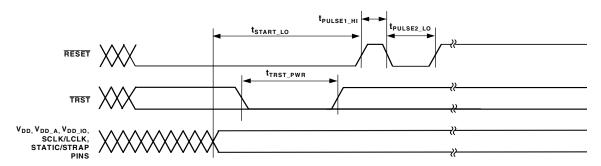

Table 25. Power-Up Reset Timing

| Parameter                          |                                                                                                                                                        | Min                         | Max                          | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|------|

| Timing Requirer                    | ments                                                                                                                                                  |                             |                              |      |

| t <sub>START_LO</sub>              | RESET Deasserted After V <sub>DD</sub> , V <sub>DD_A</sub> , V <sub>DD_IO</sub> , SCLK/LCLK, and Static/Strap Pins Are Stable and Within Specification | 2                           |                              | ms   |

| t <sub>PULSE1_HI</sub>             | RESET Deasserted for First Pulse                                                                                                                       | $50 \times t_{\text{SCLK}}$ | $100 \times t_{\text{SCLK}}$ | ns   |

| t <sub>PULSE2_LO</sub>             | RESET Asserted for Second Pulse                                                                                                                        | $100 \times t_{SCLK}$       |                              | ns   |

| t <sub>TRST_PWR</sub> <sup>1</sup> | TRST Asserted During Power-Up Reset                                                                                                                    | $2\times t_{SCLK}$          |                              | ns   |

$<sup>^{1}</sup> Applies \ after \ V_{DD}, \ V_{DD\_IO}, \ v_{DD\_IO}, \ and \ SCLK/LCLK \ and \ static/strap \ pins \ are \ stable \ and \ within \ specification, \ and \ before \ \overline{RESET} \ is \ deasserted.$

Figure 14. Power-Up Reset Timing

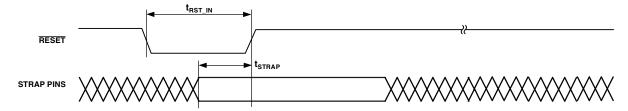

Table 26. Normal Reset Timing

| Parameter           |                                          | Min                   | Max | Unit |

|---------------------|------------------------------------------|-----------------------|-----|------|

| Timing Requirem     | ents                                     |                       |     |      |

| t <sub>RST_IN</sub> | RESET Asserted                           | $100 \times t_{SCLK}$ |     | ns   |

| t <sub>STRAP</sub>  | RESET Deasserted After Strap Pins Stable | 2                     |     | ms   |

Figure 15. Normal Reset (Hot Reset) Timing

Table 27. AC Signal Specifications (for SCLK <16.7 ns) (All values in this table are in nanoseconds)

| Name                       | Description                     | Input Setup<br>(min) | Input Hold<br>(min) | Output Valid<br>(max) <sup>1</sup> | Output Hold<br>(min) | Output Enable (min) <sup>2</sup> | Output Disable (max) <sup>2</sup> | Reference<br>Clock  |

|----------------------------|---------------------------------|----------------------|---------------------|------------------------------------|----------------------|----------------------------------|-----------------------------------|---------------------|

| ADDR31-0                   | External Address Bus            | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| DATA63-0                   | External Data Bus               | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| MSH                        | Memory Select Host Line         |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| MSSD                       | Memory Select SDRAM Line        | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| MS1-0                      | Memory Select for Static Blocks |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| RD                         | Memory Read                     | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| WRL                        | Write Low Word                  | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| WRH                        | Write High Word                 | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| ACK                        | Acknowledge for Data            | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| SDCKE                      | SDRAM Clock Enable              | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| RAS                        | Row Address Select              | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| CAS                        | Column Address Select           | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| SDWE                       | SDRAM Write Enable              | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| LDQM                       | Low Word SDRAM Data Mask        |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| HDQM                       | High Word SDRAM Data Mask       |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| SDA10                      | SDRAM ADDR10                    |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| HBR                        | Host Bus Request                | 2.6                  | 0.5                 |                                    |                      |                                  |                                   | SCLK                |

| HBG                        | Host Bus Grant                  | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| BOFF                       | Back Off Request                | 2.6                  | 0.5                 |                                    |                      |                                  |                                   | SCLK                |

| BUSLOCK                    | Bus Lock                        |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| BRST                       | Burst Access                    | 2.6                  | 0.5                 | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| BR7-0                      | Multiprocessing Bus Request     | 2.6                  | 0.5                 | 4.2                                | 1.0                  |                                  |                                   | SCLK                |

| FLYBY                      | Flyby Mode Selection            |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| IOEN                       | Flyby I/O Enable                |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| <u>CPA</u> 3, 4            | Core Priority Access            | 2.6                  | 0.5                 | 5.8                                |                      |                                  | 2.5                               | SCLK                |

| DPA 3,4                    | DMA Priority Access             | 2.6                  | 0.5                 | 5.8                                |                      |                                  | 2.5                               | SCLK                |

| BMS <sup>5</sup>           | Boot Memory Select              |                      |                     | 4.2                                | 1.0                  | 0.9                              | 2.5                               | SCLK                |

| FLAG3-0 <sup>6</sup>       | FLAG Pins                       |                      |                     | 4.2                                | 1.0                  | 1.0                              | 4.0                               | SCLK                |

| RESET <sup>4,7</sup>       | Global Reset                    |                      |                     |                                    |                      |                                  |                                   | SCLK                |

| TMS <sup>4</sup>           | Test Mode Select (JTAG)         | 1.5                  | 1.0                 |                                    |                      |                                  |                                   | TCK                 |

| TDI <sup>4</sup>           | Test Data Input (JTAG)          | 1.5                  | 1.0                 |                                    |                      |                                  |                                   | TCK                 |

| TDO                        | Test Data Output (JTAG)         |                      |                     | 6.0                                | 1.0                  | 1.0                              | 5.0                               | TCK_FE <sup>8</sup> |

| TRST <sup>4, 7, 9</sup>    | Test Reset (JTAG)               |                      |                     |                                    |                      |                                  |                                   | TCK                 |

| BM <sup>5</sup>            | Bus Master Debug Aid Only       |                      |                     | 4.2                                | 1.0                  |                                  |                                   | SCLK                |

| EMU <sup>10</sup>          | Emulation                       |                      |                     | 5.5                                |                      |                                  | 5.0                               | TCK or LCLK         |

| JTAG_SYS_IN <sup>11</sup>  | System Input                    | 1.5                  | 11.0                |                                    |                      |                                  |                                   | TCK                 |

| JTAG_SYS_OUT <sup>12</sup> | System Output                   |                      |                     | 16.0                               |                      |                                  |                                   | TCK_FE <sup>8</sup> |

| ID2-0 <sup>9</sup>         | Chip ID—Must Be Constant        |                      |                     |                                    |                      |                                  |                                   |                     |

| CONTROLIMP2-0 <sup>9</sup> | Static Pins—Must Be Constant    |                      |                     |                                    |                      |                                  |                                   |                     |

| DS2-0 <sup>9</sup>         | Static Pins—Must Be Constant    |                      |                     |                                    |                      |                                  |                                   |                     |

| LCLKRAT2-0 <sup>9</sup>    | Static Pins—Must Be Constant    |                      |                     |                                    |                      |                                  |                                   |                     |

| SCLKFREQ <sup>9</sup>      | Static Pins—Must Be Constant    |                      |                     |                                    |                      |                                  |                                   |                     |

Table 28. AC Signal Specifications (for 16.7 ns <SCLK <25 ns) (All values in this table are in nanoseconds) (Continued)

| Name                       | Description                  | Input Setup<br>(min) | Input Hold<br>(min) | Output Valid<br>(max) <sup>1</sup> | Output Hold<br>(min) | Output Enable (min) <sup>2</sup> | Output Disable (max) <sup>2</sup> | Reference<br>Clock  |

|----------------------------|------------------------------|----------------------|---------------------|------------------------------------|----------------------|----------------------------------|-----------------------------------|---------------------|

| RESET <sup>4, 7</sup>      | Global Reset                 |                      |                     |                                    |                      |                                  |                                   | SCLK                |

| TMS <sup>4</sup>           | Test Mode Select (JTAG)      | 1.5                  | 1.0                 |                                    |                      |                                  |                                   | TCK                 |

| TDI <sup>4</sup>           | Test Data Input (JTAG)       | 1.5                  | 1.0                 |                                    |                      |                                  |                                   | TCK                 |

| TDO                        | Test Data Output (JTAG)      |                      |                     | 6.0                                | 1.0                  | 1.0                              | 5.0                               | TCK_FE <sup>8</sup> |

| TRST <sup>4, 7, 9</sup>    | Test Reset (JTAG)            |                      |                     |                                    |                      |                                  |                                   | TCK                 |

| BM <sup>5</sup>            | Bus Master Debug Aid Only    |                      |                     | 4.2                                | 0.8                  |                                  |                                   | SCLK                |

| EMU <sup>10</sup>          | Emulation                    |                      |                     | 5.5                                |                      |                                  | 5.0                               | TCK or LCLK         |

| JTAG_SYS_IN <sup>11</sup>  | System Input                 | 1.5                  | 11.0                |                                    |                      |                                  |                                   | TCK                 |

| JTAG_SYS_OUT <sup>12</sup> | System Output                |                      |                     | 16.0                               |                      |                                  |                                   | TCK_FE <sup>8</sup> |

| ID2-0 <sup>9</sup>         | Chip ID—Must Be Constant     |                      |                     |                                    |                      |                                  |                                   |                     |

| CONTROLIMP2-09             | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                  |                                   |                     |

| DS2-0 <sup>9</sup>         | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                  |                                   |                     |

| LCLKRAT2-0 <sup>9</sup>    | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                  |                                   |                     |

| SCLKFREQ <sup>9</sup>      | Static Pins—Must Be Constant |                      |                     |                                    |                      |                                  |                                   |                     |

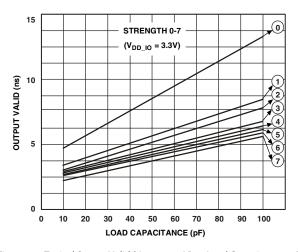

<sup>&</sup>lt;sup>1</sup> The output valid (max) value in this column applies for the standard 30 pF capacitive load used in testing. To see how output valid varies with capacitive loading, see Figure 40 on Page 36.

<sup>&</sup>lt;sup>2</sup> The external port protocols employ bus IDLE cycles for bus mastership transitions as well as slave address boundary crossings to avoid any potential bus contention. The apparent driver overlap, due to output disables being larger than output enables, is not actual.

$<sup>{}^{3}\</sup>overline{\text{CPA}}$  and  $\overline{\text{DPA}}$  pins are open drains and have 0.5 k $\Omega$  internal pull-ups.

<sup>&</sup>lt;sup>4</sup>These input pins have Schmitt triggers and therefore do not need to be synchronized to a clock reference. These synchronous specifications only apply for recognition in the current clock reference cycle.

<sup>&</sup>lt;sup>5</sup> This pin is a strap option. During reset, an internal resistor pulls the pin low.

<sup>&</sup>lt;sup>6</sup> For input specifications, see Table 21.

$<sup>^{7}\,\</sup>mathrm{For}$  additional requirement details, see Reset and Booting on Page 9.

$<sup>^8\,\</sup>mathrm{TCK\_FE}$  indicates TCK falling edge.

$<sup>^9</sup>$  These pins may change only during reset; recommend connecting it to  $\rm V_{DD\_IO}/\rm V_{SS}$

$<sup>^{\</sup>rm 10} \rm Reference$  clock depends on function.

<sup>11</sup> System inputs are: TRQ3-0, BMS, LCLKRAT2-0, SCLKFREQ, BM, TMR0E, FLAG3-0, ID2-0, BRST, WRH, WRL, RD, MSSD, SDCKE, SDWE, CAS, RAS, ADDR31-0, DATA63-0, DPA, CPA, HBG, BOFF, HBR, ACK, BR7-0, L0CLKIN, L0DAT7-0, L1CLKIN, L1DAT7-0, L2CLKIN, L2DAT7-0, L2DIR, L3CLKIN, L3DAT7-0, DS2-0, CONTROLIMP2-0, RESET, DMAR3-0.

<sup>&</sup>lt;sup>12</sup>System outputs are: BMS, BM, BUSLOCK, TMR0E, FLAG3-0, FLYBY, IOEN, MSH, BRST, WRH, WRL, RD, MS1-0, HDQM, LDQM, MSSD, SDCKE, SDWE, CAS, RAS, ADDR31-0, DATA63-0, DPA, CPA, HBG, ACK, BR7-0, L0CLKOUT, L0DAT7-0, L0DIR, L1CLKOUT, L1DAT7-0, L1DIR, L2CLKOUT, L2DAT7-0, L2DIR, L3CLKOUT, L3DAT7-0, L3DIR, EMU.

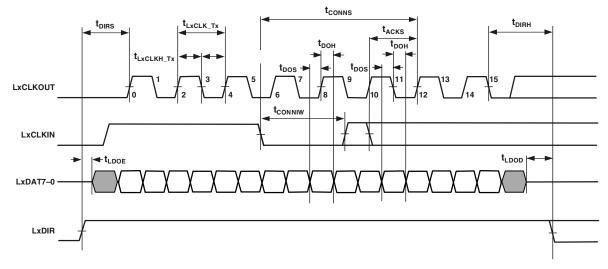

### **Link Ports Data Transfer and Token Switch Timing**

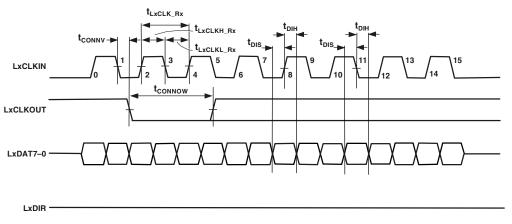

Table 31, Table 32, Table 33, and Table 34 with Figure 17, Figure 18, Figure 19, and Figure 20 provide the timing specifications for the link ports data transfer and token switch.

Table 29. Link Ports—Transmit

| Parameter                        |                                | Min                                     | Max                             | Unit |

|----------------------------------|--------------------------------|-----------------------------------------|---------------------------------|------|

| Timing Requi                     | rements                        |                                         |                                 |      |

| t <sub>CONNS</sub> 1             | Connectivity Pulse Setup       | $2 \times t_{CCLK} + 3.5$               |                                 | ns   |

| t <sub>CONNS</sub> <sup>2</sup>  | Connectivity Pulse Setup       | 8                                       |                                 | ns   |

| t <sub>CONNIW</sub> <sup>3</sup> | Connectivity Pulse Input Width | $t_{LXCLK\_TX} + 1$                     |                                 | ns   |

| t <sub>ACKS</sub>                | Acknowledge Setup              | $0.5 \times t_{LxCLK\_Tx}$              |                                 | ns   |

| Switching Ch                     | aracteristics                  |                                         |                                 |      |

| t <sub>LxCLK_Tx</sub> 4          | Transmit Link Clock Period     | $0.9 \times LR \times t_{CCLK}$         | $1.1 \times LR \times t_{CCLK}$ | ns   |

| t <sub>LxCLKH_Tx</sub> 1         | Transmit Link Clock Width High | $0.33 \times t_{LxCLK\_Tx}$             | $0.66 \times t_{LxCLK\_Tx}$     | ns   |

| t <sub>LxCLKH_Tx</sub> 2         | Transmit Link Clock Width High | $0.4 \times t_{LXCLK\_TX}$              | $0.6 \times t_{LxCLK\_Tx}$      | ns   |

| $t_{LxCLKL\_Tx}^{1}$             | Transmit Link Clock Width Low  | $0.33 \times t_{LxCLK\_Tx}$             | $0.66 \times t_{LxCLK\_Tx}$     | ns   |

| $t_{LxCLKL\_Tx}^{2}$             | Transmit Link Clock Width Low  | $0.4 \times t_{LxCLK\_Tx}$              | $0.6 \times t_{LxCLK\_Tx}$      | ns   |

| t <sub>DIRS</sub>                | LxDIR Transmit Setup           | $0.5 \times t_{LxCLK\_Tx}$              | $2\times t_{\text{LxCLK\_Tx}}$  | ns   |

| t <sub>DIRH</sub>                | LxDIR Transmit Hold            | $0.5 \times t_{LxCLK\_Tx}$              | $2 \times t_{LxCLK\_Tx}$        | ns   |

| t <sub>DOS</sub> <sup>1</sup>    | LxDAT7-0 Output Setup          | $0.25 \times t_{LxCLK\_Tx} - 1$         |                                 | ns   |

| t <sub>DOH</sub> <sup>1</sup>    | LxDAT7-0 Output Hold           | $0.25 \times t_{LxCLK\_Tx} - 1$         |                                 | ns   |

| $t_{DOS}^2$                      | LxDAT7-0 Output Setup          | Greater of 0.8 or $0.17 \times t_{LXC}$ | <sub>CLK_Tx</sub> - 1           | ns   |

| $t_{DOH}^{2}$                    | LxDAT7-0 Output Hold           | Greater of 0.8 or $0.17 \times t_{LXC}$ | <sub>CLK_Tx</sub> – 1           | ns   |

| $t_{LDOE}$                       | LxDAT7-0 Output Enable         | 1                                       |                                 | ns   |

| t <sub>LDOD</sub> <sup>5</sup>   | LxDAT7-0 Output Disable        | 1                                       |                                 | ns   |

$<sup>^{\</sup>rm 1}$  The formula for this parameter applies when LR is 2.

<sup>&</sup>lt;sup>5</sup>This specification applies to the last data byte or the "Dummy" byte that follows the verification byte if enabled. For more information, see the *ADSP-TS101* TigerSHARC *Processor Hardware Reference.*

Figure 17. Link Ports—Transmit

<sup>&</sup>lt;sup>2</sup> The formula for this parameter applies when LR is 3, 4, or 8.

<sup>&</sup>lt;sup>3</sup> LxCLKIN shows the connectivity pulse with each of the three possible transitions to "Acknowledge." After a connectivity pulse low minimum, LxCLKIN may [1] return high and remain high for "Acknowledge," [2] return high and subsequently go low (meeting t<sub>ACKS</sub>) for "Not Acknowledge," or [3] remain low for "Not Acknowledge."

$<sup>^4</sup>$  The Link clock Ratio (LR) is 2, 3, 4, or 8 as set by the SPD bits in the LCTLx register. The maximum LxCLK is 125 MHz. LR = 2 may not be used when CCLK  $\geq$  250 MHz.

Table 30. Link Ports—Receive

| Parameter                           |                                 | Min                             | Max                                | Unit |  |

|-------------------------------------|---------------------------------|---------------------------------|------------------------------------|------|--|

| Timing Requir                       | rements                         |                                 |                                    |      |  |

| t <sub>LxCLK_Rx</sub> 1, 2          | Receive Link Clock Period       | $0.9 \times LR \times t_{CCLK}$ | $1.1 \times LR \times t_{CCLK}$    | ns   |  |

| t <sub>LxCLKH_Rx</sub> 3            | Receive Link Clock Width High   | $0.33 \times t_{LxCLK\_Rx}$     | $0.66 \times t_{\text{LXCLK\_RX}}$ | ns   |  |

| t <sub>LxCLKH_Rx</sub> 4            | Receive Link Clock Width High   | $0.4 \times t_{LxCLK\_Rx}$      | $0.6 \times t_{LxCLK\_Rx}$         | ns   |  |

| $t_{LxCLKL\_Rx}^{3}$                | Receive Link Clock Width Low    | $0.33 \times t_{LxCLK\_Rx}$     | $0.66 \times t_{\text{LXCLK\_RX}}$ | ns   |  |

| t <sub>LxCLKL_Rx</sub> <sup>4</sup> | Receive Link Clock Width Low    | $0.4 \times t_{LxCLK\_Rx}$      | $0.6 \times t_{LxCLK\_Rx}$         | ns   |  |

| t <sub>DIS</sub>                    | LxDAT7-0 Input Setup            | 0.6                             |                                    | ns   |  |

| $t_{DIH}$                           | LxDAT7-0 Input Hold             | 0.6                             |                                    | ns   |  |

| Switching Cha                       | aracteristics                   |                                 |                                    |      |  |

| t <sub>CONNV</sub>                  | Connectivity Pulse Valid        | 0                               | $2.5 \times t_{LxCLK\_Rx}$         | ns   |  |

| t <sub>CONNOW</sub>                 | Connectivity Pulse Output Width | $1.5 \times t_{LxCLK\_Rx}$      |                                    | ns   |  |

$<sup>^{\</sup>rm 1}$  The link clock ratio (LR) is 2, 3, 4, or 8 as set by the SPD bits in the LCTLx register.

<sup>&</sup>lt;sup>4</sup> The formula for this parameter applies when LR is 3, 4, or 8.

Figure 18. Link Ports—Receive

<sup>&</sup>lt;sup>2</sup> The maximum LxCLK is 125 MHz. LR = 2 may not be used when CCLK  $\geq$  250 MHz.

$<sup>^3</sup>$  The formula for this parameter applies when LR is 2.

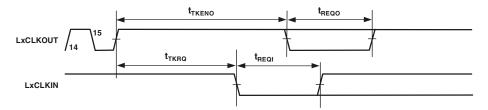

Table 31. Link Ports—Token Switch, Token Master

| Parameter          |                                              | Min                        | Max                        | Unit |  |

|--------------------|----------------------------------------------|----------------------------|----------------------------|------|--|

| Timing Requ        | uirements                                    |                            |                            |      |  |

| $t_{REQI}$         | Token Request Input Width                    | $5.0 \times t_{LxCLK\_Rx}$ |                            | ns   |  |

| $t_{\text{TKRQ}}$  | Token Request from Token Enable <sup>1</sup> |                            | $3.0 \times t_{LxCLK\_Tx}$ | ns   |  |

| Switching C        | haracteristics                               |                            |                            |      |  |

| t <sub>TKENO</sub> | Token Switch Enable Output                   | $8.0 \times t_{LxCLK\_Tx}$ |                            | ns   |  |

| $t_{REQO}$         | Token Request Output Width <sup>2</sup>      | $6.0 \times t_{LxCLK\_Tx}$ |                            | ns   |  |

$<sup>^{\</sup>rm 1}$  For guaranteeing token switch during token enable.

<sup>&</sup>lt;sup>2</sup>LxCLKOUT shows both possible responses to the token request: [1] a "Token Grant" (LxCLKOUT remains high), and [2] a "Token Regret" (LxCLKOUT goes low).

Figure 19. Link Ports—Token Switch, Token Master

Table 32. Link Ports—Token Switch, Token Requester

| Parameter            |                                         | Min                        | Max | Unit |

|----------------------|-----------------------------------------|----------------------------|-----|------|

| Timing Requ          | uirements                               |                            |     |      |

| t <sub>TKENI</sub> 1 | Token Switch Enable Input               | $8.0 \times t_{LxCLK\_Rx}$ |     | ns   |

| Switching C          | Characteristics                         |                            |     |      |

| $t_{REQO}$           | Token Request Output Width <sup>2</sup> | $6.0 \times t_{LXCLK\_RX}$ |     | ns   |

$<sup>^{\</sup>rm 1}\,\rm Required$  whenever there is a break in transmission.

<sup>&</sup>lt;sup>2</sup>LxCLKOUT shows both possible responses to the token request: [1] a "Token Grant" (LxCLKOUT remains high), and [2] a "Token Regret" (LxCLKOUT goes low).

Figure 20. Link Ports—Token Switch, Token Requester

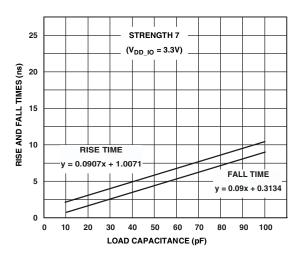

Figure 39. Typical Output Rise and Fall Time (10%–90%,  $V_{DD\_IO}$  = 3.3 V) vs. Load Capacitance at Strength 7

Figure 40. Typical Output Valid ( $V_{DD\_1O} = 3.3 \text{ V}$ ) vs. Load Capacitance at Max Case Temperature and Strength 0–7<sup>1</sup>

<sup>1</sup> The line equations for the output valid vs. load capacitance are:

Strength 0: y = 0.0956x + 3.5662

Strength 1: y = 0.0523x + 3.2144

Strength 2: y = 0.0433x + 3.1319

Strength 3: y = 0.0391x + 2.9675

Strength 4: y = 0.0393x + 2.7653

Strength 5: y = 0.0373x + 2.6515

Strength 6: y = 0.0379x + 2.1206

Strength 7: y = 0.0399x + 1.9080

### **ENVIRONMENTAL CONDITIONS**

The ADSP-TS101S is rated for performance over the extended commercial temperature range,  $T_{CASE} = -40^{\circ}\text{C}$  to +85°C.

### **Thermal Characteristics**

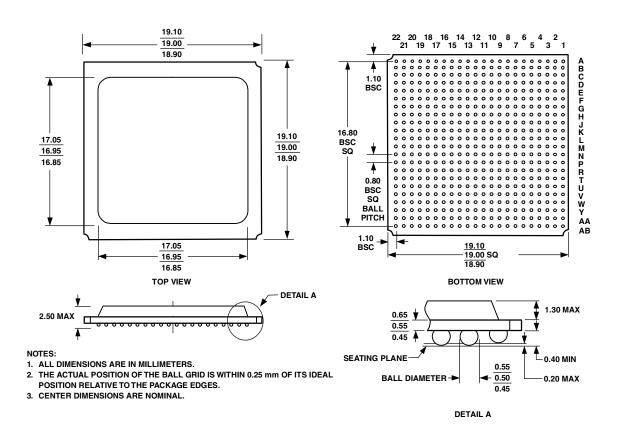

The ADSP-TS101S is packaged in a 19 mm  $\times$  19 mm and 27 mm  $\times$  27 mm Plastic Ball Grid Array (PBGA). The ADSP-TS101S is specified for a case temperature ( $T_{CASE}$ ). To

ensure that the  $T_{CASE}$  data sheet specification is not exceeded, a heat sink and/or an air flow source may be used. See Table 33 and Table 34 for thermal data.

Table 33. Thermal Characteristics for 19 mm × 19 mm Package

| Parameter         | Condition                              | Typical | Unit |

|-------------------|----------------------------------------|---------|------|

| $\theta_{JA}^{1}$ | Airflow <sup>2</sup> = $0 \text{ m/s}$ | 16.6    | °C/W |

|                   | $Airflow^3 = 1 m/s$                    | 14.0    | °C/W |

|                   | Airflow $^3 = 2 \text{ m/s}$           | 12.9    | °C/W |

| $\theta_{JC}$     |                                        | 6.7     | °C/W |

| $\theta_{JB}$     |                                        | 5.8     | °C/W |

<sup>&</sup>lt;sup>1</sup> Determination of parameter is system dependent and is based on a number of factors, including device power dissipation, package thermal resistance, board thermal characteristics, ambient temperature, and air flow.

Table 34. Thermal Characteristics for  $27 \text{ mm} \times 27 \text{ mm}$  Package

| Parameter          | Condition                              | Typical | Unit |

|--------------------|----------------------------------------|---------|------|

| $\theta_{JA}^{}1}$ | Airflow <sup>2</sup> = $0 \text{ m/s}$ | 13.8    | °C/W |

|                    | Airflow $^3 = 1 \text{ m/s}$           | 11.7    | °C/W |

|                    | Airflow $^3 = 2 \text{ m/s}$           | 10.8    | °C/W |

| $\theta_{JC}$      |                                        | 3.1     | °C/W |

| $\theta_{JB}$      |                                        | 5.9     | °C/W |

<sup>&</sup>lt;sup>1</sup> Determination of parameter is system dependent and is based on a number of factors, including device power dissipation, package thermal resistance, board thermal characteristics, ambient temperature, and air flow.

<sup>&</sup>lt;sup>2</sup> Per JEDEC JESD51-2 procedure using a four layer board (compliant with JEDEC JESD51-9)

$<sup>^3</sup>$  Per SEMI Test Method G38-87 using a four layer board (compliant with JEDEC JESD51-9).

<sup>&</sup>lt;sup>2</sup> Per JEDEC JESD51-2 procedure using a four layer board (compliant with JEDEC JESD51-9).

<sup>&</sup>lt;sup>3</sup> Per SEMI Test Method G38-87 using a four layer board (compliant with JEDEC JESD51-9).

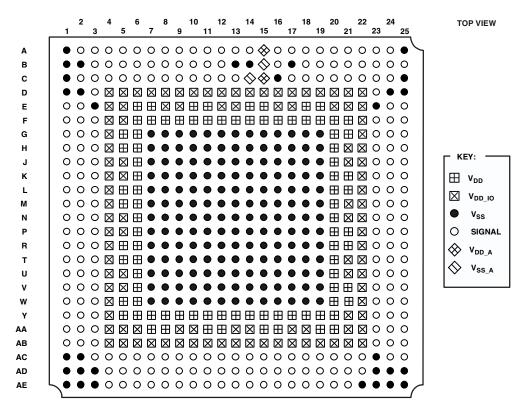

# **PBGA PIN CONFIGURATIONS**

The 484-ball PBGA pin configurations appear in Table 35 and Figure 41. The 625-ball PBGA pin configurations appear in Table 36 and Figure 42.

Table 35. 484-Ball (19 mm  $\times$  19 mm) PBGA Pin Assignments

| Pin No. | Mnemonic     | Pin No. | Mnemonic          | Pin No. | Mnemonic     | Pin No. | Mnemonic           | Pin No. | Mnemonic        |

|---------|--------------|---------|-------------------|---------|--------------|---------|--------------------|---------|-----------------|

| A1      | $V_{SS}$     | B1      | DATA21            | C1      | DATA23       | D1      | DATA24             | E1      | DATA25          |

| A2      | DATA14       | B2      | DATA18            | C2      | DATA17       | D2      | DATA19             | E2      | DATA22          |

| А3      | DATA11       | В3      | DATA12            | C3      | DATA15       | D3      | DATA16             | E3      | DATA20          |

| A4      | DATA8        | B4      | DATA13            | C4      | DATA9        | D4      | $V_{DD\_IO}$       | E4      | $V_{DD\_IO}$    |

| A5      | DATA4        | B5      | DATA7             | C5      | DATA10       | D5      | V <sub>DD</sub>    | E5      | V <sub>DD</sub> |

| A6      | DATA1        | B6      | DATA5             | C6      | DATA6        | D6      | $V_{DD}$           | E6      | $V_{DD}$        |

| A7      | LODIR        | B7      | DATA2             | C7      | DATA3        | D7      | $V_{DD\_IO}$       | E7      | $V_{DD\_IO}$    |

| A8      | LOCLKIN      | B8      | NC                | C8      | DATA0        | D8      | $V_{DD\_IO}$       | E8      | $V_{DD}$        |

| A9      | L0DAT6       | В9      | L0DAT7            | C9      | LOCLKOUT     | D9      | $V_{DD\_IO}$       | E9      | $V_{DD}$        |

| A10     | L0DAT3       | B10     | L0DAT4            | C10     | L0DAT5       | D10     | $V_{DD\_IO}$       | E10     | $V_{DD}$        |

| A11     | L0DAT1       | B11     | L0DAT0            | C11     | L0DAT2       | D11     | $V_{DD\_IO}$       | E11     | $V_{DD\_IO}$    |

| A12     | $V_{SS}$     | B12     | $V_{SS}$          | C12     | LCLK_P       | D12     | $V_{DD\_IO}$       | E12     | $V_{DD}$        |

| A13     | LCLK_N       | B13     | $V_{DD\_A}$       | C13     | $V_{SS}$     | D13     | $V_{DD\_IO}$       | E13     | $V_{DD\_IO}$    |

| A14     | $V_{SS\_A}$  | B14     | V <sub>SS_A</sub> | C14     | $V_{DD\_A}$  | D14     | V <sub>DD_IO</sub> | E14     | $V_{DD}$        |

| A15     | SCLK_N       | B15     | V <sub>SS</sub>   | C15     | DS0          | D15     | $V_{DD\_IO}$       | E15     | $V_{DD\_IO}$    |

| A16     | SCLK_P       | B16     | DS1               | C16     | DS2          | D16     | $V_{DD}$           | E16     | $V_{DD}$        |

| A17     | CONTROLIMP2  | B17     | CONTROLIMP0       | C17     | $V_{REF}$    | D17     | $V_{DD\_IO}$       | E17     | $V_{DD\_IO}$    |

| A18     | CONTROLIMP1  | B18     | DMAR2             | C18     | TRST         | D18     | $V_{DD}$           | E18     | $V_{DD\_IO}$    |

| A19     | RESET        | B19     | DMAR0             | C19     | DMAR3        | D19     | $V_{DD\_IO}$       | E19     | $V_{DD\_IO}$    |

| A20     | DMAR1        | B20     | TMS               | C20     | TCK          | D20     | TDO                | E20     | BM              |

| A21     | <b>EMU</b>   | B21     | TDI               | C21     | ĪRQ3         | D21     | IRQ2               | E21     | BMS             |

| A22     | $V_{SS}$     | B22     | ĪRQ1              | C22     | ĪRQ0         | D22     | LCLKRAT1           | E22     | LCLKRAT2        |

| F1      | DATA29       | G1      | L3DAT1            | H1      | L3DAT2       | J1      | L3DAT5             | K1      | L3CLKOUT        |

| F2      | DATA30       | G2      | DATA28            | H2      | L3DAT0       | J2      | L3DAT3             | K2      | L3DAT7          |

| F3      | DATA26       | G3      | DATA27            | H3      | DATA31       | J3      | L3DAT4             | K3      | L3DAT6          |

| F4      | $V_{DD\_IO}$ | G4      | $V_{DD}$          | H4      | $V_{DD}$     | J4      | $V_{DD\_IO}$       | K4      | $V_{DD\_IO}$    |

| F5      | $V_{DD\_IO}$ | G5      | $V_{DD}$          | H5      | $V_{DD}$     | J5      | $V_{DD\_IO}$       | K5      | $V_{DD\_IO}$    |

| F6      | $V_{SS}$     | G6      | $V_{SS}$          | H6      | $V_{SS}$     | J6      | V <sub>SS</sub>    | K6      | $V_{SS}$        |

| F7      | $V_{SS}$     | G7      | $V_{SS}$          | H7      | $V_{SS}$     | J7      | V <sub>SS</sub>    | K7      | $V_{SS}$        |

| F8      | $V_{SS}$     | G8      | $V_{SS}$          | H8      | $V_{SS}$     | J8      | V <sub>SS</sub>    | K8      | $V_{SS}$        |

| F9      | $V_{SS}$     | G9      | $V_{SS}$          | H9      | $V_{SS}$     | J9      | V <sub>SS</sub>    | K9      | $V_{SS}$        |

| F10     | $V_{SS}$     | G10     | $V_{SS}$          | H10     | $V_{SS}$     | J10     | V <sub>SS</sub>    | K10     | $V_{SS}$        |

| F11     | $V_{SS}$     | G11     | $V_{SS}$          | H11     | $V_{SS}$     | J11     | V <sub>SS</sub>    | K11     | $V_{SS}$        |

| F12     | $V_{SS}$     | G12     | $V_{SS}$          | H12     | $V_{SS}$     | J12     | V <sub>SS</sub>    | K12     | $V_{SS}$        |

| F13     | $V_{SS}$     | G13     | $V_{SS}$          | H13     | $V_{SS}$     | J13     | V <sub>SS</sub>    | K13     | $V_{SS}$        |

| F14     | $V_{SS}$     | G14     | $V_{SS}$          | H14     | $V_{SS}$     | J14     | V <sub>SS</sub>    | K14     | $V_{SS}$        |

| F15     | $V_{SS}$     | G15     | $V_{SS}$          | H15     | $V_{SS}$     | J15     | V <sub>SS</sub>    | K15     | $V_{SS}$        |

| F16     | $V_{SS}$     | G16     | $V_{SS}$          | H16     | $V_{SS}$     | J16     | V <sub>SS</sub>    | K16     | $V_{SS}$        |