#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                             |

| Core Size                  | 16-Bit                                                                              |

| Speed                      | 20MHz                                                                               |

| Connectivity               | CANbus, I <sup>2</sup> C, IEBus, SIO, UART/USART                                    |

| Peripherals                | DMA, WDT                                                                            |

| Number of I/O              | 87                                                                                  |

| Program Memory Size        | 128KB (128K x 8)                                                                    |

| Program Memory Type        | Mask ROM                                                                            |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 5K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                         |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                                |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-BQFP                                                                            |

| Supplier Device Package    | 100-QFP (14x20)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m306n4mct-137fpusq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

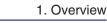

Figure 1.4 Pin Assignments (Top View) (2)

## Table 4.6 SFR Information (6) <sup>(1)</sup>

| Address        | Register                              | Symbol  | After Reset |

|----------------|---------------------------------------|---------|-------------|

| 0140h          | ~                                     |         | XXh         |

| 0141h          |                                       |         | XXh         |

| 0142h          | CAN0 Message Box 14: Identifier /DLC  |         | XXh         |

| 0143h<br>0144h | -                                     |         | XXh<br>XXh  |

| 0144n<br>0145h |                                       |         | XXh         |

| 0145h          |                                       |         | XXh         |

| 0140h          |                                       |         | XXh         |

| 0148h          |                                       |         | XXh         |

| 0149h          | CAN0 Message Box 14: Data Field       |         | XXh         |

| 014Ah          | On No Message Dox 14. Data Field      |         | XXh         |

| 014Bh          |                                       |         | XXh         |

| 014Ch          |                                       |         | XXh<br>XXh  |

| 014Dh<br>014Eh |                                       |         | XXh         |

| 014En          | CAN0 Message Box 14: Time Stamp       |         | XXh         |

| 0150h          |                                       |         | XXh         |

| 0151h          |                                       |         | XXh         |

| 0152h          | CAN0 Message Box 15: Identifier /DLC  |         | XXh         |

| 0153h          | OANO Message box 13. Identifier / DEO |         | XXh         |

| 0154h          |                                       |         | XXh         |

| 0155h          |                                       |         | XXh         |

| 0156h<br>0157h |                                       |         | XXh<br>XXh  |

| 0157h<br>0158h |                                       |         | XXh         |

| 0159h          |                                       |         | XXh         |

| 015Ah          | CAN0 Message Box 15: Data Field       |         | XXh         |

| 015Bh          |                                       |         | XXh         |

| 015Ch          |                                       |         | XXh         |

| 015Dh          |                                       |         | XXh         |

| 015Eh          | CAN0 Message Box 15: Time Stamp       |         | XXh         |

| 015Fh          |                                       |         | XXh<br>XXh  |

| 0160h<br>0161h |                                       |         | XXh         |

| 0162h          |                                       |         | XXh         |

| 0163h          | CAN0 Global Mask Register             | C0GMR - | XXh         |

| 0164h          |                                       |         | XXh         |

| 0165h          |                                       |         | XXh         |

| 0166h          |                                       |         | XXh         |

| 0167h          |                                       |         | XXh         |

| 0168h<br>0169h | CAN0 Local Mask A Register            | COLMAR  | XXh<br>XXh  |

| 016Ah          |                                       |         | XXh         |

| 016Bh          |                                       |         | XXh         |

| 016Ch          |                                       |         | XXh         |

| 016Dh          |                                       |         | XXh         |

| 016Eh          | CAN0 Local Mask B Register            | COLMBR  | XXh         |

| 016Fh          |                                       |         | XXh         |

| 0170h          |                                       |         | XXh<br>XXb  |

| 0171h<br>0172h |                                       |         | XXh         |

| 0172n<br>0173h |                                       |         |             |

| 0173h          |                                       | 1       |             |

| 0175h          |                                       |         |             |

| 0176h          |                                       |         |             |

| 0177h          |                                       |         |             |

| 0178h          |                                       |         |             |

| 0179h          |                                       |         |             |

| 017Ah<br>017Bh |                                       |         |             |

| 017Bh<br>017Ch |                                       |         |             |

| 017Dh          |                                       |         |             |

| 017Eh          |                                       |         |             |

| 017Fh          |                                       |         |             |

|                |                                       |         |             |

X: Undefined

NOTE:

1. Blank spaces are reserved. No access is allowed.

## Table 4.7 SFR Information (7) (2)

| Address        | Register                                       | Symbol | After Reset |

|----------------|------------------------------------------------|--------|-------------|

| 0180h          |                                                |        |             |

| 0181h          |                                                |        |             |

| 0182h          |                                                |        |             |

| 0183h<br>0184h |                                                |        |             |

| 0185h          |                                                |        |             |

| 0186h          |                                                |        |             |

| 0187h          |                                                |        |             |

| 0188h          |                                                |        |             |

| 0189h          |                                                |        |             |

| 018Ah          |                                                |        |             |

| 018Bh          |                                                |        |             |

| 018Ch<br>018Dh |                                                |        |             |

| 018Eh          |                                                |        |             |

| 018Fh          |                                                |        |             |

| 0190h          |                                                |        |             |

| 0191h          |                                                |        |             |

| 0192h          |                                                |        |             |

| 0193h          |                                                |        |             |

| 0194h          |                                                |        |             |

| 0195h<br>0196h |                                                |        |             |

| 0190h          |                                                |        |             |

| 0198h          |                                                |        |             |

| 0199h          |                                                |        |             |

| 019Ah          |                                                |        |             |

| 019Bh          |                                                |        |             |

| 019Ch          |                                                |        |             |

| 019Dh          |                                                |        |             |

| 019Eh<br>019Fh |                                                |        |             |

| 019Fn          |                                                |        |             |

| 01A1h          |                                                |        |             |

| 01A2h          |                                                |        |             |

| 01A3h          |                                                |        |             |

| 01A4h          |                                                |        |             |

| 01A5h          |                                                |        |             |

| 01A6h          |                                                |        |             |

| 01A7h<br>01A8h |                                                |        |             |

| 01A9h          |                                                |        |             |

| 01AAh          |                                                |        |             |

| 01ABh          |                                                |        |             |

| 01ACh          |                                                |        |             |

| 01ADh          |                                                |        |             |

| 01AEh          |                                                |        |             |

| 01AFh          |                                                |        |             |

| 01B0h<br>01B1h |                                                |        |             |

| 01B1h          |                                                |        |             |

| 01B3h          |                                                |        |             |

| 01B4h          |                                                |        |             |

| 01B5h          | Flash Memory Control Register 1 (1)            | FMR1   | 0X00XX0Xb   |

| 01B6h          |                                                |        |             |

| 01B7h          | Flash Memory Control Register 0 <sup>(1)</sup> | FMR0   | 0000001b    |

| 01B8h          | Address Motob Interrupt Register 2             | DMAD2  | 00h         |

| 01B9h<br>01BAh | Address Match Interrupt Register 2             | RMAD2  | 00h<br>X0h  |

| 01BAn<br>01BBh | Address Match Interrupt Enable Register 2      | AIER2  | XXXXXX00b   |

| 01BCh          |                                                |        | 00h         |

| 01BDh          | Address Match Interrupt Register 3             | RMAD3  | 00h         |

| 01BEh          |                                                |        | X0h         |

| 01BFh          |                                                |        |             |

| V: Undofin     |                                                |        |             |

X: Undefined

NOTES:

These registers are included in the flash memory version. Cannot be accessed by users in the mask ROM version.

Blank spaces are reserved. No access is allowed.

## Table 4.8 SFR Information (8) <sup>(1)</sup>

| Address        | Register                                            | Symbol                                | After Reset      |

|----------------|-----------------------------------------------------|---------------------------------------|------------------|

| 01C0h          | Timer B3, B4, B5 Count Start Flag                   | TBSR                                  | 000XXXXXb        |

| 01C0h          | Timer B3, B4, B3 Count Start Flag                   | IBSN                                  | 000//////        |

| 01C1h          |                                                     |                                       | XXh              |

| 01C2h          | Timer A1-1 Register                                 | TA11                                  | XXh              |

| 01C3n          |                                                     |                                       | XXh              |

|                | Timer A2-1 Register                                 | TA21                                  | XXh              |

| 01C5h          | -                                                   |                                       | XXh              |

| 01C6h          | Timer A4-1 Register                                 | TA41                                  |                  |

| 01C7h          |                                                     | 1010/000                              | XXh              |

| 01C8h          | Three-Phase PWM Control Register 0                  | INVC0<br>INVC1                        | 00h              |

| 01C9h          | Three-Phase PWM Control Register 1                  |                                       | 00h              |

| 01CAh          | Three-Phase Output Buffer Register 0                | IDB0                                  | 00111111b        |

| 01CBh          | Three-Phase Output Buffer Register 1                | IDB1                                  | 00111111b        |

| 01CCh          | Dead Time Timer                                     | DTT                                   | XXh              |

| 01CDh          | Timer B2 Interrupt Generation Frequency Set Counter | ICTB2                                 | XXh              |

| 01CEh          |                                                     |                                       |                  |

| 01CFh          |                                                     |                                       |                  |

| 01D0h          | Timer B3 Register                                   | ТВЗ                                   | XXh              |

| 01D1h          |                                                     | 120                                   | XXh              |

| 01D2h          | Timer B4 Register                                   | ТВ4 —                                 | XXh              |

| 01D3h          |                                                     |                                       | XXh              |

| 01D4h          | Timer B5 Register                                   | ТВ5 —                                 | XXh              |

| 01D5h          |                                                     | 185                                   | XXh              |

| 01D6h          |                                                     |                                       |                  |

| 01D7h          |                                                     |                                       |                  |

| 01D8h          |                                                     |                                       |                  |

| 01D9h          |                                                     |                                       |                  |

| 01DAh          |                                                     |                                       |                  |

| 01DBh          | Timer B3 Mode Register                              | TB3MR                                 | 00XX0000b        |

| 01DCh          | Timer B4 Mode Register                              | TB4MR                                 | 00XX0000b        |

| 01DDh          | Timer B5 Mode Register                              | TB5MR                                 | 00XX0000b        |

| 01DEh          | Interrupt Source Select Register 0                  | IFSR0                                 | 00XXX000b        |

| 01DFh          | Interrupt Source Select Register 1                  | IFSR1                                 | 00h              |

| 01E0h          | SI/O3 Transmit/Receive Register                     | S3TRR                                 | XXh              |

| 01E1h          | <b>3</b>                                            |                                       |                  |

| 01E2h          | SI/O3 Control Register                              | S3C                                   | 0100000b         |

| 01E3h          | SI/O3 Bit Rate Register                             | S3BRG                                 | XXh              |

| 01E4h          |                                                     | 002.10                                | 70               |

| 01E5h          |                                                     |                                       |                  |

| 01E6h          |                                                     |                                       |                  |

| 01E7h          |                                                     |                                       |                  |

| 01E8h          |                                                     |                                       |                  |

| 01E9h          |                                                     |                                       |                  |

|                |                                                     |                                       |                  |

| 01EAh<br>01EBh |                                                     |                                       |                  |

|                | LIADTO Cassial Made Degister 4                      |                                       | 00h              |

| 01ECh          | UARTO Special Mode Register 4                       | U0SMR4<br>U0SMR3                      | 00h<br>000X0X0Xb |

| 01EDh          | UARTO Special Mode Register 3                       |                                       |                  |

| 01EEh          | UARTO Special Mode Register 2                       | U0SMR2                                | X000000b         |

| 01EFh          | UARTO Special Mode Register                         | U0SMR                                 | X000000b         |

| 01F0h          | UART1 Special Mode Register 4                       | U1SMR4                                | 00h              |

| 01F1h          | UART1 Special Mode Register 3                       | U1SMR3                                | 000X0X0Xb        |

| 01F2h          | UART1 Special Mode Register 2                       | U1SMR2                                | X000000b         |

| 01F3h          | UART1 Special Mode Register                         | UISMR                                 | X000000b         |

| 01F4h          | UART2 Special Mode Register 4                       | U2SMR4                                | 00h              |

| 01F5h          | UART2 Special Mode Register 3                       | U2SMR3                                | 000X0X0Xb        |

| 01F6h          | UART2 Special Mode Register 2                       | U2SMR2                                | X000000b         |

| 01F7h          | UART2 Special Mode Register                         | U2SMR                                 | X000000b         |

| 01F8h          | UART2 Transmit/Receive Mode Register                | U2MR                                  | 00h              |

| 01F9h          | UART2 Bit Rate Register                             | U2BRG                                 | XXh              |

| 01FAh          | UART2 Transmit Buffer Register                      | U2TB                                  | XXh              |

| 01FBh          | UNITE HAIBIIIL DUILEI NEUISIEL                      | 0210                                  | XXh              |

| 01FCh          | UART2 Transmit/Receive Control Register 0           | U2C0                                  | 00001000b        |

| 01FDh          | UART2 Transmit/Receive Control Register 1           | U2C1                                  | 00000010b        |

| 01FEh          |                                                     |                                       | XXh              |

| 01FFh          | UART2 Receive Buffer Register                       | U2RB —                                | XXh              |

| Villadofia     |                                                     | · · · · · · · · · · · · · · · · · · · |                  |

X: Undefined

NOTE:

1. Blank spaces are reserved. No access is allowed.

## M16C/6N Group (M16C/6N4)

#### Table 4.9 SFR Information (9)

| Address         | Register                           | Symbol             | After Reset |

|-----------------|------------------------------------|--------------------|-------------|

| 0200h           | CAN0 Message Control Register 0    | COMCTLO            | 00h         |

| 0200h           | CANO Message Control Register 1    | COMCTL1            | 00h         |

| 0202h           | CANO Message Control Register 2    | C0MCTL2            | 00h         |

| 0203h           | CAN0 Message Control Register 3    | COMCTL3            | 00h         |

| 0203h           | CAN0 Message Control Register 4    | COMCTL4            | 00h         |

| 020411<br>0205h | CANO Message Control Register 5    | COMCTL5            | 00h         |

| 0205h           | CANO Message Control Register 6    | COMCTL6            | 00h         |

|                 | CANO Message Control Register 7    | COMOTEO<br>COMCTL7 | 00h         |

| 0207h           | CANO Message Control Register 8    | COMCTL8            | 00h         |

| 0208h<br>0209h  | CANO Message Control Register 9    | COMCTL9            | 00h         |

|                 | CANO Message Control Register 9    | COMCTL10           | 00h         |

| 020Ah           |                                    | COMCTL11           |             |

| 020Bh           | CANO Message Control Register 11   |                    | 00h         |

| 020Ch           | CANO Message Control Register 12   | COMCTL12           | 00h         |

| 020Dh           | CANO Message Control Register 13   | COMCTL13           | 00h         |

| 020Eh           | CANO Message Control Register 14   | COMCTL14           | 00h         |

| 020Fh           | CAN0 Message Control Register 15   | C0MCTL15           | 00h         |

| 0210h           | CAN0 Control Register              | COCTLR             | X000001b    |

| 0211h           |                                    |                    | XX0X0000b   |

| 0212h           | CAN0 Status Register               | COSTR              | 00h         |

| 0213h           |                                    | 00011              | X000001b    |

| 0214h           | CAN0 Slot Status Register          | COSSTR             | 00h         |

| 0215h           | CANO OIUL OLALUS HEYISLEI          |                    | 00h         |

| 0216h           | CAN0 Interrupt Control Register    | COICR              | 00h         |

| 0217h           | CANO Interrupt Control Register    | CUICR              | 00h         |

| 0218h           | CANO Estandad ID Bagistar          | 00100              | 00h         |

| 0219h           | CAN0 Extended ID Register          | COIDR              | 00h         |

| 021Ah           |                                    | 0.001              | XXh         |

| 021Bh           | CAN0 Configuration Register        | COCONR             | XXh         |

| 021Ch           | CAN0 Receive Error Count Register  | CORECR             | 00h         |

| 021Dh           | CAN0 Transmit Error Count Register | COTECR             | 00h         |

| 021Eh           | <u> </u>                           |                    | 00h         |

| 021Eh           | CAN0 Time Stamp Register           | COTSR              | 00h         |

| 0220h           | CAN1 Message Control Register 0    | C1MCTL0            | 00h         |

| 022011<br>0221h | CAN1 Message Control Register 0    | C1MCTL1            | 00h         |

| 022111<br>0222h | CAN'T Message Control Register 1   | C1MCTL2            | 00h         |

|                 | CAN'T Message Control Register 2   | C1MCTL2            | 00h         |

| 0223h           |                                    |                    |             |

| 0224h           | CAN1 Message Control Register 4    | C1MCTL4            | 00h         |

| 0225h           | CAN1 Message Control Register 5    | C1MCTL5            | 00h         |

| 0226h           | CAN1 Message Control Register 6    | C1MCTL6            | 00h         |

| 0227h           | CAN1 Message Control Register 7    | C1MCTL7            | 00h         |

| 0228h           | CAN1 Message Control Register 8    | C1MCTL8            | 00h         |

| 0229h           | CAN1 Message Control Register 9    | C1MCTL9            | 00h         |

| 022Ah           | CAN1 Message Control Register 10   | C1MCTL10           | 00h         |

| 022Bh           | CAN1 Message Control Register 11   | C1MCTL11           | 00h         |

| 022Ch           | CAN1 Message Control Register 12   | C1MCTL12           | 00h         |

| 022Dh           | CAN1 Message Control Register 13   | C1MCTL13           | 00h         |

| 022Eh           | CAN1 Message Control Register 14   | C1MCTL14           | 00h         |

| 022Fh           | CAN1 Message Control Register 15   | C1MCTL15           | 00h         |

| 0230h           | CAN1 Control Register              | C1CTLR             | X000001b    |

| 0231h           |                                    | UIUILN             | XX0X0000b   |

| 0232h           | CANI Statua Degister               | C10TD              | 00h         |

| 0233h           | CAN1 Status Register               | C1STR              | X000001b    |

| 0234h           | CANIA Class Chatrice Desciptory    | CLOOTD             | 00h         |

| 0235h           | CAN1 Slot Status Register          | C1SSTR             | 00h         |

| 0236h           |                                    | 0.1105             | 00h         |

| 0237h           | CAN1 Interrupt Control Register    | C1ICR              | 00h         |

| 0238h           |                                    |                    | 00h         |

| 0239h           | CAN1 Extended ID Register          | C1IDR              | 00h         |

| 0233h           |                                    |                    | XXh         |

| 023An           | CAN1 Configuration Register        | C1CONR             | XXh         |

| -               | CAN1 Receive Error Count Register  | C1RECR             | 00h         |

| 023Ch           | CANT Receive Error Count Register  | CITECR             |             |

| 023Dh           |                                    |                    | 00h         |

| 023Eh<br>023Fh  | CAN1 Time Stamp Register           | C1TSR              | 00h<br>00h  |

|                 |                                    |                    | UUN         |

X: Undefined

# **5. Electrical Characteristics**

## 5.1 Electrical Characteristics (T/V-ver.)

#### **Table 5.1 Absolute Maximum Ratings**

| Symbol |                              |                     | Parameter                               | Condition   | Rated Value                    | Unit |

|--------|------------------------------|---------------------|-----------------------------------------|-------------|--------------------------------|------|

| Vcc    | Supply voltage (VCC1 = VCC2) |                     |                                         | VCC = AVCC  | -0.3 to 6.5                    | V    |

| AVcc   | Analog supply voltage        |                     |                                         | VCC = AVCC  | -0.3 to 6.5                    | V    |

| Vi     | Input                        | RESET,              | CNVSS, BYTE,                            |             | -0.3 to VCC+0.3                | V    |

|        | voltage                      | P0_0 to             | P0_7, P1_0 to P1_7, P2_0 to P2_7,       |             |                                |      |

|        |                              | P3_0 to             | P3_7, P4_0 to P4_7, P5_0 to P5_7,       |             |                                |      |

|        |                              | P6_0 to F           | P6_7, P7_0, P7_2 to P7_7, P8_0 to P8_7, |             |                                |      |

|        |                              | P9_0, P             | 9_2 to P9_7, P10_0 to P10_7,            |             |                                |      |

|        |                              | VREF, >             | (IN                                     |             |                                |      |

|        |                              | P7_1, P9_1          |                                         |             | -0.3 to 6.5                    | V    |

| Vo     | Output                       | P0_0 to             | P0_7, P1_0 to P1_7, P2_0 to P2_7,       |             | -0.3 to VCC+0.3                | V    |

|        | voltage                      | P3_0 to             | P3_7, P4_0 to P4_7, P5_0 to P5_7,       |             |                                |      |

|        |                              | P6_0 to             | P6_7, P7_0, P7_2 to P7_7,               |             |                                |      |

|        |                              | P8_0 to I           | P8_4, P8_6, P8_7, P9_0, P9_2 to P9_7,   |             |                                |      |

|        |                              | P10_0 t             | o P10_7, XOUT                           |             |                                |      |

|        |                              | P7_1, P             | 9_1                                     |             | -0.3 to 6.5                    | V    |

| Pd     | Power dis                    | sipation            |                                         | Topr = 25°C | 700                            | mW   |

| Topr   | Operating                    | ambient             | During MCU operation                    |             | T version: -40 to 85           | °C   |

|        | temperature                  |                     |                                         |             | V version: -40 to 125 (option) |      |

|        |                              |                     | During flash memory program and         |             | 0 to 60                        |      |

|        |                              |                     | erase operation                         |             |                                |      |

| Tstg   | Storage te                   | Storage temperature |                                         |             | -65 to 150                     | °C   |

option: All options are on request basis.

## Table 5.2 Recommended Operating Conditions (1)

| Symbol   | Parameter      |                                                                                                       |         | ł    | Unit     |      |

|----------|----------------|-------------------------------------------------------------------------------------------------------|---------|------|----------|------|

| Symbol   |                |                                                                                                       | Min.    | Тур. | Max.     | Unit |

| Vcc      | Supply volta   | ge (VCC1 = VCC2)                                                                                      | 4.2     | 5.0  | 5.5      | V    |

| AVcc     | Analog supp    | ly voltage                                                                                            |         | Vcc  |          | V    |

| Vss      | Supply volta   | ge                                                                                                    |         | 0    |          | V    |

| AVss     | Analog supp    | ly voltage                                                                                            |         | 0    |          | V    |

| VIH      | HIGH input     | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7,                                               | 0.8 Vcc |      | Vcc      | V    |

|          | voltage        | P7_0, P7_2 to P7_7, P8_0 to P8_7, P9_0, P9_2 to P9_7,                                                 |         |      |          |      |

|          |                | P10_0 to P10_7, XIN, RESET, CNVSS, BYTE                                                               |         |      |          |      |

|          |                | P7_1, P9_1                                                                                            | 0.8 Vcc |      | 6.5      | V    |

|          |                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0                                                        | 0.8 Vcc |      | Vcc      | V    |

|          |                | (During single-chip mode)                                                                             |         |      |          |      |

|          |                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0                                                        | 0.5 Vcc |      | Vcc      | V    |

|          |                | (Data input during memory expansion and microprocessor modes)                                         |         |      |          |      |

| VIL      | LOW input      | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7,                                               | 0       |      | 0.2 Vcc  | V    |

|          | voltage        | P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7, P10_0 to P10_7,                                             |         |      |          |      |

|          |                | XIN, RESET, CNVSS, BYTE                                                                               |         |      |          |      |

|          |                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0                                                        | 0       |      | 0.2 Vcc  | V    |

|          |                | (During single-chip mode)                                                                             |         |      |          |      |

|          |                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0                                                        | 0       |      | 0.16 Vcc | V    |

|          |                | (Data input during memory expansion and microprocessor modes)                                         |         |      |          |      |

| OH(peak) | HIGH peak      | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,                                               |         |      | -10.0    | mA   |

|          | output current | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0,                                                       |         |      |          |      |

|          |                | P7_2 to P7_7, P8_0 to P8_4, P8_6, P8_7, P9_0,                                                         |         |      |          |      |

|          |                | P9_2 to P9_7, P10_0 to P10_7                                                                          |         |      |          |      |

| OH(avg)  | HIGH average   | $P0\_0 \text{ to } P0\_7, P1\_0 \text{ to } P1\_7, P2\_0 \text{ to } P2\_7, P3\_0 \text{ to } P3\_7,$ |         |      | -5.0     | mA   |

|          | output current | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0,                                                       |         |      |          |      |

|          |                | P7_2 to P7_7, P8_0 to P8_4, P8_6, P8_7, P9_0,                                                         |         |      |          |      |

|          |                | P9_2 to P9_7, P10_0 to P10_7                                                                          |         |      |          |      |

| OL(peak) | LOW peak       | $P0\_0 \text{ to } P0\_7, P1\_0 \text{ to } P1\_7, P2\_0 \text{ to } P2\_7, P3\_0 \text{ to } P3\_7,$ |         |      | 10.0     | mA   |

|          | output current | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7, $$                                            |         |      |          |      |

|          |                | P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7                                                |         |      |          |      |

| OL(avg)  | LOW average    | $P0\_0 \text{ to } P0\_7, P1\_0 \text{ to } P1\_7, P2\_0 \text{ to } P2\_7, P3\_0 \text{ to } P3\_7,$ |         |      | 5.0      | mA   |

|          | output current | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,                                               |         |      |          |      |

|          |                | P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7                                                |         |      |          |      |

NOTES:

1. Referenced to VCC = 4.2 to 5.5 V at Topr = -40 to  $85^{\circ}$ C unless otherwise specified.

2. Average output current values during 100 ms period.

3. The total IoL(peak) for ports P0, P1, P2, P8\_6, P8\_7, P9, and P10 must be 80 mA max.

The total  $I_{OL(peak)}$  for ports P3, P4, P5, P6, P7, and P8\_0 to P8\_4 must be 80 mA max.

The total  $I_{OH(peak)}$  for ports P0, P1, and P2 must be -40 mA max.

The total  $I_{OH(peak)}$  for ports P3, P4, and P5 must be -40 mA max.

The total  $I_{OH(peak)}$  for ports P6, P7, and P8\_0 to P8\_4 must be -40 mA max.

The total IOH(peak) for ports P8\_6, P8\_7, P9, and P10 must be -40 mA max.

## Table 5.3 Recommended Operating Conditions (2)

| Sumbol   | Parameter                                         |         |                      | Standard           |      |        | Unit |     |

|----------|---------------------------------------------------|---------|----------------------|--------------------|------|--------|------|-----|

| Symbol   |                                                   |         |                      | Min.               | Тур. | Max.   | Unit |     |

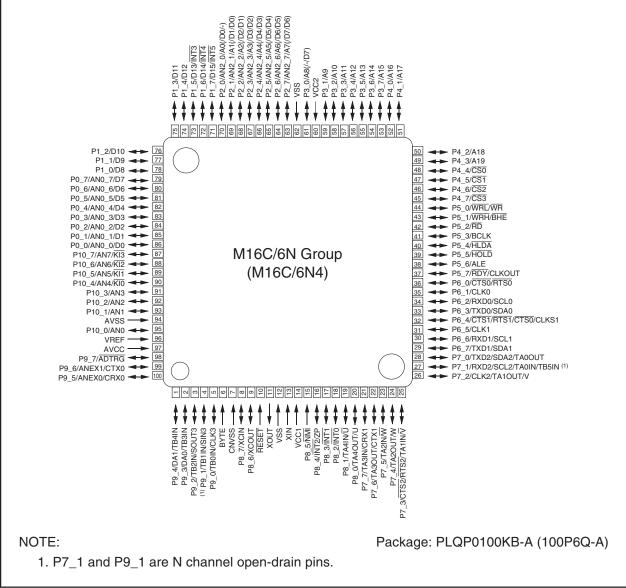

| f(XIN)   | Main clock input oscillation                      | No wait | Mask ROM version     | VCC = 4.2 to 5.5 V | 0    |        | 16   | MHz |

|          | frequency (2) (3) (4)                             |         | Flash memory version |                    |      |        |      |     |

| f(XCIN)  | Sub clock oscillation frequency                   |         |                      |                    |      | 32.768 | 50   | kHz |

| f(Ring)  | On-chip oscillation frequencies                   | uency   |                      |                    |      | 1      |      | MHz |

| f(PLL)   | PLL clock oscillation frequency                   |         |                      |                    | 16   |        | 20   | MHz |

| f(BCLK)  | CPU operation clock VCC = 4.2 to 5.5 V            |         |                      | 0                  |      | 20     | MHz  |     |

| tsu(PLL) | PLL frequency synthesizer stabilization wait time |         |                      |                    |      |        | 20   | ms  |

NOTES:

- 1. Referenced to VCC = 4.2 to 5.5 V at Topr = -40 to 85°C unless otherwise specified.

- 2. Relationship between main clock oscillation frequency and supply voltage is shown right.

- 3. Execute program/erase of flash memory by VCC =  $5.0 \pm 0.5$  V.

- 4. When using over 16 MHz, use PLL clock. PLL clock oscillation frequency which can be used is 16 MHz or 20 MHz.

| Symbol        | Parameter        |                 | Managering Condition |                                            | Standard |      | Linit |      |

|---------------|------------------|-----------------|----------------------|--------------------------------------------|----------|------|-------|------|

| Symbol        | Falan            | neter           |                      | Measuring Condition                        |          | Тур. | Max.  | Unit |

| _             | Resolution       |                 | VREF :               | = VCC                                      |          |      | 10    | Bit  |

| INL           | Integral         | 10 bits         | VREF                 | ANEX0, ANEX1 input, AN0 to AN7 input,      |          |      | ±3    | LSB  |

|               | nonlinearity     |                 | = VCC                | AN0_0 to AN0_7 input, AN2_0 to AN2_7 input |          |      |       |      |

|               | error            |                 | = 5 V                | External operation amp connection mode     |          |      | ±7    | LSB  |

|               |                  | 8 bits          | VREF :               | = AVCC = VCC = 5 V                         |          |      | ±2    | LSB  |

| _             | Absolute         | 10 bits         | VREF                 | ANEX0, ANEX1 input, AN0 to AN7 input,      |          |      | ±3    | LSB  |

|               | accuracy         |                 | = VCC                | AN0_0 to AN0_7 input, AN2_0 to AN2_7 input |          |      |       |      |

|               |                  |                 | = 5 V                | External operation amp connection mode     |          |      | ±7    | LSB  |

|               |                  | 8 bits          | VREF :               | = AVCC = VCC = 5 V                         |          |      | ±2    | LSB  |

| DNL           | Differential nor | linearity error |                      |                                            |          |      | ±1    | LSB  |

| _             | Offset error     |                 |                      |                                            |          |      | ±3    | LSB  |

| _             | Gain error       |                 |                      |                                            |          |      | ±3    | LSB  |

| RLADDER       | Resistor ladde   | r               | VREF :               | = VCC                                      | 10       |      | 40    | kΩ   |

| tconv         | 10-bit conversi  | ion time,       | VREF :               | = VCC = 5 V, φAD = 10 MHz                  | 3.3      |      |       | μs   |

|               | sample & hold    | available       |                      |                                            |          |      |       |      |

|               | 8-bit conversion | on time,        | VREF :               | = VCC = 5 V, φAD = 10 MHz                  | 2.8      |      |       | μs   |

|               | sample & hold    | available       |                      |                                            |          |      |       |      |

| <b>t</b> SAMP | Sampling time    |                 |                      |                                            | 0.3      |      |       | μs   |

| VREF          | Reference volt   | age             |                      |                                            | 2.0      |      | Vcc   | V    |

| VIA           | Analog input v   | oltage          |                      |                                            | 0        |      | VREF  | V    |

#### Table 5.6 A/D Conversion Characteristics (1)

NOTES:

1. Referenced to VCC = AVCC = VREF = 4.2 to 5.5 V, VSS = AVSS = 0 V, -40 to 85°C unless otherwise specified.

2.  $\phi$ AD frequency must be 10 MHz or less.

When sample & hold is disabled, φAD frequency must be 250kHz or more in addition to a limit of NOTE 2.

When sample & hold is enabled, φAD frequency must be 1MHz or more in addition to a limit of NOTE 2.

#### Table 5.7 D/A conversion Characteristics (1)

| Symbol | Parameter                            | Macauring condition | S    | Unit |      |      |

|--------|--------------------------------------|---------------------|------|------|------|------|

|        | Falailletei                          | Measuring condition | Min. | Тур. | Max. | Unit |

| -      | Resolution                           |                     |      |      | 8    | Bits |

| -      | Absolute accuracy                    |                     |      |      | 1.0  | %    |

| tsu    | Setup time                           |                     |      |      | 3    | μs   |

| Ro     | Output resistance                    |                     | 4    | 10   | 20   | kΩ   |

| IVREF  | Reference power supply input current | (NOTE 2)            |      |      | 1.5  | mA   |

NOTES:

1. Referenced to VCC = AVCC = VREF = 4.2 to 5.5 V, VSS = AVSS = 0 V, -40 to 85°C unless otherwise specified.

2. This applies when using one D/A converter, with the DAi register (i = 0, 1) for the unused D/A converter set to 00h. The resistor ladder of the A/D converter is not included. Also, the  $I_{VREF}$  will flow even if VREF is disconnected by the ADCON1 register.

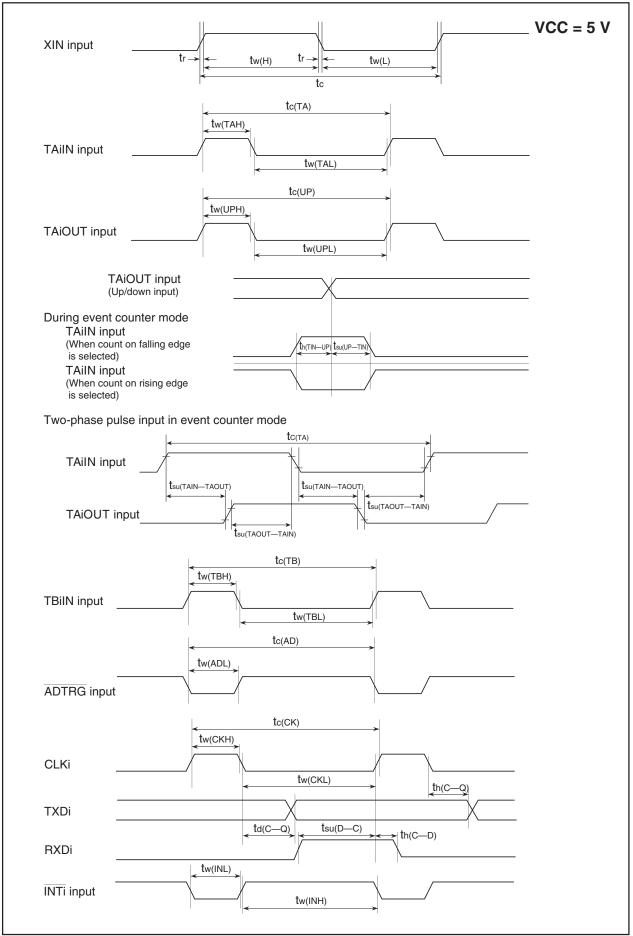

## Timing Requirements VCC = 5 V(Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85°C unless otherwise specified)

#### Table 5.9 External Clock Input (XIN Input)

| Symbol            | Parameter                             | Stan | Unit |      |

|-------------------|---------------------------------------|------|------|------|

|                   | Parameter                             |      | Max. | Unit |

| tc                | External clock input cycle time       | 62.5 |      | ns   |

| t <sub>w(H)</sub> | External clock input HIGH pulse width | 25   |      | ns   |

| tw(L)             | External clock input LOW pulse width  | 25   |      | ns   |

| tr                | External clock rise time              |      | 15   | ns   |

| tr                | External clock fall time              |      | 15   | ns   |

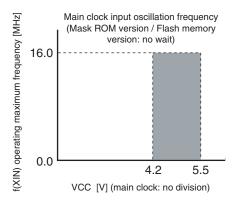

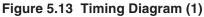

#### Table 5.10 Memory Expansion Mode and Microprocessor Mode

| Symbol            | Parameter                                                    | Stan | Unit     |      |

|-------------------|--------------------------------------------------------------|------|----------|------|

| Symbol            | Falameter                                                    | Min. | Max.     | Unit |

| tac1(RD-DB)       | Data input access time (for setting with no wait)            |      | (NOTE 1) | ns   |

| tac2(RD-DB)       | Data input access time (for setting with wait)               |      | (NOTE 2) | ns   |

| tac3(RD-DB)       | Data input access time (when accessing multiplexed bus area) |      | (NOTE 3) | ns   |

| tsu(DB-RD)        | Data input setup time                                        | 40   |          | ns   |

| tsu(RDY-BCLK)     | RDY input setup time                                         | 30   |          | ns   |

| tsu(HOLD-BCLK)    | HOLD input setup time                                        | 40   |          | ns   |

| <b>t</b> h(RD-DB) | Data input hold time                                         | 0    |          | ns   |

| th(BCLK-RDY)      | RDY input hold time                                          | 0    |          | ns   |

| th(BCLK-HOLD)     | HOLD input hold time                                         | 0    |          | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 45 [ns]$$

2. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5) \times 10^9}{f(BCLK)} - 45 \text{ [ns]}$  n is "2" for 1-wait setting, "3" for 2-wait setting and "4" for 3-wait setting.

3. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5) \times 10^9}{f(BCLK)} - 45 \text{ [ns]} \qquad n \text{ is "2" for 2-wait setting, "3" for 3-wait setting.}$$

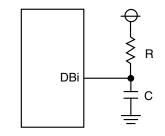

Figure 5.10 Timing Diagram (8)

RENESAS

## 5.2 Electrical Characteristics (Normal-ver.)

| Symbol | Parameter                    |            |                                           | Condition   | Rated Value     | Unit |

|--------|------------------------------|------------|-------------------------------------------|-------------|-----------------|------|

| Vcc    | Supply voltage (VCC1 = VCC2) |            |                                           | VCC = AVCC  | -0.3 to 6.5     | V    |

| AVcc   | Analog su                    | pply volta | age                                       | VCC = AVCC  | -0.3 to 6.5     | V    |

| Vi     | Input                        | RESET,     | CNVSS, BYTE,                              |             | -0.3 to VCC+0.3 | V    |

|        | voltage                      | P0_0 to    | P0_7, P1_0 to P1_7, P2_0 to P2_7,         |             |                 |      |

|        |                              | P3_0 to    | P3_7, P4_0 to P4_7, P5_0 to P5_7,         |             |                 |      |

|        |                              | P6_0 to F  | P6_7, P7_0, P7_2 to P7_7, P8_0 to P8_7,   |             |                 |      |

|        |                              | P9_0, P    | 9_2 to P9_7, P10_0 to P10_7,              |             |                 |      |

|        |                              | VREF, >    | (IN                                       |             |                 |      |

|        |                              | P7_1, P    | 9_1                                       |             | -0.3 to 6.5     | V    |

| Vo     | Output                       | P0_0 to    | P0_7, P1_0 to P1_7, P2_0 to P2_7,         |             | -0.3 to VCC+0.3 | V    |

|        | voltage P3_0 to              |            | P3_7, P4_0 to P4_7, P5_0 to P5_7,         |             |                 |      |

|        |                              | P6_0 to    | P6_7, P7_0, P7_2 to P7_7,                 |             |                 |      |

|        |                              | P8_0 to I  | P8_4, P8_6, P8_7, P9_0, P9_2 to P9_7,     |             |                 |      |

|        |                              | P10_0 t    | p P10_7, XOUT                             |             |                 |      |

|        |                              | P7_1, P    | 9_1                                       |             | -0.3 to 6.5     | V    |

| Pd     | Power dis                    | sipation   |                                           | Topr = 25°C | 700             | mW   |

| Topr   | Operating                    | ambient    | During MCU operation                      |             | -40 to 85       | °C   |

|        | temperature                  |            | During flash memory program and           |             | 0 to 60         |      |

|        |                              |            | erase operation                           |             |                 |      |

| Tstg   | Storage temperatur           |            | re la |             | -65 to 150      | °C   |

#### **Table 5.26 Absolute Maximum Ratings**

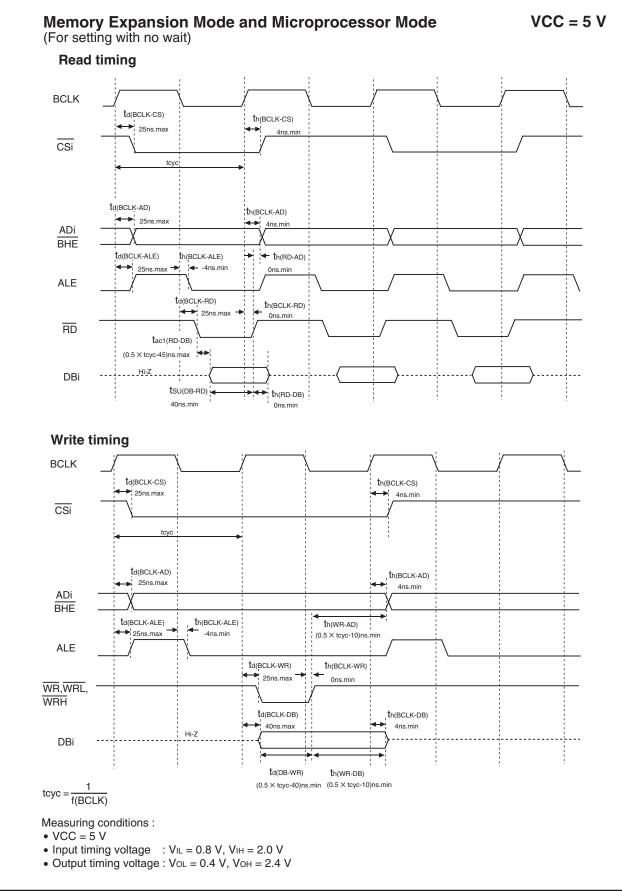

#### **Switching Characteristics**

## VCC = 5 V

## (Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85 °C unless otherwise specified)

|                    |                                                    | •           | -        |      |      |

|--------------------|----------------------------------------------------|-------------|----------|------|------|

| Symbol             | Parameter                                          | Measuring   | Standard |      | Unit |

| Symbol             | i didificici                                       | Condition   | Min.     | Max. |      |

| $t_{d(BCLK-AD)}$   | Address output delay time                          | Figure 5.12 |          | 25   | ns   |

| $t_{h(BCLK-AD)}$   | Address output hold time (in relation to BCLK)     |             | 4        |      | ns   |

| th(RD-AD)          | Address output hold time (in relation to RD)       |             | 0        |      | ns   |

| th(WR-AD)          | Address output hold time (in relation to WR)       |             | (NOTE 1) |      | ns   |

| td(BCLK-CS)        | Chip select output delay time                      |             | 25       |      | ns   |

| $t_{h(BCLK-CS)}$   | Chip select output hold time (in relation to BCLK) |             | 4        |      | ns   |

| $t_{d(BCLK-ALE)}$  | ALE signal output delay time                       |             |          | 15   | ns   |

| $t_{h(BCLK-ALE)}$  | ALE signal output hold time                        |             | -4       |      | ns   |

| td(BCLK-RD)        | RD signal output delay time                        |             |          | 25   | ns   |

| th(BCLK-RD)        | RD signal output hold time                         |             | 0        |      | ns   |

| $t_{d(BCLK-WR)}$   | WR signal output delay time                        |             |          | 25   | ns   |

| $t_{h(BCLK-WR)}$   | WR signal output hold time                         |             | 0        |      | ns   |

| td(BCLK-DB)        | Data output delay time (in relation to BCLK)       |             |          | 40   | ns   |

| th(BCLK-DB)        | Data output hold time (in relation to BCLK) (3)    |             | 4        |      | ns   |

| td(DB-WR)          | Data output delay time (in relation to WR)         |             | (NOTE 2) |      | ns   |

| th(WR-DB)          | Data output hold time (in relation to WR) (3)      |             | (NOTE 1) |      | ns   |

| $t_{d(BCLK-HLDA)}$ | HLDA output delay time                             |             |          | 40   | ns   |

## Table 5.48 Memory Expansion Mode and Microprocessor Mode (for setting with no wait)

NOTES:

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 40 \text{ [ns]} \qquad f(BCLK) \text{ is } 12.5 \text{ MHz or less.}$$

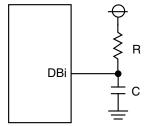

3. This standard value shows the timing when the output is off, and does not show hold time of data bus.

Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value.

Hold time of data bus is expressed in  $t = - CR \times ln (1 - V_{OL} / V_{CC})$

by a circuit of the right figure.

For example, when  $V_{OL} = 0.2 V_{CC}$ , C = 30 pF,

R =1 k $\Omega$ , hold time of output "L" level is

t =  $-30 \text{ pF} \times 1 \text{ k}\Omega \times \text{ln} (1 - 0.2 \text{ Vcc} / \text{Vcc}) = 6.7 \text{ ns.}$

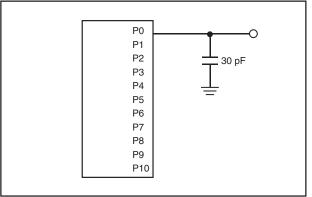

Figure 5.12 Port P0 to P10 Measurement Circuit

## Switching Characteristics

## VCC = 5 V

## (Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85 °C unless otherwise specified)

| Symbol            | Parameter                                          | Measuring   | Standard |      | Unit |  |

|-------------------|----------------------------------------------------|-------------|----------|------|------|--|

| Symbol            | Falameter                                          | Condition   | Min.     | Max. |      |  |

| td(BCLK-AD)       | Address output delay time                          | Figure 5.12 |          | 25   | ns   |  |

| th(BCLK-AD)       | Address output hold time (in relation to BCLK)     |             | 4        |      | ns   |  |

| th(RD-AD)         | Address output hold time (in relation to RD)       |             | 0        |      | ns   |  |

| th(WR-AD)         | Address output hold time (in relation to WR)       |             | (NOTE 1) |      | ns   |  |

| td(BCLK-CS)       | Chip select output delay time                      |             |          | 25   | ns   |  |

| $t_{h(BCLK-CS)}$  | Chip select output hold time (in relation to BCLK) |             | 4        |      | ns   |  |

| $t_{d(BCLK-ALE)}$ | ALE signal output delay time                       |             |          | 15   | ns   |  |

| $t_{h(BCLK-ALE)}$ | ALE signal output hold time                        |             | -4       |      | ns   |  |

| td(BCLK-RD)       | RD signal output delay time                        |             |          | 25   | ns   |  |

| $t_{h(BCLK-RD)}$  | RD signal output hold time                         |             | 0        |      | ns   |  |

| $t_{d(BCLK-WR)}$  | WR signal output delay time                        |             |          | 25   | ns   |  |

| th(BCLK-WR)       | WR signal output hold time                         |             | 0        |      | ns   |  |

| td(BCLK-DB)       | Data output delay time (in relation to BCLK)       |             |          | 40   | ns   |  |

| th(BCLK-DB)       | Data output hold time (in relation to BCLK) (3)    |             | 4        |      | ns   |  |

| td(DB-WR)         | Data output delay time (in relation to WR)         |             | (NOTE 2) |      | ns   |  |

| th(WR-DB)         | Data output hold time (in relation to WR) (3)      |             | (NOTE 1) |      | ns   |  |

| td(BCLK-HLDA)     | HLDA output delay time                             |             |          | 40   | ns   |  |

## Table 5.49 Memory Expansion Mode and Microprocessor Mode (for 1- to 3-wait setting and external area access)

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10 [ns]$$

2. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5) \times 10^9}{f(BCLK)} - 40 \text{ [ns]}$

n is "1" for 1-wait setting, "2" for 2-wait setting and "3" for 3-wait setting. When n = 1, f(BCLK) is 12.5 MHz or less.

3. This standard value shows the timing when the output is off, and does not show hold time of data bus.

Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value.

Hold time of data bus is expressed in

$t = -CR \times ln (1 - V_{OL} / V_{CC})$

by a circuit of the right figure.

For example, when  $V_{OL} = 0.2 V_{CC}$ , C = 30 pF,

R =1 k $\Omega$ , hold time of output "L" level is

t =  $-30 \text{ pF} \times 1 \text{ k}\Omega \times \text{ln} (1 - 0.2 \text{ Vcc} / \text{Vcc}) = 6.7 \text{ ns.}$

#### **Switching Characteristics**

VCC = 5 V

(Referenced to VCC = 5 V, VSS = 0 V, at Topr = -40 to 85 °C unless otherwise specified)

| Symbol                          | Parameter                                             | Measuring    | Standard |      | Unit |

|---------------------------------|-------------------------------------------------------|--------------|----------|------|------|

| Symbol                          |                                                       | Condition    | Min.     | Max. |      |

| $t_{d(BCLK-AD)}$                | Address output delay time                             | Figure 5.12  |          | 25   | ns   |

| $\mathbf{t}_{h(BCLK-AD)}$       | Address output hold time (in relation to BCLK)        |              | 4        | ns   |      |

| th(RD-AD)                       | Address output hold time (in relation to RD)          |              | (NOTE 1) |      |      |

| th(WR-AD)                       | Address output hold time (in relation to WR)          |              | (NOTE 1) |      | ns   |

| $t_{d(BCLK-CS)}$                | Chip select output delay time                         |              |          | 25   | ns   |

| $t_{h(BCLK-CS)}$                | Chip select output hold time (in relation to BCLK)    |              | 4        |      | ns   |

| $t_{h(RD-CS)}$                  | Chip select output hold time (in relation to RD)      |              | (NOTE 1) |      | ns   |

| $t_{h(WR-CS)}$                  | Chip select output hold time (in relation to WR)      |              | (NOTE 1) |      | ns   |

| $t_{d(BCLK-RD)}$                | RD signal output delay time                           |              | 25       |      | ns   |

| $t_{h(BCLK-RD)}$                | RD signal output hold time                            |              | 0        |      | ns   |

| $t_{d(BCLK-WR)}$                | WR signal output delay time                           |              |          | 25   | ns   |

| $t_{h(BCLK-WR)}$                | WR signal output hold time                            |              | 0        |      | ns   |

| $t_{d(BCLK-DB)}$                | Data output delay time (in relation to BCLK)          |              |          | 40   | ns   |

| $t_{h(BCLK-DB)}$                | Data output hold time (in relation to BCLK)           |              | 4        |      | ns   |

| $t_{d(DB-WR)}$                  | Data output delay time (in relation to WR)            | WR) (NOTE 2) |          | ns   |      |

| th(WR-DB)                       | Data output hold time (in relation to WR)             |              | (NOTE 1) |      | ns   |

| $t_{d(BCLK-HLDA)}$              | HLDA output delay time                                |              |          | 40   | ns   |

| $t_{\text{d}(\text{BCLK-ALE})}$ | ALE signal output delay time (in relation to BCLK)    |              |          | 15   | ns   |

| $t_{h(BCLK-ALE)}$               | ALE signal output hold time (in relation to BCLK)     |              | -4       |      | ns   |

| $t_{d(AD-ALE)}$                 | ALE signal output delay time (in relation to Address) |              | (NOTE 3) |      | ns   |

| $\mathbf{t}_{h(ALE-AD)}$        | ALE signal output hold time (in relation to Address)  | ]            | (NOTE 4) |      | ns   |

| td(AD-RD)                       | RD signal output delay from the end of Address        |              | 0        |      | ns   |

| td(AD-WR)                       | WR signal output delay from the end of Address        |              | 0        |      | ns   |

| $t_{dZ(RD-AD)}$                 | Address output floating start time                    | ]            |          | 8    | ns   |

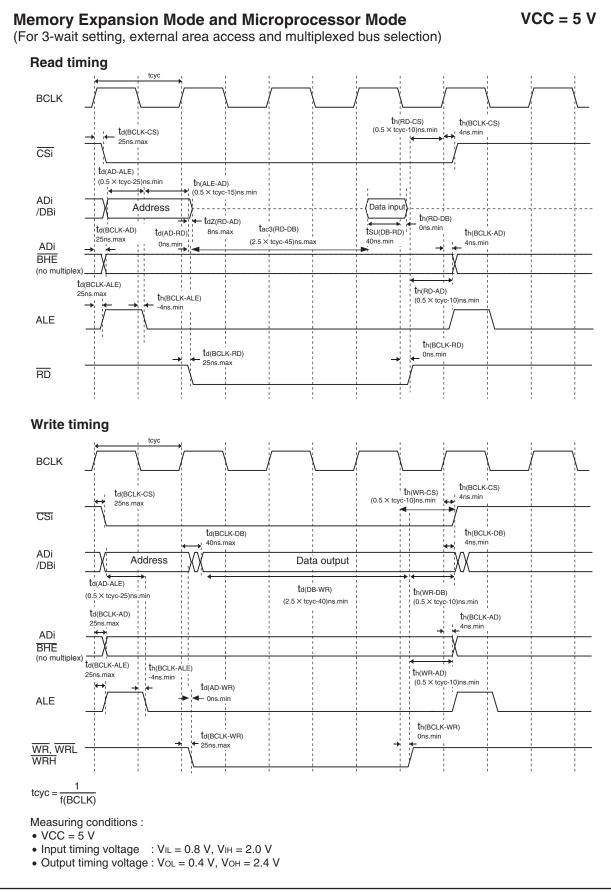

# Table 5.50 Memory Expansion Mode and Microprocessor Mode (for 2- to 3-wait setting, external area access and multiplexed bus selection)

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10 [ns]$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5) \times 10^{\circ}}{f(BCLK)} - 40 \text{ [ns]} \text{ n is "2" for 2-wait setting, "3" for 3-wait setting.}$$

3. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 25 \text{ [ns]}$$

4. Calculated according to the BCLK frequency as follows:

Rev.2.40 Aug 25, 2006 page 64 of 88 REJ03B0003-0240

RENESAS

| Memory Expansion Mode and Microprocessor Mode<br>(Effective for setting with wait)                                                                                                                              | VCC = 5 V |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| BCLK                                                                                                                                                                                                            |           |

| RDY input                                                                                                                                                                                                       |           |

| tsu(RDY-BCLK) + th(BCLK-RDY<br>(Common to setting with wait and setting without wait)<br>BCLK                                                                                                                   |           |

| HOLD input                                                                                                                                                                                                      |           |

| P0, P1, P2,                                                                                                                                                                                                     |           |

| NOTE:<br>1. The above pins are set to high-impedance regardless of the input level of the<br>the PM06 bit in the PM0 register, and the PM11 bit in the PM1 register.                                            | BYTE pin, |

| <ul> <li>Measuring conditions :</li> <li>VCC = 5 V</li> <li>Input timing voltage : Determined with VIL = 1.0 V, VIH = 4.0 V</li> <li>Output timing voltage: Determined with VoL = 2.5 V, VOH = 2.5 V</li> </ul> |           |

Figure 5.14 Timing Diagram (2)

Figure 5.15 Timing Diagram (3)

RENESAS

| Memory Expansion Mode and Microprocessor ModeVCC =(Effective for setting with wait)                                                                                                                                                                                                     | = 3.3 V |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| BCLK    RD    (Separate bus)    WR, WRL, WRH    (Separate bus)    RD    (Multiplexed bus)    WR, WRL, WRH                                                                                                                                                                               |         |

| RDY input                                                                                                                                                                                                                                                                               |         |

| tsu(RDY-BCLK) + th(BCLK-RDY)<br>(Common to setting with wait and setting without wait)<br>BCLK                                                                                                                                                                                          |         |

| HOLD input<br>HLDA output<br>P0, P1, P2,                                                                                                                                                                                                                                                |         |

| P3, P4,<br>P5_0 to P5_2 <sup>(1)</sup>                                                                                                                                                                                                                                                  |         |

| NOTE:<br>1. The above pins are set to high-impedance regardless of the input level of the BYTE p<br>the PM06 bit in the PM0 register, and the PM11 bit in the PM1 register.                                                                                                             | vin,    |

| Measuring conditions :<br>• VCC = $3.3 \text{ V}$<br>• Input timing voltage : Determined with V <sub>IL</sub> = $0.6 \text{ V}$ , V <sub>IH</sub> = $2.7 \text{ V}$<br>• Output timing voltage: Determined with V <sub>OL</sub> = $1.65 \text{ V}$ , V <sub>OH</sub> = $1.65 \text{ V}$ |         |

Figure 5.23 Timing Diagram (2)

## **REVISION HISTORY**

# M16C/6N Group (M16C/6N4) Data Sheet

| Rev.           | Data          |          | Description                                                                                                |  |  |

|----------------|---------------|----------|------------------------------------------------------------------------------------------------------------|--|--|

| Rev. Date Page |               | Page     | Summary                                                                                                    |  |  |

| 2.00           | Nov. 10, 2004 | 34       | Table 5.6 A/D Conversion Characteristics: "Tolerance Level Impedance" is added.                            |  |  |

|                |               | 35       | Table 5.8 Power Supply Circuit Timing Characteristics: "td(M-L)" is deleted.                               |  |  |

|                |               |          | Figure 5.2 Power Supply Circuit Timing Diagram is added.                                                   |  |  |

|                |               | 36       | Table 5.10 Memory Expansion Mode and Microprocessor Mode: "td(BCLK-HLDA)" is deleted.                      |  |  |

|                |               | 38       | Table 5.21 Serial I/O: Min. of standard in t <sub>su(D-C)</sub> is revised from "30" to "70".              |  |  |

|                |               | 39       | Table 5.23 Memory Expansion Mode and Microprocessor Mode (for setting with no wait)                        |  |  |

|                |               |          | • Max. of Standard in td(BCLK-ALE) is revised from "25" to "15".                                           |  |  |

|                |               |          | • td(BCLK-HLDA) is added.                                                                                  |  |  |

|                |               | 40       | Table 5.24 Memory Expansion Mode and Microprocessor Mode (for 1- to 3-wait setting                         |  |  |

|                |               |          | and external area access)                                                                                  |  |  |

|                |               |          | • Max. of Standard in td(BCLK-ALE) is revised from "25" to "15".                                           |  |  |

|                |               |          | • td(BCLK-HLDA) is added.                                                                                  |  |  |

|                |               | 41       | Table 5.25 Memory Expansion Mode and Microprocessor Mode (for 2- to 3-wait setting,                        |  |  |

|                |               |          | external area access and multiplexed bus selection)                                                        |  |  |

|                |               |          | • td(BCLK-HLDA) is added.                                                                                  |  |  |

|                |               |          | • Max. of Standard in td(BCLK-ALE) is revised from "25" to "15".                                           |  |  |

|                |               | 42       | Figure 5.4 Timing Diagram (1): "XIN input" is added.                                                       |  |  |

|                |               | 44, 45   | Figures 5.6 and 5.7 Timing Diagram (3) (4): "DB" in Read timing is revised to "DBi".                       |  |  |

|                |               | 46, 47   | Figures 5.8 and 5.9 Timing Diagram (5) (6): "DB" in Write timing is revised to "DBi".                      |  |  |

|                |               | 49       | Figure 5.11 Timing Diagram (8)                                                                             |  |  |

|                |               |          | <ul> <li>"ADi/DB" in Read/Write timing is revised to "ADi/DBi".</li> </ul>                                 |  |  |

|                |               | 50       | Appendix 1. Package Dimensions: 100P6Q-A is added.                                                         |  |  |

| 2.10           | Jun. 24, 2005 | -        | Revised edition issued                                                                                     |  |  |

|                |               |          | * The contents of product are revised. (Normal-ver. is added.)                                             |  |  |

|                |               |          | * Revised parts and revised contents are as follows (except for expressional change).                      |  |  |

|                |               | 2        | Table 1.1 Performance outline of M16C/6N Group (M16C/6N4)                                                  |  |  |

|                |               | 4        | Performance outline of Normal-ver. is added.                                                               |  |  |

|                |               | 4        | Table 1.2 Product List is revised. (Normal-ver. is added.)                                                 |  |  |

|                |               |          | Figure 1.2 Type No., Memory Size, and Package:                                                             |  |  |

|                |               | 10       | • "(no): Normal-ver." is added to Characteristics.                                                         |  |  |

|                |               | 19<br>32 | Figure 4.7 SFR Information (7): NOTE 1 is revised.<br>Table 5.4 Electrical Characteristics (1)             |  |  |

|                |               | 52       | • Measuring Condition of $V_{OL}$ is revised from "Lo <sub>L</sub> = -200µA" to "Lo <sub>L</sub> = 200µA". |  |  |

|                |               | 33       | Table 5.5 Electrical Characteristics (2): Mask ROM (5th item)                                              |  |  |

|                |               | 00       | • "f(XCIN)" is changed to "(f(BCLK)).                                                                      |  |  |

|                |               | 34       | Table 5.6 A/D Conversion Characteristics: "Tolerance Level Impedance" is deleted.                          |  |  |

| 2 40           | Aug. 25, 2006 |          | Revised edition issued                                                                                     |  |  |

| •              |               |          | * Electric Characteristics of Normal-ver. is added.                                                        |  |  |

|                |               |          | * Revised parts and revised contents are as follows (except for expressional change).                      |  |  |