#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                            |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | nX-U16/100                                                          |

| Core Size                  | 16-Bit                                                              |

| Speed                      | 8.4MHz                                                              |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | POR, PWM, WDT                                                       |

| Number of I/O              | 34                                                                  |

| Program Memory Size        | 64KB (32K x 16)                                                     |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | 1K x 16                                                             |

| RAM Size                   | 2K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                         |

| Data Converters            | A/D 12x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 52-TQFP                                                             |

| Supplier Device Package    | 52-TQFP (10x10)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/rohm-semi/ml620q156a-nnntbwatl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

- Time base counter

- Low-speed time base counter × 1 channel

- Watchdog timer

- Generates a non-maskable interrupt upon the first overflow and a system reset occurs upon the second

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, 8s @32.768kHz)

- Timers

- 8 bits  $\times$  2ch (16-bits configuration available  $\times$  1ch)

- -16 bits  $\times$  4ch

- PWM

- $-16bits \times 4ch$

- The auto reload timer mode / PWM mode

- Timer start-stop function by the software and an external trigger.

- A pulse width can be measured using an external-trigger input.

- An external event can be selected as the counter clock.

- Complement synchronous PWM

- Synchronous serial port

- 1ch

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- UART

- Full-duplex  $\times$  1ch (Half-duplex  $\times$  2ch)

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

- I<sup>2</sup>C bus interface

- Master function only

- Fast mode (400kbit/s), Standard mode (100kbit/s)

- Successive approximation type A/D converter

- 10-bit A/D converter

- Input: 12ch (Maximum)

- Conversion time: 43us, 13.5µs per channel (conversion-time is selectable)

- Analog Comparator

- 1ch

- Edge for the interrupt and sampling function is selectable.

- General-purpose ports (including secondary functions)

- Input-only ports

|                                  | Input-only ports (including multiple |                   |  |  |  |  |

|----------------------------------|--------------------------------------|-------------------|--|--|--|--|

| Product                          | functions)                           |                   |  |  |  |  |

| Floduct                          | When not using the                   | When using the    |  |  |  |  |

|                                  | crystal resonator                    | crystal resonator |  |  |  |  |

| ML620Q151A/ML620Q152A/ML620Q153A | 6ch                                  | 5ch               |  |  |  |  |

| ML620Q154A/ML620Q155A/ML620Q156A | 7ch                                  | 6ch               |  |  |  |  |

| ML620Q157A/ML620Q158A/ML620Q159A | 7ch                                  | 6ch               |  |  |  |  |

- Output-only ports : 4ch

- Input/output ports

|                                  | Input/output ports (including multiple |                |  |  |  |  |  |

|----------------------------------|----------------------------------------|----------------|--|--|--|--|--|

| Product                          | functions)                             |                |  |  |  |  |  |

| rioduct                          | When not using the                     | When using the |  |  |  |  |  |

|                                  | crystal resonator crystal resonator    |                |  |  |  |  |  |

| ML620Q151A/ML620Q152A/ML620Q153A | 31ch                                   | 30ch           |  |  |  |  |  |

| ML620Q154A/ML620Q155A/ML620Q156A | 34ch                                   | 33ch           |  |  |  |  |  |

| ML620Q157A/ML620Q158A/ML620Q159A | 46ch                                   | 45ch           |  |  |  |  |  |

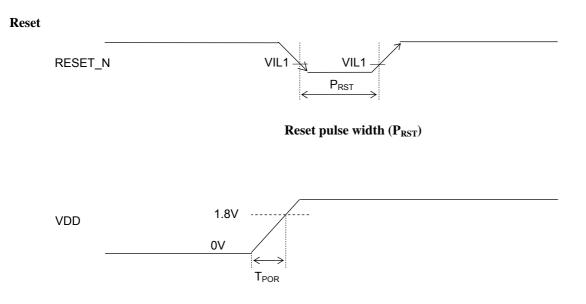

- Reset

- Reset through the RESET\_N pin

- Power-on reset generation when powered on

- Reset by the watchdog timer (WDT) overflow

- Reset by the Low Level Detector (LLD)

- Low Level detect function

- Threshold voltages: 4values (1.9V/2.55V/3.7V/4.2V) A threshold voltage is selected as Code-Option.

- LLD is a ready as a supply-voltage supervisory reset.

Reset or an interrupt output is selectable as Code-Option.

- Clock

- Low-speed clock (This LSI can not guarantee the operation without low-speed clock) Crystal oscillation (32.768 kHz) or Built-in RC oscillation (32.768kHz) Crystal oscillation or Built-in RC oscillation is selectable as Code-Option.

- High-speed clock

Built-in RC oscillation (2.097MHz) or Built-in PLL oscillation (8.192MHz)

- Power management

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, or 1/8 of the oscillation clock)

- Block control function: Operation of an intact functional block circuit is powerd down. (register reset and clock stop)

## **BLOCK DIAGRAM**

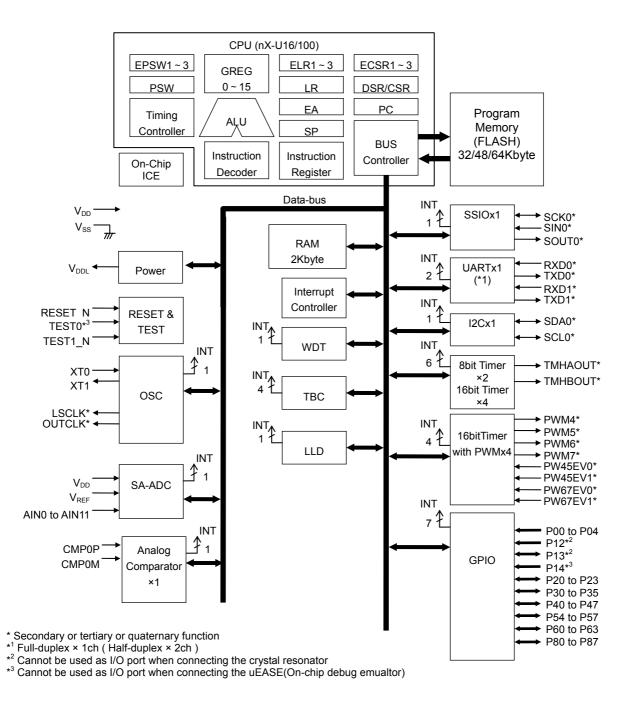

### Block Diagram of ML620Q151A/ML620Q152A/ML620Q153A(TQFP48)

Figure 1-1 Block Diagram of ML620Q151A/ML620Q152A/ML620Q153A(TQFP48)

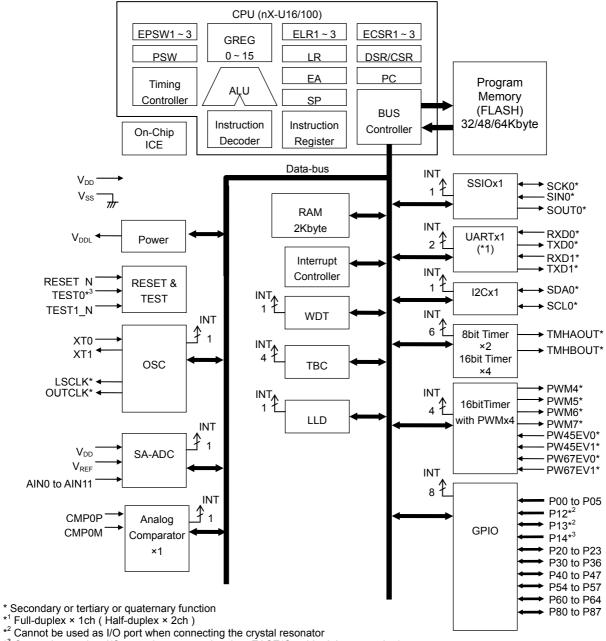

#### Block Diagram of ML620Q154A/ML620Q155A/ML620Q156A(TQFP52)

\*3 Cannot be used as I/O port when connecting the uEASE(On-chip debug emualtor)

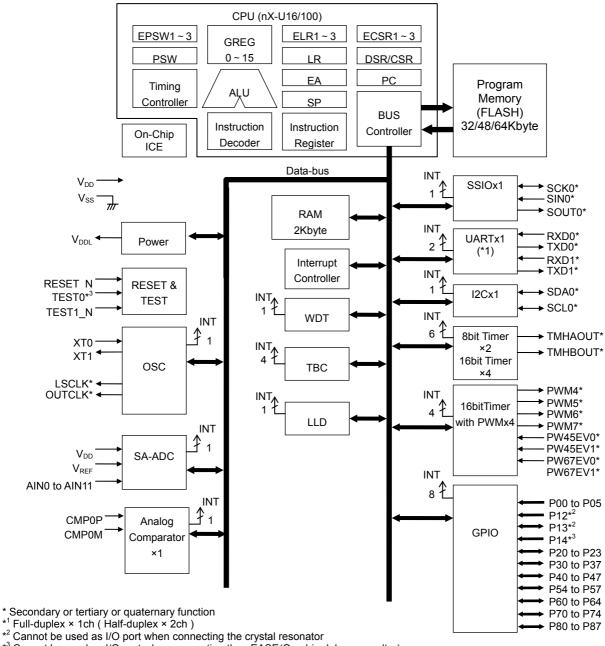

## Block Diagram of ML620Q157A/ML620Q158A/ML620Q159A(QFP64)

\*<sup>3</sup> Cannot be used as I/O port when connecting the uEASE(On-chip debug emualtor)

Figure 1-3 Block Diagram of ML620Q157A/ML620Q158A/ML620Q159A(QFP64)

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

## PIN DESCRIPTION

| Pin name         | I/O    | Description                                                                                                                                                                                                                                                | Primary/<br>Secondary/<br>Tertiary/<br>Quaternary | Logic    |

|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------|

| Power supply     |        |                                                                                                                                                                                                                                                            |                                                   |          |

| V <sub>SS</sub>  | —      | Negative power supply pin                                                                                                                                                                                                                                  |                                                   | _        |

| V <sub>DD</sub>  | —      | Positive power supply pin                                                                                                                                                                                                                                  |                                                   | —        |

| V <sub>DDL</sub> | —      | Positive power supply pin for internal logic (internally generated). Connect capacitors (C <sub>L</sub> ) (see Measuring Circuit 1) between this pin and V <sub>SS</sub> .                                                                                 | _                                                 | _        |

| Test             |        |                                                                                                                                                                                                                                                            |                                                   |          |

| TEST0            | Ι      | Input/output pin for testing.                                                                                                                                                                                                                              | _                                                 | Positive |

| TEST1_N          | Ι      | Input/output pin for testing. This pin has a pull-up resistor built in.                                                                                                                                                                                    |                                                   | Negative |

| System           |        |                                                                                                                                                                                                                                                            |                                                   |          |

| RESET_N          | Ι      | Reset input pin. When this pin is set to a "L" level, the device is placed in system reset mode and the internal circuit is initialized. If after that this pin is set to a "H" level, program execution starts. This pin has a pull-up resistor built in. | _                                                 | Negative |

| ХТ0              | Ι      | Crystal connection pin for low-speed clock. A 32.768 kHz crystal oscillator (see                                                                                                                                                                           |                                                   | _        |

| XT1              | 0      | measuring circuit 1) is connected to this pin. Capacitors CDL and CGL are connected across this pin and VSS as required.                                                                                                                                   | _                                                 | _        |

| LSCLK*           | 0      | Low-speed clock output. This function is allocated to the secondary function of the P20/P36/P65 pin.                                                                                                                                                       |                                                   | —        |

| OUTCLK*          | 0      | High-speed clock output. This function is allocated to the secondary function of the P21/P37/P66 pin.                                                                                                                                                      | Secondary                                         | _        |

| General-purpo    | se inp | ut port                                                                                                                                                                                                                                                    |                                                   |          |

| P00 to P05*      | 1      | General-purpose input or output ports.                                                                                                                                                                                                                     |                                                   |          |

| P12              | Ι      |                                                                                                                                                                                                                                                            |                                                   | <b>–</b> |

| P13              | I/O    |                                                                                                                                                                                                                                                            | Primary                                           | Positive |

| P14              | I      |                                                                                                                                                                                                                                                            |                                                   |          |

| General-purpo    | se ou  | tput port                                                                                                                                                                                                                                                  |                                                   |          |

| P20 to P23       | 0      | General-purpose output ports. Provided with a secondary or tertiary or quaternary function for each port. Cannot be used as ports if their secondary functions or tertiary or quaternary are used.                                                         | Secondary/<br>Tertiary/<br>Quaternary             | Positive |

| General-purpo    | se inp | ut/output port                                                                                                                                                                                                                                             |                                                   |          |

| P30 to P37*      | I/O    | General-purpose output ports. Provided with a secondary or tertiary or quaternary                                                                                                                                                                          | Secondary/                                        | Positive |

| P40 to P47       | 1      | function for each port. Cannot be used as ports if their secondary functions or                                                                                                                                                                            | Tertiary/                                         |          |

| P50 to P57*      | 1      | tertiary or quaternary are used.                                                                                                                                                                                                                           | Quaternary                                        |          |

| P60 to P67*      | 1      |                                                                                                                                                                                                                                                            |                                                   |          |

|                  | 1      |                                                                                                                                                                                                                                                            |                                                   |          |

| P70 to P74*      |        |                                                                                                                                                                                                                                                            |                                                   |          |

## \*: ML620Q15XA have a different pin configuration for each package. See "LIST OF PINS" for more details.

| Pin name |

|----------|

|----------|

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

|                              |                                                                           |                                                                                                                                                                                                                                         | Quaternary              |          |

|------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|

| UART                         |                                                                           |                                                                                                                                                                                                                                         |                         |          |

| TXD0*                        | 0                                                                         | UART0 data output pin. Allocated to the secondary function of the P43, P55 , P87 and the fourthly function of the P73.                                                                                                                  | Secondary<br>Quaternary | Positive |

| RXD0*                        | I                                                                         | UART0 data input pin. Allocated to the secondary function of the P02, P42, P54 and P86.                                                                                                                                                 | Secondary               | Positive |

| TXD1*                        | 0                                                                         | UART1 data output pin. Allocated to the secondary function of the P53, P73, P85, and the fourthly function of the P43, P55.                                                                                                             | Secondary<br>Quaternary | Positive |

| RXD1*                        | I                                                                         | UART1 data input pin. Allocated to the secondary function of the P03, P52, P72 and P84.                                                                                                                                                 | Secondary               | Positive |

| I <sup>2</sup> C bus interfa | ace                                                                       |                                                                                                                                                                                                                                         |                         |          |

| SDA*                         | I/O                                                                       | $I^2C$ data input/output pin. This pin is used as the secondary function of the P40, P50, P60 and P80. This pin has an NMOS open drain output. When using this pin as a function of the $I^2C$ , externally connect a pull-up resistor. | Secondary               | Positive |

| SCL*                         | I/O                                                                       | $\rm I^2C$ clock output pin. This pin is used as the secondary function of the P41, P51, P61 and P81. This pin has an NMOS open drain output. When using this pin as a function of the I^2C, externally connect a pull-up resistor.     | Secondary               | Positive |

| Synchronous                  | serial                                                                    | (SSIO)                                                                                                                                                                                                                                  |                         |          |

| SIN0*                        | Ι                                                                         | Synchronous serial data input pin. Allocated to the tertiary function of the P40, P44, P50, P55, P72, P80 and P84.                                                                                                                      | Tertiary                | Positive |

| SCK0*                        | I/O                                                                       | Synchronous serial clock input/output pin. Allocated to the tertiary function of the P41, P45, P51, P56, P73, P81 and P85.                                                                                                              |                         | _        |

| SOUT0*                       | 0                                                                         | Synchronous serial data output pin. Allocated to the tertiary function of the P42, P46, P52, P57, P74, P82 and P86.                                                                                                                     | Tertiary                | Positive |

| PWM                          |                                                                           |                                                                                                                                                                                                                                         |                         |          |

| PWM4*                        | 0                                                                         | PWM4 output pin. Allocated to the tertiary function of the P34, P43, P64 and P87.                                                                                                                                                       | Tertiary                | Positive |

| PWM5*                        | 0                                                                         | PWM5 output pin. Allocated to the tertiary function of the P35, P47, P65 and P83.                                                                                                                                                       | Tertiary                | Positive |

| PWM6*                        | 0                                                                         | PWM6 output pin. Allocated to the tertiary function of the P53, P66, P70 and fourthly function of the P22 and P60.                                                                                                                      | Tertiary<br>Quaternary  | Positive |

| PWM7*                        | 0                                                                         | PWM7 output pin. Allocated to the tertiary function of the P71 and fourthly function of the P23, P57, and P61.                                                                                                                          | Tertiary<br>Quaternary  | Positive |

| PW45EV0<br>PW45EV1           | I                                                                         | Control start /stop/clear for PWM4 and PWM5. Allocated to the primary function of the P00, P30, P32 and P62.                                                                                                                            | Primary                 | _        |

| PW67EV0<br>PW67EV1           | Control start /stop/clear pin for PWM6 and PWM7. Allocated to the primary |                                                                                                                                                                                                                                         | Primary                 | _        |

| T0P4CK                       | I                                                                         | External clock input pin for timer 0 and PWM4. Allocated to the primary function of the P44 pin.                                                                                                                                        | Primary                 | _        |

| T1P5CK                       | Ι                                                                         | External clock input pin for timer 1 and PWM5. Allocated to the primary function of the P45 pin.                                                                                                                                        | Primary                 | —        |

\*: ML620Q15XA have a different pin configuration for each package. See "LIST OF PINS" for more details.

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

| Pin name         | I/O                                                                                                             | Description                                                                                                                                                                                         |          | Logic                 |

|------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|

| External intern  | rupt                                                                                                            |                                                                                                                                                                                                     |          |                       |

| EXI0 ~ 7*        | I                                                                                                               | External maskable interrupt input pins. The interrupt is enabled and interrupt edge is selectable by the software for each bit. Allocated to the primary function of the P00 to P05 and P30 to P31. | Primary  | Positive/<br>Negative |

| Timer            |                                                                                                                 |                                                                                                                                                                                                     |          |                       |

| T16CK0           | I                                                                                                               | External clock input pin for 16bit timer 8, timer A and PWM6. Allocated to the primary function of the P46 pin.                                                                                     | Primary  | _                     |

| T16CK1           | External clock input pin for 16bit timer 9, timer B and PWM7. Allocated to the primary function of the P47 pin. |                                                                                                                                                                                                     | Primary  | _                     |

| TMHAOUT          | 0                                                                                                               | 16bit timer A output pin. Allocated to the tertiary function of the P22 and P60.                                                                                                                    |          | Positive              |

| TMHBOUT          | 0                                                                                                               | 16bit timer B output pin. Allocated to the tertiary function of the P23 and P61.                                                                                                                    | Tertiary | Positive              |

| LED drive        |                                                                                                                 |                                                                                                                                                                                                     |          |                       |

| LED0 to<br>LED3  | 0                                                                                                               | Pins for LED driving. Allocated to the primary function of the P20 to P23 pins.                                                                                                                     | Primary  | Positive/<br>Negative |

| Successive-a     | oproxir                                                                                                         | nation type A/D converter                                                                                                                                                                           |          |                       |

| V <sub>REF</sub> | I                                                                                                               | Reference power supply pin for successive approximation type A/D converter.                                                                                                                         | _        | _                     |

| AIN0 to<br>AIN11 | I                                                                                                               | Analog inputs to Ch0–Ch11 of the successive-approximation type A/D converter. Allocated to the secondary function of the P30 to P35 and P42 to P47 pins.                                            | _        | _                     |

| Analog Comp      | arator                                                                                                          |                                                                                                                                                                                                     |          |                       |

| CMP0P            | Ι                                                                                                               | Non-inverting input for comparator0. This pin is used as the primary function of the P41 pin.                                                                                                       |          | _                     |

| CMP0M            | I                                                                                                               | Inverting input for comparator0. This pin is used as the primary function of the P40 pin.                                                                                                           | _        | _                     |

\*: ML620Q15XA have a different pin configuration for each package. See "LIST OF PINS" for more details.

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

## ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings**

|                        |                   |                              |                              | (V <sub>SS</sub> = 0V |

|------------------------|-------------------|------------------------------|------------------------------|-----------------------|

| Parameter              | Symbol            | Condition                    | Rating                       | Unit                  |

| Power supply voltage 1 | V <sub>DD</sub>   | Ta = 25°C                    | -0.3 to +6.5                 | V                     |

| Power supply voltage 2 | V <sub>DDL</sub>  | Ta = 25°C                    | -0.3 to +2.0                 | V                     |

| Reference voltage      | V <sub>REF</sub>  | Ta = 25°C                    | –0.3 to V <sub>DD</sub> +0.3 | V                     |

| Analog input voltage   | V <sub>AI</sub>   | Ta = 25°C                    | –0.3 to V <sub>DD</sub> +0.3 | V                     |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C                    | –0.3 to V <sub>DD</sub> +0.3 | V                     |

| Output voltage         | V <sub>OUT</sub>  | Ta = 25°C                    | –0.3 to V <sub>DD</sub> +0.3 | V                     |

| Output current 1       | I <sub>OUT1</sub> | Port3,4,5,6,7,8<br>Ta = 25°C | -12 to +11                   | mA                    |

| Output current 2       | I <sub>OUT2</sub> | Port2 Ta = 25°C              | -12 to +20                   | mA                    |

| Power dissipation      | PD                | Ta = 25°C                    | 1                            | W                     |

| Storage temperature    | T <sub>STG</sub>  | _                            | -55 to +150                  | °C                    |

## **Recommended Operating Conditions**

|                                                        |                  |                                           |                                     | $(V_{SS} = 0V)$ |

|--------------------------------------------------------|------------------|-------------------------------------------|-------------------------------------|-----------------|

| Parameter                                              | Symbol           | Condition                                 | Range                               | Unit            |

| Operating temperature                                  | T <sub>OP</sub>  | _                                         | -40 to +105                         | °C              |

| Operating voltage                                      | V <sub>DD</sub>  | —                                         | 1.8 to 5.5                          | V               |

| Reference voltage                                      | V <sub>REF</sub> | —                                         | 1.8 to $V_{DD}$                     | V               |

| Analog input voltage                                   | V <sub>AI</sub>  | —                                         | $V_{\text{SS}}$ to $V_{\text{REF}}$ | V               |

| Operating frequency (CPU)                              | f <sub>OP</sub>  | —                                         | 30k to 8.4M                         | Hz              |

| Low-speed crystal oscillation frequency                | f <sub>XTL</sub> | _                                         | 32.768k                             | Hz              |

| Low-speed crystal oscillation                          | C <sub>DL</sub>  | Use 32.768KHz Crystal<br>Oscillator DT-26 | 12 to 25                            | ۶E              |

| external capacitor                                     | C <sub>GL</sub>  | (DAISHINKU CORP.)                         | 12 to 25                            | pF              |

| Capacitor externally connected to $V_{\text{DDL}}$ pin | CL               | _                                         | 2.2±30%                             | μF              |

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

Power On Reset VDD Rising Time  $(T_{POR})$

#### ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

## **DC Characteristics (LLD)**

| (V <sub>DD</sub> =2.2 to 5.5V, V <sub>SS</sub> =0V, Ta=–40 to +105°C, unless otherwise specified) |                  |                    |               |      |      |      |      |                          |

|---------------------------------------------------------------------------------------------------|------------------|--------------------|---------------|------|------|------|------|--------------------------|

| Parameter                                                                                         | Symbol           | Con                | dition        | Min. | Тур. | Max. | Unit | Meas<br>uring<br>circuit |

|                                                                                                   |                  |                    | LD1 to 0 = 0H | 1.8  | 1.9  | 2    |      |                          |

|                                                                                                   | V <sub>D-</sub>  | When power falling | LD1 to 0 = 1H | 2.45 | 2.55 | 2.65 | V    |                          |

|                                                                                                   |                  |                    | LD1 to 0 = 2H | 3.6  | 3.7  | 3.8  |      |                          |

| LLD threshold voltage                                                                             |                  |                    | LD1 to 0 = 3H | 4.1  | 4.2  | 4.3  |      | 1                        |

| LLD INTESHOLD VOILAGE                                                                             |                  | When power rising  | LD1 to 0 = 0H | 1.85 | 1.98 | 2.1  |      | I                        |

|                                                                                                   |                  |                    | LD1 to 0 = 1H | 2.5  | 2.63 | 2.75 |      |                          |

|                                                                                                   | V <sub>D+</sub>  |                    | LD1 to 0 = 2H | 3.65 | 3.78 | 3.9  |      |                          |

|                                                                                                   |                  |                    | LD1 to 0 = 3H | 4.15 | 4.28 | 4.4  |      |                          |

| Hysterisis                                                                                        | V <sub>hys</sub> | —                  | —             | _    | 80   | _    | mV   | mA                       |

#### -0.1 Ta = 40 to $\pm 105^{\circ}$ C uplace athenwise specified) <u>~ /</u> -2.2 to E EV/V/

#### **DC Characteristics (Analog Comparator)**

#### (V<sub>DD</sub>=2.2 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified)

| Parameter            | Symbol                   | Condition                 | Min. | Тур. | Max.                    | Unit | Meas<br>uring<br>circuit |

|----------------------|--------------------------|---------------------------|------|------|-------------------------|------|--------------------------|

| Common mode Input    | CMPnM<br>V <sub>IN</sub> | —                         | 0    | _    | V <sub>DD</sub><br>-1.4 | V    |                          |

| voltage              | CMPnP<br>V <sub>IN</sub> | _                         | 0    | _    | V <sub>DD</sub>         |      | 1                        |

| Input offset voltage | V <sub>CMPOF</sub>       | —                         | _    | 5    | 100                     | mV   |                          |

| Response time        | T <sub>CMP</sub>         | $CMPnP = CMPnM \pm 100mV$ | _    |      | 1                       | μS   |                          |

## **DC Characteristics (IDD)**

#### (V<sub>DD</sub>=1.8 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified)

| Parameter        | Symbol                                   | Condition                                                                                                  |                       | Min. | Тур. | Max. | Unit | Meas<br>uring<br>circuit |

|------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|--------------------------|

| Supply current   | IDD1 Low-speed/high-speed oscillation is |                                                                                                            | -40 to +35            | —    | 1.0  | 6    |      |                          |

| •                |                                          | stopped. V <sub>DD</sub> =3.0V                                                                             | -40 to +105           | —    | 1.0  | 22   |      |                          |

|                  |                                          | Crystal Oscillating. CPU is in HALT state (LTBC,WBC: Operating <sup>*2</sup> ).                            | -40 to +35            | _    | 2.5  | 7    |      |                          |

| Supply current   | IDD2                                     | High-speed oscillation is stopped. $V_{DD}$ =3.0V                                                          | -40 to +105           | _    | 2.5  | 24   | μA   |                          |

| 2                |                                          | Internal RC Oscillating. CPU is in HALT                                                                    | -40 to +35            | —    | 3.5  | 9    |      | 1                        |

|                  |                                          | state (LTBC,WBC: Operating <sup>*2</sup> ).<br>High-speed oscillation is stopped.<br>V <sub>DD</sub> =3.0V | -40 to +105           | _    | 3.5  | 26   |      |                          |

| Supply current   | IDD3                                     | CPU: Running at 32kHz* <sup>1</sup><br>High-speed oscillation is stopped.                                  | -40 to +35            |      | 13   | 20   |      |                          |

| 3                | 1000                                     | $V_{DD}$ =3.0V                                                                                             | -40 to +105           | _    | 13   | 42   |      |                          |

| Supply current   | IDD4                                     | CPU: Running at 2MHz RC oscillating mode <sup>*2</sup> VDD=5.0V                                            |                       | _    | 0.64 | 2.0  |      |                          |

| Supply current 5 | IDD5                                     | CPU: Running at 8.192MHz PLL oscillatir<br>VDD=5.0V                                                        | ng mode* <sup>2</sup> | —    | 5    | 8    | mA   |                          |

\*<sup>1</sup>: Case when the CPU operating rate is 100% (with no HALT state)

\*<sup>2</sup> : Significant bits of BLKCON0 to BLKCON4 registers are all "1".

#### FEDL620Q150A-01

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

## DC Characteristics (VOHL, IOHL)

| Parameter                                                                       | Symbol | Co                                                                                                       | Min.                                                                                               | Тур.                    | Max. | Unit        | Measuring<br>circuit |   |

|---------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------|------|-------------|----------------------|---|

| Output voltage 1<br>(P20 to P23)<br>(P30 to P37)*<br>(P40 to P47)               | VOH1   | IOH1                                                                                                     | = -0.5mA                                                                                           | V <sub>DD</sub><br>-0.5 | _    | _           |                      |   |

| (P50 to P57)*<br>(P60 to P67)*<br>(P70 to P74)*<br>(P80 to P87)                 | VOL1   | IOL1 = +0.5mA                                                                                            |                                                                                                    | _                       | _    | 0.5         |                      |   |

| Output voltage 2<br>(P20–P23)                                                   | VOL2   | When LED drive<br>mode<br>is selected                                                                    | $\begin{array}{l} \text{IOL2} = +10\text{mA} \\ \text{V}_{\text{DD}} \geq 5.0\text{V} \end{array}$ | _                       | _    | 0.5         |                      | 2 |

|                                                                                 | VOLZ   |                                                                                                          | $\begin{array}{l} \text{IOL2} = +8\text{mA} \\ \text{V}_{\text{DD}} \geq 3.0\text{V} \end{array}$  | _                       | _    | 0.5         |                      |   |

| Output voltage 3<br>(P40 to P41)                                                |        | When I <sup>2</sup> C mode is selected                                                                   | $\begin{array}{l} \text{IOL3} = +3\text{mA} \\ \text{V}_{\text{DD}} \geq 2.0\text{V} \end{array}$  | _                       | _    | 0.4         |                      |   |

| (P50 to P51)* VOL3<br>(P60 to P61)*<br>(P80 to P81)                             | VOL3   |                                                                                                          | $IOL3 = +2mA$ $2.0V > V_{DD} \ge 1.8V$                                                             | _                       | _    | VDD*<br>0.2 |                      |   |

| Output leakage<br>current<br>(P20 to P23)<br>(P30 to P37)*                      | ЮОН    | VOH = V <sub>DD</sub><br>(in high-impedance state)<br>VOL = V <sub>SS</sub><br>(in high-impedance state) |                                                                                                    | _                       | _    | 1           | μA                   | 3 |

| (P40 to P47)<br>(P50 to P57)*<br>(P60 to P67)*<br>(P70 to P74)*<br>(P80 to P87) | IOOL   |                                                                                                          |                                                                                                    | -1                      | _    | _           |                      |   |

#### **DC Characteristics (IIHL)**

### (V<sub>DD</sub>=1.8 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified)

| Parameter                        | Symbol                           | Condition                                           | Min.  | Тур. | Max. | Unit | Measuring circuit |

|----------------------------------|----------------------------------|-----------------------------------------------------|-------|------|------|------|-------------------|

| Input current 1                  | IIH1                             | VIH1 = V <sub>DD</sub>                              | 0     | _    | 1    |      |                   |

| (RESET_N)<br>(TEST1_N)           | IIL1                             | VIL1 = V <sub>SS</sub>                              | -1500 | -300 | -20  |      |                   |

| Input current 2<br>(P00 to P05)* | IIH2                             | VIH2 = $V_{DD}$ (when pulled down)                  | 2     | 30   | 250  |      |                   |

| (P30 to P37)*<br>(P40 to P47)    | VIL2 = $V_{SS}$ (when pulled up) | -250                                                | -30   | -2   | μA   | 4    |                   |

| (P50 to P57)*<br>(P60 to P67)*   | IIH2Z                            | VIH2 = V <sub>DD</sub><br>(in high-impedance state) | _     | —    | 1    |      |                   |

| (P70 to P74)*<br>(P80 to P87)    | IIL2Z                            | VIL2 = V <sub>SS</sub><br>(in high-impedance state) | -1    | _    |      |      |                   |

#### FEDL620Q150A-01

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

## DC Characteristics (VIHL)

| $(V_{DD}$ =1.8 to 5.5V, $V_{SS}$ =0V, Ta=-40 to +105°C, unless otherwise specific                                                                                                                 |              |                                                   |                         |      |                         |      |                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------|-------------------------|------|-------------------------|------|----------------------|

| Parameter                                                                                                                                                                                         | Symbol       | Condition                                         | Min.                    | Тур. | Max.                    | Unit | Measuring<br>circuit |

| Input voltage 1<br>(RESET_N)<br>(P14/TEST0)<br>(TEST1_N)<br>(P00 to P05)*<br>(P12, P13)                                                                                                           | VIH1<br>VIL1 | —                                                 | 0.7×<br>V <sub>DD</sub> | _    | V <sub>DD</sub>         | V    | 5                    |

| (P30 to P37)*<br>(P40 to P47)<br>(P50 to P57)*<br>(P60 to P67)*<br>(P70 to P74)*<br>(P80 to P87)                                                                                                  |              | _                                                 | 0                       | _    | 0.3×<br>V <sub>DD</sub> |      |                      |

| Input pin capacitance<br>(RESET_N)<br>(P14/TEST0)<br>(TEST1_N)<br>(P00 to P05)*<br>(P12, P13)<br>(P30 to P37)*<br>(P40 to P47)<br>(P50 to P57)*<br>(P60 to P67)*<br>(P70 to P74)*<br>(P80 to P87) | CIN          | f = 10kHz<br>V <sub>rms</sub> = 50mV<br>Ta = 25°C |                         |      | 10                      | pF   | _                    |

\*: ML620Q15X have a different pin configuration for each package. See "LIST OF PINS" for more details.

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

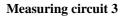

(\*2) Measured at the specified output pins.

## Measuring circuit 4

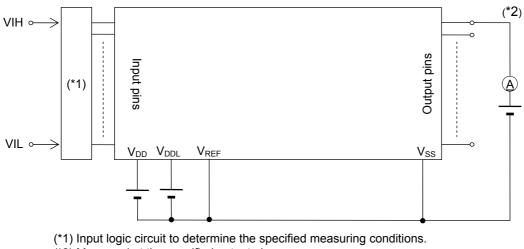

\*3: Measured at the specified input pins.

## ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

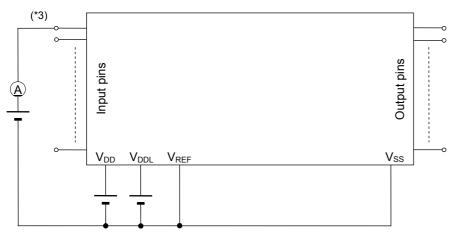

## Measuring circuit 5

\*1: Input logic circuit to determine the specified measuring conditions.

Unit

μS

### ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

#### (V<sub>DD</sub>=1.8 to 5.5V, V<sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise specified) Parameter Min. Symbol Condition Тур. Max. Interrupt: Enabled (MIE = 1), External interrupt disable 2.5× 3.5× $\mathsf{T}_{\mathsf{NUL}}$ \_\_\_\_ CPU: NOP operation LSCLK LSCLK period EXI0 to EXI7 (Rising-edge interrupt) $\mathbf{t}_{\mathsf{NUL}}$ EXI0 to EXI7 (Falling-edge interrupt) t<sub>NUL</sub> EXI0 to EXI7 (Both-edge interrupt) t<sub>NUL</sub>

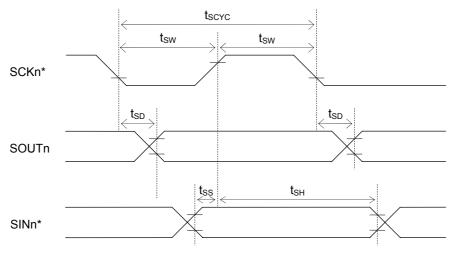

### **AC Characteristics (External Interrupt)**

| (V <sub>DD</sub> =1.8 to 5.5V, V <sub>SS</sub> =0V, Ta=-40 to +105°C, unless otherwise spec |                   |                                |                             |                             |                             |      |

|---------------------------------------------------------------------------------------------|-------------------|--------------------------------|-----------------------------|-----------------------------|-----------------------------|------|

| Parameter                                                                                   | Symbol            | Condition                      | Min.                        | Тур.                        | Max.                        | Unit |

| SCK input cycle                                                                             |                   | High-speed oscillation stopped | 10                          | —                           | —                           | μS   |

| (slave mode)                                                                                | tscyc             | During high-speed oscillation  | 500                         | —                           | —                           | ns   |

| SCK output cycle<br>(master mode)                                                           | t <sub>scyc</sub> | _                              | —                           | SCK <sup>(*1)</sup>         | —                           | sec  |

| SCK input pulse width                                                                       |                   | High-speed oscillation stopped | 4                           | _                           |                             | μS   |

| (slave mode)                                                                                | t <sub>sw</sub>   | During high-speed oscillation  | 200                         | —                           | —                           | ns   |

| SCK output pulse width (master mode)                                                        | t <sub>sw</sub>   | _                              | SCK <sup>(*1)</sup><br>×0.4 | SCK <sup>(*1)</sup><br>×0.5 | SCK <sup>(*1)</sup><br>×0.6 | sec  |

| SOUT output delay time (slave mode)                                                         | t <sub>SD</sub>   | _                              | _                           | —                           | 180                         | ns   |

| SOUT output delay time<br>(master mode)                                                     | t <sub>SD</sub>   | —                              | _                           | —                           | 80                          | ns   |

| SIN input setup time<br>(slave mode)                                                        | t <sub>ss</sub>   | _                              | 80                          | _                           | —                           | ns   |

| SIN input setup time<br>(Master mode)                                                       | t <sub>ss</sub>   | _                              | 240                         |                             |                             | ns   |

| SIN input hold time                                                                         | t <sub>SH</sub>   |                                | 80                          | —                           | —                           | ns   |

## AC Characteristics (Synchronous Serial Port)

\*1: Clock period selected by SnCK3–0 of the serial port n mode register (SIOnMOD1)

\*: Indicates the secondary function of the corresponding port.

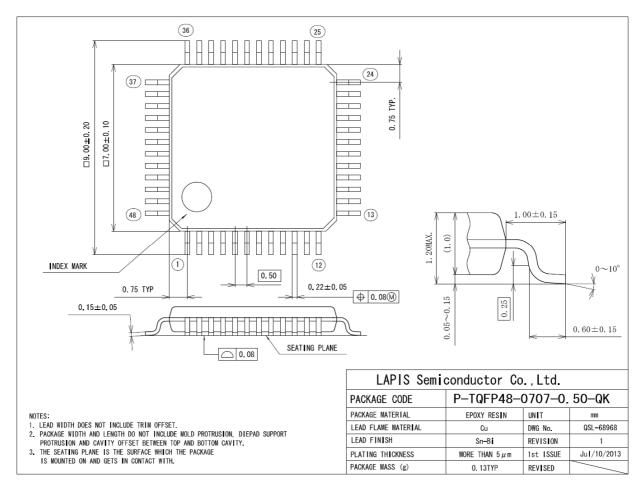

## PACKAGE DIMENSIONS

### ML620Q151A/ML620Q152A/ML620Q153A Package Dimension (48pin TQFP)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact a ROHM sales office for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

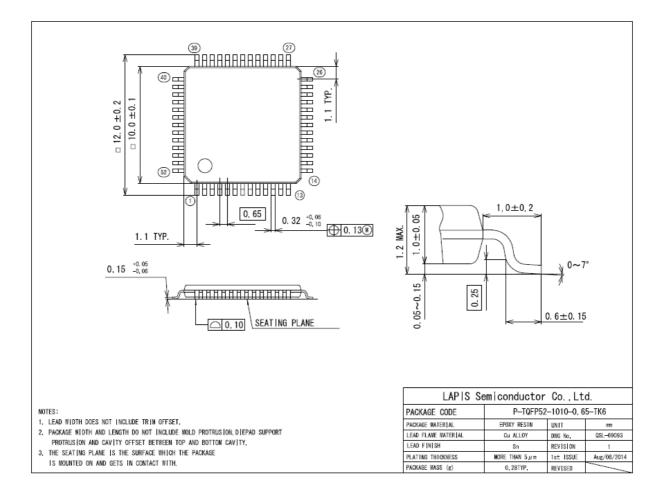

### ML620Q154A/ML620Q155A/ML620Q156A Package Dimension (52pin TQFP)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact a ROHM sales office for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### ML620Q151A/2A/3A/4A/5A/6A/7A/8A/9A

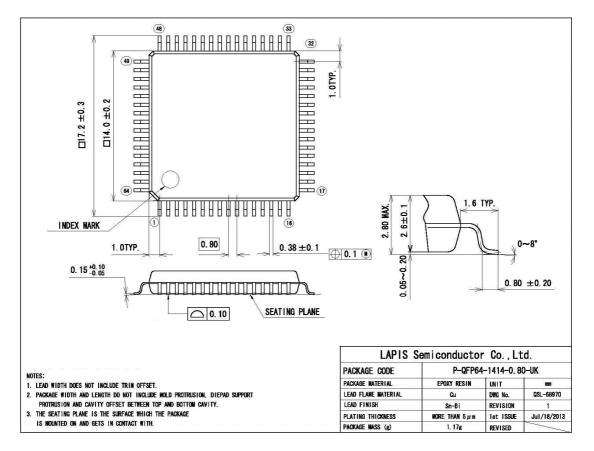

## ML620Q157A/ML620Q158A/ML620Q159A PACKAGE DIMENSION (64PIN TQFP)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact a ROHM sales office for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).