Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                           |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12dj256cpve |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 0-1  | Order Partnumber Example15                             |

|-------------|--------------------------------------------------------|

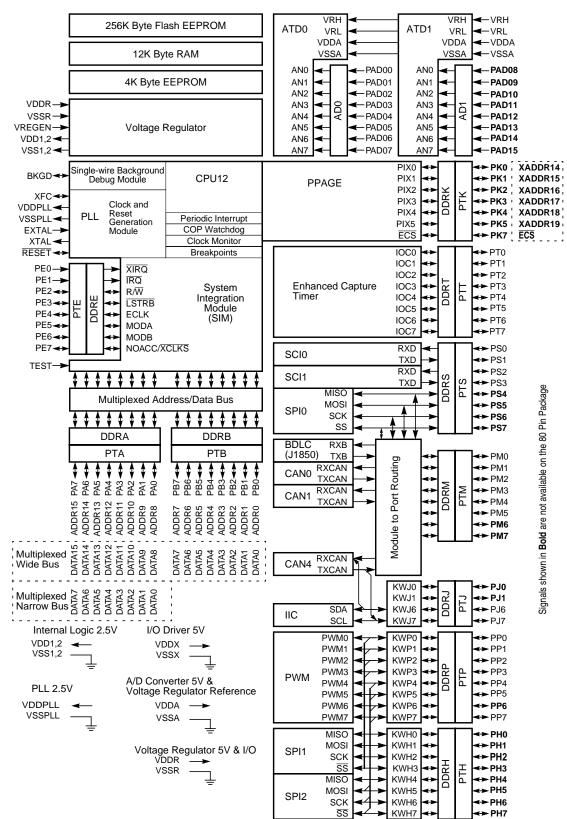

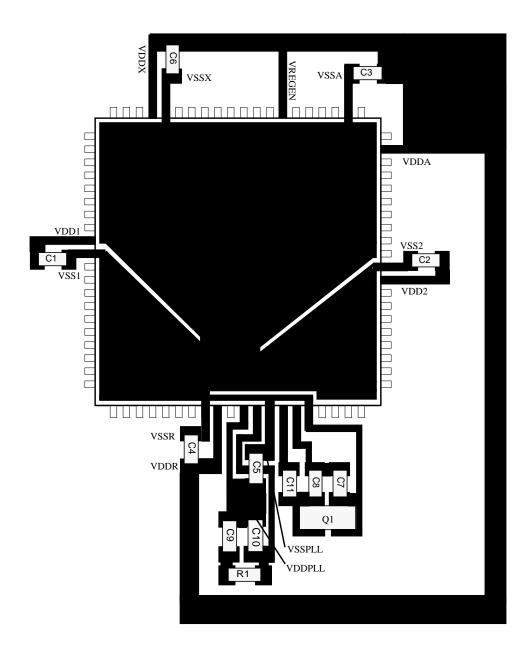

| Figure 1-1  | MC9S12DT256 Block Diagram                              |

| Figure 1-2  | MC9S12DT256 Memory Map                                 |

| Figure 2-1  | Pin Assignments in 112-pin LQFP52                      |

| Figure 2-2  | Pin Assignments in 80-pin QFP for MC9S12DJ25653        |

| Figure 2-3  | PLL Loop Filter Connections                            |

| Figure 2-4  | Colpitts Oscillator Connections (PE7=1)                |

| Figure 2-5  | Pierce Oscillator Connections (PE7=0)                  |

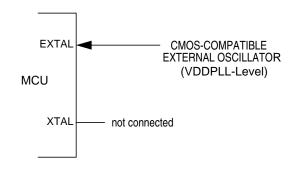

| Figure 2-6  | External Clock Connections (PE7=0)60                   |

| Figure 3-1  | Clock Connections                                      |

| Figure 20-1 | Recommended PCB Layout for 112LQFP Colpitts Oscillator |

| Figure 20-2 | Recommended PCB Layout for 80QFP Colpitts Oscillator   |

| Figure 20-3 | Recommended PCB Layout for 112LQFP Pierce Oscillator   |

| Figure 20-4 | Recommended PCB Layout for 80QFP Pierce Oscillator     |

| Figure A-1  | ATD Accuracy Definitions 102                           |

| Figure A-2  | Typical Endurance vs Temperature 107                   |

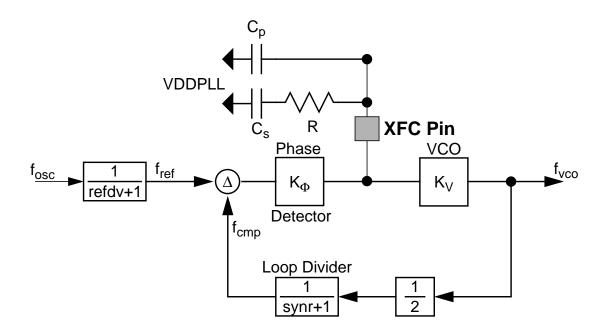

| Figure A-3  | Basic PLL functional diagram 113                       |

| Figure A-4  | Jitter Definitions                                     |

| Figure A-5  | Maximum bus clock jitter approximation 115             |

| Figure A-6  | SPI Master Timing (CPHA=0) 119                         |

| Figure A-7  | SPI Master Timing (CPHA=1) 120                         |

| Figure A-8  | SPI Slave Timing (CPHA=0) 121                          |

| Figure A-9  | SPI Slave Timing (CPHA=1) 122                          |

| Figure A-10 | General External Bus Timing 124                        |

| Figure B-1  | 112-pin LQFP mechanical dimensions (case no. 987) 128  |

| Figure B-2  | 80-pin QFP Mechanical Dimensions (case no. 841B) 129   |

#### Figure 1-1 MC9S12DT256 Block Diagram

\$00A0 - \$00C7

#### PWM (Pulse Width Modulator 8 Bit 8 Channel)

| Address              | Name     |                 | Bit 7      | Bit 6 | Bit 5        | Bit 4  | Bit 3 | Bit 2  | Bit 1       | Bit 0       |

|----------------------|----------|-----------------|------------|-------|--------------|--------|-------|--------|-------------|-------------|

| \$00B1               | PWMCNT5  | Read:           | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

|                      |          | Write:          | 0<br>Bit 7 | 0     | 0            | 0      | 0     | 0      | 0<br>1      | 0<br>Bit 0  |

| \$00B2               | PWMCNT6  | Read:<br>Write: | <u>оп</u>  | 0     | 0            | 4      | 0     | 0      | 0           | <u> </u>    |

| <b>*</b> ** <b>*</b> |          | Read:           | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B3               | PWMCNT7  | Write:          | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

| \$00B4               | PWMPER0  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B5               | PWMPER1  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B6               | PWMPER2  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B7               | PWMPER3  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B8               | PWMPER4  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B9               | PWMPER5  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BA               | PWMPER6  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BB               | PWMPER7  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BC               | PWMDTY0  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BD               | PWMDTY1  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BE               | PWMDTY2  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BF               | PWMDTY3  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C0               | PWMDTY4  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C1               | PWMDTY5  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C2               | PWMDTY6  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C3               | PWMDTY7  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C4               | PWMSDN   | Read:<br>Write: | PWMIF      | PWMIE | PWMRS<br>TRT | PWMLVL | 0     | PWM7IN | PWM7IN<br>L | PWM7E<br>NA |

| \$00C5               | Reserved | Read:<br>Write: | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

| \$00C6               | Reserved | Read:<br>Write: | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

| \$00C7               | Reserved | Read:<br>Write: | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

#### \$0240 - \$027F

PIM (Port Integration Module PIM\_9DP256)

| Address          | Name     |                 | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------------------|----------|-----------------|-------|--------|--------|--------|--------|--------|--------|--------|

| \$024D           | PPSS     | Read:<br>Write: | PPSS7 | PPSS6  | PPSS5  | PPSS4  | PPSS3  | PPSS2  | PPSS1  | PPSS0  |

| \$024E           | WOMS     | Read:<br>Write: | WOMS7 | WOMS6  | WOMS5  | WOMS4  | WOMS3  | WOMS2  | WOMS1  | WOMS0  |

| Ф004 <b>Г</b>    | Decembra | Read:           | 0     | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| \$024F           | Reserved | Write:          |       |        |        |        |        |        |        |        |

| \$0250           | PTM      | Read:<br>Write: | PTM7  | PTM6   | PTM5   | PTM4   | PTM3   | PTM2   | PTM1   | PTM0   |

| \$0251           | PTIM     | Read:           | PTIM7 | PTIM6  | PTIM5  | PTIM4  | PTIM3  | PTIM2  | PTIM1  | PTIM0  |

| <b>*</b> • - • · |          | Write:          |       |        |        |        |        |        |        |        |

| \$0252           | DDRM     | Read:<br>Write: | DDRM7 | DDRM7  | DDRM5  | DDRM4  | DDRM3  | DDRM2  | DDRM1  | DDRM0  |

| \$0253           | RDRM     | Read:<br>Write: | RDRM7 | RDRM6  | RDRM5  | RDRM4  | RDRM3  | RDRM2  | RDRM1  | RDRM0  |

| \$0254           | PERM     | Read:<br>Write: | PERM7 | PERM6  | PERM5  | PERM4  | PERM3  | PERM2  | PERM1  | PERM0  |

| \$0255           | PPSM     | Read:<br>Write: | PPSM7 | PPSM6  | PPSM5  | PPSM4  | PPSM3  | PPSM2  | PPSM1  | PPSM0  |

| \$0256           | WOMM     | Read:<br>Write: | WOMM7 | WOMM6  | WOMM5  | WOMM4  | WOMM3  | WOMM2  | WOMM1  | WOMM0  |

| \$0257           | MODRR    | Read:<br>Write: | 0     | MODRR6 | MODRR5 | MODRR4 | MODRR3 | MODRR2 | MODRR1 | MODRR0 |

| \$0258           | PTP      | Read:<br>Write: | PTP7  | PTP6   | PTP5   | PTP4   | PTP3   | PTP2   | PTP1   | PTP0   |

| \$0259           | PTIP     | Read:           | PTIP7 | PTIP6  | PTIP5  | PTIP4  | PTIP3  | PTIP2  | PTIP1  | PTIP0  |

| <b>4</b> 0209    | PHP      | Write:          |       |        |        |        |        |        |        |        |

| \$025A           | DDRP     | Read:<br>Write: | DDRP7 | DDRP7  | DDRP5  | DDRP4  | DDRP3  | DDRP2  | DDRP1  | DDRP0  |

| \$025B           | RDRP     | Read:<br>Write: | RDRP7 | RDRP6  | RDRP5  | RDRP4  | RDRP3  | RDRP2  | RDRP1  | RDRP0  |

| \$025C           | PERP     | Read:<br>Write: | PERP7 | PERP6  | PERP5  | PERP4  | PERP3  | PERP2  | PERP1  | PERP0  |

| \$025D           | PPSP     | Read:<br>Write: | PPSP7 | PPSP6  | PPSP5  | PPSP4  | PPSP3  | PPSP2  | PPSP1  | PPSS0  |

| \$025E           | PIEP     | Read:<br>Write: | PIEP7 | PIEP6  | PIEP5  | PIEP4  | PIEP3  | PIEP2  | PIEP1  | PIEP0  |

| \$025F           | PIFP     | Read:<br>Write: | PIFP7 | PIFP6  | PIFP5  | PIFP4  | PIFP3  | PIFP2  | PIFP1  | PIFP0  |

| \$0260           | PTH      | Read:<br>Write: | PTH7  | PTH6   | PTH5   | PTH4   | PTH3   | PTH2   | PTH1   | PTH0   |

| \$0261           | טידס     | Read:           | PTIH7 | PTIH6  | PTIH5  | PTIH4  | PTIH3  | PTIH2  | PTIH1  | PTIH0  |

| \$0261           | PTIH     | Write:          |       |        |        |        |        |        |        |        |

| \$0262           | DDRH     | Read:<br>Write: | DDRH7 | DDRH7  | DDRH5  | DDRH4  | DDRH3  | DDRH2  | DDRH1  | DDRH0  |

| \$0263           | RDRH     | Read:<br>Write: | RDRH7 | RDRH6  | RDRH5  | RDRH4  | RDRH3  | RDRH2  | RDRH1  | RDRH0  |

| \$0264           | PERH     | Read:<br>Write: | PERH7 | PERH6  | PERH5  | PERH4  | PERH3  | PERH2  | PERH1  | PERH0  |

| \$0265           | PPSH     | Read:<br>Write: | PPSH7 | PPSH6  | PPSH5  | PPSH4  | PPSH3  | PPSH2  | PPSH1  | PPSH0  |

\$02C0 - \$03FF

**Reserved space**

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$02C0   | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| - \$03FF |          | Write: |       |       |       |       |       |       |       |       |

# 1.7 Part ID Assignments

The part ID is located in two 8-bit registers PARTIDH and PARTIDL (addresses \$001A and \$001B after reset). The read-only value is a unique part ID for each revision of the chip. **Table 1-3** shows the assigned part ID number.

| Device      | Mask Set Number | Part ID <sup>1</sup> |

|-------------|-----------------|----------------------|

| MC9S12DT256 | 0L91N           | \$0030               |

| MC9S12DT256 | 1L91N           | \$0031               |

| MC9S12DT256 | 3L91N           | \$0032               |

| MC9S12DT256 | 4L91N           | \$0034               |

| MC9S12DT256 | 0L01Y           | \$0033               |

#### Table 1-3 Assigned Part ID Numbers

NOTES:

1. The coding is as follows:

Bit 15-12: Major family identifier

Bit 11-8: Minor family identifier

Bit 7-4: Major mask set revision number including FAB transfers Bit 3-0: Minor - non full - mask set revision

The device memory sizes are located in two 8-bit registers MEMSIZ0 and MEMSIZ1 (addresses \$001C and \$001D after reset). **Table 1-4** shows the read-only values of these registers. Refer to section Module Mapping and Control (MMC) of HCS12 Core User Guide for further details.

#### Table 1-4 Memory size registers

| Register name | Value |

|---------------|-------|

| MEMSIZ0       | \$25  |

| MEMSIZ1       | \$81  |

#### 2.3.14 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low.

#### 2.3.15 PE5 / MODA / IPIPE0 — Port E I/O Pin 5

PE5 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODA bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE0. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low.

## 2.3.16 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference.

## 2.3.17 PE3 / LSTRB / TAGLO — Port E I/O Pin 3

PE3 is a general purpose input or output pin. In MCU expanded modes of operation,  $\overline{\text{LSTRB}}$  can be used for the low-byte strobe function to indicate the type of bus access and when instruction tagging is on,  $\overline{\text{TAGLO}}$  is used to tag the low half of the instruction word being read into the instruction queue.

# 2.3.26 PH2 / KWH2 / SCK1 — Port H I/O Pin 2

PH2 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as serial clock pin SCK of the Serial Peripheral Interface 1 (SPI1).

## 2.3.27 PH1 / KWH1 / MOSI1 — Port H I/O Pin 1

PH1 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as master output (during master mode) or slave input pin (during slave mode) MOSI of the Serial Peripheral Interface 1 (SPI1).

## 2.3.28 PH0 / KWH0 / MISO1 — Port H I/O Pin 0

PH0 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as master input (during master mode) or slave output (during slave mode) pin MISO of the Serial Peripheral Interface 1 (SPI1).

## 2.3.29 PJ7 / KWJ7 / TXCAN4 / SCL - PORT J I/O Pin 7

PJ7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the transmit pin TXCAN for the Motorola Scalable Controller Area Network controller 4 (CAN4) or the serial clock pin SCL of the IIC module.

## 2.3.30 PJ6 / KWJ6 / RXCAN4 / SDA — PORT J I/O Pin 6

PJ6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the receive pin RXCAN for the Motorola Scalable Controller Area Network controller 4 (CAN4) or the serial data pin SDA of the IIC module.

## 2.3.31 PJ[1:0] / KWJ[1:0] — Port J I/O Pins [1:0]

PJ1 and PJ0 are general purpose input or output pins. They can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode .

## 2.3.32 PK7 / ECS / ROMONE — Port K I/O Pin 7

PK7 is a general purpose input or output pin. During MCU expanded modes of operation, this pin is used as the emulation chip select output ( $\overline{\text{ECS}}$ ). During MCU normal expanded wide and narrow modes of operation, this pin is used to enable the Flash EEPROM memory in the memory map (ROMONE). At the rising edge of  $\overline{\text{RESET}}$ , the state of this pin is latched to the ROMON bit.

# Section 4 Modes of Operation

# 4.1 Overview

Eight possible modes determine the operating configuration of the MC9S12DT256. Each mode has an associated default memory map and external bus configuration controlled by a further pin.

Three low power modes exist for the device.

# 4.2 Chip Configuration Summary

The operating mode out of reset is determined by the states of the MODC, MODB, and MODA pins during reset (**Table 4-1**). The MODC, MODB, and MODA bits in the MODE register show the current operating mode and provide limited mode switching during operation. The states of the MODC, MODB, and MODA pins are latched into these bits on the rising edge of the reset signal. The ROMCTL signal allows the setting of the ROMON bit in the MISC register thus controlling whether the internal Flash is visible in the memory map. ROMON = 1 mean the Flash is visible in the memory map. The state of the ROMCTL pin is latched into the ROMON bit in the MISC register on the rising edge of the reset signal.

| BKGD =<br>MODC | PE6 =<br>MODB | PE5 =<br>MODA | PK7 =<br>ROMCTL | ROMON<br>Bit | Mode Description                                                                                                                    |  |

|----------------|---------------|---------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| 0              | 0             | 0             | х               | 1            | Special Single Chip, BDM allowed and ACTIVE. BDM is allowed in all other modes but a serial command is required to make BDM active. |  |

| 0              | 0             | 1             | 0               | 1            | Emulation Expanded Narrow, RDM allowed                                                                                              |  |

| 0              | 0             | I             | 1               | 0            | Emulation Expanded Narrow, BDM allowed                                                                                              |  |

| 0              | 1             | 0             | Х               | 0            | Special Test (Expanded Wide), BDM allowed                                                                                           |  |

| 0              | 1             | 1             | 0               | 1            | Emulation Expanded Wide PDM allowed                                                                                                 |  |

| 0              | I             | I             | 1               | 0            | Emulation Expanded Wide, BDM allowed                                                                                                |  |

| 1              | 0             | 0             | Х               | 1            | Normal Single Chip, BDM allowed                                                                                                     |  |

| 1              | 0             | 1             | 0               | 0            | Normal Expanded Narrow DDM allowed                                                                                                  |  |

|                | 0             | I             | 1               | 1            | Normal Expanded Narrow, BDM allowed                                                                                                 |  |

| 1              | 1             | 0             | Х               | 1            | Peripheral; BDM allowed but bus operations would cause bus conflicts (must not be used)                                             |  |

|                |               |               | 0               | 0            |                                                                                                                                     |  |

| 1              | 1             | 1             | 1               | 1            | Normal Expanded Wide, BDM allowed                                                                                                   |  |

#### Table 4-1 Mode Selection

For further explanation on the modes refer to the Core User Guide.

#### Table 4-2 Clock Selection Based on PE7

| PE7 = XCLKS | Description                  |

|-------------|------------------------------|

| 1           | Colpitts Oscillator selected |

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD5}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD5}$ ) is greater than  $I_{DD5}$ , the injection current may flow out of VDD5 and could result in external power supply going out of regulation. Ensure external VDD5 load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g. if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

#### A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS5}$  or  $V_{DD5}$ ).

| Num | Rating                                                                                  | Symbol                           | Min   | Max  | Unit |

|-----|-----------------------------------------------------------------------------------------|----------------------------------|-------|------|------|

| 1   | I/O, Regulator and Analog Supply Voltage                                                | V <sub>DD5</sub>                 | -0.3  | 6.0  | V    |

| 2   | Digital Logic Supply Voltage <sup>2</sup>                                               | V <sub>DD</sub>                  | -0.3  | 3.0  | V    |

| 3   | PLL Supply Voltage <sup>2</sup>                                                         | V <sub>DDPLL</sub>               | -0.3  | 3.0  | V    |

| 4   | Voltage difference VDDX to VDDR and VDDA                                                | $\Delta_{VDDX}$                  | -0.3  | 0.3  | V    |

| 5   | Voltage difference VSSX to VSSR and VSSA                                                | Δ <sub>VSSX</sub>                | -0.3  | 0.3  | V    |

| 6   | Digital I/O Input Voltage                                                               | V <sub>IN</sub>                  | -0.3  | 6.0  | V    |

| 7   | Analog Reference                                                                        | V <sub>RH,</sub> V <sub>RL</sub> | -0.3  | 6.0  | V    |

| 8   | XFC, EXTAL, XTAL inputs                                                                 | V <sub>ILV</sub>                 | -0.3  | 3.0  | V    |

| 9   | TEST input                                                                              | V <sub>TEST</sub>                | -0.3  | 10.0 | V    |

| 10  | Instantaneous Maximum Current<br>Single pin limit for all digital I/O pins <sup>3</sup> | I <sub>D</sub>                   | -25   | +25  | mA   |

| 11  | Instantaneous Maximum Current<br>Single pin limit for XFC, EXTAL, XTAL <sup>4</sup>     | I <sub>DL</sub>                  | -25   | +25  | mA   |

| 12  | Instantaneous Maximum Current<br>Single pin limit for TEST <sup>5</sup>                 | I <sub>DT</sub>                  | -0.25 | 0    | mA   |

| 13  | Storage Temperature Range                                                               | T <sub>stg</sub>                 | - 65  | 155  | °C   |

| gs <sup>1</sup> |

|-----------------|

| 1               |

NOTES:

1. Beyond absolute maximum ratings device might be damaged.

- 2. The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply.

- The absolute maximum ratings apply when the device is powered from an external source.

- 3. All digital I/O pins are internally clamped to V<sub>SSX</sub> and V<sub>DDX</sub>, V<sub>SSR</sub> and V<sub>DDR</sub> or V<sub>SSA</sub> and V<sub>DDA</sub>.

- 4. Those pins are internally clamped to  $V_{SSPLL}$  and  $V_{DDPLL}$ . 5. This pin is clamped low to  $V_{SSR}$ , but not clamped high. This pin must be tied low in applications.

# A.1.6 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 Stress test qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model.

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model      | Description                                     | Symbol | Value       | Unit |

|------------|-------------------------------------------------|--------|-------------|------|

|            | Series Resistance                               | R1     | 1500        | Ohm  |

|            | Storage Capacitance                             | С      | 100         | pF   |

| Human Body | Number of Pulse per pin<br>positive<br>negative | -      | -<br>3<br>3 |      |

|            | Series Resistance                               | R1     | 0           | Ohm  |

|            | Storage Capacitance                             | С      | 200         | pF   |

| Machine    | Number of Pulse per pin<br>positive<br>negative | -      | -<br>3<br>3 |      |

| Latch-up   | Minimum input voltage limit                     |        | -2.5        | V    |

|            | Maximum input voltage limit                     |        | 7.5         | V    |

Table A-2 ESD and Latch-up Test Conditions

| Num | С | Rating                                                             | Symbol           | Min          | Max | Unit |

|-----|---|--------------------------------------------------------------------|------------------|--------------|-----|------|

| 1   | С | Human Body Model (HBM)                                             | V <sub>HBM</sub> | 2000         | -   | V    |

| 2   | С | Machine Model (MM)                                                 | V <sub>MM</sub>  | 200          | -   | V    |

| 3   | С | Charge Device Model (CDM)                                          | V <sub>CDM</sub> | 500          | -   | V    |

| 4   | с | Latch-up Current at T <sub>A</sub> = 125°C<br>positive<br>negative | I <sub>LAT</sub> | +100<br>-100 | -   | mA   |

| 5   | с | Latch-up Current at T <sub>A</sub> = 27°C<br>positive<br>negative  | I <sub>LAT</sub> | +200<br>-200 | -   | mA   |

## A.2.3 ATD accuracy

**Table A-10** specifies the ATD conversion performance excluding any errors due to current injection, input capacitance and source resistance.

| V <sub>REF</sub> = | = V <sub>F</sub> | s are shown in <b>Table A-4</b> unless otherwise noted<br>$_{RH}$ - V <sub>RL</sub> = 5.12V. Resulting to one 8 bit count = 20mV a<br>= 2.0MHz | and one 10 bi | t count = 5m\ | 1    |     |        |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------|-----|--------|

| Num                | С                | Rating                                                                                                                                         | Symbol        | Min           | Тур  | Max | Unit   |

| 1                  | Ρ                | 10-Bit Resolution                                                                                                                              | LSB           |               | 5    |     | mV     |

| 2                  | Ρ                | 10-Bit Differential Nonlinearity                                                                                                               | DNL           | -1            |      | 1   | Counts |

| 3                  | Ρ                | 10-Bit Integral Nonlinearity                                                                                                                   | INL           | -2.5          | ±1.5 | 2.5 | Counts |

| 4                  | Ρ                | 10-Bit Absolute Error <sup>1</sup>                                                                                                             | AE            | -3            | ±2.0 | 3   | Counts |

| 5                  | Ρ                | 8-Bit Resolution                                                                                                                               | LSB           |               | 20   |     | mV     |

| 6                  | Ρ                | 8-Bit Differential Nonlinearity                                                                                                                | DNL           | -0.5          |      | 0.5 | Counts |

| 7                  | Ρ                | 8-Bit Integral Nonlinearity                                                                                                                    | INL           | -1.0          | ±0.5 | 1.0 | Counts |

| 8                  | Ρ                | 8-Bit Absolute Error <sup>1</sup>                                                                                                              | AE            | -1.5          | ±1.0 | 1.5 | Counts |

#### Table A-10 ATD Conversion Performance

NOTES:

1. These values include the quantization error which is inherently 1/2 count for any A/D converter.

For the following definitions see also Figure A-1.

Differential Non-Linearity (DNL) is defined as the difference between two adjacent switching steps.

$$\mathsf{DNL}(i) = \frac{\mathsf{V}_i - \mathsf{V}_{i-1}}{\mathsf{1LSB}} - \mathsf{1}$$

The Integral Non-Linearity (INL) is defined as the sum of all DNLs:

$$INL(n) = \sum_{i=1}^{n} DNL(i) = \frac{V_n - V_0}{1LSB} - n$$

MC9S12DT256 Device User Guide V03.07

## A.5.3 Phase Locked Loop

The oscillator provides the reference clock for the PLL. The PLL's Voltage Controlled Oscillator (VCO) is also the system clock source in self clock mode.

#### A.5.3.1 XFC Component Selection

This section describes the selection of the XFC components to achieve a good filter characteristics.

Figure A-3 Basic PLL functional diagram

The following procedure can be used to calculate the resistance and capacitance values using typical values for  $K_1$ ,  $f_1$  and  $i_{ch}$  from **Table A-16**.

The grey boxes show the calculation for  $f_{VCO} = 50$ MHz and  $f_{ref} = 1$ MHz. E.g., these frequencies are used for  $f_{OSC} = 4$ MHz and a 25MHz bus clock.

The VCO Gain at the desired VCO frequency is approximated by:

$$K_{V} = K_{1} \cdot e^{\frac{(f_{1} - f_{vco})}{K_{1} \cdot 1V}} = -100 \cdot e^{\frac{(60 - 50)}{-100}} = -90.48 MHz/V$$

The phase detector relationship is given by:

$$K_{\Phi} = -|i_{ch}| \cdot K_{V} = 316.7 \text{Hz}/\Omega$$

i<sub>ch</sub> is the current in tracking mode.

| Num | С | Rating                                                                                       | Symbol            | Min | Тур | Max  | Unit |

|-----|---|----------------------------------------------------------------------------------------------|-------------------|-----|-----|------|------|

| 1   | Р | Frequency of operation (E-clock)                                                             | f <sub>o</sub>    | 0   |     | 25.0 | MHz  |

| 2   | Р | Cycle time                                                                                   | t <sub>cyc</sub>  | 40  |     |      | ns   |

| 3   | D | Pulse width, E low                                                                           | PW <sub>EL</sub>  | 19  |     |      | ns   |

| 4   | D | Pulse width, E high <sup>1</sup>                                                             | PW <sub>EH</sub>  | 19  |     |      | ns   |

| 5   | D | Address delay time                                                                           | t <sub>AD</sub>   |     |     | 8    | ns   |

| 6   | D | Address valid time to E rise $(PW_{EL}-t_{AD})$                                              | t <sub>AV</sub>   | 11  |     |      | ns   |

| 7   | D | Muxed address hold time                                                                      | t <sub>MAH</sub>  | 2   |     |      | ns   |

| 8   | D | Address hold to data valid                                                                   | t <sub>AHDS</sub> | 7   |     |      | ns   |

| 9   | D | Data hold to address                                                                         | t <sub>DHA</sub>  | 2   |     |      | ns   |

| 10  | D | Read data setup time                                                                         | t <sub>DSR</sub>  | 13  |     |      | ns   |

| 11  | D | Read data hold time                                                                          | t <sub>DHR</sub>  | 0   |     |      | ns   |

| 12  | D | Write data delay time                                                                        | t <sub>DDW</sub>  |     |     | 7    | ns   |

| 13  | D | Write data hold time                                                                         | t <sub>DHW</sub>  | 2   |     |      | ns   |

| 14  | D | Write data setup time <sup>1</sup> (PW <sub>EH</sub> -t <sub>DDW</sub> )                     | t <sub>DSW</sub>  | 12  |     |      | ns   |

| 15  | D | Address access time <sup>1</sup> (t <sub>cyc</sub> -t <sub>AD</sub> -t <sub>DSR</sub> )      | t <sub>ACCA</sub> | 19  |     |      | ns   |

| 16  | D | E high access time <sup>1</sup> (PW <sub>EH</sub> -t <sub>DSR</sub> )                        | t <sub>ACCE</sub> | 6   |     |      | ns   |

| 17  | D | Non-multiplexed address delay time                                                           | t <sub>NAD</sub>  |     |     | 6    | ns   |

| 18  | D | Non-muxed address valid to E rise (PW <sub>EL</sub> -t <sub>NAD</sub> )                      | t <sub>NAV</sub>  | 15  |     |      | ns   |

| 19  | D | Non-multiplexed address hold time                                                            | t <sub>NAH</sub>  | 2   |     |      | ns   |

| 20  | D | Chip select delay time                                                                       | t <sub>CSD</sub>  |     |     | 16   | ns   |

| 21  | D | Chip select access time <sup>1</sup> (t <sub>cyc</sub> -t <sub>CSD</sub> -t <sub>DSR</sub> ) | t <sub>ACCS</sub> | 11  |     |      | ns   |

| 22  | D | Chip select hold time                                                                        | t <sub>CSH</sub>  | 2   |     |      | ns   |

| 23  | D | Chip select negated time                                                                     | t <sub>CSN</sub>  | 8   |     |      | ns   |

| 24  | D | Read/write delay time                                                                        | t <sub>RWD</sub>  |     |     | 7    | ns   |

| 25  | D | Read/write valid time to E rise ( $PW_{EL}$ -t <sub>RWD</sub> )                              | t <sub>RWV</sub>  | 14  |     |      | ns   |

| 26  | D | Read/write hold time                                                                         | t <sub>RWH</sub>  | 2   |     |      | ns   |

| 27  | D | Low strobe delay time                                                                        | t <sub>LSD</sub>  |     |     | 7    | ns   |

| 28  | D | Low strobe valid time to E rise ( $PW_{EL}$ - $t_{LSD}$ )                                    | t <sub>LSV</sub>  | 14  |     |      | ns   |

| 29  | D | Low strobe hold time                                                                         | t <sub>LSH</sub>  | 2   |     |      | ns   |

| 30  | D | NOACC strobe delay time                                                                      | t <sub>NOD</sub>  |     |     | 7    | ns   |

| 31  | D | NOACC valid time to E rise (PW <sub>EL</sub> -t <sub>NOD</sub> )                             | t <sub>NOV</sub>  | 14  |     |      | ns   |

## Table A-21 Expanded Bus Timing Characteristics

# **User Guide End Sheet**

# FINAL PAGE OF 132 PAGES