Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 59                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                           |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-QFP                                                                  |

| Supplier Device Package    | 80-QFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12dt256vfue |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6.1   | CPU12 Block Description                                           | 79 |

|-------|-------------------------------------------------------------------|----|

| 6.2   | HCS12 Module Mapping Control (MMC) Block Description              | 79 |

| 6.2.1 | Device specific information                                       | 79 |

| 6.3   | HCS12 Multiplexed External Bus Interface (MEBI) Block Description | 79 |

| 6.3.1 | Device specific information                                       | 79 |

| 6.4   | HCS12 Interrupt (INT) Block description                           | 79 |

| 6.5   | HCS12 Background Debug (BDM) Block Description                    | 79 |

| 6.6   | HCS12 Breakpoint (BKP) Block Description                          | 80 |

|       |                                                                   |    |

## Section 7 Clock and Reset Generator (CRG) Block Description

| 7.1   | Device-specific information. | 80 |

|-------|------------------------------|----|

| 7.1.1 | XCLKS                        | 80 |

Section 8 Enhanced Capture Timer (ECT) Block Description

Section 9 Analog to Digital Converter (ATD) Block Description

Section 10 Inter-IC Bus (IIC) Block Description

Section 11 Serial Communications Interface (SCI) Block Description

Section 12 Serial Peripheral Interface (SPI) Block Description

Section 13 J1850 (BDLC) Block Description

Section 14 Pulse Width Modulator (PWM) Block Description

Section 15 Flash EEPROM 256K Block Description

Section 16 EEPROM 4K Block Description

Section 17 RAM Block Description

Section 18 MSCAN Block Description

Section 19 Port Integration Module (PIM) Block Description

Section 20 Voltage Regulator (VREG) Block Description

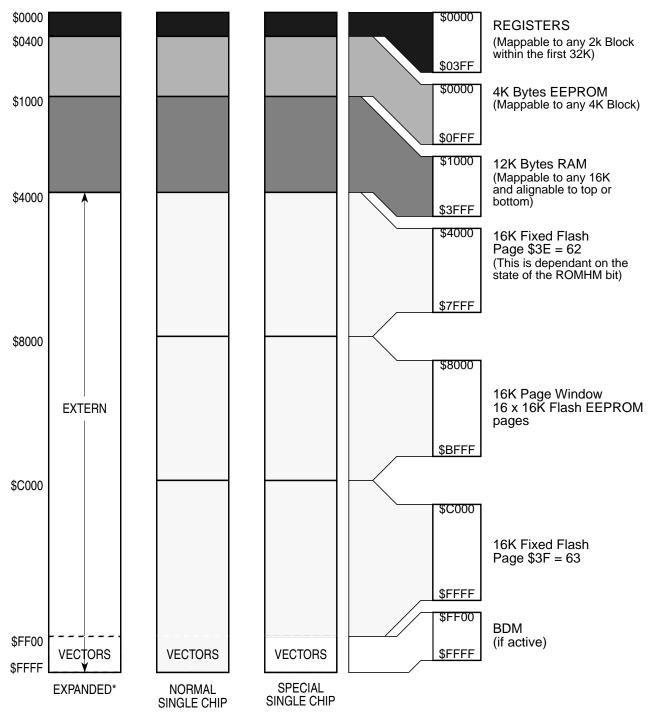

Figure 1-2 MC9S12DT256 Memory Map

\* Assuming that a '0' was driven onto port K bit 7 during MCU is reset into normal expanded wide or narrow mode.

## 1.6 Detailed Register Map

The following tables show the detailed register map of the MC9S12DT256.

```

$0000 - $000F

```

#### MEBI map 1 of 3 (Core User Guide)

| Address | Name     | Г               | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0000  | PORTA    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0001  | PORTB    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0002  | DDRA     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0003  | DDRB     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0004  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0005  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0006  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0007  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0008  | PORTE    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | Bit 1 | Bit 0 |

| \$0009  | DDRE     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | Bit 2 | 0     | 0     |

| \$000A  | PEAR     | Read:<br>Write: | NOACCE | 0     | PIPOE | NECLK | LSTRE | RDWE  | 0     | 0     |

| \$000B  | MODE     | Read:<br>Write: | MODC   | MODB  | MODA  | 0     | IVIS  | 0     | EMK   | EME   |

| \$000C  | PUCR     | Read:<br>Write: | PUPKE  | 0     | 0     | PUPEE | 0     | 0     | PUPBE | PUPAE |

| \$000D  | RDRIV    | Read:<br>Write: | RDPK   | 0     | 0     | RDPE  | 0     | 0     | RDPB  | RDPA  |

| \$000E  | EBICTL   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | ESTR  |

| \$000F  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### \$0010 - \$0014

#### MMC map 1 of 4 (Core User Guide)

| Address | Name   |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|

| \$0010  | INITRM | Read:  | RAM15 | RAM14 | RAM13 | RAM12 | RAM11 | 0     | 0     | RAMHAL |

| \$0010  |        | Write: |       |       |       |       |       |       |       |        |

| \$0011  |        | Read:  | 0     | REG14 | REG13 | REG12 | REG11 | 0     | 0     | 0      |

| \$0011  | INITRG | Write: |       | REG14 | REGIS | REGIZ | REGII |       |       |        |

\$00A0 - \$00C7

#### PWM (Pulse Width Modulator 8 Bit 8 Channel)

| Address              | Name     |                 | Bit 7      | Bit 6 | Bit 5        | Bit 4  | Bit 3 | Bit 2  | Bit 1       | Bit 0       |

|----------------------|----------|-----------------|------------|-------|--------------|--------|-------|--------|-------------|-------------|

| \$00B1               | PWMCNT5  | Read:           | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

|                      |          | Write:          | 0<br>Bit 7 | 0     | 0            | 0      | 0     | 0      | 0<br>1      | 0<br>Bit 0  |

| \$00B2               | PWMCNT6  | Read:<br>Write: | <u>оп</u>  | 0     | 0            | 4      | 0     | 0      | 0           | <u> </u>    |

| <b>*</b> ** <b>*</b> |          | Read:           | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B3               | PWMCNT7  | Write:          | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

| \$00B4               | PWMPER0  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B5               | PWMPER1  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B6               | PWMPER2  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B7               | PWMPER3  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B8               | PWMPER4  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00B9               | PWMPER5  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BA               | PWMPER6  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BB               | PWMPER7  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BC               | PWMDTY0  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BD               | PWMDTY1  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BE               | PWMDTY2  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00BF               | PWMDTY3  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C0               | PWMDTY4  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C1               | PWMDTY5  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C2               | PWMDTY6  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C3               | PWMDTY7  | Read:<br>Write: | Bit 7      | 6     | 5            | 4      | 3     | 2      | 1           | Bit 0       |

| \$00C4               | PWMSDN   | Read:<br>Write: | PWMIF      | PWMIE | PWMRS<br>TRT | PWMLVL | 0     | PWM7IN | PWM7IN<br>L | PWM7E<br>NA |

| \$00C5               | Reserved | Read:<br>Write: | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

| \$00C6               | Reserved | Read:<br>Write: | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

| \$00C7               | Reserved | Read:<br>Write: | 0          | 0     | 0            | 0      | 0     | 0      | 0           | 0           |

#### \$00D8 - \$00DF

#### **SPI0 (Serial Peripheral Interface)**

| Address     | Name     | [               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$00DC      | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             |          | Write:          |       |       |       |       |       |       |       |       |

| \$00DD      | SPI0DR   | Read:<br>Write: | Bit7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit0  |

| \$00DE      | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| <b>AUDE</b> | Reserved | Write:          |       |       |       |       |       |       |       |       |

| \$00DF      | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             |          | Write:          |       |       |       |       |       |       |       |       |

#### \$00E0 - \$00E7

## IIC (Inter IC Bus)

| Address | Name     |                 | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|---------|----------|-----------------|-------|-------|---------|-------|-------|-------|-------|--------|

| \$00E0  | IBAD     | Read:<br>Write: | ADR7  | ADR6  | ADR5    | ADR4  | ADR3  | ADR2  | ADR1  | 0      |

| \$00E1  | IBFD     | Read:<br>Write: | IBC7  | IBC6  | IBC5    | IBC4  | IBC3  | IBC2  | IBC1  | IBC0   |

| \$00E2  | IBCR     | Read:           | IBEN  | IBIE  | MS/SL   | TX/RX | ТХАК  | 0     | 0     | IBSWAI |

| 900EZ   | IDUK     | Write:          | IDEIN | IDIE  | IVIO/OL |       | IAAN  | RSTA  |       | IDSWAI |

| \$00E3  |          | Read:           | TCF   | IAAS  | IBB     | IBAL  | 0     | SRW   | IBIF  | RXAK   |

| \$00E3  | IBSR     | Write:          |       |       |         | IDAL  |       |       | IDIF  |        |

| \$00E4  | IBDR     | Read:<br>Write: | D7    | D6    | D5      | D4    | D3    | D2    | D1    | D 0    |

| \$00E5  | Reserved | Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0      |

| \$00E2  | Reserved | Write:          |       |       |         |       |       |       |       |        |

| \$00E6  | Deserved | Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0      |

| Φυυεο   | Reserved | Write:          |       |       |         |       |       |       |       |        |

| ¢00E7   | Reserved | Read:           | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0      |

| \$00E7  |          | Write:          |       |       |         |       |       |       |       |        |

#### \$00E8 - \$00EF

#### **BDLC (Bytelevel Data Link Controller J1850)**

|               |          |        | D:: 7    | Dito  | D'' C  | <b>D</b> '' 4 | Dit o | D'L O | <b>D</b> '( 4 | D'L O  |

|---------------|----------|--------|----------|-------|--------|---------------|-------|-------|---------------|--------|

| Address       | Name     |        | Bit 7    | Bit 6 | Bit 5  | Bit 4         | Bit 3 | Bit 2 | Bit 1         | Bit 0  |

| \$00E8        | DLCBCR1  | Read:  | IMSG     | CLKS  | 0      | 0             | 0     | 0     | IE            | WCM    |

| <b>Φ</b> 00⊏ο | DLCDCRI  | Write: | INISG    | ULK3  |        |               |       |       | IC            |        |

| \$00E9        | DLCBSVR  | Read:  | 0        | 0     | 13     | 12            | l1    | 10    | 0             | 0      |

| Φ00L9         | DLCDOVK  | Write: |          |       |        |               |       |       |               |        |

| \$00EA        | DLCBCR2  | Read:  | SMRST    | DLOOP | RX4XE  | NBFS          | TEOD  | TSIFR | TMIFR1        | TMIFR0 |

| <b>JUULA</b>  | DLCBCKZ  | Write: | 51011151 | DLOOI | INA4AL |               | TLOD  |       |               |        |

| ¢00EB         | DLCBDR   | Read:  | D7       | D6    | D5     | D4            | D3    | D2    | D1            | D0     |

| \$00EB        | DLCDDK   | Write: | DI       | DO    | 05     | 04            | 03    | DZ    |               | 00     |

| \$00EC        | DLCBARD  | Read:  | 0        | RXPOL | 0      | 0             | BO3   | BO2   | BO1           | BO0    |

| φUUEC         | DLCBARD  | Write: |          | KAFUL |        |               | B03   | BUZ   | БОТ           | воо    |

| \$00ED        | DLCBRSR  | Read:  | 0        | 0     | R5     | R4            | R3    | R2    | R1            | R0     |

| ΦUUED         | DLCDRSR  | Write: |          |       | КJ     | Κ4            | КJ    | RΖ    | КI            | RU     |

| ¢OOEE         |          | Read:  | 0        | 0     | 0      | BDLCE         | 0     | 0     | 0             | 0      |

| \$00EE        | DLCSCR   | Write: |          |       |        | BULCE         |       |       |               |        |

| \$00EF        |          | Read:  | 0        | 0     | 0      | 0             | 0     | 0     | 0             | IDLE   |

|               | DLCBSTAT | Write: |          |       |        |               |       |       |               |        |

\$0100 - \$010F

#### Flash Control Register (fts256k)

| Address      | Name         |                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1 | Bit 0 |

|--------------|--------------|-----------------|--------|--------|--------|--------|-------|--------|-------|-------|

| \$0104       | FPROT        | Read:<br>Write: | FPOPEN | NV6    | FPHDIS | FPHS1  | FPHS0 | FPLDIS | FPLS1 | FPLS0 |

| \$0105       | FSTAT        | Read:<br>Write: | CBEIF  | CCIF   | PVIOL  | ACCERR | 0     | BLANK  | 0     | 0     |

| \$0106       | FCMD         | Read:<br>Write: | 0      | CMDB6  | CMDB5  | 0      | 0     | CMDB2  | 0     | CMDB0 |

| <b>#0407</b> | Reserved for | Read:           | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| \$0107       | Factory Test | Write:          |        |        |        |        |       |        |       |       |

| \$0108       | FADDRHI      | Read:<br>Write: | 0      | Bit 14 | 13     | 12     | 11    | 10     | 9     | Bit 8 |

| \$0109       | FADDRLO      | Read:<br>Write: | Bit 7  | 6      | 5      | 4      | 3     | 2      | 1     | Bit 0 |

| \$010A       | FDATAHI      | Read:<br>Write: | Bit 15 | 14     | 13     | 12     | 11    | 10     | 9     | Bit 8 |

| \$010B       | FDATALO      | Read:<br>Write: | Bit 7  | 6      | 5      | 4      | 3     | 2      | 1     | Bit 0 |

| \$010C       | Reserved     | Read:<br>Write: | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| \$010D       | Reserved     | Read:<br>Write: | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| \$010E       | Reserved     | Read:<br>Write: | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

| \$010F       | Reserved     | Read:<br>Write: | 0      | 0      | 0      | 0      | 0     | 0      | 0     | 0     |

#### \$0110 - \$011B

## **EEPROM Control Register (eets4k)**

| Address       | Name         |        | Bit 7  | Bit 6   | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0   |

|---------------|--------------|--------|--------|---------|-------|--------|-------|-------|-------|---------|

| \$0110        | ECLKDIV      | Read:  | EDIVLD | PRDIV8  | EDIV5 | EDIV4  | EDIV3 | EDIV2 | EDIV1 | EDIV0   |

| ψυτιο         | ECENDIV      | Write: |        | TINDIVO | LDIVS |        | LDIVS | LDIVZ | LDIVI | LDIVO   |

| \$0111        | Deserved     | Read:  | 0      | 0       | 0     | 0      | 0     | 0     | 0     | 0       |

| φυττι         | Reserved     | Write: |        |         |       |        |       |       |       |         |

| ¢0440         | Reserved for | Read:  | 0      | 0       | 0     | 0      | 0     | 0     | 0     | 0       |

| \$0112        | Factory Test | Write: |        |         |       |        |       |       |       |         |

| ¢0112         |              | Read:  | CBEIE  |         | 0     | 0      | 0     | 0     | 0     | 0       |

| \$0113        | ECNFG        | Write: | ODEIE  | CCIE    |       |        |       |       |       |         |

| ¢0111         | EPROT        | Read:  | EPOPEN | NV6     | NV5   | NV4    | EPDIS | EP2   | EP1   | EP0     |

| \$0114        |              | Write: | EFOFEN |         |       |        | EPDIS | EP2   | EPI   | EPU     |

| Ф044 <b>Г</b> | FOTAT        | Read:  |        | CCIF    |       |        | 0     |       | 0     | 0       |

| \$0115        | ESTAT        | Write: | CBEIF  |         | PVIOL | ACCERR |       | BLANK |       |         |

| ¢0116         | FOMD         | Read:  | 0      | CMDB6   |       | 0      | 0     |       | 0     | CMDB0   |

| \$0116        | ECMD         | Write: |        | CIVIDBO | CMDB5 |        |       | CMDB2 |       | CIVIDBU |

| <b>C117</b>   | Reserved for | Read:  | 0      | 0       | 0     | 0      | 0     | 0     | 0     | 0       |

| \$0117        | Factory Test | Write: |        |         |       |        |       |       |       |         |

| \$0118        |              | Read:  | 0      | 0       | 0     | 0      | 0     | 10    | 0     | Dit 9   |

|               | EADDRHI      | Write: |        |         |       |        |       | 10    | 9     | Bit 8   |

|               |              |        |        |         |       |        |       |       |       |         |

#### \$0140 - \$017F

CAN0 (Motorola Scalable CAN - MSCAN)

| Address            | Name                     | 1               | Bit 7  | Bit 6  | Bit 5   | Bit 4    | Bit 3     | Bit 2       | Bit 1  | Bit 0  |

|--------------------|--------------------------|-----------------|--------|--------|---------|----------|-----------|-------------|--------|--------|

| \$0143             | CAN0BTR1                 | Read:<br>Write: | SAMP   | TSEG22 | TSEG21  | TSEG20   | TSEG13    | TSEG12      | TSEG11 | TSEG10 |

| \$0144             | CAN0RFLG                 | Read:<br>Write: | WUPIF  | CSCIF  | RSTAT1  | RSTAT0   | TSTAT1    | TSTAT0      | OVRIF  | RXF    |

| \$0145             | CANORIER                 | Read:<br>Write: | WUPIE  | CSCIE  | RSTATE1 | RSTATE0  | TSTATE1   | TSTATE0     | OVRIE  | RXFIE  |

| \$0146             | CAN0TFLG                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | TXE2        | TXE1   | TXE0   |

| \$0147             | CANOTIER                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | TXEIE2      | TXEIE1 | TXEIE0 |

| \$0148             | CAN0TARQ                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | ABTRQ2      | ABTRQ1 | ABTRQ0 |

| \$0149             | CANOTAAK                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | ABTAK2      | ABTAK1 | ABTAK0 |

| \$014A             | CAN0TBSEL                | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | TX2         | TX1    | ТХ0    |

| \$014B             | CANOIDAC                 | Read:<br>Write: | 0      | 0      | IDAM1   | IDAM0    | 0         | IDHIT2      | IDHIT1 | IDHIT0 |

| \$014C             | Reserved                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | 0           | 0      | 0      |

| \$014D             | Reserved                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | 0           | 0      | 0      |

| \$014E             | CANORXERR                | Read:<br>Write: | RXERR7 | RXERR6 | RXERR5  | RXERR4   | RXERR3    | RXERR2      | RXERR1 | RXERR0 |

| \$014F             | CAN0TXERR                | Read:<br>Write: | TXERR7 | TXERR6 | TXERR5  | TXERR4   | TXERR3    | TXERR2      | TXERR1 | TXERR0 |

| \$0150 -<br>\$0153 | CAN0IDAR0 -<br>CAN0IDAR3 | Read:<br>Write: | AC7    | AC6    | AC5     | AC4      | AC3       | AC2         | AC1    | AC0    |

| \$0154 -<br>\$0157 | CAN0IDMR0 -<br>CAN0IDMR3 | Read:<br>Write: | AM7    | AM6    | AM5     | AM4      | AM3       | AM2         | AM1    | AM0    |

| \$0158 -<br>\$015B | CAN0IDAR4 -<br>CAN0IDAR7 | Read:<br>Write: | AC7    | AC6    | AC5     | AC4      | AC3       | AC2         | AC1    | AC0    |

| \$015C -<br>\$015F | CAN0IDMR4 -<br>CAN0IDMR7 | Read:<br>Write: | AM7    | AM6    | AM5     | AM4      | AM3       | AM2         | AM1    | AM0    |

| \$0160 -<br>\$016F | CANORXFG                 | Read:<br>Write: |        | FOI    | REGROUN | D RECEIV | E BUFFER  | see Table   | 1-2    |        |

| \$0170 -<br>\$017F | CAN0TXFG                 | Read:<br>Write: |        | FOR    | EGROUNI | D TRANSM | IT BUFFEI | R see Table | e 1-2  |        |

## Table 1-2 Detailed MSCAN Foreground Receive and Transmit Buffer Layout

| Address | Name        | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$xxx0  | Extended ID | Read:  | ID28  | ID27  | ID26  | ID25  | ID24  | ID23  | ID22  | ID21  |

|         | Standard ID | Read:  | ID10  | ID9   | ID8   | ID7   | ID6   | ID5   | ID4   | ID3   |

|         | CANxRIDR0   | Write: |       |       |       |       |       |       |       |       |

| \$xxx1  | Extended ID | Read:  | ID20  | ID19  | ID18  | SRR=1 | IDE=1 | ID17  | ID16  | ID15  |

|         | Standard ID | Read:  | ID2   | ID1   | ID0   | RTR   | IDE=0 |       |       |       |

|         | CANxRIDR1   | Write: |       |       |       |       |       |       |       |       |

## 2.3.40 PM1 / TXCAN0 / TXB — Port M I/O Pin 1

PM1 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controller 0 (CAN0). It can be configured as the transmit pin TXB of the BDLC.

## 2.3.41 PM0 / RXCAN0 / RXB - Port M I/O Pin 0

PM0 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controller 0 (CAN0). It can be configured as the receive pin RXB of the BDLC.

## 2.3.42 PP7 / KWP7 / PWM7 / SCK2 - Port P I/O Pin 7

PP7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 7 output. It can be configured as serial clock pin SCK of the Serial Peripheral Interface 2 (SPI2).

## 2.3.43 PP6 / KWP6 / PWM6 / SS2 — Port P I/O Pin 6

PP6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 6 output. It can be configured as slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 2 (SPI2).

## 2.3.44 PP5 / KWP5 / PWM5 / MOSI2 - Port P I/O Pin 5

PP5 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 5 output. It can be configured as master output (during master mode) or slave input pin (during slave mode) MOSI of the Serial Peripheral Interface 2 (SPI2).

## 2.3.45 PP4 / KWP4 / PWM4 / MISO2 — Port P I/O Pin 4

PP4 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 4 output. It can be configured as master input (during master mode) or slave output (during slave mode) pin MISO of the Serial Peripheral Interface 2 (SPI2).

## 2.3.46 PP3 / KWP3 / PWM3 / SS1 — Port P I/O Pin 3

PP3 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 3 output. It can be configured as slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 1 (SPI1).

## 2.3.55 PS2 / RXD1 — Port S I/O Pin 2

PS2 is a general purpose input or output pin. It can be configured as the receive pin RXD of Serial Communication Interface 1 (SCI1).

## 2.3.56 PS1 / TXD0 - Port S I/O Pin 1

PS1 is a general purpose input or output pin. It can be configured as the transmit pin TXD of Serial Communication Interface 0 (SCI0).

## 2.3.57 PS0 / RXD0 - Port S I/O Pin 0

PS0 is a general purpose input or output pin. It can be configured as the receive pin RXD of Serial Communication Interface 0 (SCI0).

## 2.3.58 PT[7:0] / IOC[7:0] — Port T I/O Pins [7:0]

PT7-PT0 are general purpose input or output pins. They can be configured as input capture or output compare pins IOC7-IOC0 of the Enhanced Capture Timer (ECT).

## 2.4 Power Supply Pins

MC9S12DT256 power and ground pins are described below.

**NOTE:** All VSS pins must be connected together in the application.

## 2.4.1 VDDX,VSSX — Power & Ground Pins for I/O Drivers

External power and ground for I/O drivers. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

# 2.4.2 VDDR, VSSR — Power & Ground Pins for I/O Drivers & for Internal Voltage Regulator

External power and ground for I/O drivers and input to the internal voltage regulator. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

Consult the EETS4K Block User Guide for information about the EEPROM module.

## Section 17 RAM Block Description

This module supports single-cycle misaligned word accesses.

## Section 18 MSCAN Block Description

There are three MSCAN modules (CAN4, CAN1 and CAN0) implemented on the MC9S12DT256. Consult the MSCAN Block User Guide for information about the Motorola Scalable CAN Module.

## Section 19 Port Integration Module (PIM) Block Description

Consult the PIM\_9DP256 Block User Guide for information about the Port Integration Module.

## Section 20 Voltage Regulator (VREG) Block Description

Consult the VREG Block User Guide for information about the dual output linear voltage regulator.

#### MC9S12DT256 Device User Guide — V03.07

The VDDX, VSSX, VDDR and VSSR pairs supply the I/O pins, VDDR supplies also the internal voltage regulator.

VDD1, VSS1, VDD2 and VSS2 are the supply pins for the digital logic, VDDPLL, VSSPLL supply the oscillator and the PLL.

VSS1 and VSS2 are internally connected by metal.

VDDA, VDDX, VDDR as well as VSSA, VSSX, VSSR are connected by anti-parallel diodes for ESD protection.

NOTE: In the following context VDD5 is used for either VDDA, VDDR and VDDX; VSS5 is used for either VSSA, VSSR and VSSX unless otherwise noted. IDD5 denotes the sum of the currents flowing into the VDDA, VDDX and VDDR pins.

VDD is used for VDD1, VDD2 and VDDPLL, VSS is used for VSS1, VSS2 and VSSPLL. IDD is used for the sum of the currents flowing into VDD1 and VDD2.

## A.1.3 Pins

There are four groups of functional pins.

## A.1.3.1 5V I/O pins

Those I/O pins have a nominal level of 5V. This class of pins is comprised of all port I/O pins, the analog inputs, BKGD and the RESET pins. The internal structure of all those pins is identical, however some of the functionality may be disabled. E.g. for the analog inputs the output drivers, pull-up and pull-down resistors are disabled permanently.

## A.1.3.2 Analog Reference

This group is made up by the VRH and VRL pins.

#### A.1.3.3 Oscillator

The pins XFC, EXTAL, XTAL dedicated to the oscillator have a nominal 2.5V level. They are supplied by VDDPLL.

## A.1.3.4 TEST

This pin is used for production testing only.

## A.1.3.5 VREGEN

This pin is used to enable the on chip voltage regulator.

| Num | С | Rating                                                                           | Symbol          | Min | Тур | Max | Unit |

|-----|---|----------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 1   | т | Thermal Resistance LQFP112, single sided PCB <sup>2</sup>                        | $\theta_{JA}$   | -   | -   | 54  | °C/W |

| 2   | т | Thermal Resistance LQFP112, double sided PCB with 2 internal planes <sup>3</sup> | $\theta_{JA}$   | -   | -   | 41  | °C/W |

| 3   | т | Thermal Resistance LQFP 80, single sided PCB                                     | θ <sub>JA</sub> | -   | -   | 51  | °C/W |

| 4   | т | Thermal Resistance LQFP 80, double sided PCB with 2 internal planes              | $\theta_{JA}$   | -   | -   | 41  | °C/W |

Table A-5 Thermal Package Characteristics<sup>1</sup>

NOTES:

1. The values for thermal resistance are achieved by package simulations

2. PC Board according to EIA/JEDEC Standard 51-2

3. PC Board according to EIA/JEDEC Standard 51-7

## A.1.9 I/O Characteristics

This section describes the characteristics of all 5V I/O pins. All parameters are not always applicable, e.g. not all pins feature pull up/down resistances.

#### MC9S12DT256 Device User Guide — V03.07

specifies results in an error of less than 1/2 LSB (2.5mV) at the maximum leakage current. If device or operating conditions are less than worst case or leakage-induced error is acceptable, larger values of source resistance is allowed.

## A.2.2.2 Source Capacitance

When sampling an additional internal capacitor is switched to the input. This can cause a voltage drop due to charge sharing with the external and the pin capacitance. For a maximum sampling error of the input voltage  $\leq$  1LSB, then the external filter capacitor,  $C_f \geq 1024 * (C_{INS}-C_{INN})$ .

## A.2.2.3 Current Injection

There are two cases to consider.

- 1. A current is injected into the channel being converted. The channel being stressed has conversion values of 3FF (FF in 8-bit mode) for analog inputs greater than  $V_{RH}$  and 000 for values less than  $V_{RL}$  unless the current is higher than specified as disruptive condition.

- 2. Current is injected into pins in the neighborhood of the channel being converted. A portion of this current is picked up by the channel (coupling ratio K), This additional current impacts the accuracy of the conversion depending on the source resistance.

The additional input voltage error on the converted channel can be calculated as  $V_{ERR} = K * R_S * I_{INJ}$ , with  $I_{INJ}$  being the sum of the currents injected into the two pins adjacent to the converted channel.

| Condit | Conditions are shown in Table A-4 unless otherwise noted |                                                     |                                      |      |     |                  |      |  |  |

|--------|----------------------------------------------------------|-----------------------------------------------------|--------------------------------------|------|-----|------------------|------|--|--|

| Num    | С                                                        | Rating                                              | Symbol                               | Min  | Тур | Max              | Unit |  |  |

| 1      | С                                                        | Max input Source Resistance                         | R <sub>S</sub>                       | -    | -   | 1                | KΩ   |  |  |

| 2      | т                                                        | Total Input Capacitance<br>Non Sampling<br>Sampling | C <sub>INN</sub><br>C <sub>INS</sub> |      |     | 10<br>22         | pF   |  |  |

| 3      | С                                                        | Disruptive Analog Input Current                     | I <sub>NA</sub>                      | -2.5 |     | 2.5              | mA   |  |  |

| 4      | С                                                        | Coupling Ratio positive current injection           | К <sub>р</sub>                       |      |     | 10 <sup>-4</sup> | A/A  |  |  |

| 5      | С                                                        | Coupling Ratio negative current injection           | K <sub>n</sub>                       |      |     | 10 <sup>-2</sup> | A/A  |  |  |

## **Table A-9 ATD Electrical Characteristics**

- Maximum Erase and Programming times are achieved under particular combinations of f<sub>NVMOP</sub> and bus frequency f<sub>bus</sub>. Refer to formulae in Sections A.3.1.1 - A.3.1.4 for guidance.

- 4. Burst Programming operations are not applicable to EEPROM

- 5. Minimum Erase times are achieved under maximum NVM operating frequency f<sub>NVMOP</sub>.

- 6. Minimum time, if first word in the array is not blank

- 7. Maximum time to complete check on an erased block

## A.6 MSCAN

| Conditions are shown in Table A-4 unless otherwise noted |   |                                       |                  |     |     |     |      |  |

|----------------------------------------------------------|---|---------------------------------------|------------------|-----|-----|-----|------|--|

| Num                                                      | С | Rating                                | Symbol           | Min | Тур | Max | Unit |  |

| 1                                                        | Р | MSCAN Wake-up dominant pulse filtered | t <sub>WUP</sub> |     |     | 2   | μs   |  |

| 2                                                        | Р | MSCAN Wake-up dominant pulse pass     | t <sub>WUP</sub> | 5   |     |     | μs   |  |

#### Table A-17 MSCAN Wake-up Pulse Characteristics

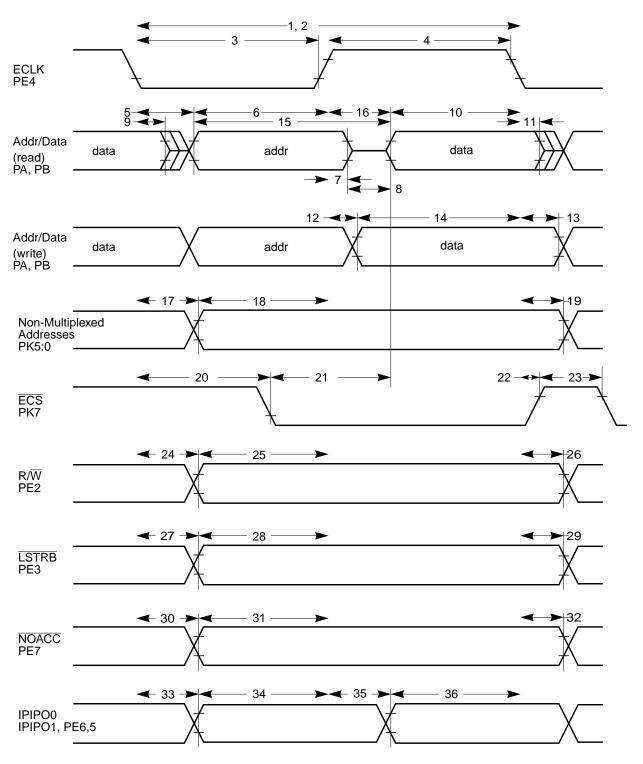

Figure A-10 General External Bus Timing

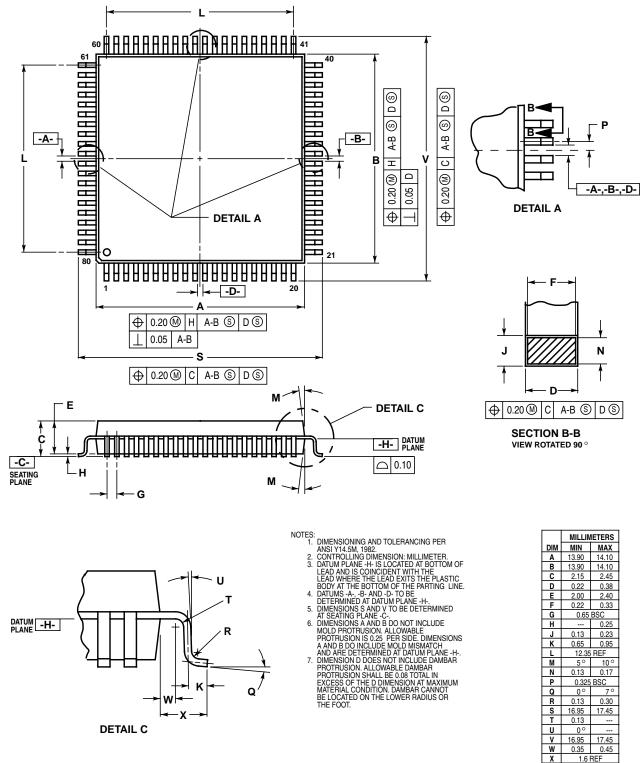

## B.3 80-pin QFP package

Figure B-2 80-pin QFP Mechanical Dimensions (case no. 841B)