# E·XFL

# XMOS - XS1-L8A-128-QF124-C8 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Active                                                         |

| Core Processor             | XCore                                                          |

| Core Size                  | 32-Bit 8-Core                                                  |

| Speed                      | 800MIPS                                                        |

| Connectivity               | Configurable                                                   |

| Peripherals                |                                                                |

| Number of I/O              | 84                                                             |

| Program Memory Size        | 128KB (32K x 32)                                               |

| Program Memory Type        | SRAM                                                           |

| EEPROM Size                | -                                                              |

| RAM Size                   | ·                                                              |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | External                                                       |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 124-TFQFN Dual Rows, Exposed Pad                               |

| Supplier Device Package    | 124-QFN DualRow (10x10)                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-l8a-128-qf124-c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

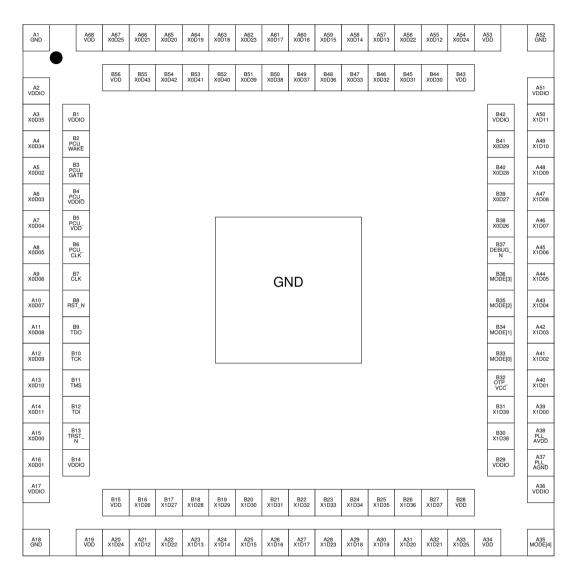

# 3 Pin Configuration

-XMOS<sup>®</sup>-

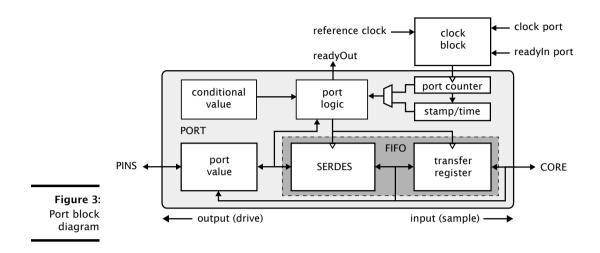

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

#### 5.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

A clock block can use a 1-bit port as its clock source allowing external application clocks to be used to drive the input and output interfaces.

In many cases I/O signals are accompanied by strobing signals. The xCORE ports can input and interpret strobe (known as readyln and readyOut) signals generated by external sources, and ports can generate strobe signals to accompany output data.

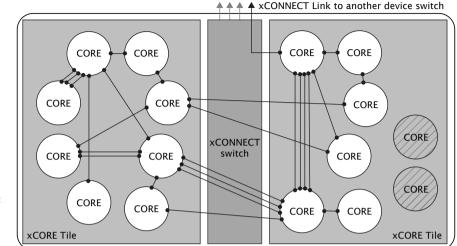

Figure 5: Switch, links and channel ends

# 6 PLL

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock.

The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 6:

PLL v N

|            | Oscillator | MC | DDE | Tile           | PLL Ratio | PLL | setting | gs |

|------------|------------|----|-----|----------------|-----------|-----|---------|----|

|            | Frequency  | 1  | 0   | Frequency      |           | OD  | F       | R  |

| Figure 6:  | 5-13 MHz   | 0  | 0   | 130-399.75 MHz | 30.75     | 1   | 122     | 0  |

| multiplier | 13-20 MHz  | 1  | 1   | 260-400.00 MHz | 20        | 2   | 119     | 0  |

| values and | 20-48 MHz  | 1  | 0   | 167-400.00 MHz | 8.33      | 2   | 49      | 0  |

| MODE pins  | 48-100 MHz | 0  | 1   | 196-400.00 MHz | 4         | 2   | 23      | 0  |

Figure 6 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

*OD*, *F* and *R* must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The *OD*, *F*, and *R* values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset.

-XMOS

-XMOS

21

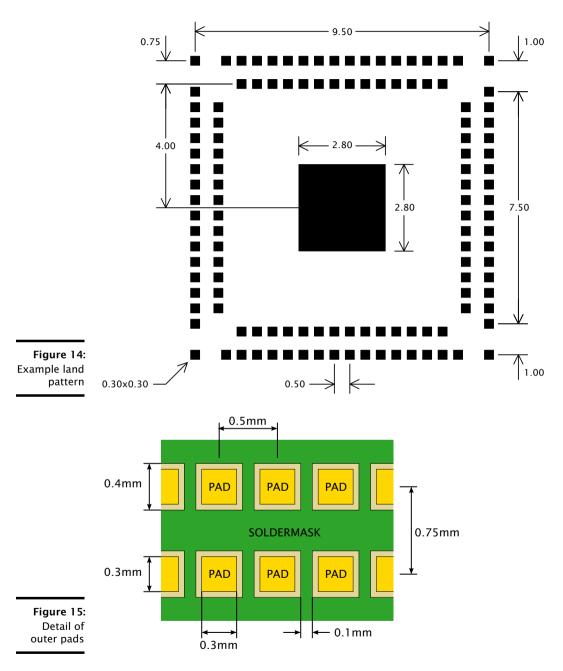

vias, with a 0.6mm diameter annular ring and a 0.3mm drill, equally spaced across the heat slug, would be suitable.

#### 10.4 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from *Joint IPC/JEDEC Standard For Moisture/Reflow Sensitivity Classification For Nonhermetic Solid State Surface-Mount Devices* J-STD-020 Revision D.

-XM()S

### 11.4 Reset Timing

Figure 21: Reset timing

| Symbol  | Parameters          | MIN | TYP | MAX | UNITS | Notes |

|---------|---------------------|-----|-----|-----|-------|-------|

| T(RST)  | Reset pulse width   | 5   |     |     | us    |       |

| T(INIT) | Initialization time |     |     | 150 | μs    | А     |

A Shows the time taken to start booting after RST\_N has gone high.

#### 11.5 Power Consumption

|   | Symbol    | Parameter                           | MIN | ТҮР | MAX | UNITS   | Notes      |

|---|-----------|-------------------------------------|-----|-----|-----|---------|------------|

| ſ | I(DDCQ)   | Quiescent VDD current               |     | 28  |     | mA      | A, B, C    |

|   | PD        | Tile power dissipation              |     | 450 |     | µW/MIPS | A, D, E, F |

|   | IDD       | Active VDD current (Speed Grade 8)  |     | 320 | 600 | mA      | A, G       |

|   |           | Active VDD current (Speed Grade 10) |     | 400 | 750 | mA      | А, Н       |

|   | I(ADDPLL) | PLL_AVDD current                    |     |     | 14  | mA      | I          |

Figure 22: xCORE Tile currents

A Use for budgetary purposes only.

B Assumes typical tile and I/O voltages with no switching activity.

C Includes PLL current.

D Assumes typical tile and I/O voltages with nominal switching activity.

E Assumes 1 MHz = 1 MIPS.

F PD(TYP) value is the usage power consumption under typical operating conditions.

-XM()S

G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 400 MHz, average device resource usage.

H Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, average device resource usage.

I PLL\_AVDD = 1.0 V

The tile power consumption of the device is highly application dependent and should be used for budgetary purposes only.

More detailed power analysis can be found in the XS1-L Power Consumption document, X2999.

#### 11.6 Clock

| Symbol | Parameter                                     | MIN  | ТҮР | MAX | UNITS | Notes |

|--------|-----------------------------------------------|------|-----|-----|-------|-------|

| f      | Frequency                                     | 4.22 | 20  | 100 | MHz   |       |

| SR     | Slew rate                                     | 0.10 |     |     | V/ns  |       |

| TJ(LT) | Long term jitter (pk-pk)                      |      |     | 2   | %     | A     |

| f(MAX) | Processor clock frequency (Speed<br>Grade 8)  |      |     | 400 | MHz   | В     |

|        | Processor clock frequency (Speed<br>Grade 10) |      |     | 500 | MHz   | В     |

Figure 23: Clock

A Percentage of CLK period.

B Assumes typical tile and I/O voltages with nominal activity.

Further details can be found in the XS1-L Clock Frequency Control document, X1433.

# 11.7 xCORE Tile I/O AC Characteristics

|                             | Symbol       | Parameter                                                           | MIN | TYP | MAX | UNITS | Notes |

|-----------------------------|--------------|---------------------------------------------------------------------|-----|-----|-----|-------|-------|

| <b></b>                     | T(XOVALID)   | Input data valid window                                             | 8   |     |     | ns    |       |

| Figure 24:                  | T(XOINVALID) | Output data invalid window                                          | 9   |     |     | ns    |       |

| I/O AC char-<br>acteristics | T(XIFMAX)    | Rate at which data can be sampled with respect to an external clock |     |     | 60  | MHz   |       |

The input valid window parameter relates to the capability of the device to capture data input to the chip with respect to an external clock source. It is calculated as the sum of the input setup time and input hold time with respect to the external clock as measured at the pins. The output invalid window specifies the time for which an output is invalid with respect to the external clock. Note that these parameters are specified as a window rather than absolute numbers since the device provides functionality to delay the incoming clock with respect to the incoming data.

Information on interfacing to high-speed synchronous interfaces can be found in the XS1 Port I/O Timing document, X5821.

# 11.8 xConnect Link Performance

|             | Symbol     | Parameter                      | MIN | TYP | MAX | UNITS  | Notes |

|-------------|------------|--------------------------------|-----|-----|-----|--------|-------|

|             | B(2blinkP) | 2b link bandwidth (packetized) |     |     | 87  | MBit/s | А, В  |

| Figure 25:  | B(5blinkP) | 5b link bandwidth (packetized) |     |     | 217 | MBit/s | А, В  |

| Link        | B(2blinkS) | 2b link bandwidth (streaming)  |     |     | 100 | MBit/s | В     |

| performance | B(5blinkS) | 5b link bandwidth (streaming)  |     |     | 250 | MBit/s | В     |

-XM()S

A Assumes 32-byte packet in 3-byte header mode. Actual performance depends on size of the header and payload.

B 7.5 ns symbol time.

26

The asynchronous nature of links means that the relative phasing of CLK clocks is not important in a multi-clock system, providing each meets the required stability criteria.

| Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|----------|-------------------------------|-----|-----|-----|-------|-------|

| f(TCK_D) | TCK frequency (debug)         |     |     | 18  | MHz   |       |

| f(TCK_B) | TCK frequency (boundary scan) |     |     | 10  | MHz   |       |

| T(SETUP) | TDO to TCK setup time         | 5   |     |     | ns    | А     |

| T(HOLD)  | TDO to TCK hold time          | 5   |     |     | ns    | А     |

| T(DELAY) | TCK to output delay           |     |     | 15  | ns    | В     |

#### 11.9 JTAG Timing

Figure 26: JTAG timing

A Timing applies to TMS and TDI inputs.

B Timing applies to TDO output from negative edge of TCK.

All JTAG operations are synchronous to TCK apart from the global asynchronous reset TRST\_N.

-XMOS°

# Appendices

# A Configuration of the XS1

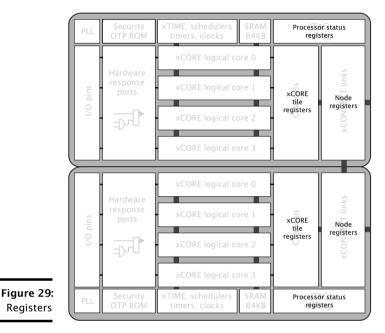

The device is configured through three banks of registers, as shown in Figure 29.

The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

# A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0C. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

# A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile

$\Rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnn is the tile-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

-XM()S

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RW   | RAM base address                      |

| 0x01      | RW   | Vector base address                   |

| 0x02      | RW   | xCORE Tile control                    |

| 0x03      | RO   | xCORE Tile boot status                |

| 0x05      | RO   | Security configuration                |

| 0x06      | RW   | Ring Oscillator Control               |

| 0x07      | RO   | Ring Oscillator Value                 |

| 0x08      | RO   | Ring Oscillator Value                 |

| 0x09      | RO   | Ring Oscillator Value                 |

| 0x0A      | RO   | Ring Oscillator Value                 |

| 0x10      | DRW  | Debug SSR                             |

| 0x11      | DRW  | Debug SPC                             |

| 0x12      | DRW  | Debug SSP                             |

| 0x13      | DRW  | DGETREG operand 1                     |

| 0x14      | DRW  | DGETREG operand 2                     |

| 0x15      | DRW  | Debug interrupt type                  |

| 0x16      | DRW  | Debug interrupt data                  |

| 0x18      | DRW  | Debug core control                    |

| 0x20 0x27 | DRW  | Debug scratch                         |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |

| 0x70 0x73 | DRW  | Data breakpoint control register      |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |

| 0x90 0x93 | DRW  | Resources breakpoint value            |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |

-XMOS<sup>®</sup>

Figure 30: Summary 0x50 .. 0x53: Data watchpoint address 1

| Data<br>1point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ress 1         | 31:0 | DRW  |      | Value.      |

#### B.23 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| ita<br>nt | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| 2         | 31:0 | DRW  |      | Value.      |

#### B.24 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

|                      | Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                       |

|----------------------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

|                      | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                                                                                 |

|                      | 15:3  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

|                      | 2     | DRW  | 0    | Set to 1 to enable breakpoints to be triggered on loads. Breakpoints always trigger on stores.                                                                                                                                                                                                    |

| <b>3:</b><br>a<br>nt | 1     | DRW  | 0    | By default, data watchpoints trigger if memory in the range [Address1Address2] is accessed (the range is inclusive of Address1 and Address2). If set to 1, data watchpoints trigger if memory outside the range (Address2Address1) is accessed (the range is exclusive of Address2 and Address1). |

| er                   | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                                                                                     |

0x70 .. 0x73: Data breakpoint control register

#### B.25 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

-XMOS

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number      | Perm | Description                                    |

|-------------|------|------------------------------------------------|

| 0x00        | RO   | Device identification                          |

| 0x01        | RO   | xCORE Tile description 1                       |

| 0x02        | RO   | xCORE Tile description 2                       |

| 0x04        | CRW  | Control PSwitch permissions to debug registers |

| 0x05        | CRW  | Cause debug interrupts                         |

| 0x06        | RW   | xCORE Tile clock divider                       |

| 0x07        | RO   | Security configuration                         |

| 0x100x13 RO |      | PLink status                                   |

| 0x20 0x27   | CRW  | Debug scratch                                  |

| 0x40        | RO   | PC of logical core 0                           |

| 0x41        | RO   | PC of logical core 1                           |

| 0x42        | RO   | PC of logical core 2                           |

| 0x43        | RO   | PC of logical core 3                           |

| 0x60        | RO   | SR of logical core 0                           |

| 0x61        | RO   | SR of logical core 1                           |

| 0x62        | RO   | SR of logical core 2                           |

| 0x63        | RO   | SR of logical core 3                           |

| 0x80 0x9F   | RO   | Chanend status                                 |

Figure 31: Summary

# C.1 Device identification: 0x00

|                | Bits  | Perm | Init | Description                                             |

|----------------|-------|------|------|---------------------------------------------------------|

|                | 31:24 | RO   |      | Processor ID of this xCORE tile.                        |

| 0x00:          | 23:16 | RO   |      | Number of the node in which this xCORE tile is located. |

| Device         | 15:8  | RO   |      | xCORE tile revision.                                    |

| identification | 7:0   | RO   |      | xCORE tile version.                                     |

# C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | RO   |      | Number of channel ends.  |

| 23:16 | RO   |      | Number of locks.         |

| 15:8  | RO   |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

# C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02 xCORE Tile description 2

0x01: xCORE Tile description 1

|    | Bits  | Perm | Init | Description             |

|----|-------|------|------|-------------------------|

| 2: | 31:16 | RO   | -    | Reserved                |

| e. | 15:8  | RO   |      | Number of clock blocks. |

| 2  | 7:0   | RO   |      | Number of timers.       |

# C.4 Control PSwitch permissions to debug registers: 0x04

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                 |

|------|------|------|-------------------------------------------------------------------------------------------------------------|

| 31:1 | RO   | -    | Reserved                                                                                                    |

| 0    | CRW  |      | Set to 1 to restrict PSwitch access to all CRW marked registers to become read-only rather than read-write. |

# C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

-XMOS-

# C.16 SR of logical core 2: 0x62

\_ ~~ SR o

| 0x62:<br>of logical | Bits | Perm | Init | Description |

|---------------------|------|------|------|-------------|

| core 2              | 31:0 | RO   |      | Value.      |

# C.17 SR of logical core 3: 0x63

0x63 SR of logica core

| В  | its | Perm | Init | Description |

|----|-----|------|------|-------------|

| 31 | :0  | RO   |      | Value.      |

#### C.18 Chanend status: 0x80 .. 0x9F

These registers record the status of each channel-end on the tile.

-XMOS

|          | Bits  | Perm | Init | Description                                                                                                    |

|----------|-------|------|------|----------------------------------------------------------------------------------------------------------------|

|          | 31:26 | RO   | -    | Reserved                                                                                                       |

|          | 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |

|          | 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |

|          | 15:6  | RO   | -    | Reserved                                                                                                       |

|          | 5:4   | RO   |      | Two-bit network identifier                                                                                     |

|          | 3     | RO   | -    | Reserved                                                                                                       |

|          | 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |

| F:       | 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |

| nd<br>Us | 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |

0x80 .. 0x9 Chanen statu

| Bits  | Perm | Init | Description                                                                            |

|-------|------|------|----------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                               |

| 25:23 | RW   |      | OD: Output divider value<br>The initial value depends on pins MODE0 and MODE1.         |

| 22:21 | RO   | -    | Reserved                                                                               |

| 20:8  | RW   |      | F: Feedback multiplication ratio<br>The initial value depends on pins MODE0 and MODE1. |

| 7     | RO   | -    | Reserved                                                                               |

| 6:0   | RW   |      | R: Oscilator input divider value<br>The initial value depends on pins MODE0 and MODE1. |

0x06: PLL settings

# D.6 System switch clock divider: 0x07

Sets the ratio of the PLL clock and the switch clock.

**0x07** System switch clock divider

| 07:        | Bits  | Perm | Init | Description                                                                                            |

|------------|-------|------|------|--------------------------------------------------------------------------------------------------------|

| em         | 31:16 | RO   | -    | Reserved                                                                                               |

| ock<br>der | 15:0  | RW   | 0    | Switch clock divider. The PLL clock will be divided by this value plus one to derive the switch clock. |

# D.7 Reference clock: 0x08

Sets the ratio of the PLL clock and the reference clock used by the node.

**0x08:** Reference clock

| Bits  | Perm | Init | Description                                                                                                                       |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                          |

| 15:0  | RW   | 3    | Architecture reference clock divider. The PLL clock will be divided by this value plus one to derive the 100 MHz reference clock. |

# D.8 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS"

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose first mismatching bit is 7. |

| 27:24 | RW   | 0    | The direction for packets whose first mismatching bit is 6. |

| 23:20 | RW   | 0    | The direction for packets whose first mismatching bit is 5. |

| 19:16 | RW   | 0    | The direction for packets whose first mismatching bit is 4. |

| 15:12 | RW   | 0    | The direction for packets whose first mismatching bit is 3. |

| 11:8  | RW   | 0    | The direction for packets whose first mismatching bit is 2. |

| 7:4   | RW   | 0    | The direction for packets whose first mismatching bit is 1. |

| 3:0   | RW   | 0    | The direction for packets whose first mismatching bit is 0. |

**0x0C:** Directions 0-7

### D.9 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                                  |

|-------|------|------|--------------------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose first mismatching bit is 15. |

| 27:24 | RW   | 0    | The direction for packets whose first mismatching bit is 14. |

| 23:20 | RW   | 0    | The direction for packets whose first mismatching bit is 13. |

| 19:16 | RW   | 0    | The direction for packets whose first mismatching bit is 12. |

| 15:12 | RW   | 0    | The direction for packets whose first mismatching bit is 11. |

| 11:8  | RW   | 0    | The direction for packets whose first mismatching bit is 10. |

| 7:4   | RW   | 0    | The direction for packets whose first mismatching bit is 9.  |

| 3:0   | RW   | 0    | The direction for packets whose first mismatching bit is 8.  |

**0x0D:** Directions 8-15

# D.10 DEBUG\_N configuration: 0x10

Configures the behavior of the DEBUG\_N pin.

|         | Bits | Perm | Init | Description                                                                          |

|---------|------|------|------|--------------------------------------------------------------------------------------|

|         | 31:2 | RO   | -    | Reserved                                                                             |

| 0:      | 1    | RW   | 0    | Set to 1 to enable signals on DEBUG_N to generate DCALL on the core.                 |

| N<br>on | 0    | RW   | 0    | When set to 1, the DEBUG_N wire will be pulled down when the node enters debug mode. |

0x10 DEBUG\_N configuration

#### D.11 Debug source: 0x1F

Contains the source of the most recent debug event.

| Bits | Perm | Init | Description                                                                        |

|------|------|------|------------------------------------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                                           |

| 4    | RW   |      | If set, the external DEBUG_N pin is the source of the most recent debug interrupt. |

| 3:1  | RO   | -    | Reserved                                                                           |

| 0    | RW   |      | If set, the xCORE Tile is the source of the most recent debug interrupt.           |

0x1F: Debug source

# D.12 Link status, direction, and network: 0x20 .. 0x27

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits  | Perm | Init | Description                                                                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                 |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field<br>specifies the type of link that the data is routed to:<br>0: plink<br>1: external link<br>2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                              |

| 15:12 | RO   | -    | Reserved                                                                                                                                                                                 |

| 11:8  | RW   | 0    | The direction that this this link is associated with; set for rout-<br>ing.                                                                                                              |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                 |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                                           |

| 3     | RO   | -    | Reserved                                                                                                                                                                                 |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                                           |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                                           |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                                           |

-XMOS

**0x20 .. 0x27** Link status, direction, and network

# H Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XS1-L8A-128-QF124. Each of the following sections contains items to check for each design.

#### H.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 10).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 10).

- The VDD (core) supply is capable of supplying 600mA (Section 10).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 10

- The PCU\_VDD pin is connected to the VDD supply and PCU\_VDDIO is connected to the VDDIO supply (Section 10).

#### H.2 Power supply decoupling

- □ The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 10).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 10).

#### H.3 Power on reset

The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place. As the errata in the datasheets show, the internal pull-ups on these two pins can occasionally provide stronger than normal pull-up currents. For this reason, an RC type reset circuit is discouraged as behavior would be unpredictable. A voltage supervisor type reset device is recommended to guarantee a good reset. This also has the benefit of resetting the system should the relevant supply go out of specification.

-XM()S

57

- □ If you included an XSYS header, you connected pin 3 to any MODE2/MODE3 pin that would otherwise be NC (Section G).

- $\Box$  If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.8 GPIO

You have not mapped both inputs and outputs to the same multi-bit port.

#### H.9 Multi device designs

Skip this section if your design only includes a single XMOS device.

-XM()S

- $\Box$  One device is connected to a SPI flash for booting.

- Devices that boot from link have MODE2 grounded and MODE3 NC. These device must have link XLB connected to a device to boot from (see 7).

- □ If you included an XSYS header, you have included buffers for RST\_N, TRST\_N, TMS, TCK, MODE2, and MODE3 (Section F).