Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                                                     |

|----------------------------|------------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                                         |

| Speed                      | 216MHz                                                                                                     |

| Connectivity               | CANbus, Ethernet, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, SAI, SPDIFRX, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                            |

| Number of I/O              | 168                                                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                                                             |

| Program Memory Type        | FLASH                                                                                                      |

| EEPROM Size                | -                                                                                                          |

| RAM Size                   | 320K x 8                                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                                |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                      |

| Oscillator Type            | Internal                                                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                          |

| Mounting Type              | Surface Mount                                                                                              |

| Package / Case             | 216-TFBGA                                                                                                  |

| Supplier Device Package    | 216-TFBGA (13x13)                                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f750n8h6                                      |

|                            |                                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Timers    | and watchdogs                                                          | . 33 |

|--------------|-----------|------------------------------------------------------------------------|------|

|              | 3.22.1    | Advanced-control timers (TIM1, TIM8)                                   | . 35 |

|              | 3.22.2    | General-purpose timers (TIMx)                                          | . 35 |

|              | 3.22.3    | Basic timers TIM6 and TIM7                                             | . 36 |

|              | 3.22.4    | Low-power timer (LPTIM1)                                               | . 36 |

|              | 3.22.5    | Independent watchdog                                                   | . 36 |

|              | 3.22.6    | Window watchdog                                                        |      |

|              | 3.22.7    | SysTick timer                                                          |      |

| 3.23         |           | tegrated circuit interface (I <sup>2</sup> C)                          |      |

| 3.24         | Univers   | al synchronous/asynchronous receiver transmitters (USART)              | . 38 |

| .25          | Serial p  | peripheral interface (SPI)/inter- integrated sound interfaces (I2S)    | . 39 |

| .26          | Serial a  | udio interface (SAI)                                                   | . 39 |

| 8.27         | SPDIFF    | RX Receiver Interface (SPDIFRX)                                        | . 40 |

| 3.28         | Audio P   | PLL (PLLI2S)                                                           | . 40 |

| 3.29         | Audio a   | nd LCD PLL(PLLSAI)                                                     | . 41 |

| 3.30         | SD/SDI    | O/MMC card host interface (SDMMC)                                      | . 41 |

| 3.31         | Etherne   | et MAC interface with dedicated DMA and IEEE 1588 support              | . 41 |

| 3.32         | Controll  | ler area network (bxCAN)                                               | . 42 |

| 3.33         | Univers   | al serial bus on-the-go full-speed (OTG_FS)                            | . 42 |

| 3.34         | Univers   | al serial bus on-the-go high-speed (OTG_HS)                            | . 42 |

| 3.35         | -         | efinition multimedia interface (HDMI) - consumer<br>nics control (CEC) | . 43 |

| 3.36         | Digital o | camera interface (DCMI)                                                | . 43 |

| 3.37         | Cryptog   | graphic acceleration                                                   | . 43 |

| 3.38         | Randon    | n number generator (RNG)                                               | . 44 |

| 3.39         | Genera    | I-purpose input/outputs (GPIOs)                                        | . 44 |

| 3.40         | Analog-   | -to-digital converters (ADCs)                                          | . 44 |

| 3.41         |           | ature sensor                                                           |      |

|              | Digital-t | to-analog converter (DAC)                                              | . 45 |

|              | -         | •                                                                      |      |

| 3.42<br>3.43 | Serial w  | vire JTAG debug port (SWJ-DP)                                          | . 45 |

4

5

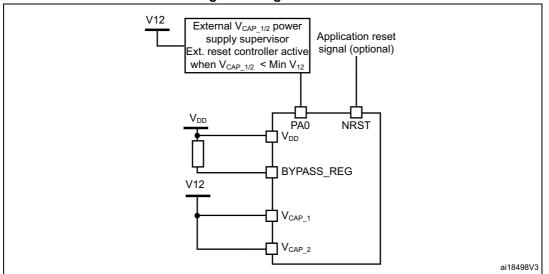

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

Figure 8. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below V<sub>12</sub> minimum value and V<sub>DD</sub> is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of  $V_{12}$  depends on the maximum frequency targeted in the application.

## 3.22.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

## 3.22.4 Low-power timer (LPTIM1)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one-shot mode

- Selectable software / hardware input trigger

- Selectable clock source:

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

## 3.22.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

## 3.22.6 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.22.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

| Table 10. STM32F750x8 | pin and ball definition | (continued)  |

|-----------------------|-------------------------|--------------|

|                       |                         | (0011111000) |

| Pin     | Num     | ber      |                                                      |          | -             |       | pin and ball definition (continued)                                                                                                   |                         |

|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                                   | Additional<br>functions |

| 23      | 35      | N2       | PA1                                                  | I/O      | FT            | (4)   | TIM2_CH2, TIM5_CH2, USART2_RTS,<br>UART4_RX, QUADSPI_BK1_IO3,<br>SAI2_MCK_B,<br>ETH_MII_RX_CLK/ETH_RMII_REF_CLK<br>, LCD_R2, EVENTOUT | ADC123_IN1              |

| 24      | 36      | P2       | PA2                                                  | I/O      | FT            | (4)   | TIM2_CH3, TIM5_CH3, TIM9_CH1,<br>USART2_TX, SAI2_SCK_B, ETH_MDIO,<br>LCD_R1, EVENTOUT                                                 | ADC123_IN2,<br>WKUP2    |

| -       | -       | K4       | PH2                                                  | I/O      | FT            |       | LPTIM1_IN2, QUADSPI_BK2_IO0,<br>SAI2_SCK_B, ETH_MII_CRS,<br>FMC_SDCKE0, LCD_R0, EVENTOUT                                              | -                       |

| -       | -       | J4       | PH3                                                  | I/O      | FT            | -     | QUADSPI_BK2_IO1, SAI2_MCK_B,<br>ETH_MII_COL, FMC_SDNE0, LCD_R1,<br>EVENTOUT                                                           | -                       |

| -       | -       | H4       | PH4                                                  | I/O      | FT            | -     | I2C2_SCL, OTG_HS_ULPI_NXT,<br>EVENTOUT                                                                                                | -                       |

| -       | -       | J3       | PH5                                                  | I/O      | FT            | -     | I2C2_SDA, SPI5_NSS, FMC_SDNWE,<br>EVENTOUT                                                                                            | -                       |

| 25      | 37      | R2       | PA3                                                  | I/O      | FT            | (4)   | TIM2_CH4, TIM5_CH4, TIM9_CH2,<br>USART2_RX, OTG_HS_ULPI_D0,<br>ETH_MII_COL, LCD_B5, EVENTOUT                                          | ADC123_IN3              |

| 26      | 38      | K6       | VSS                                                  | S        | -             | -     | -                                                                                                                                     | -                       |

| -       | -       | L5       | BYPASS_REG                                           | Ι        | FT            | -     | -                                                                                                                                     | -                       |

| 27      | 39      | K5       | VDD                                                  | S        | -             | -     | -                                                                                                                                     | -                       |

| 28      | 40      | N4       | PA4                                                  | I/O      | ТТа           | (4)   | SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS, USART2_CK,<br>OTG_HS_SOF, DCMI_HSYNC,<br>LCD_VSYNC, EVENTOUT                                   | ADC12_IN4,<br>DAC_OUT1  |

| 29      | 41      | P4       | PA5                                                  | I/O      | ТТа           | (4)   | TIM2_CH1/TIM2_ETR, TIM8_CH1N,<br>SPI1_SCK/I2S1_CK,<br>OTG_HS_ULPI_CK, LCD_R4,<br>EVENTOUT                                             | ADC12_IN5,<br>DAC_OUT2  |

| 30      | 42      | P3       | PA6                                                  | I/O      | FT            | (4)   | TIM1_BKIN, TIM3_CH1, TIM8_BKIN,<br>SPI1_MISO, TIM13_CH1,<br>DCMI_PIXCLK, LCD_G2, EVENTOUT                                             | ADC12_IN6               |

|         |         |          | Table 10. S                                          | TM3      | 2F75          | 0x8   | pin and ball definition (continued)                                                                                       |                         |

|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Pin     | Num     | ber      |                                                      |          |               |       |                                                                                                                           |                         |

| LQFP100 | LQFP144 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                       | Additional<br>functions |

| 31      | 43      | R3       | PA7                                                  | I/O      | FT            | (4)   | TIM1_CH1N, TIM3_CH2, TIM8_CH1N,<br>SPI1_MOSI/I2S1_SD, TIM14_CH1,<br>ETH_MII_RX_DV/ETH_RMII_CRS_DV,<br>FMC_SDNWE, EVENTOUT | ADC12_IN7               |

| 32      | 44      | N5       | PC4                                                  | I/O      | FT            | (4)   | I2S1_MCK, SPDIFRX_IN2,<br>ETH_MII_RXD0/ETH_RMII_RXD0,<br>FMC_SDNE0, EVENTOUT                                              | ADC12_IN14              |

| 33      | 45      | P5       | PC5                                                  | I/O      | FT            | (4)   | SPDIFRX_IN3,<br>ETH_MII_RXD1/ETH_RMII_RXD1,<br>FMC_SDCKE0, EVENTOUT                                                       | ADC12_IN15              |

| -       | -       | L7       | VDD                                                  | S        | -             | -     | -                                                                                                                         | -                       |

| -       | -       | L6       | VSS                                                  | S        | -             | -     | -                                                                                                                         | -                       |

| 34      | 46      | R5       | PB0                                                  | I/O      | FT            | (4)   | TIM1_CH2N, TIM3_CH3, TIM8_CH2N,<br>UART4_CTS, LCD_R3,<br>OTG_HS_ULPI_D1, ETH_MII_RXD2,<br>EVENTOUT                        | ADC12_IN8               |

| 35      | 47      | R4       | PB1                                                  | I/O      | FT            | (4)   | TIM1_CH3N, TIM3_CH4, TIM8_CH3N,<br>LCD_R6, OTG_HS_ULPI_D2,<br>ETH_MII_RXD3, EVENTOUT                                      | ADC12_IN9               |

| 36      | 48      | M5       | PB2                                                  | I/O      | FT            | -     | SAI1_SD_A, SPI3_MOSI/I2S3_SD,<br>QUADSPI_CLK, EVENTOUT                                                                    | -                       |

| -       | -       | G4       | PI15                                                 | I/O      | FT            | -     | LCD_R0, EVENTOUT                                                                                                          | -                       |

| -       | -       | R6       | PJ0                                                  | I/O      | FT            | -     | LCD_R1, EVENTOUT                                                                                                          | -                       |

| -       | -       | R7       | PJ1                                                  | I/O      | FT            | -     | LCD_R2, EVENTOUT                                                                                                          | -                       |

| -       | -       | P7       | PJ2                                                  | I/O      | FT            | -     | LCD_R3, EVENTOUT                                                                                                          | -                       |

| -       | -       | N8       | PJ3                                                  | I/O      | FT            | -     | LCD_R4, EVENTOUT                                                                                                          | -                       |

| -       | -       | M9       | PJ4                                                  | I/O      | FT            | -     | LCD_R5, EVENTOUT                                                                                                          | -                       |

| -       | 49      | P8       | PF11                                                 | I/O      | FT            | -     | SPI5_MOSI, SAI2_SD_B,<br>FMC_SDNRAS, DCMI_D12, EVENTOUT                                                                   | -                       |

| -       | 50      | M6       | PF12                                                 | I/O      | FT            | -     | FMC_A6, EVENTOUT                                                                                                          | -                       |

| -       | 51      | K7       | VSS                                                  | S        | -             | -     |                                                                                                                           | -                       |

| -       | 52      | L8       | VDD                                                  | S        | -             | -     |                                                                                                                           | -                       |

| -       | 53      | N6       | PF13                                                 | I/O      | FT            | -     | I2C4_SMBA, FMC_A7, EVENTOUT                                                                                               | -                       |

| Table 10. STM32F750x8 | pin and ball definition ( | (continued) |

|-----------------------|---------------------------|-------------|

|                       |                           |             |

| Table 10. STM32F750x8 | pin and ball definition | (continued) |

|-----------------------|-------------------------|-------------|

|                       |                         |             |

| Pin     | Num     | ber      |                                                      |          |               |       | pin and ball definition (continued)                                                                                |                         |

|---------|---------|----------|------------------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional<br>functions |

| 52      | 74      | K14      | PB13                                                 | I/O      | FT            | -     | TIM1_CH1N, SPI2_SCK/I2S2_CK,<br>USART3_CTS, CAN2_TX,<br>OTG_HS_ULPI_D6,<br>ETH_MII_TXD1/ETH_RMII_TXD1,<br>EVENTOUT | OTG_HS_VBUS             |

| 53      | 75      | R14      | PB14                                                 | I/O      | FT            | -     | TIM1_CH2N, TIM8_CH2N, SPI2_MISO,<br>USART3_RTS, TIM12_CH1,<br>OTG_HS_DM, EVENTOUT                                  | -                       |

| 54      | 76      | R15      | PB15                                                 | I/O      | FT            | -     | RTC_REFIN, TIM1_CH3N, TIM8_CH3N,<br>SPI2_MOSI/I2S2_SD, TIM12_CH2,<br>OTG_HS_DP, EVENTOUT                           | -                       |

| 55      | 77      | L15      | PD8                                                  | I/O      | FT            | -     | USART3_TX, SPDIFRX_IN11,<br>FMC_D13, EVENTOUT                                                                      | -                       |

| 56      | 78      | L14      | PD9                                                  | I/O      | FT            | -     | USART3_RX, FMC_D14, EVENTOUT                                                                                       | -                       |

| 57      | 79      | K15      | PD10                                                 | I/O      | FT            | -     | USART3_CK, FMC_D15, LCD_B3,<br>EVENTOUT                                                                            | -                       |

| 58      | 80      | N10      | PD11                                                 | I/O      | FT            | -     | I2C4_SMBA, USART3_CTS,<br>QUADSPI_BK1_IO0, SAI2_SD_A,<br>FMC_A16/FMC_CLE, EVENTOUT                                 | -                       |

| 59      | 81      | M1<br>0  | PD12                                                 | I/O      | FT            | -     | TIM4_CH1, LPTIM1_IN1, I2C4_SCL,<br>USART3_RTS, QUADSPI_BK1_IO1,<br>SAI2_FS_A, FMC_A17/FMC_ALE,<br>EVENTOUT         | -                       |

| 60      | 82      | M11      | PD13                                                 | I/O      | FT            | -     | TIM4_CH2, LPTIM1_OUT, I2C4_SDA,<br>QUADSPI_BK1_IO3, SAI2_SCK_A,<br>FMC_A18, EVENTOUT                               | -                       |

| -       | 83      | J10      | VSS                                                  | S        | I             | -     |                                                                                                                    | -                       |

| -       | 84      | J11      | VDD                                                  | S        | -             | -     | -                                                                                                                  | -                       |

| 61      | 85      | L12      | PD14                                                 | I/O      | FT            | -     | TIM4_CH3, UART8_CTS, FMC_D0,<br>EVENTOUT                                                                           | -                       |

| 62      | 86      | K13      | PD15                                                 | I/O      | FT            | -     | TIM4_CH4, UART8_RTS, FMC_D1,<br>EVENTOUT                                                                           | -                       |

| -       | -       | K12      | PJ6                                                  | I/O      | FT            | -     | LCD_R7, EVENTOUT                                                                                                   | -                       |

| -       | -       | J12      | PJ7                                                  | I/O      | FT            | -     | LCD_G0, EVENTOUT                                                                                                   | -                       |

## Pinouts and pin description

|          | Table 11. FMC pin definition |                  |        |       |  |  |  |  |  |  |

|----------|------------------------------|------------------|--------|-------|--|--|--|--|--|--|

| Pin name | NOR/PSRAM/SR<br>AM           | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |  |  |

| PF0      | A0                           | -                | -      | A0    |  |  |  |  |  |  |

| PF1      | A1                           | -                | -      | A1    |  |  |  |  |  |  |

| PF2      | A2                           | -                | -      | A2    |  |  |  |  |  |  |

| PF3      | A3                           | -                | -      | A3    |  |  |  |  |  |  |

| PF4      | A4                           | -                | -      | A4    |  |  |  |  |  |  |

| PF5      | A5                           | -                | -      | A5    |  |  |  |  |  |  |

| PF12     | A6                           | -                | -      | A6    |  |  |  |  |  |  |

| PF13     | A7                           | -                | -      | A7    |  |  |  |  |  |  |

| PF14     | A8                           | -                | -      | A8    |  |  |  |  |  |  |

| PF15     | A9                           | -                | -      | A9    |  |  |  |  |  |  |

| PG0      | A10                          | -                | -      | A10   |  |  |  |  |  |  |

| PG1      | A11                          | -                | -      | A11   |  |  |  |  |  |  |

| PG2      | A12                          | -                | -      | A12   |  |  |  |  |  |  |

| PG3      | A13                          | -                | -      | -     |  |  |  |  |  |  |

| PG4      | A14                          | -                | -      | BA0   |  |  |  |  |  |  |

| PG5      | A15                          | -                | -      | BA1   |  |  |  |  |  |  |

| PD11     | A16                          | A16              | CLE    | -     |  |  |  |  |  |  |

| PD12     | A17                          | A17              | ALE    | -     |  |  |  |  |  |  |

| PD13     | A18                          | A18              | -      | -     |  |  |  |  |  |  |

| PE3      | A19                          | A19              | -      | -     |  |  |  |  |  |  |

| PE4      | A20                          | A20              | -      | -     |  |  |  |  |  |  |

| PE5      | A21                          | A21              | -      | -     |  |  |  |  |  |  |

| PE6      | A22                          | A22              | -      | -     |  |  |  |  |  |  |

| PE2      | A23                          | A23              | -      | -     |  |  |  |  |  |  |

| PG13     | A24                          | A24              | -      | -     |  |  |  |  |  |  |

| PG14     | A25                          | A25              | -      | -     |  |  |  |  |  |  |

| PD14     | D0                           | DA0              | D0     | D0    |  |  |  |  |  |  |

| PD15     | D1                           | DA1              | D1     | D1    |  |  |  |  |  |  |

| PD0      | D2                           | DA2              | D2     | D2    |  |  |  |  |  |  |

| PD1      | D3                           | DA3              | D3     | D3    |  |  |  |  |  |  |

| PE7      | D4                           | DA4              | D4     | D4    |  |  |  |  |  |  |

| PE8      | D5                           | DA5              | D5     | D5    |  |  |  |  |  |  |

| PE9      | D6                           | DA6              | D6     | D6    |  |  |  |  |  |  |

| PE10     | D7                           | DA7              | D7     | D7    |  |  |  |  |  |  |

Table 11. FMC pin definition

| Table 11. FMC pin definition (continued) |                    |                  |        |       |  |  |  |  |

|------------------------------------------|--------------------|------------------|--------|-------|--|--|--|--|

| Pin name                                 | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |

| PE11                                     | D8                 | DA8              | D8     | D8    |  |  |  |  |

| PE12                                     | D9                 | DA9              | D9     | D9    |  |  |  |  |

| PE13                                     | D10                | DA10             | D10    | D10   |  |  |  |  |

| PE14                                     | D11                | DA11             | D11    | D11   |  |  |  |  |

| PE15                                     | D12                | DA12             | D12    | D12   |  |  |  |  |

| PD8                                      | D13                | DA13             | D13    | D13   |  |  |  |  |

| PD9                                      | D14                | DA14             | D14    | D14   |  |  |  |  |

| PD10                                     | D15                | DA15             | D15    | D15   |  |  |  |  |

| PH8                                      | D16                | -                | -      | D16   |  |  |  |  |

| PH9                                      | D17                | -                | -      | D17   |  |  |  |  |

| PH10                                     | D18                | -                | -      | D18   |  |  |  |  |

| PH11                                     | D19                | -                | -      | D19   |  |  |  |  |

| PH12                                     | D20                | -                | -      | D20   |  |  |  |  |

| PH13                                     | D21                | -                | -      | D21   |  |  |  |  |

| PH14                                     | D22                | -                | -      | D22   |  |  |  |  |

| PH15                                     | D23                | -                | -      | D23   |  |  |  |  |

| P10                                      | D24                | -                | -      | D24   |  |  |  |  |

| PI1                                      | D25                | -                | -      | D25   |  |  |  |  |

| PI2                                      | D26                | -                | -      | D26   |  |  |  |  |

| PI3                                      | D27                | -                | -      | D27   |  |  |  |  |

| PI6                                      | D28                | -                | -      | D28   |  |  |  |  |

| PI7                                      | D29                | -                | -      | D29   |  |  |  |  |

| PI9                                      | D30                | -                | -      | D30   |  |  |  |  |

| PI10                                     | D31                | -                | -      | D31   |  |  |  |  |

| PD7                                      | NE1                | NE1              | -      | -     |  |  |  |  |

| PG9                                      | NE2                | NE2              | NCE    | -     |  |  |  |  |

| PG10                                     | NE3                | NE3              | -      | -     |  |  |  |  |

| PG11                                     | -                  | -                | -      | -     |  |  |  |  |

| PG12                                     | NE4                | NE4              | -      | -     |  |  |  |  |

| PD3                                      | CLK                | CLK              | -      | -     |  |  |  |  |

| PD4                                      | NOE                | NOE              | NOE    | -     |  |  |  |  |

| PD5                                      | NWE                | NWE              | NWE    | -     |  |  |  |  |

| PD6                                      | NWAIT              | NWAIT            | NWAIT  | -     |  |  |  |  |

| PB7                                      | NADV               | NADV             | -      | -     |  |  |  |  |

Table 11. FMC pin definition (continued)

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 1.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

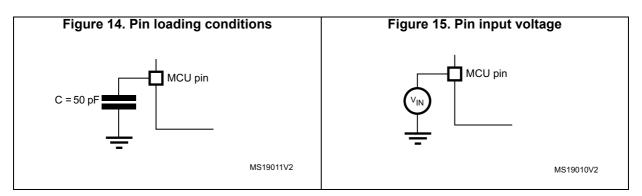

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 14*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 15*.

- 1. Guaranteed by design.

- 2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

## 6.3.6 Over-drive switching characteristics

When the over-drive mode switches from enabled to disabled or disabled to enabled, the system clock is stalled during the internal voltage set-up.

The over-drive switching characteristics are given in *Table 22*. They are sbject to general operating conditions for  $T_A$ .

| Symbol    | Parameter                        | Conditions                               | Min | Тур | Max | Unit |

|-----------|----------------------------------|------------------------------------------|-----|-----|-----|------|

| Tod_swen  |                                  | HSI                                      | -   | 45  | -   |      |

|           | Over_drive switch<br>enable time | HSE max for 4 MHz<br>and min for 26 MHz  | 45  | -   | 100 |      |

|           |                                  | External HSE<br>50 MHz                   | -   | 40  | -   |      |

|           |                                  | HSI                                      | -   | 20  | -   | μs   |

| Tod_swdis | Over_drive switch disable time   | HSE max for 4 MHz<br>and min for 26 MHz. | 20  | -   | 80  |      |

|           |                                  | External HSE<br>50 MHz                   | -   | 15  | -   |      |

Table 22. Over-drive switching characteristics<sup>(1)</sup>

1. Guaranteed by design.

## 6.3.7 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 17: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

- 2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

- 3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

- 4. Guaranteed by test in production.

#### Table 24. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART ON except prefetch / L1-cache ON) or SRAM on AXI (L1-cache ON), regulator ON

| Symbol Parameter | Parameter              | Conditions                                   | £ (MU-) | Turn                   |                        |                         | 11   |    |

|------------------|------------------------|----------------------------------------------|---------|------------------------|------------------------|-------------------------|------|----|

|                  | Conditions             | f <sub>HCLK</sub> (MHz)                      | Тур     | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |    |

|                  |                        |                                              | 216     | 186                    | 213                    | 234                     | -    |    |

|                  |                        |                                              | 200     | 172                    | 197                    | 217                     | 235  |    |

|                  |                        |                                              | 180     | 152                    | 175                    | 189                     | 202  |    |

|                  |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 168     | 135                    | 155                    | 168                     | 180  |    |

|                  |                        |                                              | 144     | 104                    | 119                    | 130                     | 140  |    |

|                  |                        |                                              | 60      | 46                     | 53                     | 64                      | 74   | mA |

|                  | Supply                 |                                              | 25      | 22                     | 25                     | 36                      | 47   |    |

| I <sub>DD</sub>  | current in<br>RUN mode |                                              | 216     | 108                    | 124                    | 146                     | -    | ШA |

|                  |                        |                                              | 200     | 100                    | 115                    | 135                     | 154  |    |

|                  |                        |                                              | 180     | 89                     | 102                    | 116                     | 129  |    |

|                  |                        |                                              | 168     | 79                     | 90                     | 103                     | 115  |    |

|                  |                        |                                              | 144     | 61                     | 69                     | 80                      | 90   |    |

|                  |                        |                                              | 60      | 27                     | 31                     | 42                      | 52   |    |

|                  |                        |                                              | 25      | 12                     | 15                     | 26                      | 36   |    |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

|                                                      |                                                               |                                                                                                          | Тур                       |                           | Max <sup>(1)</sup>        |                            |    |

|------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|----|

| Symbol                                               | Parameter                                                     | Conditions                                                                                               | 1 y p                     | v                         | Unit                      |                            |    |

|                                                      |                                                               |                                                                                                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C |    |

|                                                      | Supply current in Stop<br>mode, main regulator in<br>Run mode | Flash memory in Stop mode,<br>all oscillators OFF, no IWDG                                               | 0.45                      | 2.00                      | 14.00                     | 22.00                      |    |

|                                                      |                                                               | Flash memory in Deep power<br>down mode, all oscillators OFF                                             | 0.40                      | 2.00                      | 14.00                     | 22.00                      |    |

| IDD_STOP_NM<br>(normal mode)<br>Supply current in St | Supply current in Stop                                        | Flash memory in Stop mode, all<br>oscillators OFF, no IWDG                                               | 0.32                      | 1.50                      | 10.00                     | 18.00                      |    |

|                                                      |                                                               | Flash memory in Deep power<br>down mode, all oscillators OFF, no<br>IWDG                                 | 0.27                      | 1.50                      | 10.00                     | 18.00                      | mA |

| I <sub>DD_STOP_UDM</sub>                             | Supply current in Stop<br>mode, main regulator in             | Regulator in Run mode, Flash<br>memory in Deep power down<br>mode, all oscillators OFF, no<br>IWDG       | 0.15                      | 0.80                      | 4.00                      | 7.00                       |    |

| (under-anve Lov                                      | Low voltage and under-<br>drive modes                         | Regulator in Low-power mode,<br>Flash memory in Deep power<br>down mode, all oscillators OFF, no<br>IWDG | 0.10                      | 0.70                      | 4.00                      | 7.00                       |    |

#### Table 30. Typical and maximum current consumptions in Stop mode

1. Data based on characterization, tested in production.

pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{\text{DD}}$  is the MCU supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol            | Parameter     | Conditions                                                | I/O toggling<br>frequency (fsw)<br>MHz | Typ<br>V <sub>DD</sub> = 3.3 V | Typ<br>V <sub>DD</sub> = 1.8 V | Unit |     |     |  |

|-------------------|---------------|-----------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|------|-----|-----|--|

|                   |               | -                                                         | 2                                      | 0.1                            | 0.1                            |      |     |     |  |

|                   |               |                                                           | 8                                      | 0.4                            | 0.2                            |      |     |     |  |

|                   |               |                                                           | 25                                     | 1.1                            | 0.7                            |      |     |     |  |

|                   |               |                                                           | 50                                     | 2.4                            | 1.3                            |      |     |     |  |

|                   |               | $C_{EXT} = 0 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$ | 60                                     | 3.1                            | 1.6                            |      |     |     |  |

|                   |               | U - UNI + US + UEXT                                       | 84                                     | 4.3                            | 2.4                            | - mA |     |     |  |

|                   |               |                                                           | 90                                     | 4.9                            | 2.6                            |      |     |     |  |

|                   |               |                                                           | 100                                    | 5.4                            | 2.8                            |      |     |     |  |

|                   | I/O switching |                                                           | 108                                    | 5.6                            | -                              |      |     |     |  |

| I <sub>DDIO</sub> | Current       |                                                           | 2                                      | 0.2                            | 0.1                            |      |     |     |  |

|                   |               |                                                           | 8                                      | 0.6                            | 0.3                            |      |     |     |  |

|                   |               |                                                           | 25                                     | 1.8                            | 1.1                            |      |     |     |  |

|                   |               | C <sub>EXT</sub> = 10 pF                                  | 50                                     | 3.1                            | 2.3                            | 1    |     |     |  |

|                   |               | $C = C_{INT} + C_S + C_{EXT}$                             | 60                                     | 4.6                            | 3.4                            |      |     |     |  |

|                   |               |                                                           |                                        |                                |                                | 84   | 9.7 | 3.6 |  |

|                   |               |                                                           | 90                                     | 10.12                          | 5.2                            |      |     |     |  |

|                   |               |                                                           | 100                                    | 14.92                          | 5.4                            |      |     |     |  |

|                   |               |                                                           | 108                                    | 18.11                          | -                              |      |     |     |  |

| Table 33. Switching | a output I/O curren | t consumption <sup>(1)</sup> |

|---------------------|---------------------|------------------------------|

|                     | g output "O ourror  | it oonoumption               |

|                            |                                                             |                                       | I <sub>DD</sub> (Typ) <sup>(1)</sup>  |                                     | Unit   |

|----------------------------|-------------------------------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------|--------|

| Р                          | eripheral                                                   | Scale 1                               |                                       |                                     |        |

|                            | GPIOA<br>GPIOB<br>GPIOC                                     | 2.2<br>2.1<br>2.3                     | 2.1<br>1.8<br>2.0                     | 1.9<br>1.7<br>1.9                   |        |

|                            | GPIOD<br>GPIOE<br>GPIOF                                     | 2.2<br>2.2<br>2.2                     | 1.9<br>1.9<br>1.9                     | 1.8<br>1.8<br>1.8                   |        |

| -                          | GPIOG<br>GPIOH<br>GPIOI                                     | 2.1<br>2.0<br>2.3                     | 1.8<br>1.7<br>2.0                     | 1.7<br>1.7<br>1.7                   |        |

| AHB1<br>(up to<br>216 MHz) | GPIOJ<br>GPIOK<br>CRC                                       | 2.2<br>2.0<br>1.0                     | 1.9<br>1.7<br>0.9                     | 1.7<br>1.7<br>0.8                   | µA/MHz |

|                            | BKPSRAM<br>DMA1<br>DMA2                                     | 0.8<br>2.7 x N + 5.1<br>2.2 x N + 4.9 | 0.7<br>2.6 x N + 4.7<br>2.6 x N + 4.4 | 0.6<br>2.2 x N + 4<br>2.2 x N + 4.1 |        |

|                            | DMA2D<br>ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 87.1<br>42.1                          | 82.5<br>39.7                          | 69.6<br>34.1                        |        |

|                            | OTG_HS<br>OTG_HS+ULPI                                       | 57.5                                  | 54.4                                  | 47.6                                |        |

| AHB2                       | DCMI<br>CRYP                                                | 5.1<br>3.0                            | 4.7<br>2.6                            | 4.0<br>2.4                          |        |

| (up to<br>216 MHz)         | HASH<br>RNG<br>USB OTG FS                                   | 4.2<br>2.8<br>31.8                    | 3.7<br>2.4<br>29.9                    | 3.3<br>2.3<br>25.8                  | µA/MHz |

| AHB3<br>(up to             | FMC                                                         | 18.9                                  | 17.7                                  | 15.2                                | μΑ/MHz |

| (up to<br>216 MHz)         | QSPI                                                        | 23.2                                  | 21.8                                  | 18.5                                |        |

| В                          | us matrix <sup>(2)</sup>                                    | 21.06                                 | 20.3                                  | 17.2                                | µA/MHz |

| Table 34 | . Peripheral | current | consumption |

|----------|--------------|---------|-------------|

|----------|--------------|---------|-------------|

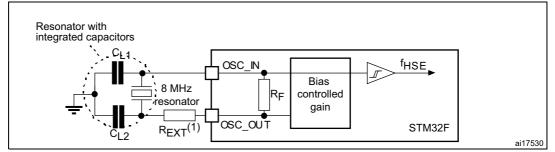

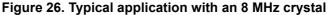

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 26*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                           | Table 39. LSE Oscillator characteristics (I <sub>LSE</sub> = 32.766 KHZ) * / |                                               |     |     |     |      |   |  |  |

|-------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|-----|-----|-----|------|---|--|--|

| Symbol                                    | Parameter                                                                    | Conditions                                    | Min | Тур | Мах | Unit |   |  |  |

|                                           |                                                                              | LSEDRV[1:0]=00<br>Low drive capability        | -   | 250 | -   |      |   |  |  |

|                                           |                                                                              | LSEDRV[1:0]=10<br>Medium low drive capability |     | -   | 300 | -    | 5 |  |  |

| I <sub>DD</sub> LSE current consumption - | LSEDRV[1:0]=01<br>Medium high drive capability                               | -                                             | 370 | -   | nA  |      |   |  |  |

|                                           |                                                                              | LSEDRV[1:0]=11<br>High drive capability       | -   | 480 | -   |      |   |  |  |

Table 39. LSE oscillator characteristics ( $f_{LSE}$  = 32.768 kHz) <sup>(1)</sup>

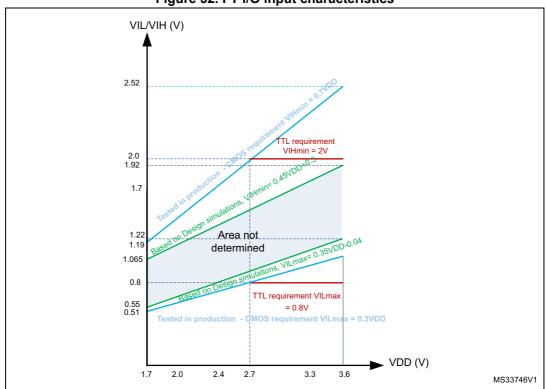

#### Figure 32. FT I/O input characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 14*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 14*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 16*. All I/Os are CMOS and TTL compliant.

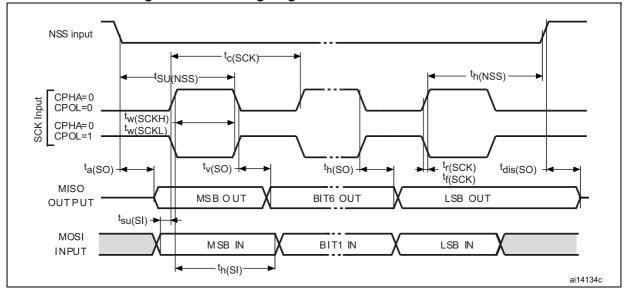

| Symbol   | Parameter                | Conditions                  | Min | Тур | Max | Unit |

|----------|--------------------------|-----------------------------|-----|-----|-----|------|

| tsu(MI)  | Data input actus tima    | Master mode                 | 5.5 | -   | -   |      |

| tsu(SI)  | Data input setup time    | Slave mode                  | 4   | -   | -   |      |

| th(MI)   | Data input hold time     | Master mode                 | 4   | -   | -   |      |

| th(SI)   | Data input hold time     | Slave mode                  | 2   | -   | -   |      |

| ta(SO)   | Data output access time  | access time Slave mode      |     | -   | 21  |      |

| tdis(SO) | Data output disable time | Slave mode                  | 5   | -   | 12  | ns   |

| tv(SO)   |                          | Slave mode 2.7≤VDD≤3.6V     | -   | 6.5 | 10  |      |

| 10(30)   | Data output valid time   | Slave mode 1.71≤VDD≤3.6V    | -   | 6.5 | 13  |      |

| tv(MO)   |                          | Master mode                 | -   | 2   | 4   |      |

| th(SO)   | Data output hold time    | Slave mode<br>1.71≤VDD≤3.6V | 5.5 | -   | -   |      |

| th(MO)   |                          | Master mode                 | 0   | -   | -   |      |

| Table 75. SPI c | lynamic | characteristics <sup>(1)</sup> | (continued) | ) |

|-----------------|---------|--------------------------------|-------------|---|

|-----------------|---------|--------------------------------|-------------|---|

1. Guaranteed by characterization results.

2. Excepting SPI1 with SCK IO pin mapped on PA5. In this configuration, Maximum achievable frequency is 40MHz.

Maximum Frequency of Slave Transmitter is determined by sum of Tv(SO) and Tsu(MI) intervals which has to fit into SCK level phase preceding the SCK sampling edge. This value can be achieved when it communicates with a Master having Tsu(MI)=0 while signal Duty(SCK)=50%.

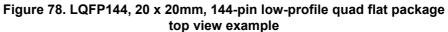

## LQFP144 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as ES or E or accompanied by an engineering sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

| package mechanical data (continued) |             |       |       |                       |        |        |  |

|-------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                              | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

| Symbol                              | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| G                                   | -           | 0.900 | -     | -                     | 0.0354 | -      |  |

| ddd                                 | -           | -     | 0.100 | -                     | -      | 0.0039 |  |

| eee                                 | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff                                 | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

# Table 113. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid arraypackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

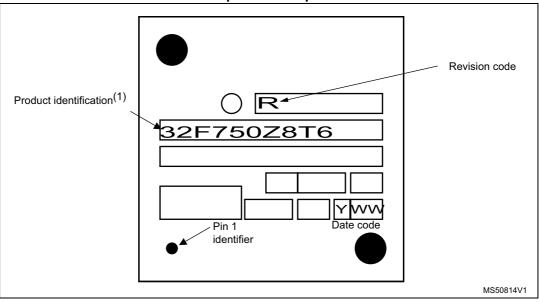

# Figure 80. TFBGA216, 13 x 13 x 0.8 mm thin fine-pitch ball grid array package recommended footprint

#### Table 114. TFBGA216 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.8                                                                   |

| Dpad              | 0.400 mm                                                              |

| Dsm               | 0.470 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.400 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.120 mm                                                              |

## Appendix A Recommendations when using internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

- The over-drive mode is not supported.

## A.1 Operating conditions

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                           | Possible Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup> | Conversion<br>time up to<br>1.2 Msps | 20 MHz                                                                                                  | 180 MHz with 8<br>wait states and<br>over-drive OFF                               | <ul> <li>No I/O compensation</li> </ul> | 8-bit erase and<br>program<br>operations only |

#### Table 117. Limitations depending on the operating power supply range

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

2. Thanks to the ART accelerator on ITCM interface and L1-cache on AXI interface, the number of wait states given here does not impact the execution speed from the Flash memory since the ART accelerator or L1-cache allows to achieve a performance equivalent to 0-wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.17.1: Internal reset ON).