Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx340f128ht-80v-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3:PIN NAMES: PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F128L, AND<br/>PIC32MX360F512L DEVICES

| Pin<br>Number | Full Pin Name        |

|---------------|----------------------|

| A1            | PMD4/RE4             |

| A2            | PMD3/RE3             |

| A3            | TRD0/RG13            |

| A4            | PMD0/RE0             |

| A5            | PMD8/RG0             |

| A6            | PMD10/RF1            |

| A7            | ENVREG               |

| A8            | Vss                  |

| A9            | IC5/PMD12/RD12       |

| A10           | OC3/RD2              |

| A11           | OC2/RD1              |

| B1            | No Connect (NC)      |

| B2            | RG15                 |

| B3            | PMD2/RE2             |

| B4            | PMD1/RE1             |

| B5            | TRD3/RA7             |

| B6            | PMD11/RF0            |

| B7            | VCAP/VCORE           |

| B8            | PMRD/CN14/RD5        |

| B0<br>B9      | OC4/RD3              |

| B10           | Vss                  |

| B10<br>B11    | SOSCO/T1CK/CN0/RC14  |

| C1            | PMD6/RE6             |

|               |                      |

| C2            |                      |

| C3            | TRD1/RG12            |

| C4            | TRD2/RG14            |

| C5            | TRCLK/RA6            |

| C6            |                      |

| C7            | PMD15/CN16/RD7       |

| C8            | OC5/PMWR/CN13/RD4    |

| C9            |                      |

| C10           | SOSCI/CN1/RC13       |

| C11           | IC4/PMCS1/PMA14/RD11 |

| D1            | T2CK/RC1             |

| D2            | PMD7/RE7             |

| D3            | PMD5/RE5             |

| D4            | Vss                  |

| D5            | Vss                  |

| D6            | No Connect (NC)      |

| D7            | PMD14/CN15/RD6       |

| D8            | PMD13/CN19/RD13      |

| D9            | OC1/RD0              |

| D10           | No Connect (NC)      |

| D11           | IC3/PMCS2/PMA15/RD10 |

| E1            | T5CK/RC4             |

| E2            | T4CK/RC3             |

| E3            | SCK2/PMA5/CN8/RG6    |

| E4            | T3CK/RC2             |

| E5            | Vdd                  |

| E6            | PMD9/RG1             |

| E7            | Vss                  |

| Pin<br>Number | Full Pin Name          |

|---------------|------------------------|

| E8            | INT4/RA15              |

| E9            | RTCC/IC1/RD8           |

| E10           | IC2/RD9                |

| E11           | INT3/RA14              |

| F1            | MCLR                   |

| F2            | SDO2/PMA3/CN10/RG8     |

| F3            | SS2/PMA2/CN11/RG9      |

| F4            | SDI2/PMA4/CN9/RG7      |

| F5            | Vss                    |

| F6            | No Connect (NC)        |

| F7            | No Connect (NC)        |

| F8            | VDD                    |

| F9            | OSC1/CLKI/RC12         |

| F10           | Vss                    |

| F11           | OSC2/CLKO/RC15         |

| G1            | INT1/RE8               |

| G2            | INT2/RE9               |

| G3            | TMS/RA0                |

| G4            | No Connect (NC)        |

| G5            | VDD                    |

| G6            | Vss                    |

| G7            | Vss                    |

| G8            | No Connect (NC)        |

| G9            | TDO/RA5                |

| G10           | SDA2/RA3               |

| G11           | TDI/RA4                |

| H1            | AN5/C1IN+/CN7/RB5      |

| H2            | AN4/C1IN-/CN6/RB4      |

| H3            | Vss                    |

| H4            | VDD                    |

| H5            | No Connect (NC)        |

| H6            | VDD                    |

| H7            | No Connect (NC)        |

| H8            | SDI1/RF7               |

| H9            | SCK1/INT0/RF6          |

| H10           | SCL1/RG2               |

| H11           | SCL2/RA2               |

| J1            | AN3/C2IN+/CN5/RB3      |

| J2            | AN2/C2IN-/SS1/CN4/RB2  |

| J3            | PGED2/AN7/RB7          |

| J4            | AVDD                   |

| J5            | AN11/PMA12/RB11        |

| J6            | TCK/RA1                |

| J7            | AN12/PMA11/RB12        |

| - J8          | No Connect (NC)        |

| - 19<br>- 10  | No Connect (NC)        |

| J10           | SD01/RF8               |

| J11           | SDO1/RG3               |

| K1            | PGEC1/AN1/CN3/RB1      |

| K1<br>K2      | PGED1/AN//CN3/RB1      |

| K2<br>K3      | VREF+/CVREF+/PMA6/RA10 |

| 110           |                        |

|            |            |            |              |            | PIC32     | 2MX440<br>2MX460<br>2MX460 | F256L               |           |           |           |              |

|------------|------------|------------|--------------|------------|-----------|----------------------------|---------------------|-----------|-----------|-----------|--------------|

|            | 1          | 2          | 3            | 4          | 5         | 6                          | 7                   | 8         | 9         | 10        | 11           |

| <b>x</b> ( | RE4        | RE3        | <b>R</b> G13 | RE0        | RG0       | RF1                        |                     | O<br>Vss  | RD12      | RD2       | RD1          |

| 3          | NC         | RG15       | RE2          | RE1        | RA7       | RF0                        | O<br>Vcore/<br>Vcap | RD5       | RD3       | O<br>Vss  | O<br>RC14    |

| ;          | RE6        | O<br>VDD   | RG12         | RG14       | RA6       | NC                         | RD7                 | RD4       | O<br>Vdd  | O<br>RC13 | RD11         |

|            | RC1        | RE7        | RE5          | O<br>Vss   | O<br>Vss  | NC                         | RD6                 | RD13      | RD0       | NC        | <b>R</b> D10 |

|            | RC4        | RC3        | RG6          | RC2        | O<br>Vdd  | RG1                        | ⊖<br>Vss            | RA15      | RD8       | RD9       | RA14         |

| -          | MCLR       | RG8        | RG9          | RG7        | O<br>Vss  | NC                         | NC                  |           | C<br>RC12 | O<br>Vss  | O<br>RC15    |

| •          | RE8        | RE9        | RA0          |            | VDD       | O<br>Vss                   | O<br>Vss            | NC        | RA5       | RA3       | RA4          |

| 1          | C<br>RB5   | C<br>RB4   | O<br>Vss     | O<br>Vdd   |           | O<br>VDD                   | NC                  | VBUS      | UUSB      | RG2       | RA2          |

| J          | C<br>RB3   | C<br>RB2   | C<br>RB7     |            | C<br>RB11 | C<br>RA1                   | O<br>RB12           | NC        | NC        | RF8       | C<br>RG3     |

| ¢          | C)<br>RB1  | O<br>RB0   | O<br>RA10    | C)<br>RB8  | NC        | RF12                       | O<br>RB14           |           | RD15      | RF3       | RF2          |

| -          | C)<br>RB6  | RA9        | AVss         | RB9        | RB10      | RF13                       | RB13                | C<br>RB15 | RD14      | RF4       | RF5          |

| L          | lote 1: Re | efer to Ta | ble 4 for    | full pin r | names.    |                            |                     |           |           |           |              |

# Pin Diagrams (Continued)

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide" DS51331

- "Using MPLAB<sup>®</sup> ICD 2" (poster) DS51265

- "MPLAB<sup>®</sup> ICD 2 Design Advisory" DS51566

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms. Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

### 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0** "**Oscillator Configuration**" for details).

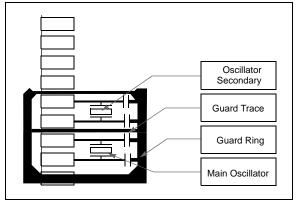

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |  |  |  |  |  |  |  |  |  |  |

|-------------------------|------------------------------------------------|---------|-------------|--|--|--|--|--|--|--|--|--|--|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |  |  |  |  |  |  |  |  |  |  |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |  |  |  |  |  |  |  |  |  |  |

| MUL                     | 16 bits                                        | 2       | 1           |  |  |  |  |  |  |  |  |  |  |

|                         | 32 bits                                        | 3       | 2           |  |  |  |  |  |  |  |  |  |  |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |  |  |  |  |  |  |  |  |  |  |

|                         | 16 bits                                        | 19      | 18          |  |  |  |  |  |  |  |  |  |  |

|                         | 24 bits                                        | 26      | 25          |  |  |  |  |  |  |  |  |  |  |

|                         | 32 bits                                        | 33      | 32          |  |  |  |  |  |  |  |  |  |  |

# TABLE 3-1:MIPS<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER<br/>MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the general purpose register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, multiply-add (MADD) and multiplysubtract (MSUB), are used to perform the multiplyaccumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (kernel, user and debug), and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                |

|--------------------|-------------------------|-------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count                                                   |

| 10                 | Reserved                | Reserved                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception                                       |

| 15                 | PRId                    | Processor identification and revision                                   |

| 15                 | EBASE                   | Exception vector base register                                          |

| 16                 | Config                  | Configuration register                                                  |

| 16                 | Config1                 | Configuration register 1                                                |

| 16                 | Config2                 | Configuration register 2                                                |

| 16                 | Config3                 | Configuration register 3                                                |

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | -                       | Function                                |

|--------------------|-------------------------|-----------------------------------------|

| 17-22              | Reserved                | Reserved                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception |

| 25-29              | Reserved                | Reserved                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register       |

#### TABLE 3-2:COPROCESSOR 0 REGISTERS (CONTINUED)

Note 1: Registers used in exception processing.

2: Registers used during debug.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 shows the exception types in order of priority.

#### TABLE 3-3: PIC32MX3XX/4XX FAMILY CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR)                                                                                                |

| DSS       | EJTAG Debug Single Step                                                                                                                 |

| DINT      | EJTAG Debug Interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input, or by setting the EjtagBrk bit in the ECR register |

| NMI       | Assertion of NMI signal                                                                                                                 |

| Interrupt | Assertion of unmasked hardware or software interrupt signal                                                                             |

| DIB       | EJTAG debug hardware instruction break matched                                                                                          |

| AdEL      | Fetch address alignment error<br>Fetch reference to protected address                                                                   |

| IBE       | Instruction fetch bus error                                                                                                             |

| DBp       | EJTAG Breakpoint (execution of SDBBP instruction)                                                                                       |

| Sys       | Execution of SYSCALL instruction                                                                                                        |

| Вр        | Execution of BREAK instruction                                                                                                          |

| RI        | Execution of a Reserved Instruction                                                                                                     |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled                                                            |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled                                                                      |

| Ov        | Execution of an arithmetic instruction that overflowed                                                                                  |

| Tr        | Execution of a trap (when trap condition is true)                                                                                       |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG Data Value Break on Store (address + value)                                            |

| AdEL      | Load address alignment error<br>Load reference to protected address                                                                     |

| AdES      | Store address alignment error<br>Store to protected address                                                                             |

| DBE       | Load or store bus error                                                                                                                 |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare                                                                             |

### INTERRUPT REGISTERS MAP FOR PIC32MX340F128H, PIC32MX340F256H, PIC32MX340F512H, PIC32MX340F128L, PIC32MX360F256L AND PIC32MX360F512L DEVICES ONLY<sup>(1)</sup> **TABLE 4-3**:

| SS                          |                        |               |         |         |          |         |                           |          |             | В                          | its      |                                         |           |                   |                         |                         |            |                 |            |  |      |

|-----------------------------|------------------------|---------------|---------|---------|----------|---------|---------------------------|----------|-------------|----------------------------|----------|-----------------------------------------|-----------|-------------------|-------------------------|-------------------------|------------|-----------------|------------|--|------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15   | 30/14   | 29/13    | 28/12   | 27/11                     | 26/10    | 25/9        | 24/8                       | 23/7     | 22/6                                    | 21/5      | 20/4              | 19/3                    | 18/2                    | 17/1       | 16/0            | All Resets |  |      |

|                             | INTCON                 | 31:16         | _       | —       | -        | —       | _                         | _        | _           | —                          | —        | _                                       | _         | —                 | —                       | _                       | —          | SS0             | 0000       |  |      |

| 1000                        | INTCON                 | 15:0          | _       | _       | _        | MVEC    |                           |          | TPC<2:0>    |                            | _        | _                                       | _         | INT4EP            | INT3EP                  | INT2EP                  | INT1EP     | INT0EP          | 0000       |  |      |

| 1010                        | INTSTAT <sup>(2)</sup> | 31:16         | —       | _       | —        | —       |                           | _        | —           | —                          | —        | _                                       | _         | —                 | —                       | _                       | —          | —               | 0000       |  |      |

| 1010                        |                        | 15:0          | —       | —       | —        | _       | —                         |          | SRIPL<2:0>  | •                          | —        | —                                       |           |                   | VEC                     | <5:0>                   |            |                 | 0000       |  |      |

| 1020                        | IPTMR                  | 31:16<br>15:0 |         |         |          |         |                           |          |             | IPTMR                      | <31:0>   |                                         |           |                   |                         |                         |            |                 | 0000       |  |      |

| 4000                        | 1500                   | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF  | U1TXIF  | U1RXIF                    | U1EIF    | SPI1RXIF    | SPI1TXIF                   | SPI1EIF  | OC5IF                                   | IC5IF     | T5IF              | INT4IF                  | OC4IF                   | IC4IF      | T4IF            | 0000       |  |      |

| 1030                        | IFS0                   | 15:0          | INT3IF  | OC3IF   | IC3IF    | T3IF    | INT2IF                    | OC2IF    | IC2IF       | T2IF                       | INT1IF   | OC1IF                                   | IC1IF     | T1IF              | INT0IF                  | CS1IF                   | CS0IF      | CTIF            | 0000       |  |      |

| 1040                        | IFS1                   | 31:16         |         | —       | _        | _       | _                         | —        | —           | FCEIF                      | _        |                                         |           |                   | DMA3IF                  | DMA2IF                  | DMA1IF     | DMA0IF          | 0000       |  |      |

| 1040                        | 151                    | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF  | I2C2SIF | I2C2BIF                   | U2TXIF   | U2RXIF      | U2EIF                      | SPI2RXIF | SPI2TXIF                                | SPI2EIF   | CMP2IF            | CMP1IF                  | PMPIF                   | AD1IF      | CNIF            | 0000       |  |      |

| 1060                        | IEC0                   | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE  | U1TXIE  | U1RXIE                    | U1EIE    | SPI1RXIE    | SPI1TXIE                   | SPI1EIE  | OC5IE                                   | IC5IE     | T5IE              | INT4IE                  | OC4IE                   | IC4IE      | T4IE            | 0000       |  |      |

| 1000                        | 1200                   | 15:0          | INT3IE  | OC3IE   | IC3IE    | T3IE    | INT2IE                    | OC2IE    | IC2IE       | T2IE                       | INT1IE   | OC1IE                                   | IC1IE     | T1IE              | INTOIE                  | CS1IE                   | CS0IE      | CTIE            | 0000       |  |      |

| 1070                        | IEC1                   | 31:16         | _       | —       | —        | _       | _                         | —        | —           | FCEIE                      | —        | —                                       | —         | _                 | DMA3IE                  | DMA2IE                  | DMA1IE     | DMA0IE          | 0000       |  |      |

| 10/0                        | 1201                   | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE  | _       | —                         | —        | —           | —                          | SPI2RXIE | SPI2TXIE                                | SPI2EIE   | CMP2IE            | CMP1IE                  | PMPIE                   | AD1IE      | CNIE            | 0000       |  |      |

| 1090                        | IPC0                   | 31:16         | —       | —       |          |         | INT0IP<2:0>               |          | INT0IS<1:0> |                            | —        | —                                       | —         |                   | CS1IP<2:0>              |                         |            | 6<1:0>          | 0000       |  |      |

|                             |                        | 15:0          | _       | —       | -        |         | CS0IP<2:0>                |          |             | CSOIS<1:0> — — — CTIP<2:0> |          |                                         | CTIS<1:0> |                   | 0000                    |                         |            |                 |            |  |      |

| 10A0                        | IPC1                   | 31:16         | _       | —       | -        |         | INT1IP<2:0>               | >        |             | S<1:0>                     | —        | —                                       | —         |                   | OC1IP<2:0>              | •                       | OC1IS<1:0> |                 | 0000       |  |      |

|                             |                        | 15:0          |         | -       | -        |         | IC1IP<2:0>                |          | IC1IS<1:0>  |                            | _        | -                                       | -         | T1IP<2:0>         |                         | T1IS<1:0><br>OC2IS<1:0> |            | 0000            |            |  |      |

| 10B0                        | IPC2                   | 31:16         | _       | _       |          |         | INT2IP<2:0>               | <b>`</b> |             | S<1:0>                     |          | _                                       | _         | OC2IP<2:0>        |                         |                         |            |                 | 0000       |  |      |

|                             |                        | 15:0          | _       | _       |          |         | IC2IP<2:0>                |          |             | 5<1:0>                     | _        | _                                       | _         | T2IP<2:0>         |                         | T2IS<1:0                |            | -               | 0000       |  |      |

| 10C0                        | IPC3                   | 31:16         | _       | _       |          |         | INT3IP<2:0>               |          |             | S<1:0>                     |          | _                                       | _         | OC3IP<2:0>        |                         | •                       |            | S<1:0>          | 0000       |  |      |

|                             | <br>                   | 15:0          | _       | —       | -        |         | IC3IP<2:0>                |          |             | S<1:0>                     | _        | _                                       | _         | T3IP<2:0>         |                         |                         |            | <1:0>           | 0000       |  |      |

| 10D0                        | IPC4                   | 31:16<br>15:0 |         | _       |          |         | INT4IP<2:0><br>IC4IP<2:0> |          |             | S<1:0><br>S<1:0>           |          |                                         |           |                   | OC4IP<2:0><br>T4IP<2:0> |                         |            | S<1:0><br><1:0> | 0000       |  |      |

|                             |                        | 31:16         |         |         |          |         | SPI1IP<2:0>               |          |             | S<1:0>                     |          |                                         |           |                   | OC5IP<2:0>              |                         |            | <1.0><br>S<1:0> | 0000       |  |      |

| 10E0                        | IPC5                   | 15:0          |         |         | _        |         | IC5IP<2:0>                | ·        | -           | S<1:0>                     | _        | _                                       | _         |                   | T5IP<2:0>               | •                       |            | <1:0>           | 0000       |  |      |

|                             |                        | 31:16         |         |         |          |         | AD1IP<2:0>                |          |             | S<1:0>                     | _        |                                         |           |                   | CNIP<2:0>               |                         |            | <1:0>           | 0000       |  |      |

| 10F0                        | IPC6                   | 15:0          | _       | _       | _        |         | I2C1IP<2:0>               |          |             | S<1:0>                     | _        | _                                       | _         |                   | U1IP<2:0>               |                         |            | <1:0>           | 0000       |  |      |

|                             |                        | 31:16         | _       | _       | _        |         | SPI2IP<2:0>               |          |             | S<1:0>                     | _        | _                                       | _         | (                 | CMP2IP<2:0              | >                       |            | S<1:0>          | 0000       |  |      |

| 1100                        | IPC7                   | 15:0          | _       | _       | _        |         | CMP1IP<2:0                |          |             | S<1:0>                     |          |                                         | _         | PMPIP<2:0>        |                         |                         |            | S<1:0>          | 0000       |  |      |

|                             |                        | 31:16         | _       | _       | _        |         | RTCCIP<2:0:               |          |             | S<1:0>                     | _        | _                                       | _         |                   | SCMIP<2:0               |                         |            | S<1:0>          | 0000       |  |      |

| 1110                        | IPC8                   | 15:0          | _       | _       | _        |         | I2C2IP<2:0>               |          |             | S<1:0>                     | _        | _                                       | _         |                   |                         | U2IP<2:0>               |            |                 | U2IS<1:0>  |  | 0000 |

|                             | 1000                   | 31:16         | _       | _       | <u> </u> |         | DMA3IP<2:0>               |          |             | DMA3IS<1:0>                |          | A3IP<2:0> DMA3IS<1:0> — — — DMA2IP<2:0> |           |                   |                         | DMA2IS<1:0>             |            | 0000            |            |  |      |

| 1120                        | IPC9                   | 15:0          | _       | _       | _        | C       | DMA1IP<2:0                | >        | DMA1        | S<1:0>                     | _        | _                                       | _         | - DMA0IP<2:0> DMA |                         | DMA0I                   | S<1:0>     | 0000            |            |  |      |

| 44.40                       |                        | 31:16         |         | _       | _        | _       |                           |          |             |                            | _        |                                         | _         |                   | _                       |                         | _          | —               | 0000       |  |      |

| 1140                        | IPC11                  | 15:0          | _       | _       | _        | _       | _                         | _        | _           | _                          | -        | _                                       | _         |                   | FCEIP<2:0>              |                         | FCEIS      | S<1:0>          | 0000       |  |      |

PIC32MX3XX/4XX

Legend: Note 1:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated CLR, SET, and INV registers. 2:

### TABLE 4-13: ADC REGISTERS MAP (CONTINUED)

| ess                         |                  |           |       |                                    |       |       |       |       |        | В           | its       |           |      |      |      |      |      |      |            |

|-----------------------------|------------------|-----------|-------|------------------------------------|-------|-------|-------|-------|--------|-------------|-----------|-----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8        | 23/7      | 22/6      | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9110                        | ADC1BUFA         | 31:16     |       | ADC Result Word A (ADC1BUFA<31:0>) |       |       |       |       |        |             |           |           |      |      |      |      |      |      | 0000       |

| -                           |                  | 15:0      |       |                                    |       |       |       |       |        |             |           |           |      |      |      |      |      |      | 0000       |

| 0120                        | ADC1BUFB         | 31:16     |       | ADC Result Word B (ADC1BUFB<31:0>) |       |       |       |       |        |             |           |           |      |      |      |      |      | 0000 |            |

| 9120                        | ADCIBUEB         | 15:0      |       | ADC Result Word B (ADC1B0FB<31:0>) |       |       |       |       |        |             |           |           |      |      |      |      | 0000 |      |            |

| 0400                        |                  | 31:16     |       |                                    |       |       |       |       |        |             |           |           |      |      |      |      |      |      | 0000       |

| 9130                        | ADC1BUFC         | 15:0      |       |                                    |       |       |       |       | ADC RE | suit word C | (ADC1BUFC | ><31:0>)  |      |      |      |      |      |      | 0000       |

| 04.40                       |                  | 31:16     |       |                                    |       |       |       |       |        |             |           |           |      |      |      |      |      |      | 0000       |

| 9140                        | ADC1BUFD         | 15:0      |       |                                    |       |       |       |       | ADC RE | suit word D | (ADC1BUFE | )<31:0>)  |      |      |      |      |      |      | 0000       |

| 0450                        |                  | 31:16     |       |                                    |       |       |       |       |        |             |           |           |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 15:0      |       |                                    |       |       |       |       | ADC Re | Suit Word E | (ADC1BUFE | :<31:0>)  |      |      |      |      |      |      | 0000       |

| 0400                        |                  | 31:16     |       |                                    |       |       |       |       |        |             |           | - 24.0. ) |      |      |      |      |      |      | 0000       |

| 9160                        | ADC1BUFF         | 15:0      |       |                                    |       |       |       |       | ADC RE | Suit Word F | (ADC1BUFF | <31:0>)   |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 4-37: PARALLEL MASTER PORT REGISTERS MAP<sup>(1)</sup>

| ess                         |                  |           |                                                                |           |            |               |         |        |              | Bi                | ts         |        |       |        |      |       |             |      |            |

|-----------------------------|------------------|-----------|----------------------------------------------------------------|-----------|------------|---------------|---------|--------|--------------|-------------------|------------|--------|-------|--------|------|-------|-------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15                                                          | 30/14     | 29/13      | 28/12         | 27/11   | 26/10  | 25/9         | 24/8              | 23/7       | 22/6   | 21/5  | 20/4   | 19/3 | 18/2  | 17/1        | 16/0 | All Resets |

| 7000                        | PMCON            | 31:16     | _                                                              | _         | _          | _             | —       | -      | —            | _                 | _          | _      | _     |        | —    |       |             | _    | 0000       |

| 1000                        |                  | 15:0      | ON                                                             | —         | SIDL       | ADRML         | JX<1:0> | PMPTTL | PTWREN       | PTRDEN            | CSF<       | <1:0>  | ALP   | CS2P   | CS1P |       | WRSP        | RDSP | 0000       |

| 7010                        | PMMODE           | 31:16     | 16                                                             |           |            |               |         |        |              |                   |            |        |       | _      | 0000 |       |             |      |            |

| 7010                        |                  | 15:0      | BUSY IRQM<1:0> INCM<1:0>                                       |           |            |               |         | MODE16 | MODE         | E<1:0> WAITB<1:0> |            |        | WAITM | /<3:0> |      | WAITE | 0000        |      |            |

| 7020                        | PMADDR           | 31:16     | -                                                              | -         |            | -             | -       |        | -            | -                 | -          | -      |       |        | -    |       |             | -    | 0000       |

| 1020                        | FINADDR          | 15:0      | CS2EN/A15                                                      | CS1EN/A14 |            |               |         |        |              |                   | ADDR       | <13:0> |       |        |      |       |             |      | 0000       |

| 7030                        | PMDOUT           | 31:16     |                                                                |           |            |               |         |        |              | DATAOU            | T-31:0>    |        |       |        |      |       |             |      | 0000       |

| 1050                        | T MIDOUT         | 15:0      |                                                                |           |            |               |         |        |              | DAIAOU            | 1<31.02    |        |       |        |      |       |             |      | 0000       |

| 7040                        | PMDIN            | 31:16     |                                                                |           |            |               |         |        |              | DATAIN            | ~31.0>     |        |       |        |      |       |             |      | 0000       |

| 7040                        |                  | 15:0      |                                                                |           |            |               |         |        |              | DATAIN            | <01.02     |        |       |        |      |       |             |      | 0000       |

| 7050                        | PMAEN            | 31:16     | -                                                              | -         |            | -             | -       |        | -            | -                 | -          | -      |       |        | -    |       |             | -    | 0000       |

| 7050                        | FINALIN          | 15:0      |                                                                |           |            |               |         |        |              | PTEN<             | :15:0>     |        |       |        |      |       |             |      | 0000       |

| 7060                        | PMSTAT           | 31:16     |                                                                |           | _          | _             | —       | _      | —            |                   |            | _      | _     | _      | —    | _     | _           |      | 0000       |

| 1000                        | FINISTAL         | 15:0      | IBF IBOV IB3F IB2F IB1F IB0F OBE OBUF OB3E OB2E OB1E OB0E 008F |           |            |               |         |        |              |                   |            |        |       |        | 008F |       |             |      |            |

| Legend                      | 1: x = u         |           |                                                                | -         | nimplement | ed. read as ' |         |        | wn in hexade |                   | <b>UDE</b> | 0201   |       |        | CDOL | ODEL  | <b>UDIE</b> | CDOL | 0001       |

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

### TABLE 4-38: PROGRAMMING AND DIAGNOSTICS REGISTERS MAP

| ess                        |                  | ۵         |       |       |       |       |       |       |      | В    | ts   |      |      |      |        |       |      |      | 6          |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|--------|-------|------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3   | 18/2  | 17/1 | 16/0 | All Resets |

| F200                       | DDPCON           | 31:16     | —     | _     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —      | —     | —    | _    | 0000       |

| F200                       | DDFCON           | 15:0      |       |       | _     | _     | —     | —     | _    | —    | _    | _    | _    | —    | JTAGEN | TROEN | _    |      | 0008       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# PIC32MX3XX/4XX

NOTES:

# 11.0 USB ON-THE-GO (OTG)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS61126) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 fullspeed and low-speed embedded host, full-speed device, or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32MX USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers, and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32MX USB module includes the following features:

- USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB OTG Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- Integrated USB Transceiver

- Transaction Handshaking Performed by Hardware

- Endpoint Buffering Anywhere in System RAM

- Integrated DMA to Access System RAM and Flash

Note: The implementation and use of the USB specifications, as well as other third-party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# PIC32MX3XX/4XX

NOTES:

# PIC32MX3XX/4XX

NOTES:

# 18.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C<sup>TM</sup>)" (DS61116) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and accessing hits

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram. The PIC32MX3XX/4XX devices have up to two  $l^2C$  interface modules, denoted as I2C1 and I2C2. Each  $l^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module, 'I2Cx' (x = 1 or 2), offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave Operation.

- I<sup>2</sup>C Slave Mode Supports 7 and 10-bit Address.

- I<sup>2</sup>C Master Mode Supports 7 and 10-bit Address.

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-master Operation; Detects Bus Collision and Arbitrates Accordingly.

- Provides Support for Address Bit Masking.

# PIC32MX3XX/4XX

NOTES:

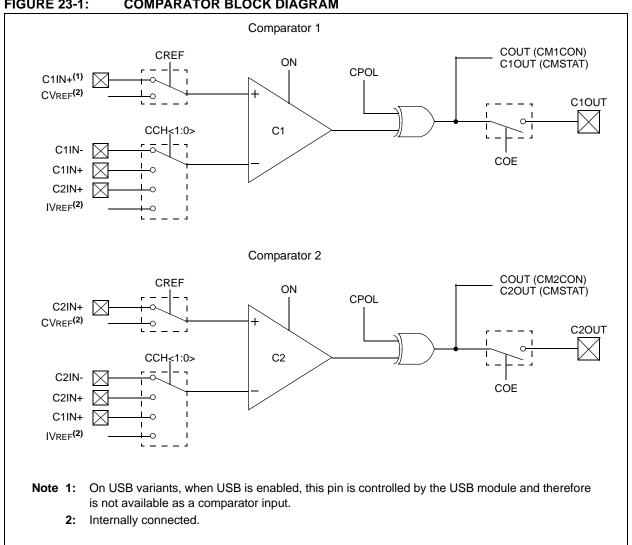

#### 23.0 COMPARATOR

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. Refer to Section 19. "Comparator" (DS61110) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC32MX3XX/4XX Analog Comparator module contains one or more comparator(s) that can be configured in a variety of ways.

Following are some of the key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be inverted

- · Selectable interrupt generation

A block diagram of the comparator module is illustrated in Figure 23-1.

#### FIGURE 23-1: COMPARATOR BLOCK DIAGRAM

#### **DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)** REGISTER 26-1:

bit 19-12 PWP<7:0>: Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. 11111111 = Disabled 11111110 = 0xBD00 0FFF 11111101 = 0xBD00\_1FFF 11111100 = 0xBD00\_2FFF 11111011 = 0xBD00\_3FFF 11111010 = 0xBD00\_4FFF 11111001 = 0xBD00 5FFF 11111000 = 0xBD00\_6FFF 11110111 = 0xBD00\_7FFF 11110110 = 0xBD00\_8FFF 11110101 = 0xBD00\_9FFF 11110100 = 0xBD00\_AFFF 11110011 = 0xBD00 BFFF 11110010 = 0xBD00\_CFFF 11110001 = 0xBD00\_DFFF 11110000 = 0xBD00\_EFFF 11101111 = 0xBD00\_FFFF 01111111 = 0xBD07\_FFFF bit 11-4 Reserved: Write '1' ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit 1 = PGEC2/PGED2 pair is used 0 = PGEC1/PGED1 pair is used Reserved: Write '1' DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled) bit 1-0

11 = Debugger disabled

bit 3

bit 2

- 10 =Debugger enabled

- 01 = Reserved (same as '11' setting) 00 = Reserved (same as '11' setting)

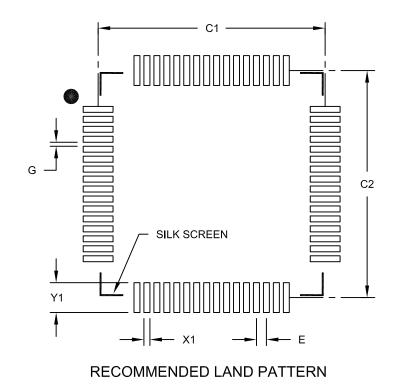

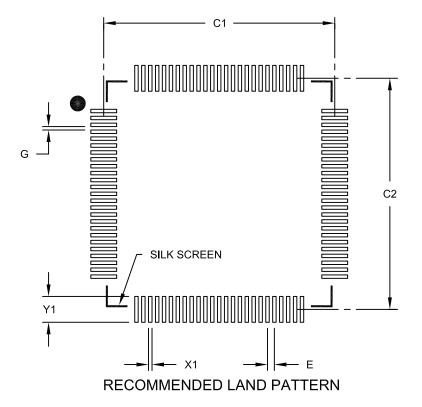

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Contact Pitch            | E  |             | 0.50 BSC |      |

| Contact Pad Spacing      | C1 |             | 11.40    |      |

| Contact Pad Spacing      | C2 |             | 11.40    |      |

| Contact Pad Width (X64)  | X1 |             |          | 0.30 |

| Contact Pad Length (X64) | Y1 |             |          | 1.50 |

| Distance Between Pads    | G  | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

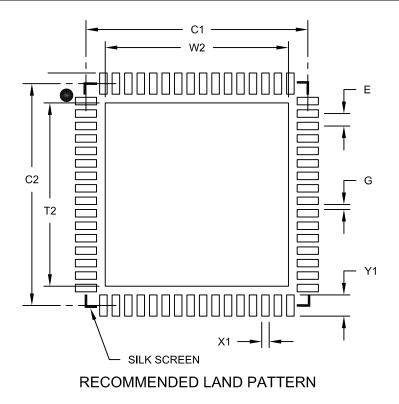

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.50 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 7.35 |

| Optional Center Pad Length | T2 |             |      | 7.35 |

| Contact Pad Spacing        | C1 |             | 8.90 |      |

| Contact Pad Spacing        | C2 |             | 8.90 |      |

| Contact Pad Width (X64)    | X1 |             |      | 0.30 |

| Contact Pad Length (X64)   | Y1 |             |      | 0.85 |

| Distance Between Pads      | G  | 0.20        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2149A

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                     |    | MILLIMETERS |          |      |

|---------------------------|----|-------------|----------|------|

| Dimension Limits          |    | MIN         | NOM      | MAX  |

| Contact Pitch             | Е  |             | 0.40 BSC |      |

| Contact Pad Spacing       | C1 |             | 13.40    |      |

| Contact Pad Spacing       | C2 |             | 13.40    |      |

| Contact Pad Width (X100)  | X1 |             |          | 0.20 |

| Contact Pad Length (X100) | Y1 |             |          | 1.50 |

| Distance Between Pads     | G  | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

# TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                            | Update Description                                                                                                                                                                             |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "Special Features"         | Modified bit names and locations in <b>Register 26-5</b> " <b>DEVID: Device and Revision ID Register</b> ".                                                                                    |

|                                         | Replaced "TSTARTUP" with "TPU", and "64-ms nominal delay" with "TPWRT", in Section 26.3.1 "On-Chip Regulator and POR".                                                                         |

|                                         | The information that appeared in the Watchdog Timer and the Programming and Diagnostics sections of 61143E version of this data sheet has been incorporated into the Special Features section: |

|                                         | <ul> <li>Section 26.2 "Watchdog Timer (WDT)"</li> </ul>                                                                                                                                        |

|                                         | Section 26.4 "Programming and Diagnostics"                                                                                                                                                     |

| Section 29.0 "Electrical                | Added the 64-Lead QFN package to Table 29-3.                                                                                                                                                   |

| Characteristics"                        | Updated data in Table 29-5.                                                                                                                                                                    |

|                                         | Updated data in Table 29-7.                                                                                                                                                                    |

|                                         | Updated data in Table 29-4, Table 29-5, Table 29-7 and Table 29-8.                                                                                                                             |

|                                         | Updated data in Table 29-11.                                                                                                                                                                   |

|                                         | Added OS42 parameter to Table 29-17.                                                                                                                                                           |

|                                         | Replaced Table 29-23.                                                                                                                                                                          |

|                                         | Replaced Table 29-24.                                                                                                                                                                          |

|                                         | Replaced Table 29-25.                                                                                                                                                                          |

|                                         | Updated Table 29-36.                                                                                                                                                                           |

| Section 30.0 "Packaging<br>Information" | Added 64-Lead QFN package marking information to <b>Section 30.1 "Package Marking Information"</b> .                                                                                           |

|                                         | Added the 64-Lead QFN (MR) package drawing and land pattern to <b>Section 30.2 "Package Details"</b> .                                                                                         |

| "Product Identification System"         | Added the MR package designator for the 64-Lead (9x9x0.9) QFN.                                                                                                                                 |