Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | -                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx340f128lt-80i-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the PIC32MX3XX/4XX devices.

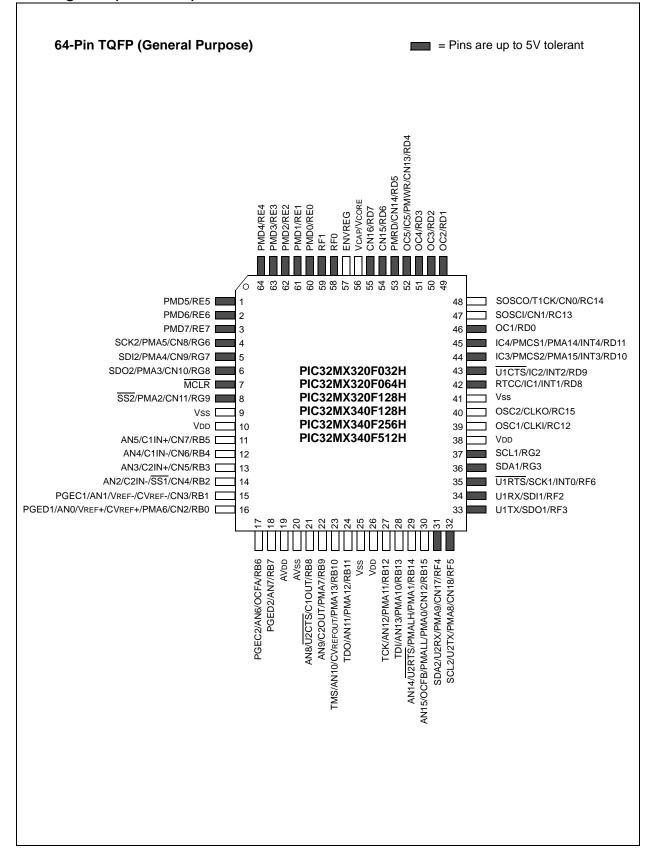

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX3XX/4XX family of devices.

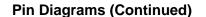

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

|          | Pin                | Number <sup>(</sup> |                 |             | CONTINU        |                                                                                            |

|----------|--------------------|---------------------|-----------------|-------------|----------------|--------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/TQFP | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type | Buffer<br>Type | Description                                                                                |

| TMS      | 23                 | 17                  | G3              | I           | ST             | JTAG Test mode select pin.                                                                 |

| ТСК      | 27                 | 38                  | J6              | I           | ST             | JTAG test clock input pin.                                                                 |

| TDI      | 28                 | 60                  | G11             | I           | ST             | JTAG test data input pin.                                                                  |

| TDO      | 24                 | 61                  | G9              | 0           | _              | JTAG test data output pin.                                                                 |

| RTCC     | 42                 | 68                  | E9              | 0           | —              | Real-Time Clock Alarm Output.                                                              |

| CVREF-   | 15                 | 28                  | L2              | I           | Analog         | Comparator Voltage Reference (low).                                                        |

| CVREF+   | 16                 | 29                  | K3              | I           | Analog         | Comparator Voltage Reference (high).                                                       |

| CVREFOUT | 23                 | 34                  | L5              | 0           | Analog         | Comparator Voltage Reference Output.                                                       |

| C1IN-    | 12                 | 21                  | H2              | I           | Analog         | Comparator 1 Negative Input.                                                               |

| C1IN+    | 11                 | 20                  | H1              | I           | Analog         | Comparator 1 Positive Input.                                                               |

| C1OUT    | 21                 | 32                  | K4              | 0           | _              | Comparator 1 Output.                                                                       |

| C2IN-    | 14                 | 23                  | J2              | I           | Analog         | Comparator 2 Negative Input.                                                               |

| C2IN+    | 13                 | 22                  | J1              | I           | Analog         | Comparator 2 Positive Input.                                                               |

| C2OUT    | 22                 | 33                  | L4              | 0           | _              | Comparator 2 Output.                                                                       |

| PMA0     | 30                 | 44                  | L8              | I/O         | TTL/ST         | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 29                 | 43                  | K7              | I/O         | TTL/ST         | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | 8                  | 14                  | F3              | 0           | _              | Parallel Master Port Address (De-multiplexed Master                                        |

| PMA3     | 6                  | 12                  | F2              | 0           | _              | Modes).                                                                                    |

| PMA4     | 5                  | 11                  | F4              | 0           | _              |                                                                                            |

| PMA5     | 4                  | 10                  | E3              | 0           |                |                                                                                            |

| PMA6     | 16                 | 29                  | K3              | 0           | _              |                                                                                            |

| PMA7     | 22                 | 28                  | L2              | 0           |                |                                                                                            |

| PMA8     | 32                 | 50                  | L11             | 0           | _              |                                                                                            |

| PMA9     | 31                 | 49                  | L10             | 0           |                |                                                                                            |

| PMA10    | 28                 | 42                  | L7              | 0           | _              |                                                                                            |

| PMA11    | 27                 | 41                  | J7              | 0           |                |                                                                                            |

| PMA12    | 24                 | 35                  | J5              | 0           | _              | 1                                                                                          |

| PMA13    | 23                 | 34                  | L5              | 0           |                |                                                                                            |

| PMA14    | 45                 | 71                  | C11             | 0           | —              | 1                                                                                          |

| PMA15    | 44                 | 70                  | D11             | 0           | —              | 1                                                                                          |

| PMCS1    | 45                 | 71                  | C11             | 0           | _              | Parallel Master Port Chip Select 1 Strobe.                                                 |

|          | 44                 | 70                  | D11             | 0           | _              | Parallel Master Port Chip Select 2 Strobe.                                                 |

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED |

|-----------------------------------------------|

|-----------------------------------------------|

ST = Schmitt Trigger input with CMOS levels O = Output TTL = TTL input buffer

I = Input

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

## 4.0 MEMORY ORGANIZATION

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Memory Organization" (DS61115) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX3XX/4XX microcontrollers provide 4 GB of unified virtual memory address space. All memory regions including program, data memory, SFRs and Configuration registers reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX3XX/4XX to execute from data memory.

## 4.1 Key Features

- 32-bit native data width

- Separate User and Kernel mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable and non-cacheable address regions

## 4.2 PIC32MX3XX/4XX Memory Layout

PIC32MX3XX/4XX microcontrollers implement two address spaces: Virtual and Physical. All hardware resources such as program memory, data memory and peripherals are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by peripherals such as DMA and Flash controller that access memory independently of CPU.

# TABLE 4-9: OUTPUT COMPARE1-5 REGISTERS MAP<sup>(1)</sup>

| ess                         |                  |               |                  |       |       |       |       |       |      | Bi    | ts     |      |      |       |        |      |            |      |            |

|-----------------------------|------------------|---------------|------------------|-------|-------|-------|-------|-------|------|-------|--------|------|------|-------|--------|------|------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15            | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1       | 16/0 | All Resets |

|                             | OC1CON           | 31:16         |                  |       |       |       |       |       |      |       |        |      |      | 0000  |        |      |            |      |            |

|                             |                  | 15:0          | ON               | —     | SIDL  | —     | —     | —     | —    | —     | —      | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000       |

| 3010                        | OC1R             | 31:16<br>15:0 |                  |       |       |       |       |       |      | OC1R- | <31:0> |      |      |       |        |      |            |      | xxxx       |

| 3020                        | OC1RS            | 31:16         |                  |       |       |       |       |       |      | OC1RS | <31:0> |      |      |       |        |      |            |      | xxxx       |

|                             |                  | 15:0          |                  |       |       |       |       |       |      |       |        |      |      |       |        |      |            |      | xxxx       |

| 3200                        | OC2CON           | 31:16<br>15:0 |                  |       |       |       |       |       |      |       | 0000   |      |      |       |        |      |            |      |            |

|                             |                  | 31:16         | UN               | _     | SIDL  | —     | _     | _     | _    | —     |        | _    | 0032 | OCFLI | OCISEL |      | 00101<2.0> |      | 0000       |

| 3210                        | OC2R             | 15:0          |                  |       |       |       |       |       |      | OC2R  | <31:0> |      |      |       |        |      |            |      | xxxx       |

| 3220                        | OC2RS            | 31:16<br>15:0 | 6<br>OC2RS<31:0> |       |       |       |       |       |      |       | xxxx   |      |      |       |        |      |            |      |            |

|                             |                  | 31:16         |                  |       |       |       |       |       |      | xxxx  |        |      |      |       |        |      |            |      |            |

| 3400                        | OC3CON           | 15:0          | ON               | _     | SIDL  | _     | _     | _     | _    | _     | _      | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000       |

| 3410                        | OC3R             | 31:16         |                  |       |       |       |       |       |      | OC3R• | :31:0> |      |      |       | 1      |      |            |      | xxxx       |

| 0.10                        | 00011            | 15:0          |                  |       |       |       |       |       |      | 00011 |        |      |      |       |        |      |            |      | XXXX       |

| 3420                        | OC3RS            | 31:16<br>15:0 |                  |       |       |       |       |       |      | OC3RS | <31:0> |      |      |       |        |      |            |      | xxxx       |

| 3600                        | OC4CON           | 31:16         | _                |       | _     | _     | _     | _     | _    | _     | —      |      | _    | —     | —      |      | —          | _    | 0000       |

| 3000                        |                  | 15:0          | ON               | —     | SIDL  | —     | _     | _     | _    | _     | —      |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000       |

| 3610                        | OC4R             | 31:16<br>15:0 |                  |       |       |       |       |       |      | OC4R- | <31:0> |      |      |       |        |      |            |      | XXXX       |

|                             |                  |               |                  |       |       |       |       |       |      |       |        |      |      |       |        |      |            |      | xxxx       |

| 3620                        | OC4RS            | 31:16<br>15:0 |                  |       |       |       |       |       |      | OC4RS | <31:0> |      |      |       |        |      |            |      | xxxx       |

| 3800                        | OC5CON           | 31:16         | 6 00             |       |       |       |       |       | 0000 |       |        |      |      |       |        |      |            |      |            |

|                             |                  | 15:0          |                  |       |       |       |       |       |      | 0000  |        |      |      |       |        |      |            |      |            |

| 3810                        | OC5R             | 31:16         |                  |       |       |       |       |       |      |       | XXXX   |      |      |       |        |      |            |      |            |

|                             |                  | 15:0<br>31:16 | 1.16             |       |       |       |       |       |      | xxxx  |        |      |      |       |        |      |            |      |            |

| 3820                        | OC5RS            | 15:0          |                  |       |       |       |       |       |      | OC5RS | <31:0> |      |      |       |        |      |            |      | XXXX       |

Legend:

x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## TABLE 4-13: ADC REGISTERS MAP

| SS                          |                        |               |                                    |        |        |        |        |           |           | Bi           | ts        |           |       |         |        |       |        |       |            |

|-----------------------------|------------------------|---------------|------------------------------------|--------|--------|--------|--------|-----------|-----------|--------------|-----------|-----------|-------|---------|--------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15                              | 30/14  | 29/13  | 28/12  | 27/11  | 26/10     | 25/9      | 24/8         | 23/7      | 22/6      | 21/5  | 20/4    | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

| 9000                        | AD1CON1 <sup>(1)</sup> | 31:16         | _                                  | —      | —      | _      | _      | —         | —         | —            | _         | —         | —     | —       | _      |       | —      | —     | 0000       |

|                             |                        | 15:0          | ON                                 | —      | SIDL   | _      | _      |           | FORM<2:0> |              |           | SSRC<2:0> |       | CLRASAM | _      | ASAM  | SAMP   | DONE  | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup> | 31:16         | —                                  | —      | —      | —      |        | —         | —         | —            | -         | —         | —     | —       | —      | —     | —      | —     | 0000       |

| 0010                        |                        | 15:0          | VCFG2                              | VCFG1  | VCFG0  | OFFCAL | -      | CSCNA     | —         | —            | BUFS      | —         |       | SMPI    | <3:0>  |       | BUFM   | ALTS  | 0000       |

| 9020                        | AD1CON3 <sup>(1)</sup> | 31:16         | —                                  | —      | —      | —      | —      | —         | —         | —            | —         | —         | —     | —       | -      | —     | —      | —     | 0000       |

| 0020                        |                        | 15:0          | ADRC                               | —      | —      |        |        | SAMC<4:0> |           |              |           |           |       | ADCS    | s<7:0> |       |        |       | 0000       |

| 9040                        | AD1CHS(1)              | 31:16         | CH0NB                              | —      | —      | —      |        | CH0SI     | B<3:0>    |              | CH0NA     | —         | —     | —       |        | CH0S  | A<3:0> |       | 0000       |

|                             |                        | 15:0          | _                                  | —      | —      | _      | —      | —         | —         | —            | _         | —         | —     | —       | -      | —     | —      | —     | 0000       |

| 9060                        | AD1PCFG <sup>(1)</sup> | 31:16         | —                                  | —      | —      | —      |        | —         | —         | —            | -         | —         | —     | —       | —      | —     | —      | —     | 0000       |

|                             |                        | 15:0          | PCFG15                             | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10    | PCFG9     | PCFG8        | PCFG7     | PCFG6     | PCFG5 | PCFG4   | PCFG3  | PCFG2 | PCFG1  | PCFG0 | 0000       |

| 9050                        | AD1CSSL <sup>(1)</sup> | 31:16         | —                                  | —      | —      | —      | —      | —         | —         | —            | —         | —         | —     | —       | -      | —     | —      | —     | 0000       |

|                             |                        | 15:0          | CSSL15                             | CSSL14 | CSSL13 | CSSL12 | CSSL11 | CSSL10    | CSSL9     | CSSL8        | CSSL7     | CSSL6     | CSSL5 | CSSL4   | CSSL3  | CSSL2 | CSSL1  | CSSL0 | 0000       |

| 9070                        | ADC1BUF0               | 31:16<br>15:0 | ADC Result Word 0 (ADC1BUF0<31:0>) |        |        |        |        |           |           |              |           | 0000      |       |         |        |       |        |       |            |

| 9080                        | ADC1BUF1               | 31:16         | ADC Result Word 1 (ADC1BUF1<31:0>) |        |        |        |        |           |           |              |           | 0000      |       |         |        |       |        |       |            |

|                             |                        | 15:0          |                                    |        |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

| 9090                        | ADC1BUF2               | 31:16         |                                    |        |        |        |        |           | ADC Re    | sult Word 2  | (ADC1BUF2 | 2<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |        |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

| 90A0                        | ADC1BUF3               | 31:16         |                                    |        |        |        |        |           | ADC Re    | sult Word 3  | (ADC1BUF3 | 8<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |        |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

| 90B0                        | ADC1BUF4               | 31:16         |                                    |        |        |        |        |           | ADC Re    | sult Word 4  | (ADC1BUF4 | l<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |        |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

| 90C0                        | ADC1BUF5               | 31:16         |                                    |        |        |        |        |           | ADC Re    | sult Word 5  | (ADC1BUF5 | 5<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |        |        |        |        |           |           |              |           |           |       |         |        |       |        |       | 0000       |

| 90D0                        | ADC1BUF6               | 31:16         |                                    |        |        |        |        |           | ADC Re    | sult Word 6  | (ADC1BUF6 | 6<31:0>)  |       |         |        |       |        |       | 0000       |

|                             |                        | 15:0          |                                    |        |        |        |        |           |           |              |           | 0000      |       |         |        |       |        |       |            |

| 90E0                        | ADC1BUF7               | 31:16<br>15:0 | ADC Result Word 7 (ADC1BUF7<31:0>) |        |        |        |        |           |           |              |           | 0000      |       |         |        |       |        |       |            |

|                             |                        | 31:16         |                                    |        |        |        |        |           |           |              |           | 0000      |       |         |        |       |        |       |            |

| 90F0                        | ADC1BUF8               | 15:0          | ADC Result Word 8 (ADC1BUE8<31:0>) |        |        |        |        |           |           |              |           | 0000      |       |         |        |       |        |       |            |

| 9100                        | ADC1BUF9               | 31:16         |                                    |        |        |        |        |           |           | esult Word 9 |           | 2<31.02)  |       |         |        |       |        |       | 0000       |

| 5100                        | 1.5015019              | 15:0          |                                    |        |        |        |        |           | ADONE     | Sur Word 9   | 0.0010013 |           |       |         |        |       |        |       | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## TABLE 4-13: ADC REGISTERS MAP (CONTINUED)

| ess                         |                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  |        | Bi          | its       |            |      |      |  |  |      |

|-----------------------------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--------|-------------|-----------|------------|------|------|--|--|------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15     30/14     29/13     28/12     27/11     26/10     25/9     24/8     23/7     22/6     21/5     20/4     19/3     18/2     17/1     16/0     Image: Second |                                    |  |  |  |  |        |             |           | All Resets |      |      |  |  |      |

| 9110                        | ADC1BUFA         | 31:16     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADC Result Word A (ADC1BUFA<31:0>) |  |  |  |  |        |             |           |            |      | 0000 |  |  |      |

|                             |                  | 15:0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                               |  |  |  |  |        |             |           |            |      |      |  |  |      |

| 0120                        | ADC1BUFB         | 31:16     | ADC Result Word B (ADC1BUFB<31:0>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |  |  |  |  |        |             |           |            | 0000 |      |  |  |      |

| 9120                        | ADCIBUEB         | 15:0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  |        |             |           |            |      |      |  |  |      |

| 0400                        |                  | 31:16     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  |        |             |           | 2.01.0.)   |      |      |  |  | 0000 |

| 9130                        | ADC1BUFC         | 15:0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  | ADC RE | suit word C | (ADC1BUFC | -<31:0>)   |      |      |  |  | 0000 |

| 04.40                       |                  | 31:16     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  |        |             |           |            |      |      |  |  | 0000 |

| 9140                        | ADC1BUFD         | 15:0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  | ADC Re | suit word D | (ADC1BUFE | D<31:0>)   |      |      |  |  | 0000 |

| 0450                        |                  | 31:16     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  |        |             |           |            |      |      |  |  | 0000 |

| 9150                        | ADC1BUFE         | 15:0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADC Result Word E (ADC1BUFE<31:0>) |  |  |  |  |        |             |           |            |      |      |  |  |      |

| 0400                        |                  | 31:16     | ADC Result Word F (ADC1BUFF<31:0>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |  |  |  |  |        |             |           |            | 0000 |      |  |  |      |

| 9160                        | ADC1BUFF         | 15:0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |  |  |  |  | ADC RE | suit word F | (ADC1BUFF | -<31:0>)   |      |      |  |  | 0000 |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## 12.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS61120) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Following are some of the key features of this module:

- Individual Output Pin Open-drain Enable/Disable

- Individual Input Pin Weak Pull-up Enable/Disable

- Monitor Selective Inputs and Generate Interrupt when Change in Pin State is Detected

- Operation during CPU Sleep and Idle modes

- Fast Bit Manipulation using CLR, SET and INV Registers

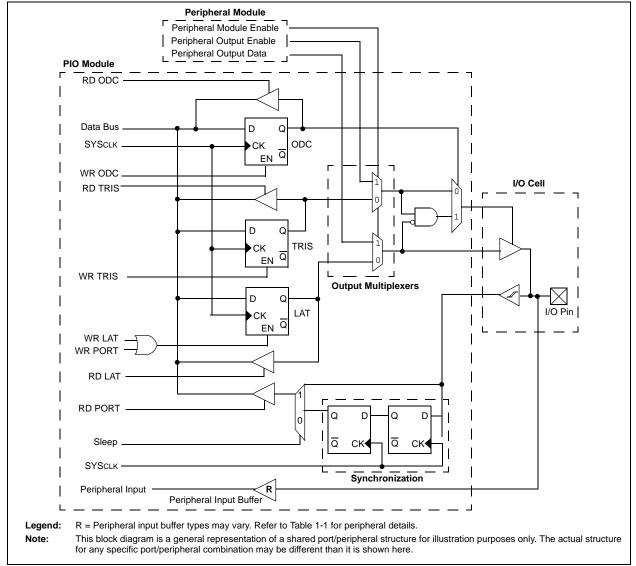

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

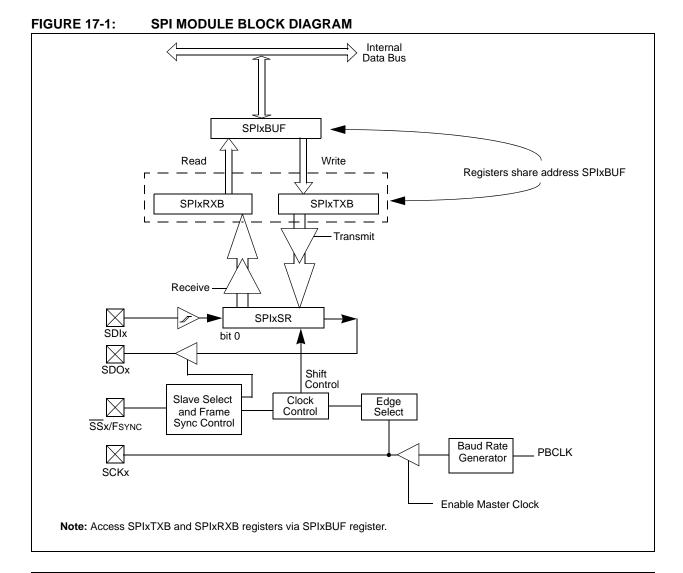

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32MX SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Following are some of the key features of this module:

- Master and Slave Modes Support

- Four Different Clock Formats

- Framed SPI Protocol Support

- User Configurable 8-bit, 16-bit and 32-bit Data

Width

- Separate SPI Data Registers for Receive and Transmit

- Programmable Interrupt Event on every 8-bit, 16-bit and 32-bit Data Transfer

- Operation during CPU Sleep and Idle Mode

- Fast Bit Manipulation using CLR, SET and INV Registers

NOTES:

NOTES:

NOTES:

#### **DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)** REGISTER 26-1:

bit 19-12 PWP<7:0>: Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. 11111111 = Disabled 11111110 = 0xBD00 0FFF 11111101 = 0xBD00\_1FFF 11111100 = 0xBD00\_2FFF 11111011 = 0xBD00\_3FFF 11111010 = 0xBD00\_4FFF 11111001 = 0xBD00 5FFF 11111000 = 0xBD00\_6FFF 11110111 = 0xBD00\_7FFF 11110110 = 0xBD00\_8FFF 11110101 = 0xBD00\_9FFF 11110100 = 0xBD00\_AFFF 11110011 = 0xBD00 BFFF 11110010 = 0xBD00\_CFFF 11110001 = 0xBD00\_DFFF 11110000 = 0xBD00\_EFFF 11101111 = 0xBD00\_FFFF 01111111 = 0xBD07\_FFFF bit 11-4 Reserved: Write '1' ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit 1 = PGEC2/PGED2 pair is used 0 = PGEC1/PGED1 pair is used Reserved: Write '1' DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled) bit 1-0

11 = Debugger disabled

bit 3

bit 2

- 10 =Debugger enabled

- 01 = Reserved (same as '11' setting) 00 = Reserved (same as '11' setting)

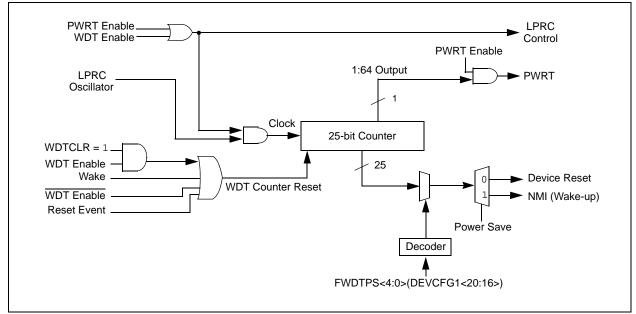

## 26.2 Watchdog Timer (WDT)

This section describes the operation of the WDT and Power-Up Timer of the PIC32MX3XX/4XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- · Can wake the device from Sleep or Idle

## FIGURE 26-1: WATCHDOG AND POWER-UP TIMER BLOCK DIAGRAM

| DC CHARA         | CTERISTIC              | S                   |       | <b>Operating</b><br>temperatu | re -40°0 | ns: 2.3V to 3.6V (unless otherwise stated)<br>C ≤TA ≤+85°C for Industrial<br>C ≤TA ≤+105°C for V-Temp |  |  |  |  |

|------------------|------------------------|---------------------|-------|-------------------------------|----------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter<br>No. | Typical <sup>(2)</sup> | Max.                | Units | Conditions                    |          |                                                                                                       |  |  |  |  |

| Power-Dow        | n Current (            | [PD) <sup>(1)</sup> |       | •                             |          |                                                                                                       |  |  |  |  |

| DC40             | 7                      | 30                  | μA    | -40°C                         |          |                                                                                                       |  |  |  |  |

| DC40a            | 24                     | 30                  | μA    | +25°C                         | 0.01/    |                                                                                                       |  |  |  |  |

| DC40b            | 205                    | 300                 | μΑ    | +85°C                         | 2.3V     | Base Power-Down Current (Note 6)                                                                      |  |  |  |  |

| DC40h            | 450                    | 900                 | μA    | +105⁰C                        |          |                                                                                                       |  |  |  |  |

| DC40c            | 25                     |                     | μΑ    | +25°C                         | 3.3V     | Base Power-Down Current                                                                               |  |  |  |  |

| DC40d            | 9                      | 70                  | μΑ    | -40°C                         |          |                                                                                                       |  |  |  |  |

| DC40e            | 25                     | 70                  | μΑ    | +25°C                         |          |                                                                                                       |  |  |  |  |

| DC40g            | 115                    | 200 <sup>(5)</sup>  | μΑ    | +70°C                         | 3.6V     | Base Power-Down Current                                                                               |  |  |  |  |

| DC40f            | 200                    | 400                 | μA    | +85°C                         |          |                                                                                                       |  |  |  |  |

| DC40i            | 470                    | 1200                | μA    | +105⁰C                        |          |                                                                                                       |  |  |  |  |

| Module Dif       | ferential Cu           | rrent               |       |                               |          |                                                                                                       |  |  |  |  |

| DC41             | —                      | 10                  | μΑ    | -40°C                         |          |                                                                                                       |  |  |  |  |

| DC41a            |                        | 10                  | μA    | +25°C                         | 0.01/    | Wetch dog Timer Comments Alwart (Notes 2, C)                                                          |  |  |  |  |

| DC41b            | —                      | 10                  | μA    | +85°C                         | 2.3V     | Watchdog Timer Current: ∆IwDT (Notes 3, 6)                                                            |  |  |  |  |

| DC41g            | —                      | 12                  | μA    | +105⁰C                        |          |                                                                                                       |  |  |  |  |

| DC41c            | 5                      | _                   | μA    | +25°C                         | 3.3V     | Watchdog Timer Current: ∆IwDT (Note 3)                                                                |  |  |  |  |

| DC41d            | —                      | 10                  | μA    | -40°C                         |          |                                                                                                       |  |  |  |  |

| DC41e            | —                      | 10                  | μA    | +25°C                         | 3.6V     | Watchdog Timer Current: ∆Iwor (Note 3)                                                                |  |  |  |  |

| DC41f            | —                      | 12                  | μA    | +85°C                         | 3.00     | Watchdog Timer Current. Ziwbr (Note 3)                                                                |  |  |  |  |

| DC41h            | —                      | 15                  | μA    | +105⁰C                        |          |                                                                                                       |  |  |  |  |

| DC42             | —                      | 10                  | μA    | -40°C                         |          |                                                                                                       |  |  |  |  |

| DC42a            | —                      | 17                  | μΑ    | +25°C                         | 2.3V     | RTCC + Timer1 w/32 kHz Crystal: ∆IRTCC                                                                |  |  |  |  |

| DC42b            | —                      | 37                  | μΑ    | +85°C                         | 2.3V     | (Notes 3, 6)                                                                                          |  |  |  |  |

| DC42h            | —                      | 45                  | μA    | +105⁰C                        |          |                                                                                                       |  |  |  |  |

| DC42c            | 23                     | _                   | μΑ    | +25°C                         | 3.3V     | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3)                                                       |  |  |  |  |

| DC42e            | —                      | 10                  | μΑ    | -40°C                         |          |                                                                                                       |  |  |  |  |

| DC42f            | —                      | 30                  | μΑ    | +25°C                         | 3.6V     | RTCC + Timer1 w/32 kHz Crystal: ∆IRTCC (Note 3)                                                       |  |  |  |  |

| DC42g            | —                      | 44                  | μΑ    | +85°C                         | 3.00     |                                                                                                       |  |  |  |  |

| DC42i            | —                      | 44                  | μA    | +105⁰C                        |          |                                                                                                       |  |  |  |  |

## TABLE 29-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Base IPD is measured with all digital peripheral modules disabled. All I/Os are configured as inputs and pulled low. WDT and FSCM are disabled.

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: Data is characterized at +70°C and not tested. Parameter is for design guidance only.

- 6: This parameter is characterized, but not tested in manufacturing.

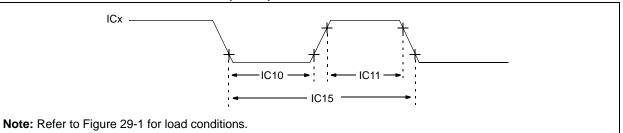

## FIGURE 29-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

## TABLE 29-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS               | (unless othe             | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +105^{\circ}C$ for V-Temp |      |       |                                         |                                  |  |  |  |  |

|---------------|---------|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------|----------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Charac              | teristics <sup>(1)</sup> | Min.                                                                                                                                                                                                   | Max. | Units | Conditions                              |                                  |  |  |  |  |

| IC10          | TccL    | ICx Input Low Time  |                          | [(12.5 ns or 1ТРВ)/N]<br>+ 25 ns                                                                                                                                                                       | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |  |  |  |  |

| IC11          | Тссн    | ICx Input High Time |                          | [(12.5 ns or 1TPB)/N]<br>+ 25 ns                                                                                                                                                                       | _    | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |  |  |  |  |

| IC15          | TCCP    | ICx Input           | Period                   | [(25 ns or 2Трв)/N]<br>+ 50 ns                                                                                                                                                                         | —    | ns    | —                                       |                                  |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

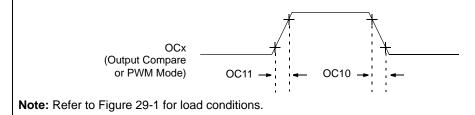

### FIGURE 29-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

## TABLE 29-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| АС СНА        | RACTER | ISTICS                         | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +105^{\circ}C$ for V-Temp |                        |      |       |                     |  |  |  |  |

|---------------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|---------------------|--|--|--|--|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                   | Typical <sup>(2)</sup> | Max. | Units | Conditions          |  |  |  |  |

| OC10          | TccF   | OCx Output Fall Time           | _                                                                                                                                                                                                      | —                      |      | ns    | See parameter DO32. |  |  |  |  |

| OC11          | TCCR   | OCx Output Rise Time           | —                                                                                                                                                                                                      | —                      | _    | ns    | See parameter DO31. |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

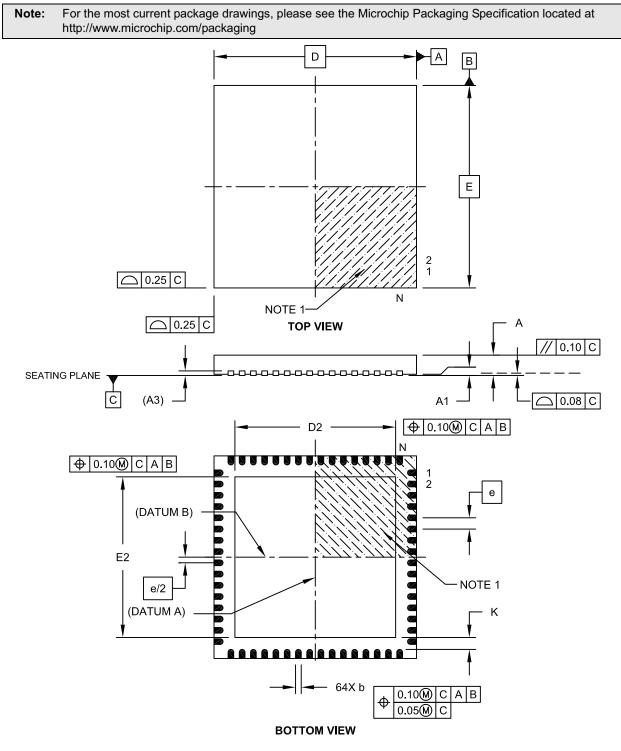

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Microchip Technology Drawing C04-149C Sheet 1 of 2

DS61143H-page 194

## Revision H (May 2011)

The revision includes the following global update:

- All references to VDDCORE/VCAP have been changed to: VCORE/VCAP

- Added references to the new V-Temp temperature range: -40°C to +105°C

This revision also includes minor typographical and formatting changes throughout the data sheet text. Major updates are referenced by their respective section in the following table.

| Section Name                                            | Update Description                                                                                                                                                                         |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 1.0 "Device Overview"                           | Updated the VBUS description in Table 1-1: "Pinout I/O Descriptions".                                                                                                                      |

| Section 4.0 "Memory Organization"                       | Added Note 2 and changed the RIPL<2:0> bits to SRIPL<2:0> in the Interrupt Register Map tables (see Table 4-2 through Table 4-6.                                                           |

|                                                         | Added Note 2 to the Timer1-5 Register Map (see Table 4-7).                                                                                                                                 |