Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx340f128lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1:PIC32MX GENERAL PURPOSE – FEATURES

|                 | GENERAL PURPOSE |                         |     |                         |                  |                        |                              |      |       |                             |                 |             |         |      |

|-----------------|-----------------|-------------------------|-----|-------------------------|------------------|------------------------|------------------------------|------|-------|-----------------------------|-----------------|-------------|---------|------|

| Device          | Pins            | Packages <sup>(2)</sup> | ZHW | Program Memory (KB)     | Data Memory (KB) | Timers/Capture/Compare | Programmable DMA<br>Channels | VREG | Trace | EUART/SPI/I <sup>2</sup> C™ | 10-bit ADC (ch) | Comparators | dSd/dWd | JTAG |

| PIC32MX320F032H | 64              | PT, MR                  | 40  | 32 + 12 <sup>(1)</sup>  | 8                | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX320F064H | 64              | PT, MR                  | 80  | 64 + 12 <sup>(1)</sup>  | 16               | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX320F128H | 64              | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 16               | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX340F128H | 64              | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX340F256H | 64              | PT, MR                  | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX340F512H | 64              | PT, MR                  | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX320F128L | 100<br>121      | PT<br>BG                | 80  | 128 + 12 <sup>(1)</sup> | 16               | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100             | PT                      | 00  | 400 + 40(1)             | 20               | _ /_ /_                | 4                            | Vee  | Nia   | 0/0/0                       | 40              | 0           | Vee     | Vee  |

| PIC32MX340F128L | 121             | BG                      | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100             | PT                      |     | 0.50 (0(1)              |                  |                        |                              |      |       | 0/0/5                       |                 |             |         |      |

| PIC32MX360F256L | 121             | BG                      | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100             | PT                      |     | 540 40(1)               |                  | - (- (-                |                              |      | ~     | 0/0/6                       |                 |             |         |      |

| PIC32MX360F512L | 121             | BG                      | 80  | $512 + 12^{(1)}$        | 32               | 5/5/5                  | 4                            | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

Legend: PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB Boot Flash memory.

2: See Legend for an explanation of the acronyms. See Section 30.0 "Packaging Information" for details.

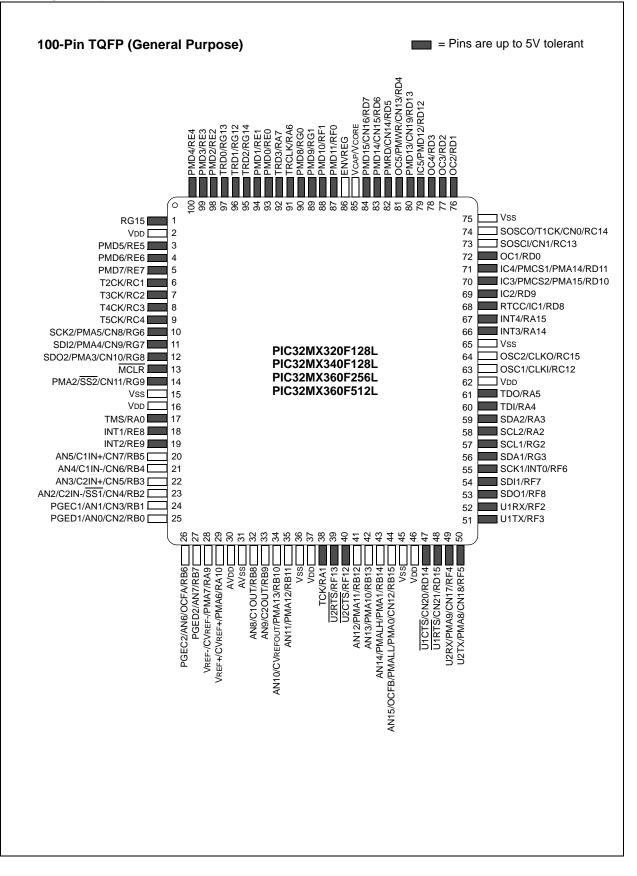

# **Pin Diagrams (Continued)**

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Register<br>Number | -                       | Function                                |

|--------------------|-------------------------|-----------------------------------------|

| 17-22              | Reserved                | Reserved                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception |

| 25-29              | Reserved                | Reserved                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register       |

## TABLE 3-2:COPROCESSOR 0 REGISTERS (CONTINUED)

Note 1: Registers used in exception processing.

2: Registers used during debug.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 shows the exception types in order of priority.

## TABLE 3-3: PIC32MX3XX/4XX FAMILY CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR)                                                                                                |

| DSS       | EJTAG Debug Single Step                                                                                                                 |

| DINT      | EJTAG Debug Interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input, or by setting the EjtagBrk bit in the ECR register |

| NMI       | Assertion of NMI signal                                                                                                                 |

| Interrupt | Assertion of unmasked hardware or software interrupt signal                                                                             |

| DIB       | EJTAG debug hardware instruction break matched                                                                                          |

| AdEL      | Fetch address alignment error<br>Fetch reference to protected address                                                                   |

| IBE       | Instruction fetch bus error                                                                                                             |

| DBp       | EJTAG Breakpoint (execution of SDBBP instruction)                                                                                       |

| Sys       | Execution of SYSCALL instruction                                                                                                        |

| Вр        | Execution of BREAK instruction                                                                                                          |

| RI        | Execution of a Reserved Instruction                                                                                                     |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled                                                            |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled                                                                      |

| Ov        | Execution of an arithmetic instruction that overflowed                                                                                  |

| Tr        | Execution of a trap (when trap condition is true)                                                                                       |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG Data Value Break on Store (address + value)                                            |

| AdEL      | Load address alignment error<br>Load reference to protected address                                                                     |

| AdES      | Store address alignment error<br>Store to protected address                                                                             |

| DBE       | Load or store bus error                                                                                                                 |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare                                                                             |

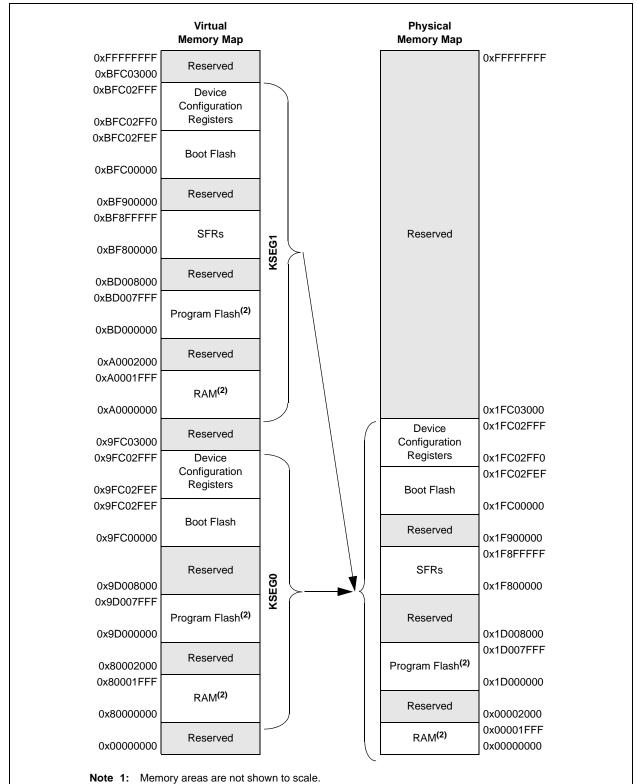

#### FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX320F032H AND PIC32MX420F032H DEVICES<sup>(1)</sup>

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range     |       |       |             |       |        |       |      |        |        |        |        |        |         |        |        |        |            |

|-----------------------------|------------------|---------------|-------|-------|-------------|-------|--------|-------|------|--------|--------|--------|--------|--------|---------|--------|--------|--------|------------|

| /irtual Addre<br>(BF88_#)   | Register<br>Name | ange          |       |       |             |       |        |       |      | Bi     | ts     |        |        |        |         |        |        |        |            |

| -                           |                  | Bit R         | 31/15 | 30/14 | 29/13       | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH0CON          | 31:16         | -     |       | -           |       |        |       | -    | -      |        | —      |        | —      | —       | —      |        | _      | 0000       |

|                             | Denteent         | 15:0          | —     | _     | —           |       | _      | _     | _    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON         | 31:16         | —     | —     | —           | —     | —      | —     | _    | —      |        |        |        |        |         |        |        |        | OOFF       |

| 00/0 0                      |                  | 15:0          |       |       |             | CHSIR | Q<7:0> |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      |        | FF00       |

| 3080                        | DCH0INT          | 31:16         | —     | —     | —           | —     | —      |       | _    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        | Denoirtí         | 15:0          | —     | _     | —           |       | _      | _     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090 I                      | DCH0SSA          | 31:16<br>15:0 |       |       |             |       |        |       |      | CHSSA  | <31:0> |        |        |        |         |        |        |        | 0000       |

| 30A0 I                      | DCH0DSA          | 31:16<br>15:0 |       |       |             |       |        |       |      | CHDSA  | <31:0> |        |        |        |         |        |        |        | 0000       |

|                             |                  | 31:16         | _     | —     | _           | _     | —      | —     | _    | —      | —      | —      | —      | _      | —       | —      | _      | _      | 0000       |

| 30B0 [                      | DCH0SSIZ         | 15:0          | _     | _     | _           | _     | _      | _     | _    | -      |        |        |        | CHSSI  | Z<7:0>  |        |        |        | 0000       |

|                             |                  | 31:16         | _     | _     | _           |       | _      | _     | _    | _      | _      | —      | _      | _      | —       | _      | —      |        | 0000       |

| 30C0 [                      | DCH0DSIZ         | 15:0          | _     |       | —           | _     |        | _     | _    | —      |        |        |        | CHDSI  | Z<7:0>  |        |        |        | 0000       |

| 2000                        |                  | 31:16         | _     | _     | —           | _     | _      | _     | -    | —      |        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 30D0 L                      | DCH0SPTR         | 15:0          | _     |       | _           | _     |        |       | -    | —      |        |        |        | CHST   | R<7:0>  |        |        |        | 0000       |

| 2050 5                      |                  | 31:16         | _     |       | _           | _     |        |       |      | —      |        | —      | —      | —      | —       | _      | _      | _      | 0000       |

| 30E0 L                      | OCH0DPTR         | 15:0          | —     | _     | —           |       | _      | _     | -    | —      |        | •      |        | CHDPT  | R<7:0>  |        |        |        | 0000       |

| 30F0 [                      | DCH0CSIZ         | 31:16         | _     | —     | —           | —     | —      | _     | —    | —      | _      | —      | —      | —      | —       | —      |        |        | 0000       |

| 3050 1                      | DCHUCSIZ         | 15:0          | -     | —     | —           | —     | —      | —     | —    | —      |        |        |        | CHCSI  | Z<7:0>  |        |        |        | 0000       |

| 2100 0                      | OCH0CPTR         | 31:16         | _     | _     | —           | _     | _      | _     | _    | —      | _      | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 3100 L                      | JUNUEFIK         | 15:0          | -     |       | —           | _     |        |       | _    | _      |        |        |        | CHCPT  | R<7:0>  |        |        |        | 0000       |

| 3110                        | DCH0DAT          | 31:16         | _     |       | _           | _     |        |       |      | —      |        | —      |        | —      | —       | —      |        |        | 0000       |

| 3110                        | DCI10DA1         | 15:0          | -     |       | _           | _     |        |       | I    | —      |        |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3120 [                      | DCH1CON          | 31:16         | —     |       | _           | _     |        |       |      | —      |        | -      |        | —      | _       | —      |        |        | 0000       |

| 0120                        | Donnoon          | 15:0          | —     |       | —           | _     |        |       | -    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | OCH1ECON         | 31:16         | —     |       | _           | _     |        |       |      | —      |        |        |        | CHAIR  | Q<7:0>  |        |        |        | OOFF       |

| 0100 0                      | John Cook        | 15:0          |       |       |             | CHSIR | Q<7:0> |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | _      | -      | FF00       |

| 3140                        | DCH1INT          | 31:16         | —     | _     | —           | —     | -      | -     | -    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| -                           |                  | 15:0          | —     | —     | —           | —     | —      | —     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150 I                      | DCH1SSA          | 31:16<br>15:0 |       |       | nimplemente |       |        |       |      | CHSSA  | <31:0> |        |        |        |         |        |        |        | 0000       |

# TABLE 4-16: DMA CHANNELS 0-3 REGISTERS MAP FOR PIC32MX340FXXXX/360FXXXX/440FXXXX/460XXXX DESUGE 2010 (1) DESUGE 2010 (1)

All registers except DCHxSPTR, DCHxDPTR and DCHxCPTR have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

DS61143H-page 65

PIC32MX3XX/4XX

# TABLE 4-33: PORTG REGISTERS MAP FOR PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F256L, PIC32MX360F512L, PIC32MX440F128L, PIC32MX460F256L AND PIC32MX460F512L DEVICES ONLY<sup>(1)</sup>

| ess                         |                  |           |         |         |         |         |       |       |        | Bi     | its    |        |      |      |        |        |        |        |            |

|-----------------------------|------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG            | 31:16     | _       | _       |         | —       |       |       |        |        |        | —      | —    |      | —      | —      | —      | —      | 0000       |

| 0100                        | 11100            | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 |       |       | TRISG9 | TRISG8 | TRISG7 | TRISG6 | -    | -    | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF       |

| 6190                        | PORTG            | 31:16     | -       | _       | -       | -       | -     | _     | _      | -      | -      | -      | -    | -    | -      | -      | -      | _      | 0000       |

| 0190                        | FURIG            | 15:0      | RG15    | RG14    | RG13    | RG12    | —     | —     | RG9    | RG8    | RG7    | RG6    | —    | —    | RG3    | RG2    | RG1    | RG0    | xxxx       |

| 61A0                        | LATG             | 31:16     |         | _       | _       | —       | —     | —     | —      | —      | —      | —      | —    | —    | —      | —      | —      | —      | 0000       |

| 6TAU                        | LAIG             | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | —    | —    | LATG3  | LATG2  | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG             | 31:16     | _       | —       | —       | —       | _     |       | _      | —      | _      | —      | —    | _    | —      | —      | —      | —      | 0000       |

| UIDU                        | ODCG             | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | _     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | —    | _    | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 4-34: PORTG REGISTERS MAP FOR PIC32MX320F032H, PIC32MX320F064H, PIC32MX320F128H, PIC32MX340F128H, PIC32MX340F256H, PIC32MX340F512H, PIC32MX420F032H, PIC32MX440F128H, PIC32MX440F256H AND PIC32MX440F512H DEVICES ONLY<sup>(1)</sup>

| ess                         |                  |           |       |       |       |       |       |       |        | Bi     | its    |        |      |      |        |        |      |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Resets |

| 6180                        | TRISG            | 31:16     | -     | _     |       | _     |       | —     |        |        |        | —      |      |      | —      | —      |      | —    | 0000       |

| 0100                        | IRISG            | 15:0      | —     | —     | —     | —     | —     | —     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | _    | —    | 03cc       |

| 6190                        | PORTG            | 31:16     |       | -     | _     | _     | —     | —     | _      | _      | —      | —      | _    | _    | —      | —      | _    | _    | 0000       |

| 0190                        | FORIG            | 15:0      | -     | -     | -     | _     | -     | -     | RG9    | RG8    | RG7    | RG6    | _    | -    | RG3    | RG2    | -    | -    | xxxx       |

| 61A0                        | LATG             | 31:16     | -     | _     |       | _     |       | _     |        | _      | -      | _      | _    | -    | —      | _      |      | _    | 0000       |

| 0170                        | LAIG             | 15:0      | -     |       |       | -     | -     | -     | LATG9  | LATG8  | LATG7  | LATG6  |      | -    | LATG3  | LATG2  |      | —    | xxxx       |

| 61B0                        | ODCG             | 31:16     | -     | _     |       | _     |       | —     |        | _      |        | —      | _    |      | —      | —      |      | _    | 0000       |

| 0100                        | 0000             | 15:0      | _     | _     |       | —     |       | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _    | -    | ODCG3  | ODCG2  |      | _    | 0000       |

Legend: x = unknown value on Reset, --- unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

NOTES:

# 11.0 USB ON-THE-GO (OTG)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS61126) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 fullspeed and low-speed embedded host, full-speed device, or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32MX USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers, and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32MX USB module includes the following features:

- USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB OTG Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- Integrated USB Transceiver

- Transaction Handshaking Performed by Hardware

- Endpoint Buffering Anywhere in System RAM

- Integrated DMA to Access System RAM and Flash

Note: The implementation and use of the USB specifications, as well as other third-party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

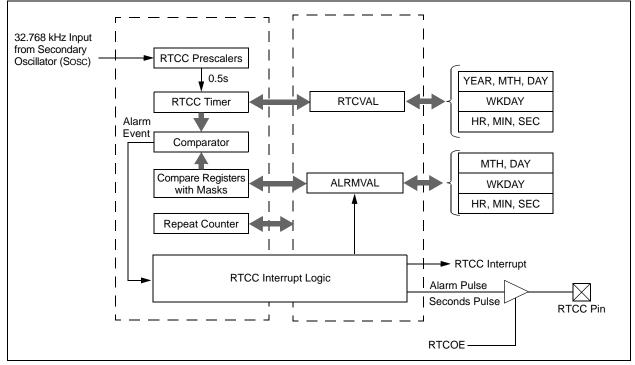

# 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS61125) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC32MX RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. The following are some of the key features of this module:

- Time: Hours, Minutes and Seconds

- 24-Hour Format (Military Time)

- Visibility of One-Half-Second Period

- Provides Calendar: Weekday, Date, Month and Year

- Alarm Intervals are configurable for Half of a Second, One Second, 10 Seconds, One Minute, 10 Minutes, One Hour, One Day, One Week, One Month and One Year

- Alarm Repeat with Decrementing Counter

- · Alarm with Indefinite Repeat: Chime

- Year Range: 2000 to 2099

- Leap Year Correction

- BCD Format for Smaller Firmware Overhead

- Optimized for Long-Term Battery Operation

- Fractional Second Synchronization

- User Calibration of the Clock Crystal Frequency with Auto-Adjust

- Calibration Range: ±0.66 Seconds Error per Month

- · Calibrates up to 260 ppm of Crystal Error

- Requirements: External 32.768 kHz Clock Crystal

- Alarm Pulse or Seconds Clock Output on RTCC pin

# FIGURE 21-1: RTCC BLOCK DIAGRAM

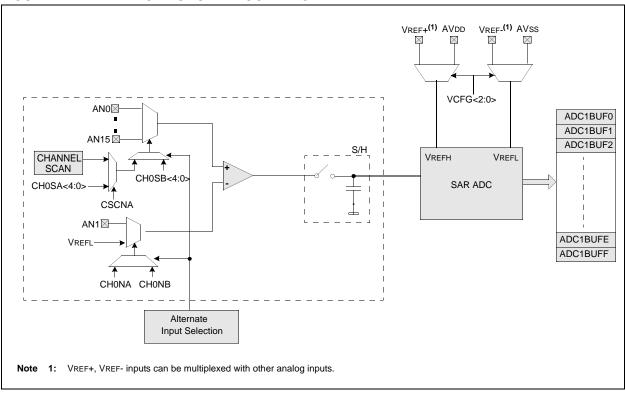

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. Refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS61104) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC32MX3XX/4XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1000 kilo samples per second (ksps) conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample-and-Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- Selectable Buffer Fill modes

- Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers (MUXs) to one SHA. The analog input MUXs can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 22-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight, 32-bit output formats when it is read from the result buffer.

# FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

# 26.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX3XX/4XX family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-up Timer" (DS61114), Section 32. "Configuration" (DS61124) and Section 33. "Programming and Diagnostics" (DS61129) of the "PIC32 Family Reference Manual", which is available from Microchip the web site (www.microchip.com/PIC32).

PIC32MX3XX/4XX devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- Flexible Device Configuration

- Watchdog Timer

- JTAG Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

# 26.1 Configuration Bits

The Configuration bits can be programmed to select various device configurations.

| REGISTE      | REGISTER 26-1: DEVCEG0: DEVICE CONFIGURATION WORD 0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-----------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 04.04        | r-0                                                 | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | R/P              |  |  |  |  |

| 31:24        | —                                                   | —                 | —                 | CP                | _                 | —                 | —                | BWP              |  |  |  |  |

| 00.40        | r-1                                                 | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 23:16        | —                                                   | —                 | —                 | —                 |                   | PWP               | <7:4>            |                  |  |  |  |  |

| 15:8         | R/P                                                 | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |  |  |  |

| 10.0         |                                                     | PWP<              | <3:0>             |                   |                   |                   | —                | —                |  |  |  |  |

| 7.0          | r-1                                                 | r-1               | r-1               | r-1               | R/P               | r-1               | R/P              | R/P              |  |  |  |  |

| 7:0          |                                                     | —                 | —                 | _                 | ICESEL            |                   | DEBU             | G<1:0>           |  |  |  |  |

|              |                                                     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:      |                                                     |                   |                   | •                 |                   |                   |                  |                  |  |  |  |  |

| R = Read     | able bit                                            |                   | W = Writable      | e bit             | P = Progran       | nmable bit        | r = Reserve      | d bit            |  |  |  |  |

| U = Unim     | plemented bit                                       |                   | -n = Bit Valu     | e at POR: ('0'    | , '1', x = Unk    | nown)             |                  |                  |  |  |  |  |

# REGISTER 26-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

- bit 31 **Reserved:** Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection disabled

- 0 = Protection enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

# 26.2 Watchdog Timer (WDT)

This section describes the operation of the WDT and Power-Up Timer of the PIC32MX3XX/4XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- · Can wake the device from Sleep or Idle

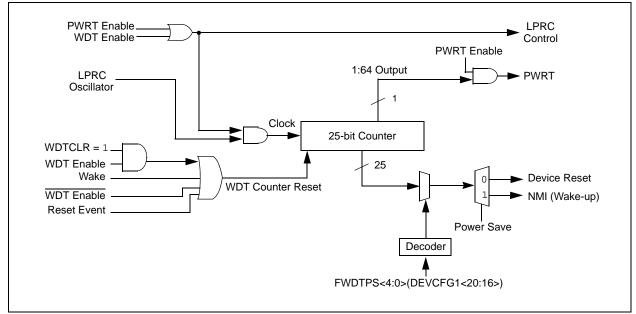

## FIGURE 26-1: WATCHDOG AND POWER-UP TIMER BLOCK DIAGRAM

## TABLE 29-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHA        | RACTER | ISTICS              | Standard O<br>stated)<br>Operating te |   | nditions: 2.3V to 3.6V (unless otherwise<br>-40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+105°C for V-Temp |   |                             |  |  |  |  |

|---------------|--------|---------------------|---------------------------------------|---|-------------------------------------------------------------------------------------------------------------|---|-----------------------------|--|--|--|--|

| Param.<br>No. | Symbol | Characteristics     | Min. Typical Max. Units Conditions    |   |                                                                                                             |   |                             |  |  |  |  |

| -             | Vol    | Output Low Voltage  |                                       |   |                                                                                                             |   |                             |  |  |  |  |

| DO10          |        | I/O Ports           | —                                     | — | 0.4                                                                                                         | V | IOL = 7 mA, VDD = 3.6V      |  |  |  |  |

|               |        |                     | —                                     | — | 0.4                                                                                                         | V | IOL = 6  mA,  VDD = 2.3  V  |  |  |  |  |

| DO16          |        | OSC2/CLKO           | —                                     | — | 0.4                                                                                                         | V | IOL = 3.5 mA, VDD = 3.6V    |  |  |  |  |

|               |        |                     | —                                     | — | 0.4                                                                                                         | V | IOL = 2.5  mA,  VDD = 2.3 V |  |  |  |  |

|               | Vон    | Output High Voltage |                                       |   |                                                                                                             |   |                             |  |  |  |  |

| DO20          |        | I/O Ports           | 2.4                                   | — | _                                                                                                           | V | ЮН = -12 mA, VDD = 3.6V     |  |  |  |  |

|               |        |                     | 1.4                                   | — | _                                                                                                           | V | Юн = -12 mA, VDD = 2.3V     |  |  |  |  |

| DO26          |        | OSC2/CLKO           | 2.4                                   | — | —                                                                                                           | V | ЮН = -12 mA, VDD = 3.6V     |  |  |  |  |

|               |        |                     | 1.4                                   | — | —                                                                                                           | V | Юн = -12 mA, VDD = 2.3V     |  |  |  |  |

## TABLE 29-10: ELECTRICAL CHARACTERISTICS: BROWN-OUT RESET (BOR)

| DC CHA        | RACTER | ISTICS                                  | stated) | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise<br>stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \leq TA \leq +105^{\circ}C$ for V-Temp |                       |  |  |  |  |  |  |  |  |

|---------------|--------|-----------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|--|--|--|--|

| Param.<br>No. | Symbol | Characteristics                         | Min.    | Typical                                                                                                                                                                                                       | Max. Units Conditions |  |  |  |  |  |  |  |  |

| BO10          | VBOR   | BOR Event on VDD transition high-to-low | 2.0     | 2.0 — 2.3 V —                                                                                                                                                                                                 |                       |  |  |  |  |  |  |  |  |

### TABLE 29-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | RACTER        | ISTICS                                                                                                           | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                        |                            |            |                                         |  |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|------------|-----------------------------------------|--|--|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max.                       | Units      | Conditions                              |  |  |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                  |                        | <sub>50</sub> (3)<br>50(5) | MHz<br>MHz | EC (Note 5)<br>ECPLL (Note 4)           |  |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                        | —                      | 10                         | MHz        | XT (Note 5)                             |  |  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                        | _                      | 10                         | MHz        | XTPLL<br>(Notes 4, 5)                   |  |  |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                       | —                      | 25                         | MHz        | HS (Note 5)                             |  |  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                       | _                      | 25                         | MHz        | HSPLL<br>(Notes 4, 5)                   |  |  |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                       | 32.768                 | 100                        | kHz        | Sosc (Note 5)                           |  |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy <sup>(2)</sup>                                                                               | _                                                                                                                                                                                        |                        | _                          | —          | See parameter<br>OS10 for Fosc<br>value |  |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                              | —                      | _                          | ns         | EC (Note 5)                             |  |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                        | —                      | 0.05 x Tosc                | ns         | EC (Note 5)                             |  |  |  |

| OS40          | Тоят          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                        | 1024                   | _                          | Tosc       | (Note 5)                                |  |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                        | 2                      |                            | ms         | (Note 5)                                |  |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance                                                                          | —                                                                                                                                                                                        | 12                     |                            | mA/V       | VDD = 3.3V<br>TA = +25°C<br>(Note 5)    |  |  |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- **3:** 40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.

- **4:** PLL input requirements: 4 MHz ≤FPLLIN ≤5 MHz (use PLL prescaler to reduce FOSC). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 5: This parameter is characterized, but not tested in manufacturing.

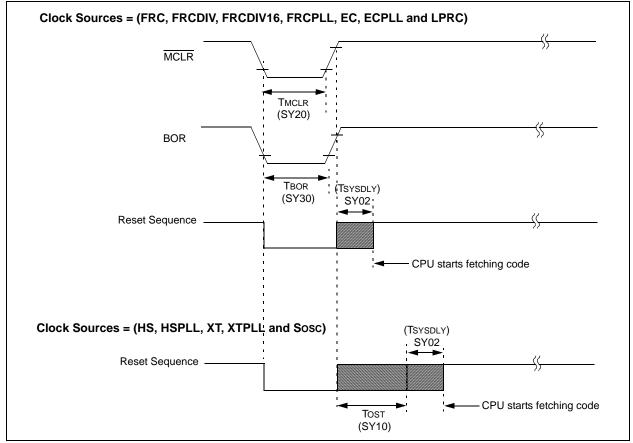

# FIGURE 29-5: EXTERNAL RESET TIMING CHARACTERISTICS

#### TABLE 29-22: RESETS TIMING

| AC CHA        | RACTER  | ISTICS                                                                                                                                     | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                                 |      |       |                |  |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|-------|----------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                                                                                             | Min.                                                                                                                                                                                   | Typical <sup>(2)</sup>          | Max. | Units | Conditions     |  |  |  |  |

| SY00          | Τρυ     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      |                                                                                                                                                                                        | 400                             | 600  | μs    | -40°C to +85°C |  |  |  |  |

| SY01          | TPWRT   | Power-up Period<br>External Vcore Applied<br>(Power-Up-Timer Active)                                                                       | 48                                                                                                                                                                                     | 64                              | 80   | ms    | -40°C to +85°C |  |  |  |  |

| SY02          | TSYSDLY | System Delay Period:<br>Time required to reload Device<br>Configuration Fuses plus SYSCLK<br>delay before first instruction is<br>fetched. |                                                                                                                                                                                        | 1 μs<br>+<br>8 sysclκ<br>cycles |      | _     | -40°C to +85°C |  |  |  |  |

| SY20          | TMCLR   | MCLR Pulse Width (low)                                                                                                                     |                                                                                                                                                                                        | 2                               | _    | μs    | -40°C to +85°C |  |  |  |  |

| SY30          | TBOR    | BOR Pulse Width (low)                                                                                                                      | —                                                                                                                                                                                      | 1                               | —    | μs    | -40°C to +85°C |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

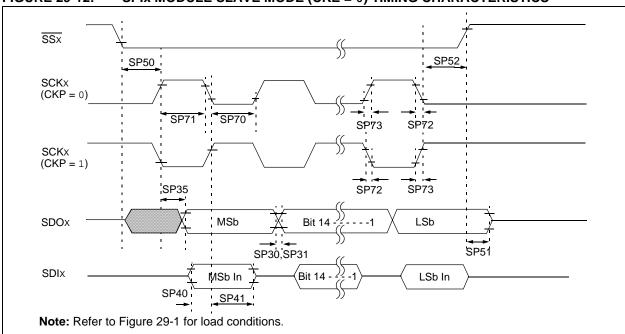

#### FIGURE 29-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 29-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                               | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                        |      |       |                    |  |

|--------------------|-----------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                | Min.                                                                                                                                                                                     | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70               | TscL                  | SCKx Input Low Time <sup>(3)</sup>                            | Тѕск/2                                                                                                                                                                                   | _                      |      | ns    | _                  |  |

| SP71               | TscH                  | SCKx Input High Time <sup>(3)</sup>                           | Тѕск/2                                                                                                                                                                                   | _                      |      | ns    | —                  |  |

| SP72               | TscF                  | SCKx Input Fall Time                                          |                                                                                                                                                                                          | _                      |      | ns    | See parameter DO32 |  |

| SP73               | TscR                  | SCKx Input Rise Time                                          | _                                                                                                                                                                                        | _                      | _    | ns    | See parameter DO31 |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                     |                                                                                                                                                                                          |                        |      | ns    | See parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>                     | _                                                                                                                                                                                        | _                      | _    | ns    | See parameter DO31 |  |

| SP35               | TscH2doV,             | SDOx Data Output Valid after                                  | _                                                                                                                                                                                        | —                      | 15   | ns    | Vdd > 2.7V         |  |

|                    | TscL2doV              | SCKx Edge                                                     | _                                                                                                                                                                                        | —                      | 20   | ns    | Vdd < 2.7V         |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                    | 10                                                                                                                                                                                       | _                      | —    | ns    | _                  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                     | 10                                                                                                                                                                                       | _                      | _    | ns    | _                  |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow $ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                      | _                      | _    | ns    | _                  |  |

| SP51               | TssH2doZ              | SSx                                                           | 5                                                                                                                                                                                        | —                      | 25   | ns    | —                  |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                           | Тѕск + 20                                                                                                                                                                                | _                      |      | ns    | —                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

# TABLE 29-34: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHARACTERISTICS |                        |                                | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial |              |                            |      |                                                         |  |  |

|--------------------|------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|------|---------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol Characteristics |                                | -40°C ≤TA ≤+105°C for V-<br>Min. Typical Max. Units                                                                                               |              | C for V-Temp<br>Conditions |      |                                                         |  |  |

| ADC Ac             | curacy – N             | leasurements with Inter        | nal VREF+/VR                                                                                                                                      | EF-          |                            |      | •                                                       |  |  |

| AD20d              | Nr                     | Resolution                     | 1                                                                                                                                                 | 10 data bits |                            | bits | (Note 3)                                                |  |  |

| AD21d              | INL                    | Integral Nonlinearity          |                                                                                                                                                   | _            | <±1                        | LSb  | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD22d              | DNL                    | Differential Nonlinearity      | —                                                                                                                                                 | _            | <±1                        | LSb  | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |

| AD23d              | Gerr                   | Gain Error                     | —                                                                                                                                                 | _            | <±4                        | LSb  | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD24d              | EOFF                   | Offset Error                   |                                                                                                                                                   | _            | <±2                        | LSb  | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD25d              | _                      | Monotonicity                   | _                                                                                                                                                 | _            |                            | _    | Guaranteed                                              |  |  |

| Dynami             | c Performa             | ance                           |                                                                                                                                                   |              |                            |      |                                                         |  |  |

| AD31b              | SINAD                  | Signal to Noise and Distortion | 55                                                                                                                                                | 58.5         | —                          | dB   | (Notes 3, 4)                                            |  |  |

| AD34b              | ENOB                   | Effective Number of Bits       | 9.0                                                                                                                                               | 9.5          |                            | bits | (Notes 3, 4)                                            |  |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with 1 kHz sinewave.

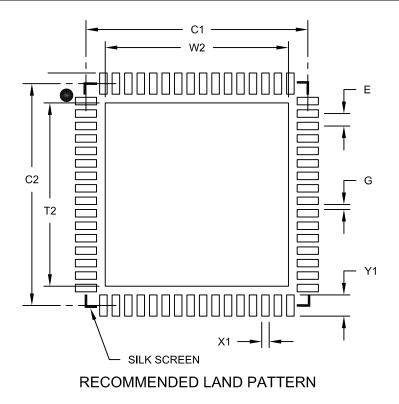

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |  |  |

|----------------------------|-------------|------|----------|------|--|--|

| Dimension Limits           |             | MIN  | NOM      | MAX  |  |  |

| Contact Pitch              | E           |      | 0.50 BSC |      |  |  |

| Optional Center Pad Width  | W2          |      |          | 7.35 |  |  |

| Optional Center Pad Length | T2          |      |          | 7.35 |  |  |

| Contact Pad Spacing        | C1          |      | 8.90     |      |  |  |

| Contact Pad Spacing        | C2          |      | 8.90     |      |  |  |

| Contact Pad Width (X64)    | X1          |      |          | 0.30 |  |  |

| Contact Pad Length (X64)   | Y1          |      |          | 0.85 |  |  |

| Distance Between Pads      | G           | 0.20 |          |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2149A

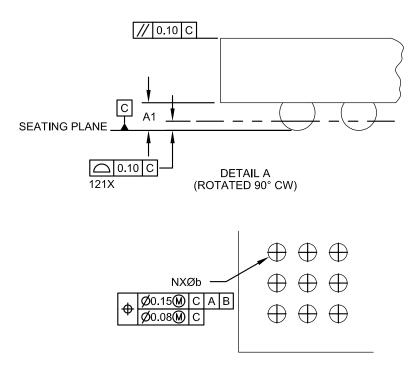

# 121-Lead Plastic Thin Profile Ball Grid Array (BG) - 10x10x1.10 mm Body [XBGA]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL B

|                          | MILLIMETERS      |           |      |      |  |  |

|--------------------------|------------------|-----------|------|------|--|--|

| Dimensior                | Dimension Limits |           |      | MAX  |  |  |

| Number of Contacts       | N                | 121       |      |      |  |  |

| Contact Pitch            | e                | 0.80 BSC  |      |      |  |  |

| Overall Height           | A                | 1.00      | 1.10 | 1.20 |  |  |

| Standoff                 | A1               | 0.25      | 0.30 | 0.35 |  |  |

| Molded Package Thickness | A2               | 0.55      | 0.60 | 0.65 |  |  |

| Overall Width            | E                | 10.00 BSC |      |      |  |  |

| Array Width              | E1               | 8.00 BSC  |      |      |  |  |

| Overall Length           | D                | 10.00 BSC |      |      |  |  |

| Array Length             | D1               | 8.00 BSC  |      |      |  |  |

| Contact Diameter         | b                | 0.40 TYP  |      |      |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

3. The outer rows and colums of balls are located with respect to datums A and B.

Microchip Technology Drawing C04-148 Rev B Sheet 2 of 2