Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx340f512h-80i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

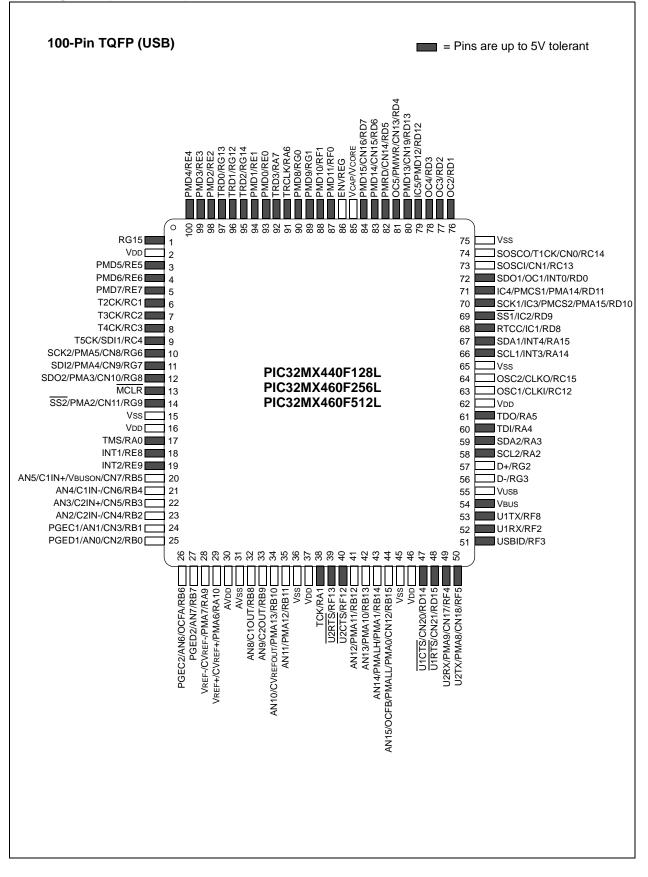

### Pin Diagrams (Continued)

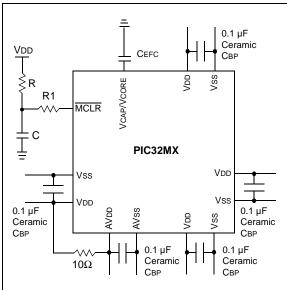

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

#### 2.3 Capacitor on Internal Voltage Regulator (VCAP/VCORE)

### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (< 1 Ohm) capacitor is required on the VCAP/VCORE pin, which is used to stabilize the internal voltage regulator output. The VCAP/VCORE pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 29.0** "**Electrical Characteristics**" for additional information on CEFC specifications. This mode is enabled by connecting the ENVREG pin to VDD.

### 2.3.2 EXTERNAL REGULATOR MODE

In this mode the core voltage is supplied externally through the VCORE/VCAP pin. A low-ESR capacitor of 10  $\mu F$  is recommended on the VCAP/VCORE pin. This mode is enabled by grounding the ENVREG pin.

The placement of this capacitor should be close to the VCAP/VCORE. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 26.3** "**On-Chip Voltage Regulator**" for details.

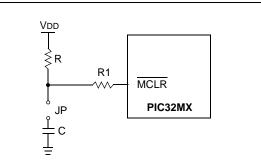

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| FIGURE 2-2: | EXAMPLE OF MCLR PIN |

|-------------|---------------------|

|             | CONNECTIONS         |

- Note 1: R ≤10 kΩ is recommended. A suggested starting value is 10 kΩ Ensure that the MCLR pin VIH and VIL specifications are met.

- 2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

- **3:** The capacitor can be sized to prevent unintentional resets from brief glitches or to extend the device reset period during POR.

#### 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core contains several logic blocks working together in parallel, providing an efficient high performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e Support

- Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit general purpose registers used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and Store Aligner

#### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core includes a multiply/divide unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the integer unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32MX core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If rs is 8 bits wide, 23 iterations are skipped. For a 16bit-wide rs, 15 iterations are skipped, and for a 24-bitwide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32MX core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

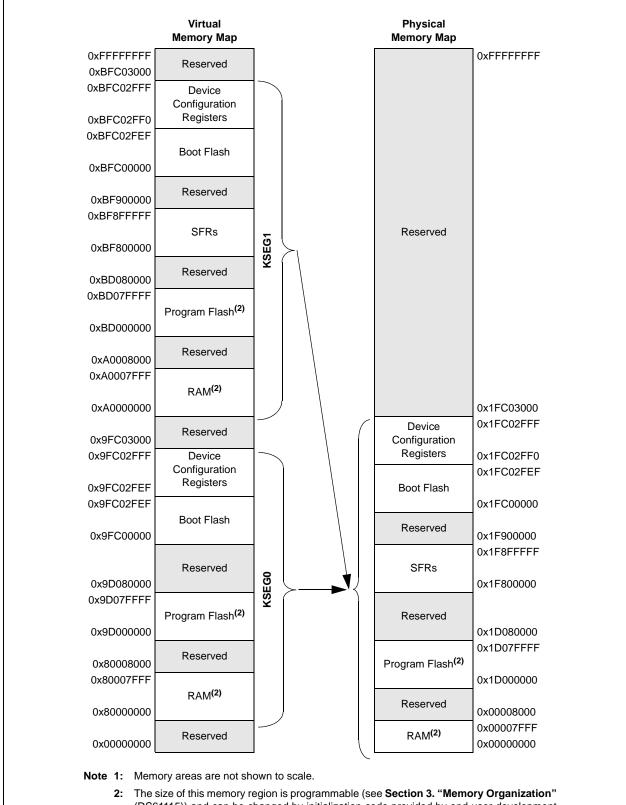

### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX340F128H, PIC32MX340F128L, PIC32MX440F128H AND PIC32MX440F128L DEVICES<sup>(1)</sup>

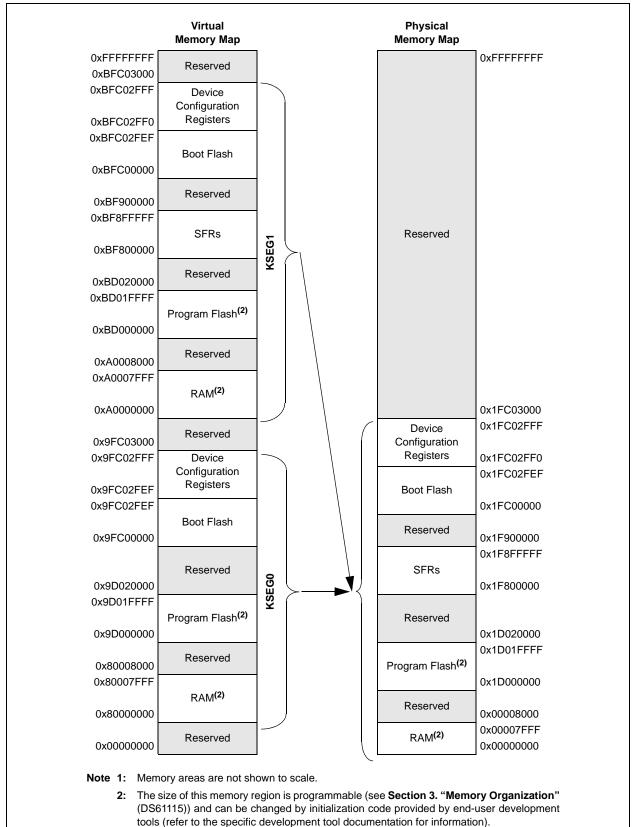

## FIGURE 4-6: MEMORY MAP ON RESET FOR PIC32MX340F512H, PIC32MX360F512L, PIC32MX440F512H AND PIC32MX460F512L DEVICES<sup>(1)</sup>

<sup>(</sup>DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

#### TABLE 4-11: UART1-2 REGISTERS MAP

| SSS                         |                       |           |              |        |        |       |               |       |       | Bi     | its              |         |       |          |          |      |        |       |            |

|-----------------------------|-----------------------|-----------|--------------|--------|--------|-------|---------------|-------|-------|--------|------------------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15        | 30/14  | 29/13  | 28/12 | 27/11         | 26/10 | 25/9  | 24/8   | 23/7             | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | —            | _      | —      |       | —             | I     | —     | —      | —                | —       | _     | -        | —        | —    |        | —     | 0000       |

| 0000                        | OINIODE               | 15:0      | ON           | -      | SIDL   | IREN  | RTSMD         |       | UEN   | <1:0>  | WAKE             | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | -            |        | _      |       |               |       | _     | ADM_EN |                  |         |       | ADDR     | 2<7:0>   |      |        |       | 0000       |

| 0010                        | OTOTA                 | 15:0      | UTXISE       | L<1:0> | UTXINV | URXEN | UTXBRK        | UTXEN | UTXBF | TRMT   | URXIS            | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6020                        | U1TXREG               | 31:16     | —            | _      | —      |       | —             |       | _     | —      | —                | —       | —     |          | —        | —    | —      | —     | 0000       |

| 0020                        | UTIANEO               | 15:0      | —            | -      | —      | -     | —             | -     | —     | TX8    |                  |         |       | Transmit | Register |      |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16     | —            | -      | —      | -     | —             | -     | —     | —      | —                | —       | —     | -        | —        | —    | —      | —     | 0000       |

| 0000                        | UNIXALO               | 15:0      | —            | -      | —      |       | _             | -     | —     | RX8    | Receive Register |         |       |          |          |      | 0000   |       |            |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | —            | -      | —      | -     | —             | -     | —     | —      | —                | —       | —     | -        | —        | —    | —      | —     | 0000       |

| 0010                        | OTDICO                | 15:0      | BRG<15:0> 00 |        |        |       |               |       |       |        |                  |         |       |          |          | 0000 |        |       |            |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | —            | _      | —      |       | —             |       | _     | —      | —                | —       | —     |          | —        | —    | —      | —     | 0000       |

| 0200                        | OZINODE               | 15:0      | ON           | -      | SIDL   | IREN  | RTSMD         |       | UEN   | <1:0>  | WAKE             | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | —            | -      | —      | -     | —             | -     | —     | ADM_EN |                  |         |       | ADDR     | 2<7:0>   |      |        |       | 0000       |

| 0210                        | 02017                 | 15:0      | UTXISE       | L<1:0> | UTXINV | URXEN | UTXBRK        | UTXEN | UTXBF | TRMT   | URXIS            | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6220                        | U2TXREG               | 31:16     | —            | -      | —      | -     | —             | -     | —     | —      | —                | —       | —     | -        | —        | —    | —      | —     | 0000       |

| 0220                        | OZIAREO               | 15:0      | —            | -      | —      | -     | —             | -     | —     | TX8    |                  |         |       | Transmit | Register |      |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | -            |        | _      |       |               |       | _     | _      | _                | —       | _     |          | _        | —    | _      | —     | 0000       |

| 0230                        | UZIXINEO              | 15:0      | -            |        | _      |       |               | I     | —     | RX8    |                  |         |       | Receive  | Register |      |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | -            |        | _      |       | -             | _     | -     | _      | —                | _       | _     |          | -        | —    | -      | _     | 0000       |

| 0240                        |                       | 15:0      |              |        |        |       | '. Reset valu |       |       | BRG<   | :15:0>           |         |       |          |          |      |        |       | 0000       |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

### TABLE 4-40: RTCC REGISTERS MAP<sup>(1)</sup>

| SSS                         |                            |                                           |            | Bits       |         |       |            |                   |        |             |                       |            |        |        |              |         |         |       |            |

|-----------------------------|----------------------------|-------------------------------------------|------------|------------|---------|-------|------------|-------------------|--------|-------------|-----------------------|------------|--------|--------|--------------|---------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name           | Bit Range                                 | 31/15      | 30/14      | 29/13   | 28/12 | 27/11      | 26/10             | 25/9   | 24/8        | 23/7                  | 22/6       | 21/5   | 20/4   | 19/3         | 18/2    | 17/1    | 16/0  | All Resets |

| 0200                        | 200 RTCCON 31:1            |                                           | _          | _          | —       | —     |            | -                 |        |             |                       |            | CAL<   | :11:0> |              |         |         |       | 0000       |

| 0200                        | RICCON                     | 15:0                                      | ON         | —          | SIDL    | —     | —          | —                 | —      | —           | RTSECSEL              | RTCCLKON   | —      | —      | RTCWREN      | RTCSYNC | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                    | 31:16                                     | _          |            | —       | —     |            | —                 | —      | _           | _                     | —          |        | —      | —            | —       | —       | —     | 0000       |

| 0210                        | RICALRINI                  | 15:0 ALRMEN CHIME PIV ALRMSYNC AMASK<3:0> |            |            |         |       |            | ARPT<7:0>         |        |             |                       |            |        |        | 0000         |         |         |       |            |

| 0000                        | DTOTIME                    | 31:16                                     |            | HR10       | )<3:0>  |       |            | HR01              | <3:0>  |             | MIN10<3:0> MIN01<3:0> |            |        |        |              |         | xxxx    |       |            |

| 0220                        | RTCTIME                    | 15:0                                      |            | SEC1       | 0<3:0>  |       |            | SEC0 <sup>2</sup> | <3:0>  |             | —                     | _          |        | —      | —            | —       | _       | —     | xx00       |

| 0000                        | RTCDATE                    | 31:16                                     |            | YEAR       | 10<3:0> |       |            | YEAR0             | 1<3:0> |             | MONTH10<3:0>          |            |        |        | MONTH01<3:0> |         |         |       | xxxx       |

| 0230                        | RICDATE                    | 15:0                                      |            | DAY1       | 0<3:0>  |       |            | DAY0'             | <3:0>  |             | _                     | _          | _      | _      |              | WDAY    | 1<3:0>  |       | xx0x       |

| 0040                        |                            | 31:16                                     |            | MIN1       | 0<3:0>  |       |            | MIN01             | <3:0>  |             |                       | MIN10<3:0> |        |        |              | MIN01   | <3:0>   |       | xxxx       |

| 0240                        | ALRMTIME                   | 15:0                                      | SEC10<3:0> |            |         |       | SEC01<3:0> |                   |        |             | _                     | _          | _      | _      | -            | —       | _       | _     | xx00       |

| 0050                        |                            | 31:16                                     | _          | _          | —       | -     | —          | —                 | —      | —           |                       | MONTH1     | 0<3:0> |        |              | MONTH   | 01<3:0> |       | 00xx       |

| 0250                        | 0 ALRMDATE 15:0 DAY10<3:0> |                                           |            | DAY01<3:0> |         |       |            |                   |        | WDAY01<3:0> |                       |            |        | xx0x   |              |         |         |       |            |

as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### TABLE 4-41: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess                         |                  |           |                       |          |          |          |          |          |             | Bi      | its     |         |            |         |         |           |             |         |            |

|-----------------------------|------------------|-----------|-----------------------|----------|----------|----------|----------|----------|-------------|---------|---------|---------|------------|---------|---------|-----------|-------------|---------|------------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31/15                 | 30/14    | 29/13    | 28/12    | 27/11    | 26/10    | 25/9        | 24/8    | 23/7    | 22/6    | 21/5       | 20/4    | 19/3    | 18/2      | 17/1        | 16/0    | All Resets |

| 2550                        | DEVCFG3          | 31:16     | —                     | _        | —        | —        | —        | —        |             | —       | —       | —       | —          | —       | —       | —         | —           | —       | xxxx       |

| ZFFU                        | DEVCEGS          | 15:0      | USERID15              | USERID14 | USERID13 | USERID12 | USERID11 | USERID10 | USERID9     | USERID8 | USERID7 | USERID6 | USERID5    | USERID4 | USERID3 | USERID2   | USERID1     | USERID0 | xxxx       |

| 2554                        | DEVCFG2          | 31:16     | —                     | _        | —        | _        | —        |          |             | —       | —       | —       | —          | _       | _       | FI        | PLLODIV<2:  | 0>      | xxxx       |

| 2664                        | DEVCFG2          | 15:0      | UPLLEN <sup>(1)</sup> | -        | -        | —        | —        | UP       | LLIDIV<2:0> | (1)     | —       | F       | PLLMUL<2:0 | )>      | —       | F         | PLLIDIV<2:0 | )>      | xxxx       |

| 2550                        | DEVCFG1          | 31:16     | —                     | -        | -        | —        | —        | —        | —           | —       | FWDTEN  | —       | —          |         | V       | VDTPS<4:0 | >           |         | xxxx       |

| 2660                        | DEVCEGI          | 15:0      | FCKSN                 | /<1:0>   | FPBDI    | V<1:0>   | -        | OSCIOFNC | POSCM       | OD<1:0> | IESO    | -       | FSOSCEN    | -       | —       | I         | FNOSC<2:0>  | >       | xxxx       |

| 2550                        | DEVCFG0          | 31:16     | —                     |          |          | CP       | —        | —        |             | BWP     | —       | _       |            |         | PWP19   | PWP18     | PWP17       | PWP16   | xxxx       |

| 21 FC                       | DEVERGO          | 15:0      | PWP15                 | PWP14    | PWP13    | PWP12    | —        | _        | _           | _       | _       |         | —          | -       | ICESEL  |           | DEBU        | G<1:0>  | xxxx       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

These bits are only available on PIC32MX4XX devices. Note 1:

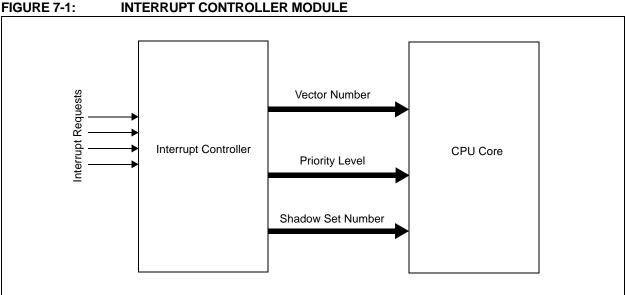

#### 7.0 INTERRUPT CONTROLLER

- **Note 1:** This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS61108) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

PIC32MX3XX/4XX devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX3XX/4XX interrupts module includes the following features:

- · Up to 96 interrupt sources

- Up to 64 interrupt vectors

- · Single and Multi-Vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Module Freeze in Debug mode

- Seven user-selectable priority levels for each vector

- · Four user-selectable subpriority levels within each priority

- Dedicated shadow set for highest priority level

- Software can generate any interrupt

- · User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

#### Several of the registers cited in this section are not in the interrupt controller module. These registers (and Note: bits) are associated with the CPU. Details about them are available in Section 3.0 "CPU".

To avoid confusion, a typographic distinction is made for registers in the CPU. The register names in this section, and all other sections of this manual, are signified by uppercase letters only. The CPU register names are signified by upper and lowercase letters. For example, INTSTAT is an Interrupts register; whereas, IntCtl is a CPU register.

#### FIGURE 7-1:

#### © 2011 Microchip Technology Inc.

### TABLE 7-1: INTERRUPT IRQ AND VECTOR LOCATION

| Interrupt Source <sup>(1)</sup>  | Interrupt Source <sup>(1)</sup> IRQ Vector<br>Number |    |          | Interrupt Bit Location |             |             |  |  |  |  |

|----------------------------------|------------------------------------------------------|----|----------|------------------------|-------------|-------------|--|--|--|--|

| Highest Natural Order F          | Priority                                             |    | Flag     | Enable                 | Priority    | Subpriority |  |  |  |  |

| CT – Core Timer Interrupt        | 0                                                    | 0  | IFS0<0>  | IEC0<0>                | IPC0<4:2>   | IPC0<1:0>   |  |  |  |  |

| CS0 – Core Software Interrupt 0  | 1                                                    | 1  | IFS0<1>  | IEC0<1>                | IPC0<12:10> | IPC0<9:8>   |  |  |  |  |

| CS1 – Core Software Interrupt 1  | 2                                                    | 2  | IFS0<2>  | IEC0<2>                | IPC0<20:18> | IPC0<17:16> |  |  |  |  |

| INT0 – External Interrupt 0      | 3                                                    | 3  | IFS0<3>  | IEC0<3>                | IPC0<28:26> | IPC0<25:24> |  |  |  |  |

| T1 – Timer1                      | 4                                                    | 4  | IFS0<4>  | IEC0<4>                | IPC1<4:2>   | IPC1<1:0>   |  |  |  |  |

| IC1 – Input Capture 1            | 5                                                    | 5  | IFS0<5>  | IEC0<5>                | IPC1<12:10> | IPC1<9:8>   |  |  |  |  |

| OC1 – Output Compare 1           | 6                                                    | 6  | IFS0<6>  | IEC0<6>                | IPC1<20:18> | IPC1<17:16> |  |  |  |  |

| INT1 – External Interrupt 1      | 7                                                    | 7  | IFS0<7>  | IEC0<7>                | IPC1<28:26> | IPC1<25:24> |  |  |  |  |

| T2 – Timer2                      | 8                                                    | 8  | IFS0<8>  | IEC0<8>                | IPC2<4:2>   | IPC2<1:0>   |  |  |  |  |

| IC2 – Input Capture 2            | 9                                                    | 9  | IFS0<9>  | IEC0<9>                | IPC2<12:10> | IPC2<9:8>   |  |  |  |  |

| OC2 – Output Compare 2           | 10                                                   | 10 | IFS0<10> | IEC0<10>               | IPC2<20:18> | IPC2<17:16> |  |  |  |  |

| INT2 – External Interrupt 2      | 11                                                   | 11 | IFS0<11> | IEC0<11>               | IPC2<28:26> | IPC2<25:24> |  |  |  |  |

| T3 – Timer3                      | 12                                                   | 12 | IFS0<12> | IEC0<12>               | IPC3<4:2>   | IPC3<1:0>   |  |  |  |  |

| IC3 – Input Capture 3            | 13                                                   | 13 | IFS0<13> | IEC0<13>               | IPC3<12:10> | IPC3<9:8>   |  |  |  |  |

| OC3 – Output Compare 3           | 14                                                   | 14 | IFS0<14> | IEC0<14>               | IPC3<20:18> | IPC3<17:16> |  |  |  |  |

| INT3 – External Interrupt 3      | 15                                                   | 15 | IFS0<15> | IEC0<15>               | IPC3<28:26> | IPC3<25:24> |  |  |  |  |

| T4 – Timer4                      | 16                                                   | 16 | IFS0<16> | IEC0<16>               | IPC4<4:2>   | IPC4<1:0>   |  |  |  |  |

| IC4 – Input Capture 4            | 17                                                   | 17 | IFS0<17> | IEC0<17>               | IPC4<12:10> | IPC4<9:8>   |  |  |  |  |

| OC4 – Output Compare 4           | 18                                                   | 18 | IFS0<18> | IEC0<18>               | IPC4<20:18> | IPC4<17:16> |  |  |  |  |

| INT4 – External Interrupt 4      | 19                                                   | 19 | IFS0<19> | IEC0<19>               | IPC4<28:26> | IPC4<25:24> |  |  |  |  |

| T5 – Timer5                      | 20                                                   | 20 | IFS0<20> | IEC0<20>               | IPC5<4:2>   | IPC5<1:0>   |  |  |  |  |

| IC5 – Input Capture 5            | 21                                                   | 21 | IFS0<21> | IEC0<21>               | IPC5<12:10> | IPC5<9:8>   |  |  |  |  |

| OC5 – Output Compare 5           | 22                                                   | 22 | IFS0<22> | IEC0<22>               | IPC5<20:18> | IPC5<17:16> |  |  |  |  |

| SPI1E – SPI1 Fault               | 23                                                   | 23 | IFS0<23> | IEC0<23>               | IPC5<28:26> | IPC5<25:24> |  |  |  |  |

| SPI1TX – SPI1 Transfer Done      | 24                                                   | 23 | IFS0<24> | IEC0<24>               | IPC5<28:26> | IPC5<25:24> |  |  |  |  |

| SPI1RX – SPI1 Receive Done       | 25                                                   | 23 | IFS0<25> | IEC0<25>               | IPC5<28:26> | IPC5<25:24> |  |  |  |  |

| U1E – UART1 Error                | 26                                                   | 24 | IFS0<26> | IEC0<26>               | IPC6<4:2>   | IPC6<1:0>   |  |  |  |  |

| U1RX – UART1 Receiver            | 27                                                   | 24 | IFS0<27> | IEC0<27>               | IPC6<4:2>   | IPC6<1:0>   |  |  |  |  |

| U1TX – UART1 Transmitter         | 28                                                   | 24 | IFS0<28> | IEC0<28>               | IPC6<4:2>   | IPC6<1:0>   |  |  |  |  |

| I2C1B – I2C1 Bus Collision Event | 29                                                   | 25 | IFS0<29> | IEC0<29>               | IPC6<12:10> | IPC6<9:8>   |  |  |  |  |

| I2C1S – I2C1 Slave Event         | 30                                                   | 25 | IFS0<30> | IEC0<30>               | IPC6<12:10> | IPC6<9:8>   |  |  |  |  |

| I2C1M – I2C1 Master Event        | 31                                                   | 25 | IFS0<31> | IEC0<31>               | IPC6<12:10> | IPC6<9:8>   |  |  |  |  |

| CN – Input Change Interrupt      | 32                                                   | 26 | IFS1<0>  | IEC1<0>                | IPC6<20:18> | IPC6<17:16> |  |  |  |  |

| AD1 – ADC1 Convert Done          | 33                                                   | 27 | IFS1<1>  | IEC1<1>                | IPC6<28:26> | IPC6<25:24> |  |  |  |  |

| PMP – Parallel Master Port       | 34                                                   | 28 | IFS1<2>  | IEC1<2>                | IPC7<4:2>   | IPC7<1:0>   |  |  |  |  |

| CMP1 – Comparator Interrupt      | 35                                                   | 29 | IFS1<3>  | IEC1<3>                | IPC7<12:10> | IPC7<9:8>   |  |  |  |  |

| CMP2 – Comparator Interrupt      | 36                                                   | 30 | IFS1<4>  | IEC1<4>                | IPC7<20:18> | IPC7<17:16> |  |  |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX General Purpose – Features" and TABLE 2: "PIC32MX USB – Features" for available peripherals.

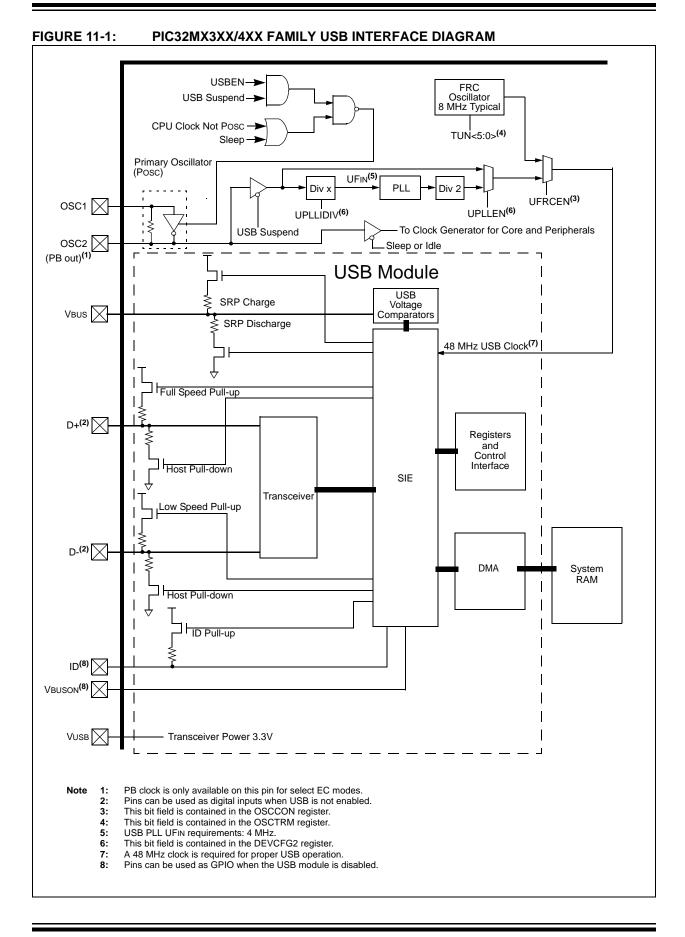

### 11.0 USB ON-THE-GO (OTG)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS61126) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 fullspeed and low-speed embedded host, full-speed device, or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32MX USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers, and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32MX USB module includes the following features:

- USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB OTG Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- Integrated USB Transceiver

- Transaction Handshaking Performed by Hardware

- Endpoint Buffering Anywhere in System RAM

- Integrated DMA to Access System RAM and Flash

Note: The implementation and use of the USB specifications, as well as other third-party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

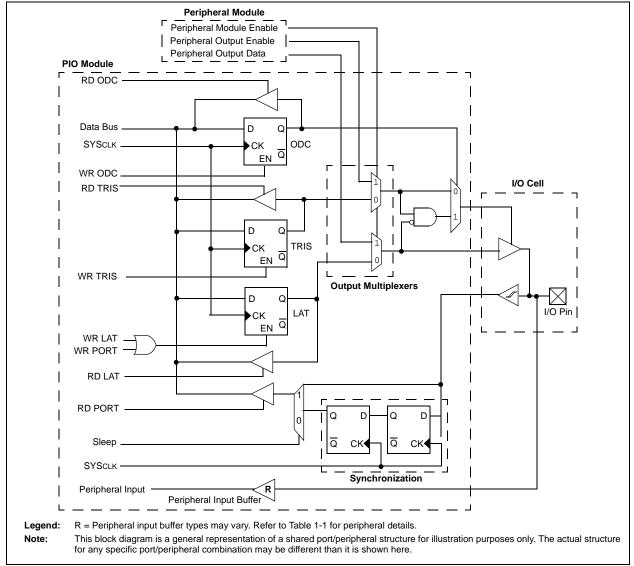

### 12.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS61120) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Following are some of the key features of this module:

- Individual Output Pin Open-drain Enable/Disable

- Individual Input Pin Weak Pull-up Enable/Disable

- Monitor Selective Inputs and Generate Interrupt when Change in Pin State is Detected

- Operation during CPU Sleep and Idle modes

- Fast Bit Manipulation using CLR, SET and INV Registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

| TABLE 27-1: | MIPS32 <sup>®</sup> INSTRUCTION SET (CONTINUED)            |                                                                                                                                   |

|-------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Instruction | Description                                                | Function                                                                                                                          |

| BLEZL       | Branch on Less Than or Equal to Zero Likely <sup>(1)</sup> | <pre>if Rs[31]    Rs == 0    PC += (int)offset else    Ignore Next Instruction</pre>                                              |

| BLTZ        | Branch on Less Than Zero                                   | if Rs[31]<br>PC += (int)offset                                                                                                    |

| BLTZAL      | Branch on Less Than Zero and Link                          | GPR[31] = PC + 8<br>if Rs[31]<br>PC += (int)offset                                                                                |

| BLTZALL     | Branch on Less Than Zero and Link Likely <sup>(1)</sup>    | <pre>GPR[31] = PC + 8 if Rs[31]     PC += (int)offset else     Ignore Next Instruction</pre>                                      |

| BLTZL       | Branch on Less Than Zero Likely <sup>(1)</sup>             | if Rs[31]<br>PC += (int)offset<br>else<br>Ignore Next Instruction                                                                 |

| BNE         | Branch on Not Equal                                        | if Rs != Rt<br>PC += (int)offset                                                                                                  |

| BNEL        | Branch on Not Equal Likely <sup>(1)</sup>                  | if Rs != Rt<br>PC += (int)offset<br>else<br>Ignore Next Instruction                                                               |

| BREAK       | Breakpoint                                                 | Break Exception                                                                                                                   |

| CLO         | Count Leading Ones                                         | Rd = NumLeadingOnes(Rs)                                                                                                           |

| CLZ         | Count Leading Zeroes                                       | Rd = NumLeadingZeroes(Rs)                                                                                                         |

| DERET       | Return from Debug Exception                                | PC = DEPC<br>Exit Debug Mode                                                                                                      |

| DI          | Atomically Disable Interrupts                              | Rt = Status; Status <sub>IE</sub> = 0                                                                                             |

| DIV         | Divide                                                     | LO = (int)Rs / (int)Rt<br>HI = (int)Rs % (int)Rt                                                                                  |

| DIVU        | Unsigned Divide                                            | LO = (uns)Rs / (uns)Rt<br>HI = (uns)Rs % (uns)Rt                                                                                  |

| EHB         | Execution Hazard Barrier                                   | Stop instruction execution<br>until execution hazards are<br>cleared                                                              |

| EI          | Atomically Enable Interrupts                               | Rt = Status; Status <sub>IE</sub> = 1                                                                                             |

| ERET        | Return from Exception                                      | if Status <sub>ERL</sub><br>PC = ErrorEPC<br>else<br>PC = EPC<br>Status <sub>ERL</sub> = 0<br>Status <sub>ERL</sub> = 0<br>LL = 0 |

| EXT         | Extract Bit Field                                          | <pre>Rt = ExtractField(Rs, pos,<br/>size)</pre>                                                                                   |

| INS         | Insert Bit Field                                           | Rt = InsertField(Rs, Rt, pos, size)                                                                                               |

| J           | Unconditional Jump                                         | PC = PC[31:28]    offset<<2                                                                                                       |

|             |                                                            |                                                                                                                                   |

### <u></u>

**Note 1:** This instruction is deprecated and should not be used.

#### 28.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 28.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 28.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response        | Total Pages Sent                      |

|------------|----------------------------------------------------------|---------------------------------------|

| Fror       | n: Name                                                  |                                       |

| 1 101      | Company                                                  |                                       |

|            | Address                                                  |                                       |

|            | City / State / ZIP / Country                             |                                       |

|            | Telephone: ()                                            | FAX: ()                               |

| Арр        | lication (optional):                                     |                                       |

| Wou        | Id you like a reply?YN                                   |                                       |

| Dev        | ice: PIC32MX3XX/4XX                                      | Literature Number: DS61143H           |

| Que        | stions:                                                  |                                       |

| 1.         | What are the best features of this document?             |                                       |

| •          |                                                          |                                       |

| 2.         | How does this document meet your hardware and soft       | ware development needs?               |

|            |                                                          |                                       |

| 3.         | Do you find the organization of this document easy to f  | ollow? If not, why?                   |

|            |                                                          |                                       |

| 4.         | What additions to the document do you think would en     | hance the structure and subject?      |

|            |                                                          |                                       |

| 5.         | What deletions from the document could be made with      | out affecting the overall usefulness? |

|            |                                                          |                                       |

| 6.         | Is there any incorrect or misleading information (what a | and where)?                           |

|            |                                                          |                                       |

| 7.         | How would you improve this document?                     |                                       |

|            |                                                          |                                       |