Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | -                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx360f512l-80i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: PIN NAMES: PIC32MX440F128L, PIC32MX460F256L AND PIC32MX460F512L DEVICES

| Pin      | Eull Bin Name             |

|----------|---------------------------|

| Number   | Full Pin Name             |

| A1       | PMD4/RE4                  |

| A2       | PMD3/RE3                  |

| A3       | TRD0/RG13                 |

| A4       | PMD0/RE0                  |

| A5       | PMD8/RG0                  |

| A6       | PMD10/RF1                 |

| A7       | ENVREG                    |

| A8       | Vss                       |

| A9       | IC5/PMD12/RD12            |

| A10      | OC3/RD2                   |

| A11      | OC2/RD1                   |

| B1       | No Connect (NC)           |

| B2       | RG15                      |

| B3       | PMD2/RE2                  |

| B4       | PMD1/RE1                  |

| B5       | TRD3/RA7                  |

| B6       | PMD11/RF0                 |

| B7       | VCAP/VCORE                |

| B8       | PMRD/CN14/RD5             |

| B9       | OC4/RD3                   |

| B10      | Vss                       |

| B11      | SOSCO/T1CK/CN0/RC14       |

| C1       | PMD6/RE6                  |

| C2       | VDD                       |

| C3       | TRD1/RG12                 |

| C4       | TRD2/RG14                 |

| C4<br>C5 | TRCLK/RA6                 |

| C3<br>C6 | No Connect (NC)           |

| C8<br>C7 |                           |

|          | PMD15/CN16/RD7            |

| C8       | OC5/PMWR/CN13/RD4         |

| C9       |                           |

| C10      | SOSCI/CN1/RC13            |

| C11      | IC4/PMCS1/PMA14/RD11      |

| D1       | T2CK/RC1                  |

| D2       | PMD7/RE7                  |

| D3       | PMD5/RE5                  |

| D4       | Vss                       |

| D5       | Vss                       |

| D6       | No Connect (NC)           |

| D7       | PMD14/CN15/RD6            |

| D8       | CN19/PMD13/RD13           |

| D9       | SDO1/OC1/INT0/RD0         |

| D10      | No Connect (NC)           |

| D11      | SCK1/IC3/PMCS2/PMA15/RD10 |

| E1       | T5CK/SDI1/RC4             |

| E2       | T4CK/RC3                  |

| E3       | SCK2/PMA5/CN8/RG6         |

| E4       | T3CK/RC2                  |

| E5       | VDD                       |

| E6       | PMD9/RG1                  |

| E7       | Vss                       |

|          |                           |

| Pin<br>Number | Full Pin Name            |

|---------------|--------------------------|

| E8            | SDA1/INT4/RA15           |

| E9            | RTCC/IC1/RD8             |

| E10           | SS1/IC2/RD9              |

| E11           | SCL1/INT3/RA14           |

| F1            | MCLR                     |

| F2            | SDO2/PMA3/CN10/RG8       |

| F3            | SS2/PMA2/CN11/RG9        |

| F4            | SDI2/PMA4/CN9/RG7        |

| F5            | Vss                      |

| F6            | No Connect (NC)          |

| F7            | No Connect (NC)          |

| F8            | Vdd                      |

| F9            | OSC1/CLKI/RC12           |

| F10           | Vss                      |

| F11           | OSC2/CLKO/RC15           |

| G1            | INT1/RE8                 |

| G2            | INT2/RE9                 |

| G3            | TMS/RA0                  |

| G4            | No Connect (NC)          |

| G5            | VDD                      |

| G6            | Vss                      |

| G7            | Vss                      |

| G8            | No Connect (NC)          |

| G9            | TDO/RA5                  |

| G10           | SDA2/RA3                 |

| G11           | TDI/RA4                  |

| H1            | AN5/C1IN+/VBUSON/CN7/RB5 |

| H2            | AN4/C1IN-/CN6/RB4        |

| H3            | Vss                      |

| H4            | VDD                      |

| H5            | No Connect (NC)          |

| H6            | VDD                      |

| H7            | No Connect (NC)          |

| H8            | VBUS                     |

| H9            | Vusb                     |

| H10           | D+/RG2                   |

| H11           | SCL2/RA2                 |

| J1            | AN3/C2IN+/CN5/RB3        |

| J2            | AN2/C2IN-/CN4/RB2        |

| J3            | PGED2/AN7/RB7            |

| J4            | AVdd                     |

| J5            | AN11/PMA12/RB11          |

| J6            | TCK/RA1                  |

| J7            | AN12/PMA11/RB12          |

| J8            | No Connect (NC)          |

| J9            | No Connect (NC)          |

| J10           | U1TX/RF8                 |

| J11           | D-/RG3                   |

| K1            | PGEC1/AN1/CN3/RB1        |

| K2            | PGED1/AN0/CN2/RB0        |

| K3            | VREF+/CVREF+/PMA6/RA10   |

|                | Pin                       | Number <sup>(</sup>      | 1)                                                   | Pin         | Buffer |                                                                              |

|----------------|---------------------------|--------------------------|------------------------------------------------------|-------------|--------|------------------------------------------------------------------------------|

| Pin Name       | 64-pin<br>QFN/TQFP        | 100-pin<br>TQFP          | 121-pin<br>XBGA                                      | Ріп<br>Туре | Туре   | Description                                                                  |

| PGED2          | 18                        | 27                       | J3                                                   | I/O         | ST     | Data I/O pin for programming/debugging communication channel 2.              |

| PGEC2          | 17                        | 26                       | L1                                                   | I           | ST     | Clock input pin for programming/debugging communication channel 2.           |

| MCLR           | 7                         | 13                       | F1                                                   | I/P         | ST     | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |

| AVdd           | 19                        | 30                       | J4                                                   | Р           | Р      | Positive supply for analog modules. This pin must be connected at all times. |

| AVss           | 20                        | 31                       | L3                                                   | Р           | Р      | Ground reference for analog modules.                                         |

| Vdd            | 10, 26, 38                | 2, 16, 37,<br>46, 62     | C2, C9,<br>E5, F8,<br>G5, H4,<br>H6, K8              | Ρ           | _      | Positive supply for peripheral logic and I/O pins.                           |

| Vcore/<br>Vcap | 56                        | 85                       | B7                                                   | Р           | _      | Capacitor for Internal Voltage Regulator.                                    |

| Vss            | 9, 25, 41                 | 15, 36,<br>45, 65,<br>75 | A8, B10,<br>D4, D5,<br>E7, F10,<br>F5, G6,<br>G7, H3 | Ρ           |        | Ground reference for logic and I/O pins.                                     |

| VREF+          | 16                        | 29                       | K3                                                   | I           | Analog | Analog voltage reference (high) input.                                       |

| VREF-          | 15                        | 28                       | L2                                                   | I           | Analog | Analog voltage reference (low) input.                                        |

|                | CMOS = CM<br>ST = Schmitt |                          |                                                      |             |        | nalog = Analog input P = Power<br>) = Output I = Input                       |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> | CONTINUED) |  |

|------------|----------------------------------|------------|--|

|            |                                  | oonnoed/   |  |

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

## 2.11 Referenced Sources

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX460F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS61127)

- Section 2. "CPU" (DS61113)

- Section 3. "Memory Organization" (DS61115)

- Section 4. "Prefetch Cache" (DS61119)

- Section 5. "Flash Program Memory" (DS61121)

- Section 6. "Oscillator Configuration" (DS61112)

- Section 7. "Resets" (DS61118)

- Section 8. "Interrupt Controller" (DS61108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS61114)

- Section 10. "Power-Saving Features" (DS61130)

- Section 12. "I/O Ports" (DS61120)

- Section 13. "Parallel Master Port (PMP)" (DS61128)

- Section 14. "Timers" (DS61105)

- Section 15. "Input Capture" (DS61122)

- Section 16. "Output Compare" (DS61111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS61104)

- Section 19. "Comparator" (DS61110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS61109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS61116)

- Section 27. "USB On-The-Go (OTG)" (DS61126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS61125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS61117)

- Section 32. "Configuration" (DS61124)

- Section 33. "Programming and Diagnostics" (DS61129)

# PIC32MX3XX/4XX

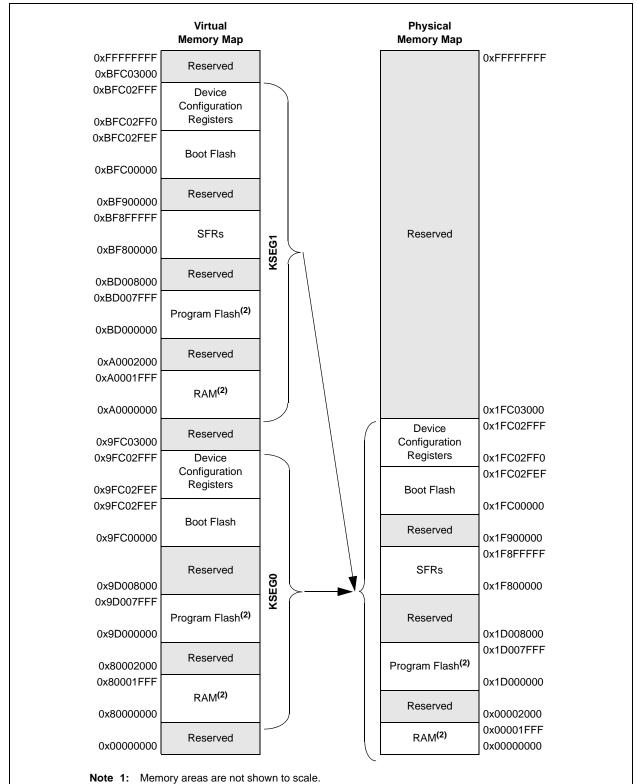

#### FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX320F032H AND PIC32MX420F032H DEVICES<sup>(1)</sup>

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| ess                         |                        |               |         |         |         |             |                             |        |             | Bi       | ts       |          |         |             |               |            |           |        |            |

|-----------------------------|------------------------|---------------|---------|---------|---------|-------------|-----------------------------|--------|-------------|----------|----------|----------|---------|-------------|---------------|------------|-----------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15   | 30/14   | 29/13   | 28/12       | 27/11                       | 26/10  | 25/9        | 24/8     | 23/7     | 22/6     | 21/5    | 20/4        | 19/3          | 18/2       | 17/1      | 16/0   | All Resets |

| 1000                        | INTCON                 | 31:16         | _       | —       | —       |             |                             | —      | -           |          | _        | —        | _       | -           | —             |            | —         | SS0    | 00         |

| 1000                        | INTCOM                 | 15:0          |         | —       | —       | MVEC        | _                           |        | TPC<2:0>    |          | _        | _        | _       | INT4EP      | INT3EP        | INT2EP     | INT1EP    | INT0EP | 00         |

| 1010                        | INTSTAT <sup>(2)</sup> | 31:16         | _       | _       | _       |             | _                           |        | _           |          |          | _        |         |             | _             | _          | _         | _      | 00         |

| 1010                        | INIGIAI                | 15:0          | —       | _       | _       |             |                             |        | SRIPL<2:0>  |          |          | _        |         |             | VEC           | <5:0>      |           |        | 00         |

| 1020                        | IPTMR                  | 31:16<br>15:0 |         |         |         |             | IPTMR<31:0>                 |        |             |          |          |          |         |             |               | 00         |           |        |            |

|                             |                        | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF | U1TXIF      | U1RXIF                      | U1EIF  | SPI1RXIF    | SPI1TXIF | SPI1EIF  | OC5IF    | IC5IF   | T5IF        | INT4IF        | OC4IF      | IC4IF     | T4IF   | 00         |

| 1030                        | IFS0                   | 15:0          | INT3IF  | OC3IF   | IC3IF   | T3IF        | INT2IF                      | OC2IF  | IC2IF       | T2IF     | INT1IF   | OC1IF    | IC1IF   | T1IF        | INT0IF        | CS1IF      | CS0IF     | CTIF   | 00         |

|                             | 1504                   | 31:16         | _       | _       | _       | _           | _                           | _      | USBIF       | FCEIF    | _        | _        | _       | _           | <b>DMA3IF</b> | DMA2IF     | DMA1IF    | DMA0IF | 00         |

| 1040                        | IFS1                   | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF | I2C2SIF     | I2C2BIF                     | U2TXIF | U2RXIF      | U2EIF    | SPI2RXIF | SPI2TXIF | SPI2EIF | CMP2IF      | CMP1IF        | PMPIF      | AD1IF     | CNIF   | 00         |

| 4000                        | 15.00                  | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE | U1TXIE      | U1RXIE                      | U1EIE  | SPI1RXIE    | SPI1TXIE | SPI1EIE  | OC5IE    | IC5IE   | T5IE        | INT4IE        | OC4IE      | IC4IE     | T4IE   | 00         |

| 1060                        | IEC0                   | 15:0          | INT3IE  | OC3IE   | IC3IE   | T3IE        | INT2IE                      | OC2IE  | IC2IE       | T2IE     | INT1IE   | OC1IE    | IC1IE   | T1IE        | INT0IE        | CS1IE      | CS0IE     | CTIE   | 00         |

| 4070                        | IEC1                   | 31:16         | —       | —       | _       |             |                             | -      | USBIE       | FCEIE    |          | —        |         |             | DMA3IE        | DMA2IE     | DMA1IE    | DMA0IE | 00         |

| 1070                        | IECT                   | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE | I2C2SIE     | I2C2BIE                     | U2TXIE | U2RXIE      | U2EIE    | SPI2RXIE | SPI2TXIE | SPI2EIE | CMP2IE      | CMP1IE        | PMPIE      | AD1IE     | CNIE   | 00         |

| 1090                        | IPC0                   | 31:16         | —       | —       | —       | INT0IP<2:0> |                             | INTOIS | S<1:0>      | _        | —        | _        |         | CS1IP<2:0>  |               | CS1IS      | S<1:0>    | 00     |            |

| 1090                        | IFCU                   | 15:0          | _       | -       | -       | CS0IP<2:0>  |                             | CSOIS  | i<1:0>      | _        | -        | _        |         | CTIP<2:0>   |               | CTIS       | <1:0>     | 00     |            |

| 10A0                        | IPC1                   | 31:16         | —       | -       | -       |             | NT1IP<2:0>                  |        | INT1IS      | S<1:0>   |          | -        | -       | OC1IP<2:0>  |               | OC1IS      | S<1:0>    | 00     |            |

| IUAU                        | 1101                   | 15:0          | —       | _       | _       |             | IC1IP<2:0>                  |        | IC1IS<1:0>  |          |          | -        |         |             | T1IP<2:0>     |            | T1IS<1:0> |        | 00         |

| 10B0                        | IPC2                   | 31:16         | —       | —       | —       |             | NT2IP<2:0>                  |        | INT2IS<1:0> |          | —        | —        | —       | OC2IP<2:0>  |               | OC2IS<1:0> |           | 00     |            |

| TODO                        | 11 02                  | 15:0          | _       | —       | —       |             | IC2IP<2:0>                  |        | IC2IS       | <1:0>    | _        | —        | _       |             | T2IP<2:0>     |            | T2IS      | <1:0>  | 00         |

| 10C0                        | IPC3                   | 31:16         | _       | —       | —       |             | NT3IP<2:0>                  |        |             | S<1:0>   | _        | —        | _       |             | OC3IP<2:0>    |            |           | S<1:0> | 00         |

| 1000                        |                        | 15:0          | _       |         | —       |             | IC3IP<2:0>                  |        | IC3IS       |          | _        | —        | _       |             | T3IP<2:0>     |            | T3IS      | <1:0>  | 00         |

| 10D0                        | IPC4                   | 31:16         | _       |         | —       |             | NT4IP<2:0>                  | •      | INT4IS      | S<1:0>   | _        | —        | _       |             | OC4IP<2:0>    |            | OC4IS     | S<1:0> | 00         |

|                             |                        | 15:0          | _       |         | —       |             | IC4IP<2:0>                  |        | IC4IS       |          | _        | —        | _       |             | T4IP<2:0>     |            |           | <1:0>  | 00         |

| 10E0                        | IPC5                   | 31:16         | _       | —       | _       |             | SPI1IP<2:0>                 |        |             | 6<1:0>   | _        | —        | _       |             | OC5IP<2:0>    |            |           | S<1:0> | 00         |

|                             |                        | 15:0          | _       | —       | —       |             | IC5IP<2:0>                  |        | IC5IS       |          | —        | —        | _       |             | T5IP<2:0>     |            |           | <1:0>  | 00         |

| 10F0                        | IPC6                   | 31:16         | _       | —       | —       |             | AD1IP<2:0>                  |        | AD1IS       |          | —        | —        | _       |             | CNIP<2:0>     |            |           | <1:0>  | 00         |

|                             |                        | 15:0          | —       | —       | —       |             | I2C1IP<2:0>                 |        | 12C115      |          | —        | —        | —       |             | U1IP<2:0>     |            |           | <1:0>  | 00         |

| 1100                        | IPC7                   | 31:16         | —       | _       | —       |             | SPI2IP<2:0>                 |        | SPI2IS      |          | _        | —        | _       |             | CMP2IP<2:0    |            |           | S<1:0> | 00         |

|                             |                        | 15:0          | _       | —       | —       |             | CMP1IP<2:0                  |        | CMP1I       |          | _        | —        | _       |             | PMPIP<2:0>    |            |           | S<1:0> | 00         |

| 1110                        | IPC8                   | 31:16         | _       | —       | —       |             | RTCCIP<2:0>                 |        | RTCCI       |          | —        | —        | —       | F           | SCMIP<2:0     | >          |           | S<1:0> | 00         |

|                             |                        | 15:0          | —       | —       | —       |             | I2C2IP<2:0>                 |        |             | S<1:0>   | _        | —        | —       |             | U2IP<2:0>     |            | U2IS<1:0> |        | 00         |

| 1120                        | IPC9                   | 31:16         | _       | —       | —       |             | MA3IP<2:0                   |        | DMA3I       |          | —        | —        | —       | DMA2IP<2:0> |               |            | S<1:0>    | 00     |            |

|                             |                        | 15:0          | _       | _       | -       |             | 0MA1IP<2:0                  | >      | DMA1        | S<1:0>   | _        | -        | _       | [           | DMA0IP<2:0    | >          | DMA0      | S<1:0> | 00         |

| 1140                        | IPC11                  | 31:16         | _       | _       | —       | _           | -                           | —      | —           | —        | _        | _        | _       | —           | -             | —          | -         |        | 000        |

| Legen                       | L                      | 15:0          |         | —       | L —     |             | USBIP<2:0><br>0'. Reset val |        |             | 5<1:0>   | —        | —        | —       |             | FCEIP<2:0>    |            | FCEIS     | S<1:0> | 000        |

#### TABLE 4-2: INTERRUPT REGISTERS MAP FOR PIC32MX440F128L, PIC32MX460F256L AND PIC32MX460F512L DEVICES ONLY<sup>(1)</sup>

Note 1: Except where noted, all registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX3XX/4XX

2: This register does not have associated CLR, SET, and INV registers.

#### TABLE 4-11: UART1-2 REGISTERS MAP

| sse                         |                       |           |                     |        |        |       |        |       |       | Bi     | its                  |         |       |          |          |      |        |       |            |

|-----------------------------|-----------------------|-----------|---------------------|--------|--------|-------|--------|-------|-------|--------|----------------------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15               | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8   | 23/7                 | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     |                     | -      | —      | _     | _      | _     | _     | _      | -                    | —       | _     | -        | —        | —    | —      | —     | 0000       |

| 0000                        | OINIODE               | 15:0      | ON                  | -      | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>  | WAKE                 | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | —                   | -      | —      | -     | —      | -     | -     | ADM_EN |                      |         |       | ADDR     | 2<7:0>   |      |        |       | 0000       |

| 0010                        | OTOTA                 | 15:0      | UTXISE              | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI               | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6020                        | U1TXREG               | 31:16     | —                   | -      | —      |       | _      | -     | -     | _      | -                    | -       |       | -        | —        | —    | —      | —     | 0000       |

| 0020                        | UTTAKEG               | 15:0      | —                   |        | —      |       |        | I     |       | TX8    |                      |         |       | Transmit | Register |      |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16     | —                   |        | —      |       |        |       | 1     | _      |                      | -       |       |          | _        | _    | _      | —     | 0000       |

| 0030                        | UINAREG               | 15:0      | —                   |        | —      |       |        |       |       | RX8    |                      |         |       | Receive  | Register |      |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | —                   |        | _      |       |        |       |       | _      |                      | —       |       |          | _        | _    | _      | —     | 0000       |

| 0040                        | OTDING                | 15:0      |                     |        |        |       |        |       |       | BRG<   | :15:0>               |         |       |          |          |      |        |       | 0000       |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | —                   | -      | —      |       | _      | -     | -     | _      | -                    | -       |       | -        | —        | —    | —      | —     | 0000       |

| 0200                        | OZIVIODE              | 15:0      | ON                  |        | SIDL   | IREN  | RTSMD  | I     | UEN   | <1:0>  | WAKE                 | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | —                   |        | —      |       |        |       | 1     | ADM_EN |                      |         |       | ADDR     | l<7:0>   |      |        |       | 0000       |

| 0210                        | 02017                 | 15:0      | UTXISE              | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI               | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6220                        | U2TXREG               | 31:16     | —                   |        | —      |       |        | I     |       | -      |                      | -       | I     |          | _        | -    | —      | —     | 0000       |

| 0220                        | OZTAREO               | 15:0      | —                   |        | —      |       |        |       | 1     | TX8    |                      |         |       | Transmit | Register |      |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | —                   |        | —      |       | _      | _     |       | _      | -                    | _       | _     |          | —        | —    | —      | _     | 0000       |

| 0230                        | UZIXINEO              | 15:0      | —                   |        | —      |       |        | I     |       | RX8    | B Receive Register 0 |         |       |          |          | 0000 |        |       |            |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | —                   |        | _      |       | -      | _     |       | _      | —                    | —       | _     |          | -        | —    | -      | _     | 0000       |

| 0240                        | OZDING: /             | 15:0      | 15:0 BRG<15:0> 0000 |        |        |       |        |       |       |        |                      |         | 0000  |          |          |      |        |       |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

## TABLE 4-13: ADC REGISTERS MAP (CONTINUED)

| ess                         |                  |           |                                      |                                    |       |       |       |       |        | В           | its       |          |      |      |      |      |      |      |            |

|-----------------------------|------------------|-----------|--------------------------------------|------------------------------------|-------|-------|-------|-------|--------|-------------|-----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15                                | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8        | 23/7      | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9110                        | ADC1BUFA         | 31:16     |                                      | ADC Result Word A (ADC1BUFA<31:0>) |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| -                           |                  | 15:0      |                                      | 000                                |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 0120                        | ADC1BUFB         | 31:16     | ADC Browth Word P (ADC4PI JEP -310-) |                                    |       |       |       |       |        |             |           | 0000     |      |      |      |      |      |      |            |

| 9120                        | ADCIBUEB         | 15:0      |                                      | ADC Result Word B (ADC1BUFB<31:0>) |       |       |       |       |        |             |           |          | 0000 |      |      |      |      |      |            |

| 0400                        |                  | 31:16     |                                      |                                    |       |       |       |       |        |             |           |          |      |      |      |      |      |      | 0000       |

| 9130                        | ADC1BUFC         | 15:0      |                                      |                                    |       |       |       |       | ADC RE | suit word C | (ADC1BUFC | ><31:0>) |      |      |      |      |      |      | 0000       |

| 04.40                       |                  | 31:16     |                                      |                                    |       |       |       |       |        |             |           |          |      |      |      |      |      |      | 0000       |

| 9140                        | ADC1BUFD         | 15:0      |                                      |                                    |       |       |       |       | ADC RE | suit word D | (ADC1BUFE | )<31:0>) |      |      |      |      |      |      | 0000       |

| 0450                        |                  | 31:16     |                                      |                                    |       |       |       |       |        |             |           |          |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 15:0      | ADC Result Word E (ADC1BUFE<31:0>)   |                                    |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

| 0400                        |                  | 31:16     |                                      |                                    |       |       |       |       |        |             |           |          | 0000 |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 15:0      | ADC Result Word F (ADC1BUFF<31:0>)   |                                    |       |       |       |       |        |             |           |          |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS61121) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

PIC32MX3XX/4XX devices contain an internal program Flash memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self Programming (RTSP)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- EJTAG Programming

#### EXAMPLE 5-1:

NVMCON = 0x4004;

// Enable and configure for erase operation

Wait(delay);

// Delay for 6 µs for LVDstartup

NVMKEY = 0xAA996655;

NVMKEY = 0x556699AA;

NVMCONSET = 0x8000;

// Initiate operation

while(NVMCONbits.WR==1);

// Wait for current operation to complete

RTSP is performed by software executing from either Flash or RAM memory. EJTAG is performed using the EJTAG port of the device and a EJTAG capable programmer. ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP. RTSP techniques are described in this chapter. The ICSP and EJTAG methods are described in the "*PIC32MX Flash Programming Specification*" (DS61145), which can be downloaded from the Microchip web site.

**Note:** Flash LVD Delay (LVDstartup) must be taken into account between setting up and executing any Flash command operation. See Example 5-1 for a code example to set up and execute a Flash command operation.

| Interrupt Source <sup>(1)</sup>     | IRQ      | Vector<br>Number | Interrupt Bit Location |          |              |             |  |  |  |  |

|-------------------------------------|----------|------------------|------------------------|----------|--------------|-------------|--|--|--|--|

| Highest Natural Order F             | Priority |                  | Flag                   | Enable   | Priority     | Subpriority |  |  |  |  |

| SPI2E – SPI2 Fault                  | 37       | 31               | IFS1<5>                | IEC1<5>  | IPC7<28:26>  | IPC7<25:24> |  |  |  |  |

| SPI2TX – SPI2 Transfer Done         | 38       | 31               | IFS1<6>                | IEC1<6>  | IPC7<28:26>  | IPC7<25:24> |  |  |  |  |

| SPI2RX – SPI2 Receive Done          | 39       | 31               | IFS1<7>                | IEC1<7>  | IPC7<28:26>  | IPC7<25:24> |  |  |  |  |

| U2E – UART2 Error                   | 40       | 32               | IFS1<8>                | IEC1<8>  | IPC8<4:2>    | IPC8<1:0>   |  |  |  |  |

| U2RX – UART2 Receiver               | 41       | 32               | IFS1<9>                | IEC1<9>  | IPC8<4:2>    | IPC8<1:0>   |  |  |  |  |

| U2TX – UART2 Transmitter            | 42       | 32               | IFS1<10>               | IEC1<10> | IPC8<4:2>    | IPC8<1:0>   |  |  |  |  |

| I2C2B – I2C2 Bus Collision Event    | 43       | 33               | IFS1<11>               | IEC1<11> | IPC8<12:10>  | IPC8<9:8>   |  |  |  |  |

| I2C2S – I2C2 Slave Event            | 44       | 33               | IFS1<12>               | IEC1<12> | IPC8<12:10>  | IPC8<9:8>   |  |  |  |  |

| I2C2M – I2C2 Master Event           | 45       | 33               | IFS1<13>               | IEC1<13> | IPC8<12:10>  | IPC8<9:8>   |  |  |  |  |

| FSCM – Fail-Safe Clock Monitor      | 46       | 34               | IFS1<14>               | IEC1<14> | IPC8<20:18>  | IPC8<17:16> |  |  |  |  |

| RTCC – Real-Time Clock and Calendar | 47       | 35               | IFS1<15>               | IEC1<15> | IPC8<28:26>  | IPC8<25:24> |  |  |  |  |

| DMA0 – DMA Channel 0                | 48       | 36               | IFS1<16>               | IEC1<16> | IPC9<4:2>    | IPC9<1:0>   |  |  |  |  |

| DMA1 – DMA Channel 1                | 49       | 37               | IFS1<17>               | IEC1<17> | IPC9<12:10>  | IPC9<9:8>   |  |  |  |  |

| DMA2 – DMA Channel 2                | 50       | 38               | IFS1<18>               | IEC1<18> | IPC9<20:18>  | IPC9<17:16> |  |  |  |  |

| DMA3 – DMA Channel 3                | 51       | 39               | IFS1<19>               | IEC1<19> | IPC9<28:26>  | IPC9<25:24> |  |  |  |  |

| FCE – Flash Control Event           | 56       | 44               | IFS1<24>               | IEC1<24> | IPC11<4:2>   | IPC11<1:0>  |  |  |  |  |

| USB                                 | 57       | 45               | IFS1<25>               | IEC1<25> | IPC11<12:10> | IPC11<9:8>  |  |  |  |  |

| Lowest Natural Order Priority       |          |                  |                        |          |              |             |  |  |  |  |

## TABLE 7-1: INTERRUPT IRQ AND VECTOR LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX General Purpose – Features" and TABLE 2: "PIC32MX USB – Features" for available peripherals.

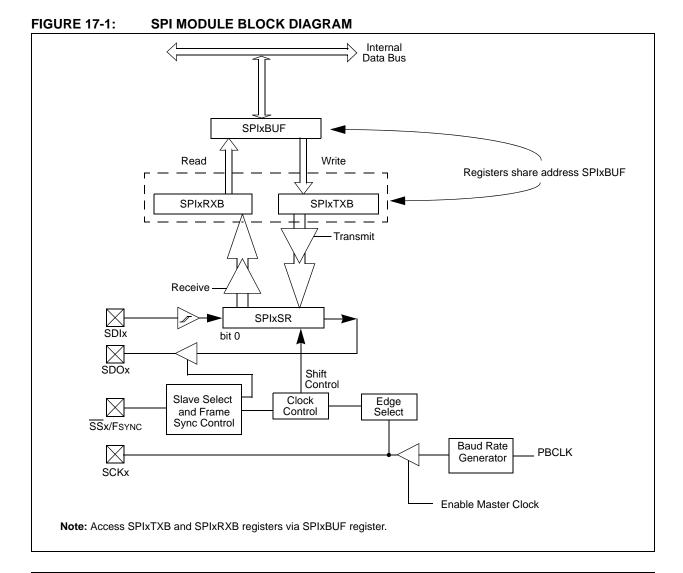

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32MX SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Following are some of the key features of this module:

- Master and Slave Modes Support

- Four Different Clock Formats

- Framed SPI Protocol Support

- User Configurable 8-bit, 16-bit and 32-bit Data

Width

- Separate SPI Data Registers for Receive and Transmit

- Programmable Interrupt Event on every 8-bit, 16-bit and 32-bit Data Transfer

- Operation during CPU Sleep and Idle Mode

- Fast Bit Manipulation using CLR, SET and INV Registers

## 25.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS61130) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This section describes power-saving for the PIC32MX3XX/4XX. The PIC32MX devices offer a total of nine methods and modes that are organized into two categories that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

### 25.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK, and by individually disabling modules. These methods are grouped into the following modes:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

- Peripheral Bus Scaling mode: peripherals are clocked at programmable fraction of the CPU clock (SYSCLK).

## 25.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which halt the clock to the CPU. These modes operate with all clock sources, as listed below:

• Posc Idle Mode: the system clock is derived from the Posc. The system clock source continues to operate.

Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle Mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle Mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

• LPRC Idle Mode: the system clock is derived from the LPRC.

Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

• Sleep Mode: the CPU, the system clock source, and any peripherals that operate from the system clock source, are halted.

Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

### 25.3 Power-Saving Operation

The purpose of all power-saving is to reduce power consumption by reducing the device clock frequency. To achieve this, low-frequency clock sources can be selected. In addition, the peripherals and CPU can be halted or disabled to further reduce power consumption.

#### 25.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device Power-Saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep mode.

Sleep mode includes the following characteristics:

- The CPU is halted.

- The system clock source is typically shut down. See **Section 25.3.2 "Idle Mode**" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit, if enabled, remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator, e.g., RTCC and Timer 1.

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to Section 11.0 "USB On-The-Go (OTG)" for specific details.

- Some modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.

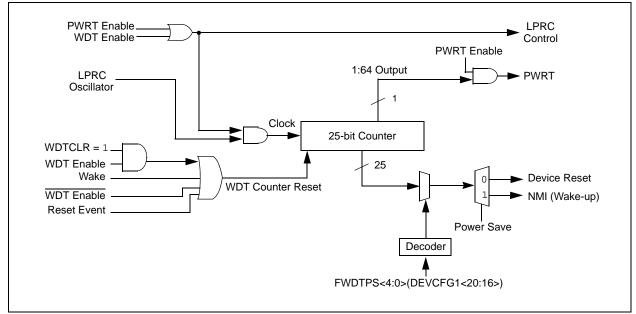

## 26.2 Watchdog Timer (WDT)

This section describes the operation of the WDT and Power-Up Timer of the PIC32MX3XX/4XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- · Can wake the device from Sleep or Idle

#### FIGURE 26-1: WATCHDOG AND POWER-UP TIMER BLOCK DIAGRAM

## 28.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 28.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 28.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines  $\mathsf{PIC32MX3XX/4XX}$  AC characteristics and timing parameters.

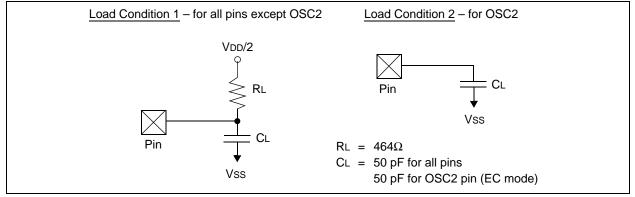

#### FIGURE 29-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 29-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHA        | RACTER | ISTICS                | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                                                   |     |    |                           |  |  |  |  |

|---------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|----|---------------------------|--|--|--|--|

| Param.<br>No. | Symbol | Characteristics       | Min.                                                                                                                                                                                   | Min. Typical <sup>(1)</sup> Max. Units Conditions |     |    | Conditions                |  |  |  |  |

| DO56          | Сю     | All I/O pins and OSC2 |                                                                                                                                                                                        | _                                                 | 50  | pF | EC mode                   |  |  |  |  |

| DO58          | Св     | SCLx, SDAx            | _                                                                                                                                                                                      | —                                                 | 400 | pF | In l <sup>2</sup> C™ mode |  |  |  |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

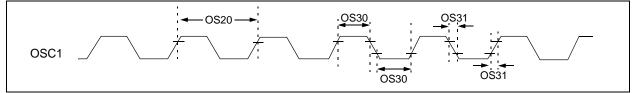

#### FIGURE 29-2: EXTERNAL CLOCK TIMING

#### TABLE 29-34: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHA        | ARACTERIS  | STICS                          | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |             |                   |       |                                                         |  |  |  |  |

|---------------|------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-------|---------------------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol     | Characteristics                | Min.                                                                                                                                                                                     | Typical     | -40°C ≤1/<br>Max. | Units | C for V-Temp<br>Conditions                              |  |  |  |  |

| ADC Ac        | curacy – N | leasurements with Inter        | nal VREF+/VR                                                                                                                                                                             | EF-         |                   |       | •                                                       |  |  |  |  |

| AD20d         | Nr         | Resolution                     | 1                                                                                                                                                                                        | 0 data bits |                   | bits  | (Note 3)                                                |  |  |  |  |

| AD21d         | INL        | Integral Nonlinearity          |                                                                                                                                                                                          | _           | <±1               | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |  |

| AD22d         | DNL        | Differential Nonlinearity      | —                                                                                                                                                                                        | _           | <±1               | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |  |  |

| AD23d         | Gerr       | Gain Error                     | —                                                                                                                                                                                        | _           | <±4               | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |  |

| AD24d         | EOFF       | Offset Error                   |                                                                                                                                                                                          | _           | <±2               | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |  |

| AD25d         | —          | Monotonicity                   | —                                                                                                                                                                                        | —           | _                 | —     | Guaranteed                                              |  |  |  |  |

| Dynami        | c Performa | ance                           |                                                                                                                                                                                          |             |                   |       |                                                         |  |  |  |  |

| AD31b         | SINAD      | Signal to Noise and Distortion | 55                                                                                                                                                                                       | 58.5        | —                 | dB    | (Notes 3, 4)                                            |  |  |  |  |

| AD34b         | ENOB       | Effective Number of Bits       | 9.0                                                                                                                                                                                      | 9.5         |                   | bits  | (Notes 3, 4)                                            |  |  |  |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with 1 kHz sinewave.

| AC CHA        | ARACTERIS | TICS                                                                             | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |      |       |            |  |  |  |

|---------------|-----------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol    | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                     | Typical | Max. | Units | Conditions |  |  |  |

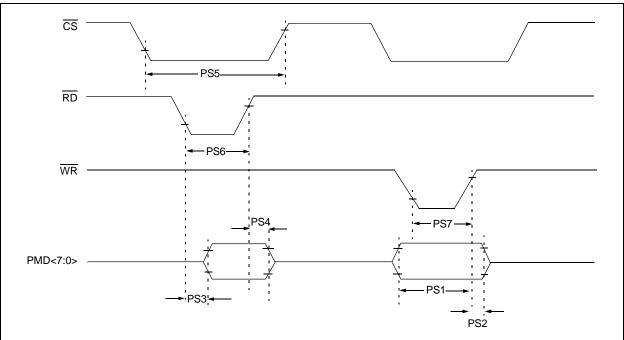

| PS1           | TdtV2wrH  | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                       |         |      | ns    | _          |  |  |  |

| PS2           | TwrH2dtl  | WR or CS Inactive to Data –<br>In Invalid (hold time)                            | 40                                                                                                                                                                                       |         | _    | ns    |            |  |  |  |

| PS3           | TrdL2dtV  | $\overline{RD}$ and $\overline{CS}$ Active to Data –<br>Out Valid                | _                                                                                                                                                                                        |         | 60   | ns    |            |  |  |  |

| PS4           | TrdH2dtl  | RD Active or CS Inactive to Data –<br>Out Invalid                                | 0                                                                                                                                                                                        | _       | 10   | ns    | _          |  |  |  |

| PS5           | Tcs       | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                 | _       | _    | ns    | —          |  |  |  |

| PS6           | Twr       | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                 | _       |      | ns    | —          |  |  |  |

| PS7           | Trd       | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                 | _       |      | ns    |            |  |  |  |

## TABLE 29-37: PARALLEL SLAVE PORT REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

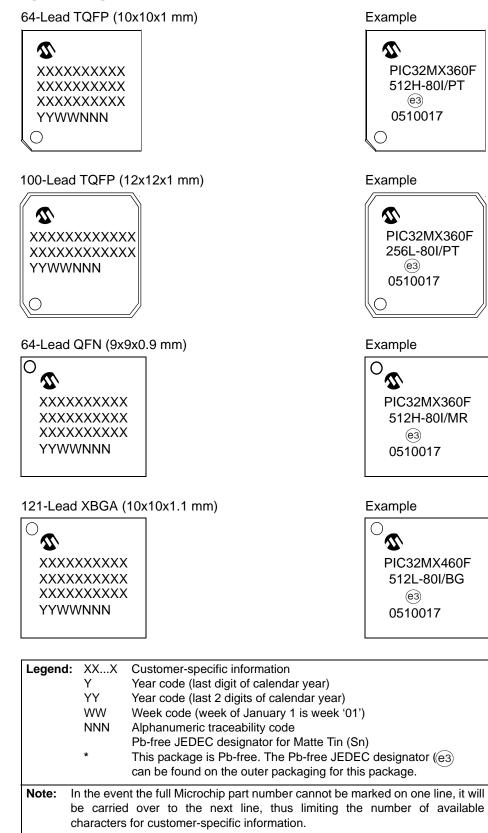

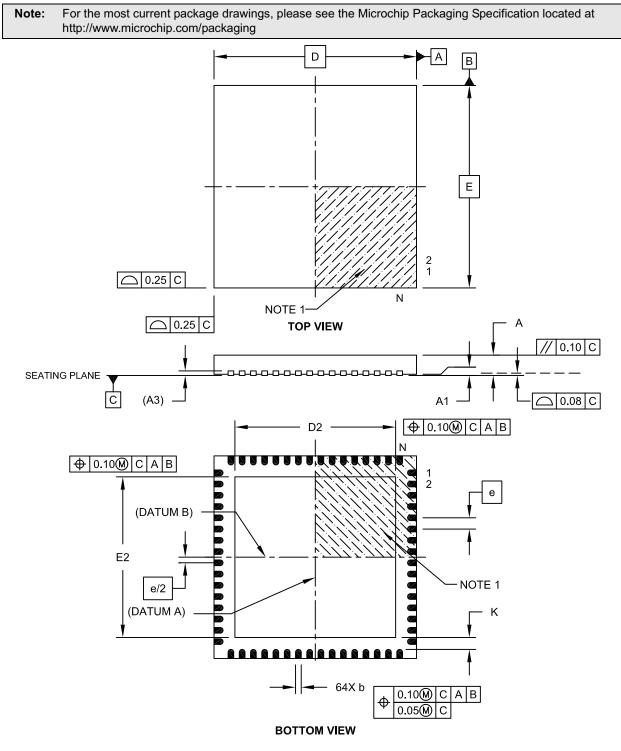

## **30.0 PACKAGING INFORMATION**

## **30.1** Package Marking Information

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

Microchip Technology Drawing C04-149C Sheet 1 of 2

DS61143H-page 194

# PIC32MX3XX/4XX

#### W

| Watchdog Timer       |     |

|----------------------|-----|

| Operation            | 137 |

| WWW Address          | 209 |

| WWW, On-Line Support | 19  |

## **Product Identification System**

| To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.                                                                  |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Microchip Brand<br>Architecture<br>Product Groups<br>Flash Memory Family<br>Program Memory Size<br>Pin Count<br>Tape and Reel Flag (if<br>Speed<br>Temperature Range<br>Package | PIC32 MX 3XX F 512 H T - 80 I / PT - XXX                                                                                                                                                                                                     | Examples:<br>PIC32MX320F032H-40I/PT:<br>General purpose PIC32MX,<br>32 KB program memory,<br>64-pin, Industrial temperature,<br>TQFP package.<br>PIC32MX360F256L-80I/PT:<br>General purpose PIC32MX,<br>256 KB program memory,<br>100-pin, Industrial temperature,<br>TQFP package. |  |

| Flash Memory Family                                                                                                                                                             |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                     |  |

| Architecture                                                                                                                                                                    | MX = 32-bit RISC MCU core                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                     |  |

| Product Groups                                                                                                                                                                  | 3XX = General purpose microcontroller family<br>4XX = USB                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                     |  |

| Flash Memory Family                                                                                                                                                             | F = Flash program memory                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |  |

| Program Memory Size                                                                                                                                                             | 32 = 32K<br>64 = 64K<br>128 = 128K<br>256 = 256K<br>512 = 512K                                                                                                                                                                               |                                                                                                                                                                                                                                                                                     |  |

| Speed                                                                                                                                                                           | 40 = 40 MHz<br>80 = 80 MHz                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                     |  |

| Pin Count                                                                                                                                                                       | H = 64-pin<br>L = 100-pin                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                     |  |

| Temperature Range                                                                                                                                                               | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>V = $-40^{\circ}$ C to $+105^{\circ}$ C (V-Temp)                                                                                                                                      |                                                                                                                                                                                                                                                                                     |  |

| Package                                                                                                                                                                         | PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack)<br>PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)<br>MR = 64-Lead (9x9x0.9 mm) QFN (Plastic Quad Flat)<br>BG = 121-Lead (10x10x1.1 mm) XBGA (Plastic Thin Profile Ball Grid Array) |                                                                                                                                                                                                                                                                                     |  |

| Pattern                                                                                                                                                                         | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                             |                                                                                                                                                                                                                                                                                     |  |