Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              |                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx360f512l-80v-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### TABLE 4-25: PORTD REGISTERS MAP FOR PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F256L, PIC32MX360F512L, PIC32MX440F128L, PIC32MX460F256L AND PIC32MX460F512L DEVICES ONLY<sup>(1)</sup>

| ess                         |                  |           | Bits    |         |         |         |         |         |        |        |        |        |        |        |        |        |        |        |            |

|-----------------------------|------------------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 60C0                        | TRISD            | 31:16     | _       | -       | _       | —       |         |         | _      | _      | —      | _      | —      | —      | —      | _      | _      | -      | 0000       |

| 0000                        | TRISD            | 15:0      | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF       |

| 60D0                        | PORTD            | 31:16     | -       | -       | —       | _       | _       | -       | _      | _      | _      | —      | _      | _      | _      | _      | _      | -      | 0000       |

| 0000                        | FURID            | 15:0      | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx       |

| 60E0                        | LATD             | 31:16     | -       | _       | _       | _       | _       | —       | _      | _      | _      | _      | _      | _      | _      | _      | _      | —      | 0000       |

| OUEU                        | LAID             | 15:0      | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx       |

| 60F0                        | ODCD             | 31:16     | _       |         |         | _       |         |         | _      | _      | _      |        | _      | _      | _      | _      | _      | -      | 0000       |

| 0000                        | 0000             | 15:0      | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 4-26: PORTD REGISTERS MAP FOR PIC32MX320F032H, PIC32MX320F064H, PIC32MX320F128H, PIC32MX340F128H, PIC32MX340F256H, PIC32MX340F512H, PIC32MX420F032H, PIC32MX440F128H, PIC32MX440F256H AND PIC32MX440F512H DEVICES ONLY<sup>(1)</sup>

|                             |                  | r - r     |       |       |       |       |         |         |        |        |        |        |        |        |        |        |        |        |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| ess                         |                  |           |       |       |       |       |         |         |        | Bi     | ts     |        |        |        |        |        |        |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 60C0                        | TRISD            | 31:16     | _     |       |       | _     |         | _       |        |        | _      | —      |        | _      |        |        |        | —      | 0000       |

| 0000                        | IRISD            | 15:0      | —     | —     | _     | —     | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | OFFF       |

| 60D0                        | PORTD            | 31:16     |       | _     | _     | _     | _       | —       | _      | _      | _      | —      | _      | _      | _      | —      | _      | —      | 0000       |

| 0000                        | FORID            | 15:0      |       | -     | -     | _     | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx       |

| 60E0                        | LATD             | 31:16     | -     | 1     |       | -     | 1       | -       |        | 1      | _      | _      | 1      | _      |        |        | 1      | _      | 0000       |

| UULU                        | LAID             | 15:0      | _     |       |       | _     | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx       |

| 60F0                        | ODCD             | 31:16     | _     |       | _     | _     |         | —       | _      |        | _      | —      |        | _      | _      |        |        | —      | 0000       |

| 0010                        | ODCD             | 15:0      | _     | _     |       | -     | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 4-37: PARALLEL MASTER PORT REGISTERS MAP<sup>(1)</sup>

| ess                         |                  |           |           |                                                                                                                                                                                                                                                        |       |       |         |        |        | Bi     | ts      |        |      |       |         |      |       |       |            |

|-----------------------------|------------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------|--------|--------|--------|---------|--------|------|-------|---------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15     | 30/14                                                                                                                                                                                                                                                  | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4  | 19/3    | 18/2 | 17/1  | 16/0  | All Resets |

| 7000                        | PMCON            | 31:16     | _         | _                                                                                                                                                                                                                                                      | _     | _     | —       | -      | —      | _      | _       | _      | _    |       | —       |      |       | _     | 0000       |

| 1000                        |                  | 15:0      | ON        | —                                                                                                                                                                                                                                                      | SIDL  | ADRML | JX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF<    | <1:0>  | ALP  | CS2P  | CS1P    |      | WRSP  | RDSP  | 0000       |

| 7010                        | PMMODE           | 31:16     | —         | —                                                                                                                                                                                                                                                      | _     | -     | _       | _      | _      | —      | —       | -      | _    |       | —       |      |       | _     | 0000       |

| 7010                        |                  | 15:0      | BUSY      | IRQM                                                                                                                                                                                                                                                   | <1:0> | INCM  | <1:0>   | MODE16 | MODE   | <1:0>  | WAITE   | 3<1:0> |      | WAITM | //<3:0> |      | WAITE | <1:0> | 0000       |

| 7020                        | PMADDR           | 31:16     | -         | -                                                                                                                                                                                                                                                      |       | -     | -       |        | -      | -      | -       | -      |      |       | -       |      |       | -     | 0000       |

| 1020                        | FINADDR          | 15:0      | CS2EN/A15 | CS1EN/A14                                                                                                                                                                                                                                              |       |       |         |        |        |        | ADDR    | <13:0> |      |       |         |      |       |       | 0000       |

| 7030                        | PMDOUT           | 31:16     |           |                                                                                                                                                                                                                                                        |       |       |         |        |        | DATAOU | T-31:0> |        |      |       |         |      |       |       | 0000       |

| 1050                        | T MIDOUT         | 15:0      |           |                                                                                                                                                                                                                                                        |       |       |         |        |        | DAIAOU | 1<31.02 |        |      |       |         |      |       |       | 0000       |

| 7040                        | PMDIN            | 31:16     |           |                                                                                                                                                                                                                                                        |       |       |         |        |        | DATAIN | ~31.0>  |        |      |       |         |      |       |       | 0000       |

| 7040                        |                  | 15:0      |           |                                                                                                                                                                                                                                                        |       |       |         |        |        | DATAIN | <01.02  |        |      |       |         |      |       |       | 0000       |

| 7050                        | PMAEN            | 31:16     | -         | -                                                                                                                                                                                                                                                      |       | -     | -       |        | -      | -      | -       | -      |      |       | -       |      |       | -     | 0000       |

| 7050                        | FINALIN          | 15:0      |           |                                                                                                                                                                                                                                                        |       |       |         |        |        | PTEN<  | :15:0>  |        |      |       |         |      |       |       | 0000       |

| 7060                        | PMSTAT           | 31:16     |           |                                                                                                                                                                                                                                                        | _     | _     | —       | _      | —      |        |         | _      | _    | _     | —       | _    | _     |       | 0000       |

| 1000                        | FINISTAL         | 15:0      | IBF       | IBOV                                                                                                                                                                                                                                                   | —     | _     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —    | _     | OB3E    | OB2E | OB1E  | OB0E  | 008F       |

| Legend                      | 1: x = u         |           |           | 3F       IBOV       —       —       IB3F       IB1F       IB0F       OBE       OBUF       —       —       OB3E       OB2E       OB1E       OB0E       008F         ue on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |       |         |        |        |        |         |        |      |       |         |      |       |       |            |

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 4-38: PROGRAMMING AND DIAGNOSTICS REGISTERS MAP

| ess                        |                  | ۵         |       |       |       |       |       |       |      | В    | ts   |      |      |      |        |       |      |      | 6          |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|--------|-------|------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3   | 18/2  | 17/1 | 16/0 | All Resets |

| F200                       | DDPCON           | 31:16     | —     | _     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —      | —     | —    | _    | 0000       |

| F200                       | DDFCON           | 15:0      |       |       | _     | _     | —     | —     | _    | —    | _    | _    | _    | —    | JTAGEN | TROEN | _    |      | 0008       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

NOTES:

#### 18.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C<sup>TM</sup>)" (DS61116) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and accessing hits

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram. The PIC32MX3XX/4XX devices have up to two  $l^2C$  interface modules, denoted as I2C1 and I2C2. Each  $l^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module, 'I2Cx' (x = 1 or 2), offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave Operation.

- I<sup>2</sup>C Slave Mode Supports 7 and 10-bit Address.

- I<sup>2</sup>C Master Mode Supports 7 and 10-bit Address.

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-master Operation; Detects Bus Collision and Arbitrates Accordingly.

- Provides Support for Address Bit Masking.

#### 26.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX3XX/4XX family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-up Timer" (DS61114), Section 32. "Configuration" (DS61124) and Section 33. "Programming and Diagnostics" (DS61129) of the "PIC32 Family Reference Manual", which is available from Microchip the web site (www.microchip.com/PIC32).

PIC32MX3XX/4XX devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- Flexible Device Configuration

- Watchdog Timer

- JTAG Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

#### 26.1 Configuration Bits

The Configuration bits can be programmed to select various device configurations.

| REGISTE      | =R 26-1: D        | EVCFG0: D         | EVICE CON         | FIGURATIC                                   | N WORD 0          |                   |                  |                  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|---------------------------------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                           | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 04-04        | r-0               | r-1               | r-1               | R/P                                         | r-1               | r-1               | r-1              | R/P              |  |  |  |  |  |

| 31:24        | _                 | —                 | —                 | CP                                          | —                 | _                 | _                | BWP              |  |  |  |  |  |

| 00.40        | r-1               | r-1               | r-1               | r-1                                         | R/P               | R/P               | R/P              | R/P              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                                           |                   | PWP               | <7:4>            |                  |  |  |  |  |  |

| 15:8         | R/P               | R/P               | R/P               | R/P                                         | r-1               | r-1               | r-1              | r-1              |  |  |  |  |  |

| 10.0         |                   | PWP<              | <3:0>             |                                             | —                 | _                 | _                | —                |  |  |  |  |  |

| 7.0          | r-1               | r-1               | r-1               | r-1                                         | R/P               | r-1               | R/P              | R/P              |  |  |  |  |  |

| 7:0          | —                 | —                 | —                 | —                                           | ICESEL            | _                 | DEBU             | G<1:0>           |  |  |  |  |  |

|              |                   |                   |                   |                                             |                   |                   |                  |                  |  |  |  |  |  |

| Legend:      |                   |                   |                   |                                             |                   |                   |                  |                  |  |  |  |  |  |

| R = Read     | lable bit         |                   | W = Writable      | e bit                                       | P = Progran       | nmable bit        | r = Reserve      | d bit            |  |  |  |  |  |

| U = Unim     | plemented bit     |                   | -n = Bit Valu     | = Bit Value at POR: ('0', '1', x = Unknown) |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 26-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

- bit 31 **Reserved:** Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection disabled

- 0 = Protection enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

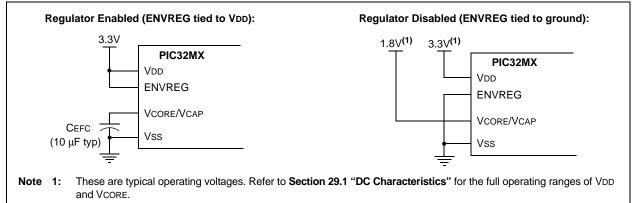

#### 26.3 On-Chip Voltage Regulator

All PIC32MX3XX/4XX device's core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX3XX/4XX incorporate an on-chip regulator providing the required core logic voltage from VDD.

The internal 1.8V regulator is controlled by the ENVREG pin. Tying this pin to VDD enables the regulator, which in turn provides power to the core. A low ESR capacitor (such as tantalum) must be connected to the VCORE/VCAP pin (Figure 26-2). This helps to maintain the stability of the regulator. The recommended value for the filer capacitor is provided in **Section 29.1 "DC Characteristics"**.

| Note: | It is important that the low ESR capacitor |  |  |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | is placed as close as possible to the      |  |  |  |  |  |  |  |  |  |  |  |

|       | VCORE/VCAP pin.                            |  |  |  |  |  |  |  |  |  |  |  |

Tying the ENVREG pin to Vss disables the regulator. In this case, separate power for the core logic at a nominal 1.8V must be supplied to the device on the VCORE/VCAP pin.

Alternatively, the VCORE/VCAP and VDD pins can be tied together to operate at a lower nominal voltage. Refer to Figure 26-2 for possible configurations.

#### 26.3.1 ON-CHIP REGULATOR AND POR

When the voltage regulator is enabled, it takes fixed delay for it to generate output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

If the regulator is disabled, a separate Power-up Timer (PWRT) is automatically enabled. The PWRT adds a fixed delay of TPWRT at device start-up. See **Section 29.0 "Electrical Characteristics"** for more information on TPU AND TPWRT.

#### 26.3.2 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC32MX3XX/4XX devices also have a simple brownout capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 29.1** "**DC Characteristics**".

#### 26.3.3 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VCORE must never exceed VDD by 0.3 volts.

#### FIGURE 26-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

#### 29.1 DC Characteristics

#### TABLE 29-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range  | Temp. Range     | Max. Frequency         |

|----------------|------------|-----------------|------------------------|

| Characteristic | (in Volts) | (in °C)         | PIC32MX3XX/4XX         |

| DC5            | 2.3V-3.6V  | -40°C to +85°C  | 80 MHz (Note 1)        |

| DC5b           | 2.3V-3.6V  | -40°C to +105°C | 80 MHz <b>(Note 1)</b> |

Note 1: 40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.

#### TABLE 29-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol         | Min. | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------------|----------------|------|-------------|------|------|

| Industrial Temperature Devices                                                       |                |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ             | -40  | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                  | TA             | -40  | —           | +85  | °C   |

| V-Temp Temperature Devices                                                           |                |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ             | -40  | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                  | TA             | -40  | —           | +105 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD – S IOH) | PD PINT + PI/O |      |             |      |      |

| I/O Pin Power Dissipation:<br>I/O = S ({VDD - VOH} x IOH) + S (VOL x IOL))           |                |      |             |      |      |

| Maximum Allowed Power Dissipation                                                    | PDMAX          | (    | TJ — TA)/θJ | A    | W    |

#### TABLE 29-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                                         | Symbol | Typical | Max. | Unit | Notes |

|---------------------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 121-Pin XBGA (10x10x1.1 mm) | θја    | 40      | _    | °C/W | 1     |

| Package Thermal Resistance, 100-Pin TQFP (12x12x1 mm)   | θја    | 43      | _    | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP (10x10x1 mm)    | θја    | 47      | _    | °C/W | 1     |

| Package Thermal Resistance, 64-Pin QFN (9x9x0.9 mm)     | θja    | 28      | _    | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 29-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHA        | RACTER    | ISTICS                                                           | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |      |       |            |  |  |  |  |  |

|---------------|-----------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|--|--|

| Param.<br>No. | Symbol    | Characteristics                                                  | Min.                                                                                                                                                                                   | Typical | Max. | Units | Conditions |  |  |  |  |  |

| Operati       | ng Voltag | e                                                                |                                                                                                                                                                                        |         |      |       |            |  |  |  |  |  |

| DC10          | Vdd       | Supply Voltage                                                   | 2.3                                                                                                                                                                                    | —       | 3.6  | V     | —          |  |  |  |  |  |

| DC12          | Vdr       | RAM Data Retention Voltage (Note 1)                              | 1.75                                                                                                                                                                                   | —       |      | V     | _          |  |  |  |  |  |

| DC16          | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | 1.75                                                                                                                                                                                   | _       | 1.95 | V     | _          |  |  |  |  |  |

| DC17          | SVDD      | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                                                                                                                                                   | —       | _    | V/ms  | _          |  |  |  |  |  |

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

| DC CHAR       | ACTERISTIC             | S                                                                               | (unless | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +105^{\circ}C$ for V-Temp |                           |       |                           |  |  |  |  |  |  |

|---------------|------------------------|---------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|---------------------------|--|--|--|--|--|--|

| Param.<br>No. | Typical <sup>(3)</sup> | Max.                                                                            | Units   |                                                                                                                                                                                                        | Conditions                |       |                           |  |  |  |  |  |  |

| Operating     | Current (ID            | o) <sup>(1,2)</sup>                                                             |         |                                                                                                                                                                                                        |                           |       |                           |  |  |  |  |  |  |

| DC20          | 8.5                    | 13                                                                              | mA      | Code executing from Flash                                                                                                                                                                              | -40°C,<br>+25°C,<br>+85°C | _     | 4 MHz                     |  |  |  |  |  |  |

|               | 9                      | 15                                                                              | +10     |                                                                                                                                                                                                        | +105⁰C                    |       |                           |  |  |  |  |  |  |

| DC20c         | 4.0                    |                                                                                 | mA      | Code executing from SRAM                                                                                                                                                                               | —                         |       |                           |  |  |  |  |  |  |

| DC21          | 23.5                   | 32                                                                              | mA      | Code executing from Flash                                                                                                                                                                              |                           |       | 20 MHz                    |  |  |  |  |  |  |

| DC21c         | 16.4                   | _                                                                               | mA      | Code executing from SRAM                                                                                                                                                                               |                           |       | (Note 4)                  |  |  |  |  |  |  |

| DC22          | 48                     | 61                                                                              | mA      | Code executing from Flash                                                                                                                                                                              |                           |       | 60 MHz                    |  |  |  |  |  |  |

| DC22c         | 45                     | —                                                                               | mA      | Code executing from SRAM                                                                                                                                                                               |                           |       | (Note 4)                  |  |  |  |  |  |  |

| DC23          | 55                     | 75                                                                              | mA      | Code executing from Flash                                                                                                                                                                              | -40°C,<br>+25°C,<br>+85°C | 2.3V  | 80 MHz                    |  |  |  |  |  |  |

|               | 60                     | 100                                                                             |         |                                                                                                                                                                                                        | +105⁰C                    |       |                           |  |  |  |  |  |  |

| DC23c         | 55                     |                                                                                 | mA      | Code executing from SRAM                                                                                                                                                                               |                           | _     |                           |  |  |  |  |  |  |

| DC24          | —                      | 100                                                                             | μA      | —                                                                                                                                                                                                      | -40°C                     |       |                           |  |  |  |  |  |  |

| DC24a         | —                      | 130                                                                             | μA      | —                                                                                                                                                                                                      | +25°C                     | 2.3V  |                           |  |  |  |  |  |  |

| DC24b         | —                      | 670                                                                             | μA      | —                                                                                                                                                                                                      | +85°C                     | 2.3V  |                           |  |  |  |  |  |  |

| DC24c         | —                      | 850                                                                             | μA      | —                                                                                                                                                                                                      | +105°C                    |       |                           |  |  |  |  |  |  |

| DC25          | 94                     | _                                                                               | μA      | —                                                                                                                                                                                                      | -40°C                     |       |                           |  |  |  |  |  |  |

| DC25a         | 125                    | _                                                                               | μA      | —                                                                                                                                                                                                      | +25°C                     | 2 21/ |                           |  |  |  |  |  |  |

| DC25b         | 302                    | _                                                                               | μA      | _                                                                                                                                                                                                      | +85°C                     | 3.3V  | LPRC (31 kHz)<br>(Note 4) |  |  |  |  |  |  |

| DC25d         | 400                    | _                                                                               | μA      | —                                                                                                                                                                                                      | +105⁰C                    | ]     |                           |  |  |  |  |  |  |

| DC25c         | 71                     | _                                                                               | μA      | Code executing from SRAM                                                                                                                                                                               | _                         |       | ]                         |  |  |  |  |  |  |

| DC26          | —                      | 110                                                                             | μA      | —                                                                                                                                                                                                      | -40°C                     |       | ]                         |  |  |  |  |  |  |

| DC26a         | —                      | —         180         μA         —           —         700         μA         — | —       | +25°C                                                                                                                                                                                                  | 3.6V                      |       |                           |  |  |  |  |  |  |

| DC26b         | _                      |                                                                                 | +85°C   | 3.00                                                                                                                                                                                                   |                           |       |                           |  |  |  |  |  |  |

| DC26c         | _                      | 900                                                                             | μA      | —                                                                                                                                                                                                      | +105⁰C                    |       |                           |  |  |  |  |  |  |

#### TABLE 29-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type as well as temperature can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows: Oscillator mode = EC+PLL with OSC1 driven by external square wave from rail to rail and PBCLK divisor = 1:8. CPU, Program Flash and SRAM data memory are operational, Program Flash memory Wait states = 7, program cache and prefetch are disabled and SRAM data memory Wait states = 1. All peripheral modules are disabled (ON bit = 0). WDT and FSCM are disabled. All I/O pins are configured as inputs and pulled to Vss. MCLR = VDD.

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

| DC CHARACTERISTICS |            |                                                            | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                                                   |     |      |   |  |

|--------------------|------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|---|--|

| Param.<br>No.      | Symbol     | Characteristics                                            | Min.                                                                                                                                                                                   | Min. Typical <sup>(1)</sup> Max. Units Conditions |     |      |   |  |

|                    |            | Program Flash Memory                                       |                                                                                                                                                                                        |                                                   |     |      |   |  |

| D130               | Eр         | Cell Endurance                                             | 1000                                                                                                                                                                                   | —                                                 | _   | E/W  | — |  |

| D131               | Vpr        | VDD for Read                                               | Vmin                                                                                                                                                                                   | —                                                 | 3.6 | V    | — |  |

| D132               | VPEW       | VDD for Erase or Write                                     | 3.0                                                                                                                                                                                    | —                                                 | 3.6 | V    | — |  |

| D134               | TRETD      | Characteristic Retention                                   | 20                                                                                                                                                                                     | —                                                 | _   | Year | — |  |

| D135               | IDDP       | Supply Current during<br>Programming                       | —                                                                                                                                                                                      | 10                                                | —   | mA   | — |  |

|                    | Tww        | Word Write Cycle Time                                      | 20                                                                                                                                                                                     | —                                                 | 40  | μs   | — |  |

| D136               | Trw        | Row Write Cycle Time <sup>(2)</sup><br>(128 words per row) | 3                                                                                                                                                                                      | 4.5                                               | —   | ms   | _ |  |

| D137               | TPE        | Page Erase Cycle Time                                      | 20                                                                                                                                                                                     | —                                                 | —   | ms   | — |  |

|                    | TCE        | Chip Erase Cycle Time                                      | 80                                                                                                                                                                                     | —                                                 | —   | ms   | — |  |

| D138               | LVDstartup | Flash LVD Delay                                            | _                                                                                                                                                                                      | —                                                 | 6   | μs   |   |  |

#### TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY<sup>(3)</sup>

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the "*PIC32MX Flash Programming Specification*" (DS61145) for operating conditions during programming and erase cycles.

#### TABLE 29-12: PROGRAM FLASH MEMORY WAIT STATE CHARACTERISTICS

| DC CHARACTERISTICS         | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |       |          |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|--|--|

| Required Flash wait states | SYSCLK                                                                                                                                                                                 | Units | Comments |  |  |

| 0 Wait State               | 0 to 30                                                                                                                                                                                |       |          |  |  |

| 1 Wait State               | 31 to 60                                                                                                                                                                               | MHz   | —        |  |  |

| 2 Wait States              | 61 to 80                                                                                                                                                                               |       |          |  |  |

**Note 1:** 40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.

#### 29.2 AC Characteristics and Timing Parameters

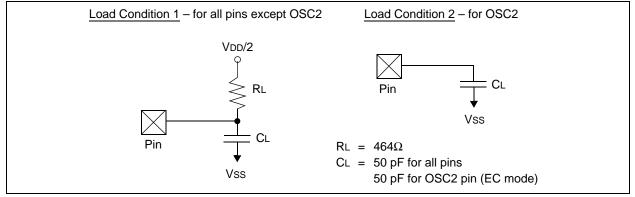

The information contained in this section defines  $\mathsf{PIC32MX3XX/4XX}$  AC characteristics and timing parameters.

#### FIGURE 29-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 29-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |  |  |  |            |  |

|--------------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|------------|--|

| Param.<br>No.      | Symbol | Characteristics       | Min. Typical <sup>(1)</sup> Max. Units Conditions                                                                                                                                        |  |  |  | Conditions |  |

| DO56               | Сю     | All I/O pins and OSC2 | — — 50 pF EC mode                                                                                                                                                                        |  |  |  |            |  |

| DO58               | Св     | SCLx, SDAx            | — — 400 pF In I <sup>2</sup> C™ mode                                                                                                                                                     |  |  |  |            |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### FIGURE 29-2: EXTERNAL CLOCK TIMING

#### TABLE 29-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                                                                  | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                        |                            |            |                                         |  |  |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|------------|-----------------------------------------|--|--|

| Param.<br>No.      | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max.                       | Units      | Conditions                              |  |  |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                  |                        | <sub>50</sub> (3)<br>50(5) | MHz<br>MHz | EC (Note 5)<br>ECPLL (Note 4)           |  |  |

| OS11               |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                        | —                      | 10                         | MHz        | XT (Note 5)                             |  |  |

| OS12               |               |                                                                                                                  | 4                                                                                                                                                                                        | _                      | 10                         | MHz        | XTPLL<br>(Notes 4, 5)                   |  |  |

| OS13               |               |                                                                                                                  | 10                                                                                                                                                                                       | —                      | 25                         | MHz        | HS (Note 5)                             |  |  |

| OS14               |               |                                                                                                                  | 10                                                                                                                                                                                       | _                      | 25                         | MHz        | HSPLL<br>(Notes 4, 5)                   |  |  |

| OS15               |               |                                                                                                                  | 32                                                                                                                                                                                       | 32.768                 | 100                        | kHz        | Sosc (Note 5)                           |  |  |

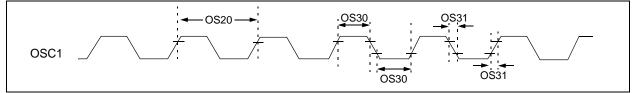

| OS20               | Tosc          | Tosc = 1/Fosc = Tcy <sup>(2)</sup>                                                                               | _                                                                                                                                                                                        |                        | _                          | —          | See parameter<br>OS10 for Fosc<br>value |  |  |

| OS30               | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                              | —                      | _                          | ns         | EC (Note 5)                             |  |  |

| OS31               | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                        | —                      | 0.05 x Tosc                | ns         | EC (Note 5)                             |  |  |

| OS40               | Тоят          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                        | 1024                   | _                          | Tosc       | (Note 5)                                |  |  |

| OS41               | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                        | 2                      |                            | ms         | (Note 5)                                |  |  |

| OS42               | Gм            | External Oscillator<br>Transconductance                                                                          | —                                                                                                                                                                                        | 12                     |                            | mA/V       | VDD = 3.3V<br>TA = +25°C<br>(Note 5)    |  |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- **3:** 40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.

- **4:** PLL input requirements: 4 MHz ≤FPLLIN ≤5 MHz (use PLL prescaler to reduce FOSC). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 5: This parameter is characterized, but not tested in manufacturing.

#### TABLE 29-18:PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.3V TO 3.6V)

| AC CHARACTERISTICS |        |                                                                | Standard (<br>(unless oth<br>Operating | nerwise s | ture -40°C | ≤TA ≤+8 | 5°C for I | ndustrial<br>· V-Temp                |

|--------------------|--------|----------------------------------------------------------------|----------------------------------------|-----------|------------|---------|-----------|--------------------------------------|

| Param.<br>No.      | Symbol | Characteristi                                                  | ics <sup>(1)</sup>                     | Min.      | Typical    | Max.    | Units     | Conditions                           |

| OS50               | Fplli  | PLL Voltage Control<br>Oscillator (VCO) Inp<br>Frequency Range |                                        | 4         | _          | 5       | MHz       | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51               | Fsys   | On-Chip VCO Syste<br>Frequency                                 | m                                      | 60        | _          | 120     | MHz       | —                                    |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                  |                                        | —         | _          | 2       | ms        | —                                    |

| OS53               | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative) |                                        | -0.25     | _          | +0.25   | %         | Measured over 100 ms period          |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 80 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{80}{20}}} = \frac{D_{CLK}}{2}$$

#### TABLE 29-19: INTERNAL FRC ACCURACY

| AC CHA        | RACTERISTICS                                    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +105^{\circ}C$ for V-Temp |  |  |  |  |  |  |  |

|---------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Param.<br>No. | Characteristics                                 | Min. Typical Max. Units Conditions                                                                                                                                                                     |  |  |  |  |  |  |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| F20           | FRC                                             | -2 - +2 % -                                                                                                                                                                                            |  |  |  |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

#### TABLE 29-20: INTERNAL RC ACCURACY

| AC CHA        | RACTERISTICS                    | (unless                                | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |  |  |  |  |  |  |  |

|---------------|---------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Param.<br>No. | Characteristics                 | ics Min. Typical Max. Units Conditions |                                                                                                                                                                                        |  |  |  |  |  |  |  |

| LPRC @        | LPRC @ 31.25 kHz <sup>(1)</sup> |                                        |                                                                                                                                                                                        |  |  |  |  |  |  |  |

| F21           | LPRC                            | -15 — +15 % —                          |                                                                                                                                                                                        |  |  |  |  |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

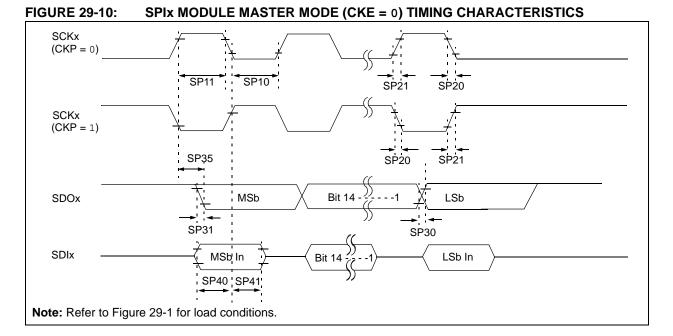

#### TABLE 29-28: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+85°C for Industrial-40°C ≤TA ≤+105°C for V-Temp |                        |      |       |                    |  |

|--------------------|-----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>             | Min.                                                                                                                                                 | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>        | Tsck/2                                                                                                                                               | _                      |      | ns    | _                  |  |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>       | Tsck/2                                                                                                                                               | —                      |      | ns    | —                  |  |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>       | _                                                                                                                                                    | —                      | _    | ns    | See parameter DO32 |  |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>       | _                                                                                                                                                    | _                      | _    | ns    | See parameter DO31 |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>  | _                                                                                                                                                    | —                      | _    | ns    | See parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>  | _                                                                                                                                                    | —                      | _    | ns    | See parameter DO31 |  |

| SP35               | TscH2doV,             | SDOx Data Output Valid after               | _                                                                                                                                                    | —                      | 15   | ns    | VDD > 2.7V         |  |

|                    | TscL2doV              | SCKx Edge                                  | _                                                                                                                                                    | —                      | 20   | ns    | Vdd < 2.7V         |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 10                                                                                                                                                   | _                      |      | ns    | _                  |  |

| SP41               | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10                                                                                                                                                   | —                      |      | ns    | —                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

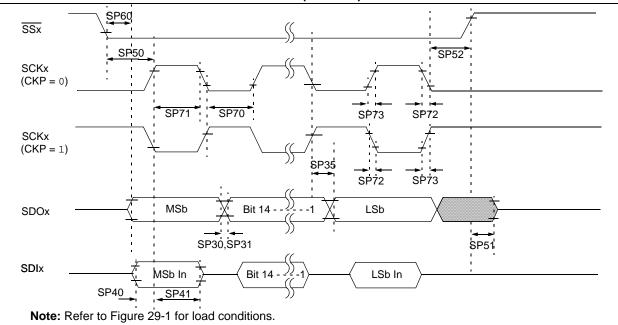

#### TABLE 29-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS    |                                            |              | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |      |       |                    |  |  |

|---------------|-----------------------|--------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.         | Typical <sup>(2)</sup>                                                                                                                                                                   | Max. | Units | Conditions         |  |  |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>         | Тѕск/2       | _                                                                                                                                                                                        |      | ns    | _                  |  |  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>        | Tsck/2       | _                                                                                                                                                                                        |      | ns    | —                  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                       | _            | 5                                                                                                                                                                                        | 10   | ns    | —                  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                       | _            | 5                                                                                                                                                                                        | 10   | ns    | —                  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>  | _            | —                                                                                                                                                                                        |      | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>  | _            | —                                                                                                                                                                                        |      | ns    | See parameter DO31 |  |  |