Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx360f512lt-80v-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

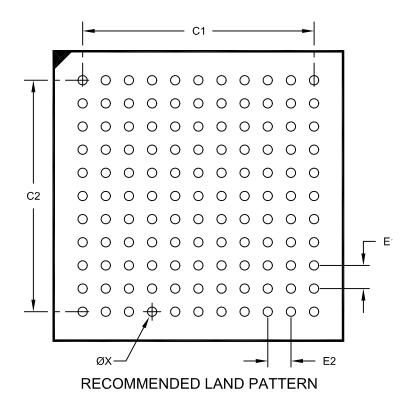

## TABLE 3:PIN NAMES: PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F128L, AND<br/>PIC32MX360F512L DEVICES (CONTINUED)

| Pin<br>Number            | Full Pin Name        |  |  |  |  |  |  |

|--------------------------|----------------------|--|--|--|--|--|--|

| K4                       | AN8/C1OUT/RB8        |  |  |  |  |  |  |

| K5                       | No Connect (NC)      |  |  |  |  |  |  |

| K6                       | U2CTS/RF12           |  |  |  |  |  |  |

| K7                       | AN14/PMALH/PMA1/RB14 |  |  |  |  |  |  |

| K8                       | VDD                  |  |  |  |  |  |  |

| K9                       | U1RTS/CN21/RD15      |  |  |  |  |  |  |

| K10                      | U1TX/RF3             |  |  |  |  |  |  |

| K11                      | U1RX/RF2             |  |  |  |  |  |  |

| L1                       | PGEC2/AN6/OCFA/RB6   |  |  |  |  |  |  |

| L2 VREF-/CVREF-/PMA7/RA9 |                      |  |  |  |  |  |  |

| Pin<br>Number | Full Pin Name                  |

|---------------|--------------------------------|

| L3            | AVss                           |

| L4            | AN9/C2OUT/RB9                  |

| L5            | AN10/CVREFOUT/PMA13/RB10       |

| L6            | U2RTS/RF13                     |

| L7            | AN13/PMA10/RB13                |

| L8            | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| L9            | CN20/U1CTS/RD14                |

| L10           | U2RX/PMA9/CN17/RF4             |

| L11           | U2TX/PMA8/CN18/RF5             |

|          | Pin                                       | Number <sup>(</sup> | 1)              | Din Duff    |                |                                                         |  |  |  |  |  |

|----------|-------------------------------------------|---------------------|-----------------|-------------|----------------|---------------------------------------------------------|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/TQFP                        | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type | Buffer<br>Type | Description                                             |  |  |  |  |  |

| CN0      | 48                                        | 74                  | B11             | I           | ST             | Change notification inputs.                             |  |  |  |  |  |

| CN1      | 47                                        | 73                  | C10             | -           | ST             | Can be software programmed for internal weak            |  |  |  |  |  |

| CN2      | 16                                        | 25                  | K2              | I           | ST             | pull-ups on all inputs.                                 |  |  |  |  |  |

| CN3      | 15                                        | 24                  | K1              | I           | ST             |                                                         |  |  |  |  |  |

| CN4      | 14                                        | 23                  | J2              | I           | ST             |                                                         |  |  |  |  |  |

| CN5      | 13                                        | 22                  | J1              | I           | ST             |                                                         |  |  |  |  |  |

| CN6      | 12                                        | 21                  | H2              | I           | ST             |                                                         |  |  |  |  |  |

| CN7      | 11                                        | 20                  | H1              | I           | ST             |                                                         |  |  |  |  |  |

| CN8      | 4                                         | 10                  | E3              | I           | ST             |                                                         |  |  |  |  |  |

| CN9      | 5                                         | 11                  | F4              | I           | ST             |                                                         |  |  |  |  |  |

| CN10     | 6                                         | 12                  | F2              | I           | ST             |                                                         |  |  |  |  |  |

| CN11     | 8                                         | 14                  | F3              | I           | ST             |                                                         |  |  |  |  |  |

| CN12     | 30                                        | 44                  | L8              | Ι           | ST             |                                                         |  |  |  |  |  |

| CN13     | 52                                        | 81                  | C8              | -           | ST             |                                                         |  |  |  |  |  |

| CN14     | 53                                        | 82                  | B8              | Ι           | ST             |                                                         |  |  |  |  |  |

| CN15     | 54                                        | 83                  | D7              | Ι           | ST             |                                                         |  |  |  |  |  |

| CN16     | 55                                        | 84                  | C7              | Ι           | ST             |                                                         |  |  |  |  |  |

| CN17     | 31                                        | 49                  | L10             | -           | ST             |                                                         |  |  |  |  |  |

| CN18     | 32                                        | 50                  | L11             | -           | ST             |                                                         |  |  |  |  |  |

| CN19     | _                                         | 80                  | D8              | -           | ST             |                                                         |  |  |  |  |  |

| CN20     | _                                         | 47                  | L9              | -           | ST             |                                                         |  |  |  |  |  |

| CN21     | _                                         | 48                  | K9              | -           | ST             |                                                         |  |  |  |  |  |

| IC1      | 42                                        | 68                  | E9              | I           | ST             | Capture inputs 1-5.                                     |  |  |  |  |  |

| IC2      | 43                                        | 69                  | E10             | I           | ST             |                                                         |  |  |  |  |  |

| IC3      | 44                                        | 70                  | D11             | I           | ST             |                                                         |  |  |  |  |  |

| IC4      | 45                                        | 71                  | C11             | -           | ST             |                                                         |  |  |  |  |  |

| IC5      | 52                                        | 79                  | A9              | -           | ST             |                                                         |  |  |  |  |  |

| OCFA     | 17                                        | 26                  | L1              | -           | ST             | Output Compare Fault A Input.                           |  |  |  |  |  |

| OC1      | 46                                        | 72                  | D9              | 0           |                | Output Compare output 1.                                |  |  |  |  |  |

| OC2      | 49                                        | 76                  | A11             | 0           | —              | Output Compare output 2                                 |  |  |  |  |  |

| OC3      | 50                                        | 77                  | A10             | 0           |                | Output Compare output 3.                                |  |  |  |  |  |

| OC4      | 51                                        | 78                  | B9              | 0           | —              | Output Compare output 4.                                |  |  |  |  |  |

| OC5      | 52                                        | 81                  | C8              | 0           |                | Output Compare output 5.                                |  |  |  |  |  |

| OCFB     | 30                                        | 44                  | L8              |             | ST             | Output Compare Fault B Input.                           |  |  |  |  |  |

| INT0     | 35,46                                     | 55,72               | H9,D9           |             | ST             | External interrupt 0.                                   |  |  |  |  |  |

| INT1     | 42                                        | 18                  | 61              | -           | ST             | External interrupt 1.                                   |  |  |  |  |  |

| INT2     | 43                                        | 19                  | 62              | I           | ST             | External interrupt 2.                                   |  |  |  |  |  |

| -        | CMOS = CM<br>ST = Schmitt<br>TTL = TTL in | Trigger in          |                 |             |                | Analog = Analog input P = Power<br>D = Output I = Input |  |  |  |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------|

|            |                                     |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

### TABLE 4-17: COMPARATOR REGISTERS MAP<sup>(1)</sup>

| ss         and an and a second se | 7/11 26/10 | 25/9 | 24/8 | 23/7 | 22/6    | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|------|---------|------|------|------|------|-------|-------|------------|

| A000 CM1CON 15:0 ON COE CPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br>       | _    | —    | _    |         |      |      |      |      |       |       |            |

| 15:0 ON COE CPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |      |      |      | _       | —    | —    | —    | —    | -     | _     | 0000       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <br>       | -    | COUT | EVPO | )L<1:0> | —    | CREF | —    | —    | CCH   | <1:0> | 00C3       |

| A010 CM2CON 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br>       | -    | —    | _    | —       | _    | —    | _    | _    | —     | _     | 0000       |

| 15:0 ON COE CPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>       | -    | COUT | EVPO | )L<1:0> | —    | CREF | _    | —    | CCH   | <1:0> | 00C3       |

| A060 CMSTAT 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br>       | -    | —    | _    | —       | —    | _    | _    | _    | _     | _     | 0000       |

| A000 CMISTAT 15:0 SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br>       | _    | _    | _    | _       | _    | —    | _    | _    | C2OUT | C10UT | 0000       |

as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 4-18: COMPARATOR VOLTAGE REFERENCE REGISTERS MAP<sup>(1)</sup>

| ess                       |                  | ø         |       | Bits  |       |       |       |       |      |      |      |       |      |       |      |      |       |      |            |

|---------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|-------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 9800                      | CVRCON           | 31:16     | —     | —     | —     | —     |       | —     |      | —    | —    | —     | -    | —     | -    | —    | —     | _    | 0000       |

| 9000                      | CVRCON           | 15:0      | ON    | —     | —     | —     | _     | —     | —    | —    | —    | CVROE | CVRR | CVRSS |      | CVR  | <3:0> |      | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

## TABLE 4-33: PORTG REGISTERS MAP FOR PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F256L, PIC32MX360F512L, PIC32MX440F128L, PIC32MX460F256L AND PIC32MX460F512L DEVICES ONLY<sup>(1)</sup>

| ess                         |                  |           |         |         |         |         |       |       |        | Bi     | its    |        |      |      |        |        |        |        |            |

|-----------------------------|------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG            | 31:16     | _       | _       |         | —       |       |       |        |        |        | —      | —    |      | —      | —      | —      | —      | 0000       |

| 0100                        | 11100            | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 |       |       | TRISG9 | TRISG8 | TRISG7 | TRISG6 | -    | -    | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF       |

| 6190                        | PORTG            | 31:16     | -       | _       | -       | -       | -     | _     | _      | -      | -      | -      | -    | -    | -      | -      | -      | _      | 0000       |

| 0190                        | FURIG            | 15:0      | RG15    | RG14    | RG13    | RG12    | —     | —     | RG9    | RG8    | RG7    | RG6    | —    | —    | RG3    | RG2    | RG1    | RG0    | xxxx       |

| 61A0                        | LATG             | 31:16     |         | _       | _       | —       | —     | —     | —      | —      | —      | —      | —    | —    | _      | —      | —      | —      | 0000       |

| 6TAU                        | LAIG             | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | —    | —    | LATG3  | LATG2  | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG             | 31:16     | _       | —       | —       | —       | _     |       | _      | —      | _      | —      | —    | _    | —      | —      | —      | —      | 0000       |

| UIDU                        | ODCG             | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | _     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | —    | _    | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 4-34: PORTG REGISTERS MAP FOR PIC32MX320F032H, PIC32MX320F064H, PIC32MX320F128H, PIC32MX340F128H, PIC32MX340F256H, PIC32MX340F512H, PIC32MX420F032H, PIC32MX440F128H, PIC32MX440F256H AND PIC32MX440F512H DEVICES ONLY<sup>(1)</sup>

| ess                         |                  |           |       |       |       |       |       |       |        | Bi     | its    |        |      |      |        |        |      |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Resets |

| 6180                        | TRISG            | 31:16     | -     | _     |       | _     |       | —     |        |        |        | —      |      |      | —      | —      |      | —    | 0000       |

| 0100                        | IRISG            | 15:0      | —     | —     | —     | —     | —     | —     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | _    | —    | 03cc       |

| 6190                        | PORTG            | 31:16     |       | -     | _     | _     | —     | —     | _      | _      | —      | —      | _    | _    | —      | —      | —    | _    | 0000       |

| 0190                        | FORIG            | 15:0      | -     | -     | -     | _     | -     | -     | RG9    | RG8    | RG7    | RG6    | _    | -    | RG3    | RG2    | -    | -    | xxxx       |

| 61A0                        | LATG             | 31:16     | -     | _     |       | _     |       | _     |        | _      | -      | _      | _    | -    | —      | _      |      | _    | 0000       |

| 0170                        | LAIG             | 15:0      | -     |       |       | -     | -     | -     | LATG9  | LATG8  | LATG7  | LATG6  |      | -    | LATG3  | LATG2  |      | —    | xxxx       |

| 61B0                        | ODCG             | 31:16     | -     | _     |       | _     |       | —     |        | _      |        | —      | _    |      | —      | —      |      | _    | 0000       |

| 0100                        | 0000             | 15:0      | _     | _     |       | —     |       | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _    | -    | ODCG3  | ODCG2  |      | _    | 0000       |

Legend: x = unknown value on Reset, --- unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## TABLE 4-43: USB REGISTERS MAP<sup>(1)</sup>

| 0        |

|----------|

| S        |

| ဂ္       |

|          |

| <u> </u> |

| 4        |

| ω        |

| T        |

| <b>—</b> |

| ÷        |

| ×        |

| <u>س</u> |

| g        |

| ē        |

| τυ.      |

| ~        |

| ω        |

| N        |

|          |

| ess                         |                              |           |                                                                                              |       |       |       |       |       |      |      | Bits                   |                    |                       |             |         |          |          |          |            |

|-----------------------------|------------------------------|-----------|----------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|------|------|------------------------|--------------------|-----------------------|-------------|---------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name             | Bit Range | 31/15                                                                                        | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6               | 21/5                  | 20/4        | 19/3    | 18/2     | 17/1     | 16/0     | All Resets |

| 5040                        | U10TG                        | 31:16     | _                                                                                            |       |       |       |       | _     |      | _    | —                      | —                  | _                     | _           | _       | —        | —        | _        |            |

| 3040                        | IR <sup>(2)</sup>            | 15:0      | _                                                                                            |       |       |       |       | —     |      | —    | IDIF                   | T1MSECIF           | LSTATEIF              | ACTVIF      | SESVDIF | SESENDIF | _        | VBUSVDIF | 0000       |

| 5050                        | U1OTG                        | 31:16     | _                                                                                            | _     | _     | _     | -     | —     | _    | —    | —                      | —                  | —                     | —           | —       | —        | -        | —        | 0000       |

|                             | IE                           | 15:0      | _                                                                                            |       |       |       |       | —     |      | —    | IDIE                   | T1MSECIE           | LSTATEIE              | ACTVIE      | SESVDIE | SESENDIE | -        | VBUSVDIE |            |

| 5060                        | U1OTG<br>STAT <sup>(3)</sup> | 31:16     | —                                                                                            | _     |       | _     | _     | —     |      | —    | -                      | —                  | —                     | —           | —       | —        | —        | —        | 0000       |

|                             | STAT                         | 15:0      | _                                                                                            | _     | _     | _     |       | —     | _    | —    | ID                     | —                  | LSTATE                | —           | SESVD   | SESEND   | _        | VBUSVD   | 0000       |

| 5070                        | U1OTG<br>CON                 | 31:16     | _                                                                                            | _     | —     | _     | —     | —     | —    | —    | —                      | —                  | —                     | —           | —       | —        | —        | —        | 0000       |

|                             | CON                          | 15:0      | -                                                                                            | —     | _     | —     | -     | —     | _    | —    | DPPULUP                | DMPULUP            | DPPULDWN              | DMPULDWN    |         | OTGEN    | VBUSCHG  | VBUSDIS  | 0000       |

| 5080                        | U1PWRC                       | 31:16     | _                                                                                            | _     | _     | _     | _     |       | _    | —    | —                      | _                  | —                     | —           | _       | -        | —        | —        | 0000       |

|                             |                              | 15:0      | _                                                                                            |       |       |       |       |       |      | _    | UACTPND <sup>(4)</sup> | _                  | _                     | USLPGRD     |         |          | USUSPEND | USBPWR   | 0000       |

|                             | U1IR <sup>(2)</sup>          | 31:16     | _                                                                                            | _     | _     | _     | _     | _     | _    | —    | -                      | —                  | _                     | _           | _       | -        | -        | -        | 0000       |

| 5200                        | U11R**/                      | 15:0      | _                                                                                            | —     | _     | —     | _     | _     | _    | _    | STALLIF                | ATTACHIF           | RESUMEIF              | IDLEIF      | TRNIF   | SOFIF    | UERRIF   | URSTIF   | 0000       |

|                             |                              | 31:16     |                                                                                              |       |       |       |       |       |      |      |                        |                    |                       | _           |         |          | _        | DETACHIF |            |

| 5210                        | U1IE                         | 31:16     | _                                                                                            | _     | _     | _     |       |       | _    | —    |                        | _                  | _                     | _           | —       | —        | _        |          | 0000       |

| 5210                        | OTIE                         | 15:0      | _                                                                                            | —     | —     | —     | —     | —     | —    | _    | STALLIE                | ATTACHIE           | RESUMEIE              | IDLEIE      | TRNIE   | SOFIE    | UERRIE   | DETACHIE |            |

|                             |                              | 31:16     | _                                                                                            |       |       |       | _     | _     | _    |      | _                      |                    | _                     | _           | _       | _        | _        | —        | 0000       |

| 5220                        | U1EIR                        | 51.10     |                                                                                              |       |       |       |       |       |      |      |                        |                    |                       |             |         |          | CRC5EF   |          | 0000       |

| 5220                        | OTEIR                        | 15:0      | —                                                                                            | —     | —     | —     | —     | —     | —    | —    | BTSEF                  | BMXEF              | DMAEF                 | BTOEF       | DFN8EF  | CRC16EF  | EOFEF    | PIDEF    | 0000       |

|                             |                              | 31:16     | _                                                                                            | _     |       | _     |       | _     |      | _    | -                      | _                  | _                     | _           | _       | _        | _        | _        | 0000       |

| 5230                        | U1EIE                        | 00        |                                                                                              |       |       |       |       |       |      |      |                        |                    |                       |             |         |          | CRC5EE   |          | 0000       |

|                             |                              | 15:0      | -                                                                                            | —     | -     | —     | _     | —     | -    | —    | BTSEE                  | BMXEE              | DMAEE                 | BTOEE       | DFN8EE  | CRC16EE  | EOFEE    | PIDEE    | 0000       |

|                             | (0)                          | 31:16     | _                                                                                            | _     | _     | _     | _     | _     | _    | _    | _                      |                    | _                     | _           | _       | _        | _        |          | 0000       |

| 5240                        | U1STAT <sup>(3)</sup>        | 15:0      | _                                                                                            | _     | _     | _     | _     | _     | _    | _    |                        | ENDP               | T<3:0> <sup>(4)</sup> |             | DIR     | PPBI     | _        | _        | 0000       |

|                             |                              | 31:16     | _                                                                                            | _     | _     | _     | _     | _     | _    | _    | _                      | _                  | _                     | —           | _       | _        | _        | _        | 0000       |

| 5250                        | U1CON                        |           |                                                                                              |       |       |       |       |       |      |      | (4)                    | a==(/)             | PKTDIS                |             |         |          |          | USBEN    | 0000       |

|                             |                              | 15:0      | -                                                                                            | —     | -     | —     | _     | -     | -    | -    | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | TOKBUSY               | USBRST      | HOSTEN  | RESUME   | PPBRST   | SOFEN    | 0000       |

| 5000                        |                              | 31:16     | _                                                                                            |       | _     |       | _     | _     | _    | _    | _                      |                    | —                     |             | —       | —        | _        |          | 0000       |

| 5260                        | U1ADDR                       | 15:0      | _                                                                                            | —     | —     | —     | _     | —     | —    | _    | LSPDEN DEVADDR<6:0>    |                    |                       |             |         |          | 0000     |          |            |

| 5070                        |                              | 31:16     | _                                                                                            | —     | _     | —     | _     | —     | —    | —    | -                      | —                  | _                     | _           | _       | —        | —        | _        | 0000       |

| 5270                        | U1BDTP1                      | 15:0      | _                                                                                            | _     | _     | _     | -     | _     | _    | _    |                        |                    | В                     | DTPTRL<7:1> |         |          |          | _        | 0000       |

| egen                        | <b>d:</b> x = u              | unknowi   | known value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |       |       |       |       |      |      |                        |                    |                       |             |         |          |          |          |            |

Legend: Note 1:

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated CLR, SET, and INV registers. 2:

All bits in this register are read-only; therefore, CLR, SET, and INV registers are not supported. 3:

4: The reset value for this bit is undefined.

### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS61121) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

PIC32MX3XX/4XX devices contain an internal program Flash memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self Programming (RTSP)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- EJTAG Programming

#### EXAMPLE 5-1:

NVMCON = 0x4004;

// Enable and configure for erase operation

Wait(delay);

// Delay for 6 µs for LVDstartup

NVMKEY = 0xAA996655;

NVMKEY = 0x556699AA;

NVMCONSET = 0x8000;

// Initiate operation

while(NVMCONbits.WR==1);

// Wait for current operation to complete

RTSP is performed by software executing from either Flash or RAM memory. EJTAG is performed using the EJTAG port of the device and a EJTAG capable programmer. ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP. RTSP techniques are described in this chapter. The ICSP and EJTAG methods are described in the "*PIC32MX Flash Programming Specification*" (DS61145), which can be downloaded from the Microchip web site.

**Note:** Flash LVD Delay (LVDstartup) must be taken into account between setting up and executing any Flash command operation. See Example 5-1 for a code example to set up and execute a Flash command operation.

## PIC32MX3XX/4XX

NOTES:

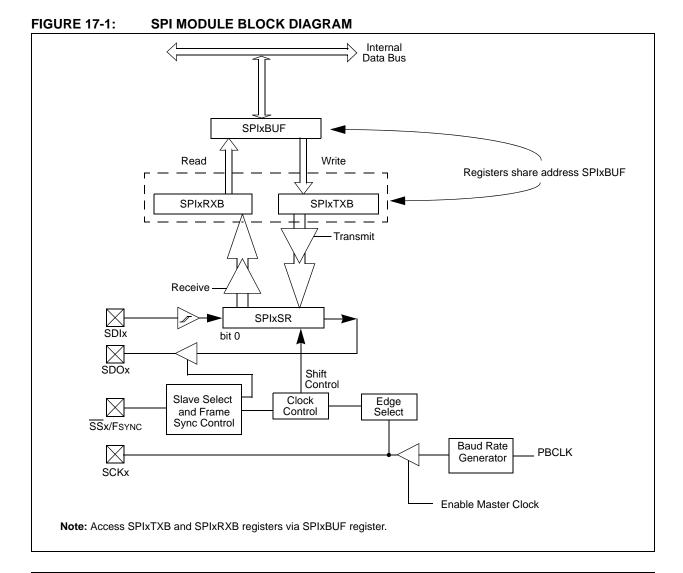

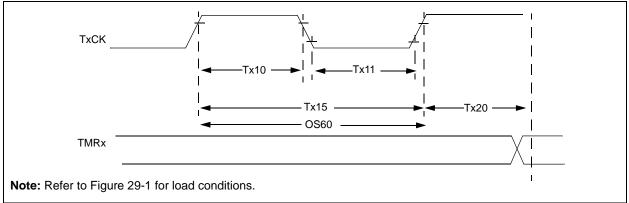

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32MX SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Following are some of the key features of this module:

- Master and Slave Modes Support

- Four Different Clock Formats

- Framed SPI Protocol Support

- User Configurable 8-bit, 16-bit and 32-bit Data

Width

- Separate SPI Data Registers for Receive and Transmit

- Programmable Interrupt Event on every 8-bit, 16-bit and 32-bit Data Transfer

- Operation during CPU Sleep and Idle Mode

- Fast Bit Manipulation using CLR, SET and INV Registers

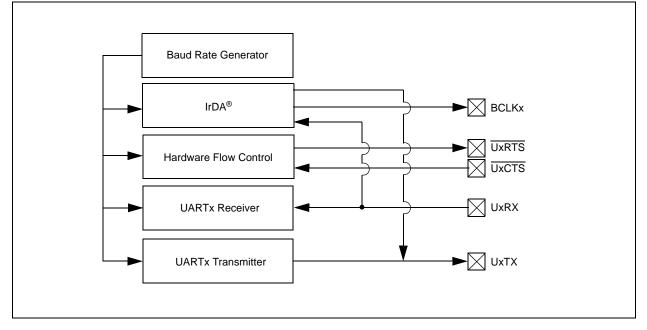

### 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS61107) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The UART module is one of the serial I/O modules available in PIC32MX3XX/4XX family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols such as RS-232, RS-485, LIN 1.2 and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 20 Mbps at 80 MHz

- 4-level-deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-level-deep FIFO Receive Data Buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

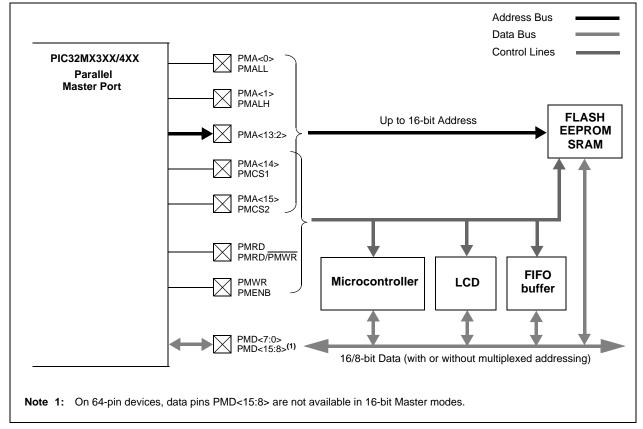

## 20.0 PARALLEL MASTER PORT (PMP)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS61128) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Key features of the PMP module include:

- 8-bit,16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- · Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- Freeze option for in-circuit debugging

Note: On 64-pin devices, data pins PMD<15:8> are not available.

#### FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

## PIC32MX3XX/4XX

NOTES:

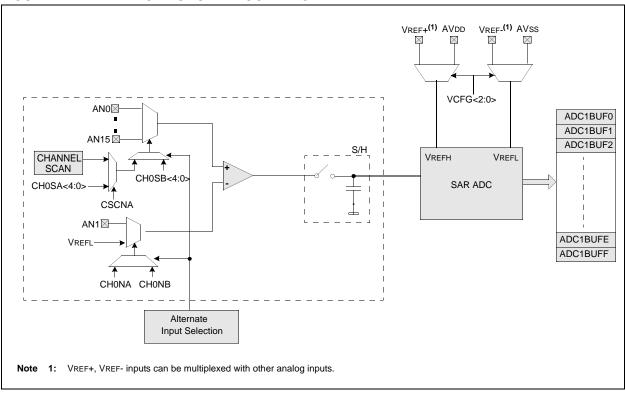

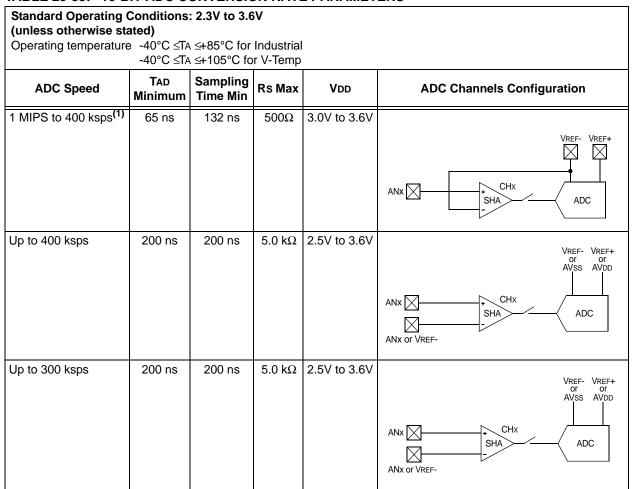

### 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. Refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS61104) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC32MX3XX/4XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1000 kilo samples per second (ksps) conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample-and-Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- Selectable Buffer Fill modes

- Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers (MUXs) to one SHA. The analog input MUXs can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 22-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight, 32-bit output formats when it is read from the result buffer.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

#### **DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)** REGISTER 26-1:

bit 19-12 PWP<7:0>: Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. 11111111 = Disabled 11111110 = 0xBD00 0FFF 11111101 = 0xBD00\_1FFF 11111100 = 0xBD00\_2FFF 11111011 = 0xBD00\_3FFF 11111010 = 0xBD00\_4FFF 11111001 = 0xBD00 5FFF 11111000 = 0xBD00\_6FFF 11110111 = 0xBD00\_7FFF 11110110 = 0xBD00\_8FFF 11110101 = 0xBD00\_9FFF 11110100 = 0xBD00\_AFFF 11110011 = 0xBD00 BFFF 11110010 = 0xBD00\_CFFF 11110001 = 0xBD00\_DFFF 11110000 = 0xBD00\_EFFF 11101111 = 0xBD00\_FFFF 01111111 = 0xBD07\_FFFF bit 11-4 Reserved: Write '1' ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit 1 = PGEC2/PGED2 pair is used 0 = PGEC1/PGED1 pair is used Reserved: Write '1' DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled) bit 1-0

11 = Debugger disabled

bit 3

bit 2

- 10 =Debugger enabled

- 01 = Reserved (same as '11' setting) 00 = Reserved (same as '11' setting)

#### REGISTER 26-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output signal active on the OSCO pin; primary oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 OR 00)

- 0 = CLKO output disabled

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary oscillator disabled

- 10 = HS oscillator mode selected

- 01 = XT oscillator mode selected

- 00 = External clock mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode enabled (Two-Speed Start-up enabled)

- 0 = Internal External Switchover mode disabled (Two-Speed Start-up disabled)

- bit 6 Reserved: Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable Posc (POSCMOD = 00) when using this oscillator source.

| TABLE 27-1: | MIPS32 <sup>®</sup> INSTRUCTION SET (CONTINUED)                       |                                                                     |  |  |  |  |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Instruction | Description                                                           | Function                                                            |  |  |  |  |  |  |  |  |  |  |

| JAL         | Jump and Link                                                         | GPR[31] = PC + 8<br>PC = PC[31:28]    offset<<2                     |  |  |  |  |  |  |  |  |  |  |

| JALR        | Jump and Link Register                                                | Rd = PC + 8<br>PC = Rs                                              |  |  |  |  |  |  |  |  |  |  |

| JALR.HB     | Jump and Link Register with Hazard Barrier                            | Like JALR, but also clears execution and instruction hazards        |  |  |  |  |  |  |  |  |  |  |

| JR          | Jump Register                                                         | PC = Rs                                                             |  |  |  |  |  |  |  |  |  |  |

| JR.HB       | Jump Register with Hazard Barrier                                     | Like JR, but also clears execution and instruction hazards          |  |  |  |  |  |  |  |  |  |  |

| LB          | Load Byte                                                             | Rt = (byte)Mem[Rs+offset]                                           |  |  |  |  |  |  |  |  |  |  |

| LBU         | Unsigned Load Byte                                                    | Rt = (ubyte))Mem[Rs+offset]                                         |  |  |  |  |  |  |  |  |  |  |

| LH          | Load Halfword                                                         | Rt = (half)Mem[Rs+offset]                                           |  |  |  |  |  |  |  |  |  |  |

| LHU         | Unsigned Load Halfword                                                | Rt = (uhalf)Mem[Rs+offset]                                          |  |  |  |  |  |  |  |  |  |  |

| LL          | Load Linked Word                                                      | Rt = Mem[Rs+offset><br>LL <sub>bit</sub> = 1<br>LLAdr = Rs + offset |  |  |  |  |  |  |  |  |  |  |

| LUI         | Load Upper Immediate                                                  | Rt = immediate << 16                                                |  |  |  |  |  |  |  |  |  |  |

| LW          | Load Word                                                             | Rt = Mem[Rs+offset]                                                 |  |  |  |  |  |  |  |  |  |  |

| LWPC        | Load Word, PC relative                                                | Rt = Mem[PC+offset]                                                 |  |  |  |  |  |  |  |  |  |  |

| LWL         | Load Word Left                                                        | Re = Re MERGE Mem[Rs+offset]                                        |  |  |  |  |  |  |  |  |  |  |

| LWR         | Load Word Right                                                       | Re = Re MERGE Mem[Rs+offset]                                        |  |  |  |  |  |  |  |  |  |  |

| MADD        | Multiply-Add                                                          | HI   LO += (int)Rs * (int)Rt                                        |  |  |  |  |  |  |  |  |  |  |

| MADDU       | Multiply-Add Unsigned                                                 | HI   LO += (uns)Rs * (uns)Rt                                        |  |  |  |  |  |  |  |  |  |  |

| MFC0        | Move from Coprocessor 0                                               | Rt = CPR[0, Rd, sel]                                                |  |  |  |  |  |  |  |  |  |  |

| MFHI        | Move from HI                                                          | Rd = HI                                                             |  |  |  |  |  |  |  |  |  |  |

| MFLO        | Move from LO                                                          | Rd = LO                                                             |  |  |  |  |  |  |  |  |  |  |

| MOVN        | Move Conditional on Not Zero                                          | if Rt $\frac{1}{4}$ 0 then<br>Rd = Rs                               |  |  |  |  |  |  |  |  |  |  |

| MOVZ        | Move Conditional on Zero                                              | if Rt = 0 then<br>Rd = Rs                                           |  |  |  |  |  |  |  |  |  |  |

| MSUB        | Multiply-Subtract                                                     | HI   LO -= (int)Rs * (int)Rt                                        |  |  |  |  |  |  |  |  |  |  |

| MSUBU       | Multiply-Subtract Unsigned                                            | HI   LO -= (uns)Rs * (uns)Rt                                        |  |  |  |  |  |  |  |  |  |  |

| MTC0        | Move to Coprocessor 0                                                 | CPR[0, n, Sel] = Rt                                                 |  |  |  |  |  |  |  |  |  |  |

| MTHI        | Move to HI                                                            | HI = Rs                                                             |  |  |  |  |  |  |  |  |  |  |

| MTLO        | Move to LO                                                            | LO = Rs                                                             |  |  |  |  |  |  |  |  |  |  |

| MUL         | Multiply with register write                                          | HI   LO =Unpredictable<br>Rd = ((int)Rs * (int)Rt) <sub>310</sub>   |  |  |  |  |  |  |  |  |  |  |

| MULT        | Integer Multiply                                                      | HI   LO = (int)Rs * (int)Rd                                         |  |  |  |  |  |  |  |  |  |  |

| MULTU       | Unsigned Multiply                                                     | HI   LO = (uns)Rs * (uns)Rd                                         |  |  |  |  |  |  |  |  |  |  |

| NOP         | No Operation<br>(Assembler idiom for: SLL r0, r0, r0)                 |                                                                     |  |  |  |  |  |  |  |  |  |  |

| NOR         | Logical NOR                                                           | $Rd = \sim (Rs   Rt)$                                               |  |  |  |  |  |  |  |  |  |  |

| OR          | Logical OR                                                            | Rd = Rs   Rt                                                        |  |  |  |  |  |  |  |  |  |  |

| ORI         | Logical OR Immediate                                                  | Rt = Rs   Immed                                                     |  |  |  |  |  |  |  |  |  |  |

| RDHWR       | Read Hardware Register (if enabled by HWRE <sub>na</sub><br>Register) | Re = HWR[Rd]                                                        |  |  |  |  |  |  |  |  |  |  |

TABLE 27-1: MIPS32<sup>®</sup> INSTRUCTION SET (CONTINUED)

Note 1: This instruction is deprecated and should not be used.

| DC CHARACTERISTICS |            |                                                            | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)       -40°C ≤TA ≤+85°C for Industrial         Operating temperature       -40°C ≤TA ≤+105°C for V-Temp |                                                |     |            |   |  |

|--------------------|------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|------------|---|--|

| Param.<br>No.      | Symbol     | Characteristics                                            | Min.                                                                                                                                                                                 | Min. Typical <sup>(1)</sup> Max. Units Conditi |     | Conditions |   |  |

|                    |            | Program Flash Memory                                       |                                                                                                                                                                                      |                                                |     |            |   |  |

| D130               | Eр         | Cell Endurance                                             | 1000                                                                                                                                                                                 | —                                              | _   | E/W        | — |  |

| D131               | Vpr        | VDD for Read                                               | Vmin                                                                                                                                                                                 | —                                              | 3.6 | V          | — |  |

| D132               | VPEW       | VDD for Erase or Write                                     | 3.0                                                                                                                                                                                  | —                                              | 3.6 | V          | — |  |

| D134               | TRETD      | Characteristic Retention                                   | 20                                                                                                                                                                                   | —                                              | —   | Year       | — |  |

| D135               | IDDP       | Supply Current during<br>Programming                       | —                                                                                                                                                                                    | 10                                             | —   | mA         | — |  |

|                    | Tww        | Word Write Cycle Time                                      | 20                                                                                                                                                                                   | —                                              | 40  | μs         | — |  |

| D136               | Trw        | Row Write Cycle Time <sup>(2)</sup><br>(128 words per row) | 3                                                                                                                                                                                    | 4.5                                            | —   | ms         | _ |  |

| D137               | TPE        | Page Erase Cycle Time                                      | 20                                                                                                                                                                                   | —                                              | —   | ms         | — |  |

|                    | TCE        | Chip Erase Cycle Time                                      | 80                                                                                                                                                                                   | —                                              | —   | ms         | — |  |

| D138               | LVDstartup | Flash LVD Delay                                            | _                                                                                                                                                                                    | —                                              | 6   | μs         |   |  |

#### TABLE 29-11: DC CHARACTERISTICS: PROGRAM MEMORY<sup>(3)</sup>

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the "*PIC32MX Flash Programming Specification*" (DS61145) for operating conditions during programming and erase cycles.

#### TABLE 29-12: PROGRAM FLASH MEMORY WAIT STATE CHARACTERISTICS

| DC CHARACTERISTICS         | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |       |          |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|--|--|--|

| Required Flash wait states | SYSCLK                                                                                                                                                                                 | Units | Comments |  |  |  |

| 0 Wait State               | 0 to 30                                                                                                                                                                                |       |          |  |  |  |

| 1 Wait State               | 31 to 60                                                                                                                                                                               | MHz   | —        |  |  |  |

| 2 Wait States              | 61 to 80                                                                                                                                                                               |       |          |  |  |  |

**Note 1:** 40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.