Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 40MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx420f032ht-40i-mr |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin                | Number <sup>(</sup> | 1)              |             |                |                                                 |

|----------|--------------------|---------------------|-----------------|-------------|----------------|-------------------------------------------------|

| Pin Name | 64-pin<br>QFN/TQFP | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type | Buffer<br>Type | Description                                     |

| RG0      | _                  | 90                  | A5              | I/O         | ST             | PORTG is a bidirectional I/O port.              |

| RG1      | _                  | 89                  | E6              | I/O         | ST             |                                                 |

| RG6      | 4                  | 10                  | E3              | I/O         | ST             |                                                 |

| RG7      | 5                  | 11                  | F4              | I/O         | ST             |                                                 |

| RG8      | 6                  | 12                  | F2              | I/O         | ST             |                                                 |

| RG9      | 8                  | 14                  | F3              | I/O         | ST             |                                                 |

| RG12     | _                  | 96                  | C3              | I/O         | ST             |                                                 |

| RG13     | _                  | 97                  | А3              | I/O         | ST             |                                                 |

| RG14     | _                  | 95                  | C4              | I/O         | ST             |                                                 |

| RG15     | _                  | 1                   | B2              | I/O         | ST             |                                                 |

| RG2      | 37                 | 57                  | H10             | I           | ST             | PORTG input pins.                               |

| RG3      | 36                 | 56                  | J11             | ı           | ST             |                                                 |

| T1CK     | 48                 | 74                  | B11             | I           | ST             | Timer1 external clock input.                    |

| T2CK     | _                  | 6                   | D1              | I           | ST             | Timer2 external clock input.                    |

| T3CK     | _                  | 7                   | E4              | I           | ST             | Timer3 external clock input.                    |

| T4CK     | _                  | 8                   | E2              | I           | ST             | Timer4 external clock input.                    |

| T5CK     | _                  | 9                   | E1              | I           | ST             | Timer5 external clock input.                    |

| U1CTS    | 43                 | 47                  | L9              | I           | ST             | UART1 clear to send.                            |

| U1RTS    | 35, 49             | 48                  | K9              | 0           | _              | UART1 ready to send.                            |

| U1RX     | 34, 50             | 52                  | K11             | I           | ST             | UART1 receive.                                  |

| U1TX     | 33, 51             | 51, 53              | J10, K10        | 0           | _              | UART1 transmit.                                 |

| U2CTS    | 21                 | 40                  | K6              | ı           | ST             | UART2 clear to send.                            |

| U2RTS    | 29                 | 39                  | L6              | 0           | _              | UART2 ready to send.                            |

| U2RX     | 31                 | 49                  | L10             | I           | ST             | UART2 receive.                                  |

| U2TX     | 32                 | 50                  | L11             | 0           | _              | UART2 transmit.                                 |

| SCK1     | 35                 | 55, 70              | D11, H9         | I/O         | ST             | Synchronous serial clock input/output for SPI1. |

| SDI1     | 34                 | 9, 54               | E1, H8          | I           | ST             | SPI1 data in.                                   |

| SDO1     | 33                 | 53, 72              | D9, J10         | 0           | _              | SPI1 data out.                                  |

| SS1      | 14                 | 23, 69              | E10, J2         | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O.  |

| SCK2     | 4                  | 10                  | E3              | I/O         | ST             | Synchronous serial clock input/output for SPI2. |

| SDI2     | 5                  | 11                  | F4              | I           | ST             | SPI2 data in.                                   |

| SDO2     | 6                  | 12                  | F2              | 0           |                | SPI2 data out.                                  |

| SS2      | 8                  | 14                  | F3              | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O.  |

| SCL1     | 37, 44             | 57, 66              | E11, H10        | I/O         | ST             | Synchronous serial clock input/output for I2C1. |

| SDA1     | 36, 43             | 56, 67              | E8, J11         | I/O         | ST             | Synchronous serial data input/output for I2C1.  |

| SCL2     | 32                 | 58                  | H11             | I/O         | ST             | Synchronous serial clock input/output for I2C2. |

| SDA2     | 31                 | 59                  | G10             | I/O         | ST             | Synchronous serial data input/output for I2C2.  |

|          | CMOS - CM          |                     |                 |             |                | palea – Apalea input                            |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input P = PowerO = Output I = Input

TTL = TTL input buffer

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin                | Number <sup>(</sup> | 1)              | D:          | Duffe          |                                                                                                           |

|----------|--------------------|---------------------|-----------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/TQFP | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type | Buffer<br>Type | Description                                                                                               |

| PMD0     | 60                 | 93                  | A4              | I/O         | TTL/ST         | Parallel Master Port Data (De-multiplexed Master                                                          |

| PMD1     | 61                 | 94                  | В4              | I/O         | TTL/ST         | mode) or Address/Data (Multiplexed Master modes).                                                         |

| PMD2     | 62                 | 98                  | В3              | I/O         | TTL/ST         |                                                                                                           |

| PMD3     | 63                 | 99                  | A2              | I/O         | TTL/ST         |                                                                                                           |

| PMD4     | 64                 | 100                 | A1              | I/O         | TTL/ST         |                                                                                                           |

| PMD5     | 1                  | 3                   | D3              | I/O         | TTL/ST         |                                                                                                           |

| PMD6     | 2                  | 4                   | C1              | I/O         | TTL/ST         |                                                                                                           |

| PMD7     | 3                  | 5                   | D2              | I/O         | TTL/ST         |                                                                                                           |

| PMD8     | _                  | 90                  | A5              | I/O         | TTL/ST         |                                                                                                           |

| PMD9     | _                  | 89                  | E6              | I/O         | TTL/ST         |                                                                                                           |

| PMD10    | _                  | 88                  | A6              | I/O         | TTL/ST         |                                                                                                           |

| PMD11    | _                  | 87                  | B6              | I/O         | TTL/ST         |                                                                                                           |

| PMD12    | _                  | 79                  | A9              | I/O         | TTL/ST         |                                                                                                           |

| PMD13    | _                  | 80                  | D8              | I/O         | TTL/ST         |                                                                                                           |

| PMD14    | _                  | 83                  | D7              | I/O         | TTL/ST         |                                                                                                           |

| PMD15    | _                  | 84                  | C7              | I/O         | TTL/ST         |                                                                                                           |

| PMRD     | 53                 | 82                  | B8              | 0           | _              | Parallel Master Port Read Strobe.                                                                         |

| PMWR     | 52                 | 81                  | C8              | 0           | _              | Parallel Master Port Write Strobe.                                                                        |

| PMALL    | 30                 | 44                  | L8              | 0           | _              | Parallel Master Port Address Latch Enable low-byte (Multiplexed Master modes).                            |

| PMALH    | 29                 | 43                  | K7              | 0           | _              | Parallel Master Port Address Latch Enable high-byte (Multiplexed Master modes).                           |

| VBUS     | 34                 | 54                  | H8              | I           | Analog         | USB Bus Power Monitor.                                                                                    |

| Vusb     | 35                 | 55                  | H9              | Р           | _              | USB Internal Transceiver Supply. If the USB module is <i>not</i> used, this pin must be connected to VDD. |

| VBUSON   | 11                 | 20                  | H1              | 0           | _              | USB Host and OTG Bus Power Control Output.                                                                |

| D+       | 37                 | 57                  | H10             | I/O         | Analog         | USB D+.                                                                                                   |

| D-       | 36                 | 56                  | J11             | I/O         | Analog         | USB D                                                                                                     |

| USBID    | 33                 | 51                  | K10             | I           | ST             | USB OTG ID Detect.                                                                                        |

| ENVREG   | 57                 | 86                  | A7              | I           | ST             | Enable for On-Chip Voltage Regulator.                                                                     |

| TRCLK    | _                  | 91                  | C5              | 0           | _              | Trace Clock.                                                                                              |

| TRD0     | _                  | 97                  | А3              | 0           | _              | Trace Data Bits 0-3.                                                                                      |

| TRD1     | _                  | 96                  | C3              | 0           | _              |                                                                                                           |

| TRD2     |                    | 95                  | C4              | 0           | _              |                                                                                                           |

| TRD3     |                    | 92                  | B5              | 0           |                |                                                                                                           |

| PGED1    | 16                 | 25                  | K2              | I/O         | ST             | Data I/O pin for programming/debugging communication channel 1.                                           |

| PGEC1    | 15                 | 24                  | K1              | I           | ST             | Clock input pin for programming/debugging communication channel 1.                                        |

|          | CNACC CNA          | 00 00000            |                 |             | ·              | nolog Angleginnut D Dower                                                                                 |

**Legend:** CMOS = CMOS compatible input or output

Analog = Analog input

P = Power

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

TTL = TTL input buffer

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

#### 2.11 Referenced Sources

This device data sheet is based on the following individual chapters of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX460F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS61127)

- Section 2. "CPU" (DS61113)

- Section 3. "Memory Organization" (DS61115)

- Section 4. "Prefetch Cache" (DS61119)

- Section 5. "Flash Program Memory" (DS61121)

- Section 6. "Oscillator Configuration" (DS61112)

- Section 7. "Resets" (DS61118)

- Section 8. "Interrupt Controller" (DS61108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS61114)

- Section 10. "Power-Saving Features" (DS61130)

- Section 12. "I/O Ports" (DS61120)

- Section 13. "Parallel Master Port (PMP)" (DS61128)

- Section 14. "Timers" (DS61105)

- Section 15. "Input Capture" (DS61122)

- Section 16. "Output Compare" (DS61111)

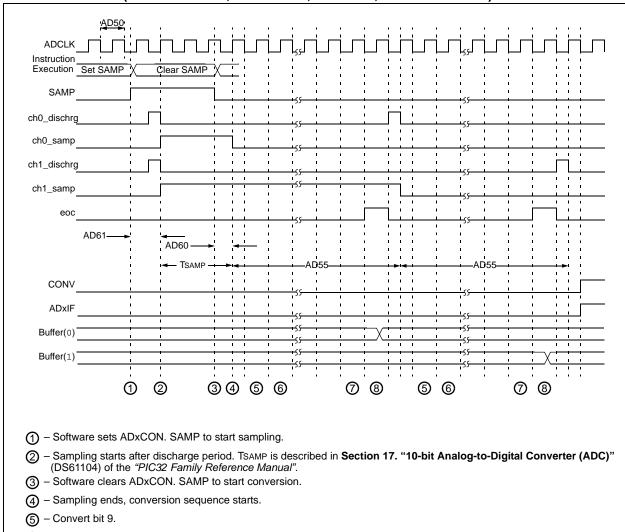

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS61104)

- **Section 19. "Comparator"** (DS61110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS61109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS61116)

- Section 27. "USB On-The-Go (OTG)" (DS61126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS61125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS61117)

- Section 32. "Configuration" (DS61124)

- Section 33. "Programming and Diagnostics" (DS61129)

### 4.0 MEMORY ORGANIZATION

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Memory Organization" (DS61115) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX3XX/4XX microcontrollers provide 4 GB of unified virtual memory address space. All memory regions including program, data memory, SFRs and Configuration registers reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX3XX/4XX to execute from data memory.

### 4.1 Key Features

- · 32-bit native data width

- · Separate User and Kernel mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- · Cacheable and non-cacheable address regions

## 4.2 PIC32MX3XX/4XX Memory Layout

PIC32MX3XX/4XX microcontrollers implement two address spaces: Virtual and Physical. All hardware resources such as program memory, data memory and peripherals are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by peripherals such as DMA and Flash controller that access memory independently of CPU.

1140

| SS                          |                        |               |         |                       |         |         |                            |        |               | В                | its      |          |            |            |                         |            |        |                 |            |

|-----------------------------|------------------------|---------------|---------|-----------------------|---------|---------|----------------------------|--------|---------------|------------------|----------|----------|------------|------------|-------------------------|------------|--------|-----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15   | 30/14                 | 29/13   | 28/12   | 27/11                      | 26/10  | 25/9          | 24/8             | 23/7     | 22/6     | 21/5       | 20/4       | 19/3                    | 18/2       | 17/1   | 16/0            | All Resets |

| 1000                        | INTCON                 | 31:16         | _       | _                     | _       | _       |                            | _      | _             | _                | _        | _        |            | _          | _                       | _          | _      | SS0             | 000        |

|                             |                        | 15:0          | _       | _                     | _       | MVEC    |                            |        | TPC<2:0>      |                  | _        | _        |            | INT4EP     | INT3EP                  | INT2EP     | INT1EP | INT0EP          | 000        |

| 1010                        | INTSTAT <sup>(2)</sup> | 31:16         | _       | _                     | _       | _       | _                          | _      |               | _                | _        | _        | _          | _          |                         |            | _      | _               | 000        |

|                             |                        | 15:0          | _       | _                     | _       | _       |                            |        | SRIPL<2:0>    | •                | _        | _        |            |            | VEC-                    | <5:0>      |        |                 | 000        |

| 1020                        | IPTMR                  | 31:16<br>15:0 |         | IPTMR<31:0> 0000 0000 |         |         |                            |        |               |                  |          |          |            |            |                         |            |        |                 |            |

| 1020                        | IFS0                   | 31:16         | I2C1MIF | I2C1SIF               | I2C1BIF | U1TXIF  | U1RXIF                     | U1EIF  | _             | _                | _        | OC5IF    | IC5IF      | T5IF       | INT4IF                  | OC4IF      | IC4IF  | T4IF            | 000        |

| 1030                        | IF50                   | 15:0          | INT3IF  | OC3IF                 | IC3IF   | T3IF    | INT2IF                     | OC2IF  | IC2IF         | T2IF             | INT1IF   | OC1IF    | IC1IF      | T1IF       | INT0IF                  | CS1IF      | CS0IF  | CTIF            | 000        |

| 1040                        | IFS1                   | 31:16         | _       | _                     | _       | _       | _                          | _      | USBIF         | FCEIF            | _        | _        | _          | _          | DMA3IF                  | DMA2IF     | DMA1IF | DMA0IF          | 000        |

| 1040                        | 1501                   | 15:0          | RTCCIF  | FSCMIF                | I2C2MIF | I2C2SIF | I2C2BIF                    | U2TXIF | U2RXIF        | U2EIF            | SPI2RXIF | SPI2TXIF | SPI2EIF    | CMP2IF     | CMP1IF                  | PMPIF      | AD1IF  | CNIF            | 000        |

| 1060                        | IEC0                   | 31:16         | I2C1MIE | I2C1SIE               | I2C1BIE | U1TXIE  | U1RXIE                     | U1EIE  | _             | _                | _        | OC5IE    | IC5IE      | T5IE       | INT4IE                  | OC4IE      | IC4IE  | T4IE            | 000        |

| 1000                        | 1200                   | 15:0          | INT3IE  | OC3IE                 | IC3IE   | T3IE    | INT2IE                     | OC2IE  | IC2IE         | T2IE             | INT1IE   | OC1IE    | IC1IE      | T1IE       | INT0IE                  | CS1IE      | CS0IE  | CTIE            | 000        |

| 1070                        | IEC1                   | 31:16         | _       | _                     | _       | _       |                            | _      | USBIE         | FCEIE            | _        | _        | -          | _          | DMA3IE                  | DMA2IE     | DMA1IE | DMA0IE          | 000        |

| 1070                        | iLO1                   | 15:0          | RTCCIE  | FSCMIE                | I2C2MIE | I2C2SIE | I2C2BIE                    | U2TXIE | U2RXIE        | U2EIE            | SPI2RXIE | SPI2TXIE | SPI2EIE    | CMP2IE     | CMP1IE                  | PMPIE      | AD1IE  | CNIE            | 000        |

| 1090                        | IPC0                   | 31:16         | _       | _                     | _       |         | NT0IP<2:0>                 |        | INT0IS<1:0> — |                  | _        | _        | CS1IP<2:0> |            | CS1IS<1:0>              |            | 000    |                 |            |

|                             |                        | 15:0          | _       | _                     | _       |         | CS0IP<2:0>                 |        | CS0IS<1:0>    |                  | _        | _        | _          |            | CTIP<2:0>               |            |        | <1:0>           | 000        |

| 10A0                        | IPC1                   | 31:16         | _       | _                     | _       |         | NT1IP<2:0>                 | •      | INT1IS<1:0>   |                  | _        | _        | _          | OC1IP<2:0> |                         | OC1IS<1:0> |        | 000             |            |

|                             |                        | 15:0          | _       | _                     | _       |         | IC1IP<2:0>                 |        |               | 5<1:0>           | _        | _        | _          | T1IP<2:0>  |                         | T1IS<1:0>  |        | 000             |            |

| 10B0                        | IPC2                   | 31:16         | _       | _                     | _       | ļ       | NT2IP<2:0>                 | •      |               | S<1:0>           | _        | _        | _          | OC2IP<2:0> |                         | OC2IS<1:0  |        | 000             |            |

|                             |                        | 15:0          | _       | _                     | _       |         | IC2IP<2:0>                 |        |               | 5<1:0>           | _        | _        | _          | T2IP<2:0>  |                         |            | <1:0>  | 000             |            |

| 10C0                        | IPC3                   | 31:16         |         |                       | _       |         | NT3IP<2:0>                 | •      |               | S<1:0>           | _        | _        |            |            | OC3IP<2:0>              |            |        | S<1:0>          | 000        |

|                             |                        | 15:0          | _       | _                     | _       |         | IC3IP<2:0>                 |        |               | S<1:0>           | _        | _        |            |            | T3IP<2:0>               |            |        | <1:0>           | 000        |

| 10D0                        | IPC4                   | 31:16<br>15:0 | _       | _                     |         |         | INT4IP<2:0>                | •      |               | S<1:0><br>S<1:0> | _        | _        |            |            | OC4IP<2:0><br>T4IP<2:0> | •          |        | S<1:0><br><1:0> | 000        |

|                             |                        | 31:16         |         |                       | _       | _       | 1041P<2:0>                 | _      | 10415         | N = 1:0>         | _        | _        |            |            | OC5IP<2:0>              |            |        | <1:0><br>S<1:0> | 000        |

| 10E0                        | IPC5                   | 15:0          | _       |                       |         | _       | IC5IP<2:0>                 |        | ICEIS         | S<1:0>           | _        |          |            |            | T5IP<2:0>               |            |        | <1:0>           | 000        |

|                             |                        | 31:16         |         |                       |         |         | AD1IP<2:0>                 |        |               | S<1:0>           | _        |          |            |            | CNIP<2:0>               |            |        | <1:0>           | 000        |

| 10F0                        | IPC6                   | 15:0          |         |                       | _       |         | I2C1IP<2:0>                |        |               | S<1:0>           | _        |          |            |            | U1IP<2:0>               |            |        | <1:0>           | 000        |

|                             |                        | 31:16         |         |                       |         |         | SPI2IP<2:0>                |        |               | S<1:0>           | _        | _        |            | (          | CMP2IP<2:0              | >          |        | S<1:0>          | 000        |

| 1100                        | IPC7                   | 15:0          | _       |                       | _       |         | SPIZIP<2:0><br>CMP1IP<2:0> |        |               | S<1:0>           | _        | _        |            |            | PMPIP<2:0>              |            |        | S<1:0>          | 000        |

|                             |                        | 31:16         | _       |                       | _       |         | RTCCIP<2:0:                |        |               | IS<1:0>          | _        | _        |            |            | SCMIP<2:0               |            |        |                 | 000        |

| 1110                        | IPC8                   | 15:0          | _       | _                     | _       |         | 12C2IP<2:0>                |        |               | S<1:0>           | _        | _        |            |            | U2IP<2:0>               |            |        | <1:0>           | 000        |

|                             |                        | 31:16         | _       |                       | _       |         | MA3IP<2:0:                 |        |               | S<1:0>           | _        | _        |            | 1          | DMA2IP<2:0              | >          |        | S<1:0>          | 000        |

| 1120                        | IPC9                   | 15:0          |         |                       | _       |         | MA1IP<2:0:                 |        |               | S<1:0>           | _        | _        |            |            | OMA0IP<2:0              |            | DMA0I  |                 | 000        |

PIC32MX3XX/4XX

0000

0000

FCEIS<1:0>

FCEIP<2:0>

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

USBIP<2:0>

USBIS<1:0>

Except where noted, all registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated CLR, SET, and INV registers.

## TABLE 4-43: USB REGISTERS MAP<sup>(1)</sup> (CONTINUED)

|                             |                  |           | , O D I \ L |       | 10 1117 11 |       |       | <u> </u> |      |      |      |      |          |          |        |        |          |        |            |

|-----------------------------|------------------|-----------|-------------|-------|------------|-------|-------|----------|------|------|------|------|----------|----------|--------|--------|----------|--------|------------|

| ess                         |                  |           |             |       |            |       |       |          |      |      | Bits |      | <u> </u> |          |        |        | <u> </u> |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15       | 30/14 | 29/13      | 28/12 | 27/11 | 26/10    | 25/9 | 24/8 | 23/7 | 22/6 | 21/5     | 20/4     | 19/3   | 18/2   | 17/1     | 16/0   | All Resets |

| 5380                        | U1EP8            | 31:16     | _           | _     | _          | _     | _     | _        | _    | _    | _    | _    | _        | _        | _      | _      | _        | _      | 0000       |

| 5560                        | UILFO            | 15:0      | _           |       | _          | _     | _     | _        | _    | _    | _    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 5390                        | U1EP9            | 31:16     |             | 1     | 1          | _     | İ     |          | _    | _    | 1    | _    | _        | _        | 1      | _      | 1        | 1      | 0000       |

| 5590                        | UIEF9            | 15:0      |             | 1     | _          | _     |       | _        | _    | _    | 1    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 53A0                        | U1EP10           | 31:16     | _           | 1     | -          | _     | -     | _        | _    | _    | 1    | _    | _        | _        | 1      | _      | -        | 1      | 0000       |

| 3370                        | OTET TO          | 15:0      |             | 1     | 1          | _     | İ     |          | _    | _    | 1    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 53B0                        | U1EP11           | 31:16     | _           |       | -          | _     | -     | _        |      | _    | 1    | _    | _        | _        | 1      | _      | -        | ı      | 0000       |

| 3300                        | OTET II          | 15:0      | _           | -     | _          | _     | -     | _        | _    | _    | _    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 53C0                        | U1EP12           | 31:16     | _           | -     | _          | _     | _     | _        | _    | _    | _    | _    | _        | _        | _      | _      | _        | _      | 0000       |

| 3300                        | OTET 12          | 15:0      | _           | _     | _          | _     | _     | _        | _    | _    | _    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 53D0                        | U1EP13           | 31:16     | _           | _     |            | _     | _     | _        | _    | _    | _    | _    | _        | _        | _      | _      | _        | _      | 0000       |

| 0000                        | O I E I I I O    | 15:0      | _           | _     | _          | _     | _     | _        | _    | _    | _    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 53E0                        | U1EP14           | 31:16     | _           | _     | _          | _     | _     | _        | _    | _    | _    | _    | _        | _        | _      | _      | _        | _      | 0000       |

| 0020                        | O I E I I I      | 15:0      | _           | _     |            | _     | _     | _        | _    | _    | _    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

| 53F0                        | U1EP15           | 31:16     | _           | _     | _          | _     | _     | _        | _    | _    | _    | _    | _        | _        | _      | _      | _        | _      | 0000       |

| 3310                        |                  | 15:0      | _           |       | -          | _     | 1     | _        |      | _    | 1    | _    | _        | EPCONDIS | EPRXEN | EPTXEN | EPSTALL  | EPHSHK | 0000       |

PIC32MX3XX/4XX

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

- 2: This register does not have associated CLR, SET, and INV registers.

- 3: All bits in this register are read-only; therefore, CLR, SET, and INV registers are not supported.

- 4: The reset value for this bit is undefined.

#### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS61121) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

PIC32MX3XX/4XX devices contain an internal program Flash memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self Programming (RTSP)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- EJTAG Programming

RTSP is performed by software executing from either Flash or RAM memory. EJTAG is performed using the EJTAG port of the device and a EJTAG capable programmer. ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP. RTSP techniques are described in this chapter. The ICSP and EJTAG methods are described in the "PIC32MX Flash Programming Specification" (DS61145), which can be downloaded from the Microchip web site.

Flash LVD Delay (LVDstartup) must be taken into account between setting up and executing any Flash command operation. See Example 5-1 for a code example to set up and execute a Flash command operation.

#### **EXAMPLE 5-1:**

Note:

**NOTES:**

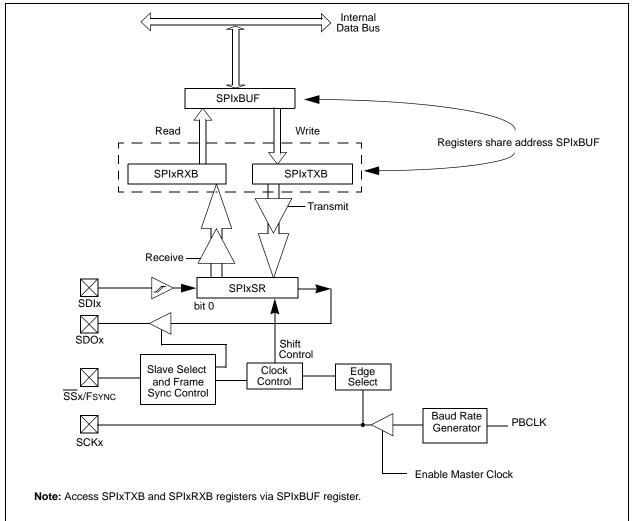

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32MX SPI module is compatible with Motorola® SPI and SIOP interfaces.

Following are some of the key features of this module:

- · Master and Slave Modes Support

- · Four Different Clock Formats

- · Framed SPI Protocol Support

- User Configurable 8-bit, 16-bit and 32-bit Data Width

- Separate SPI Data Registers for Receive and Transmit

- Programmable Interrupt Event on every 8-bit, 16-bit and 32-bit Data Transfer

- · Operation during CPU Sleep and Idle Mode

- Fast Bit Manipulation using CLR, SET and INV Registers

#### FIGURE 17-1: SPI MODULE BLOCK DIAGRAM

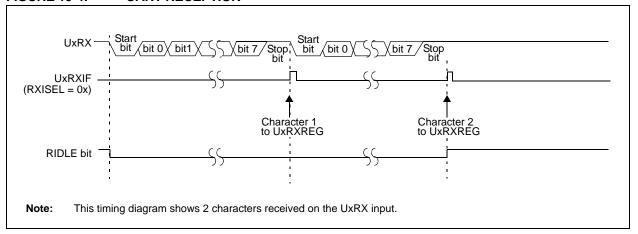

## FIGURE 19-4: UART RECEPTION

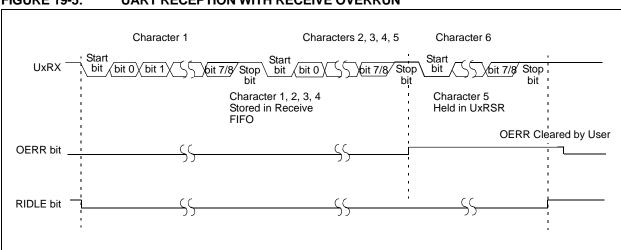

### FIGURE 19-5: UART RECEPTION WITH RECEIVE OVERRUN

**Note:** This diagram shows 6 characters received without the user reading the input buffer. The 5th character received is held in the Receive Shift register. An overrun error occurs at the start of the 6th character.

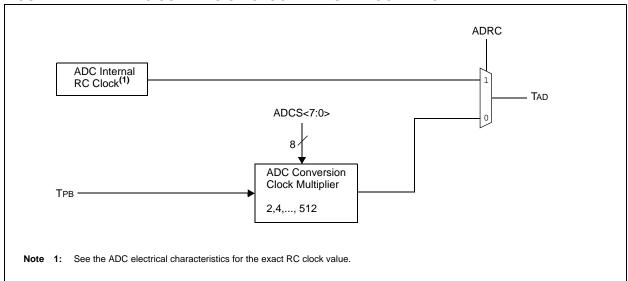

## FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

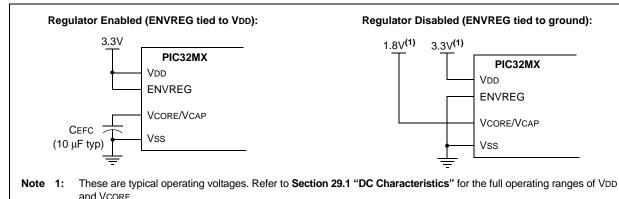

### 26.3 On-Chip Voltage Regulator

All PIC32MX3XX/4XX device's core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX3XX/4XX incorporate an on-chip regulator providing the required core logic voltage from VDD.

The internal 1.8V regulator is controlled by the ENVREG pin. Tying this pin to VDD enables the regulator, which in turn provides power to the core. A low ESR capacitor (such as tantalum) must be connected to the VCORE/VCAP pin (Figure 26-2). This helps to maintain the stability of the regulator. The recommended value for the filer capacitor is provided in **Section 29.1 "DC Characteristics"**.

**Note:** It is important that the low ESR capacitor is placed as close as possible to the VCORE/VCAP pin.

Tying the ENVREG pin to Vss disables the regulator. In this case, separate power for the core logic at a nominal 1.8V must be supplied to the device on the VCORE/VCAP pin.

Alternatively, the VCORE/VCAP and VDD pins can be tied together to operate at a lower nominal voltage. Refer to Figure 26-2 for possible configurations.

#### 26.3.1 ON-CHIP REGULATOR AND POR

When the voltage regulator is enabled, it takes fixed delay for it to generate output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

If the regulator is disabled, a separate Power-up Timer (PWRT) is automatically enabled. The PWRT adds a fixed delay of TPWRT at device start-up. See **Section 29.0 "Electrical Characteristics"** for more information on TPU AND TPWRT.

#### 26.3.2 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC32MX3XX/4XX devices also have a simple brownout capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 29.1** "DC Characteristics".

#### 26.3.3 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VCORE must never exceed VDD by 0.3 volts.

#### FIGURE 26-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

TABLE 27-1: MIPS32<sup>®</sup> INSTRUCTION SET (CONTINUED)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Instruction | Description                                                | Function                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| BLTZAL Branch on Less Than Zero and Link BLTZALL Branch on Less Than Zero and Link GPR[31] = PC + 8 if Rs[31] PC += (int)offset  BLTZALL Branch on Less Than Zero and Link Likely(1) BLTZL Branch on Less Than Zero Likely(1) BLTZL Branch on Less Than Zero Likely(1) BLTZL Branch on Not Equal BLTZL Branch on Not Equal BRE BRE BRAC BRE BRAC BREAC BRE BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC BREAC B | BLEZL       | Branch on Less Than or Equal to Zero Likely <sup>(1)</sup> | PC += (int)offset else                                                                                   |

| BLTZALL  Branch on Less Than Zero and Link Likely(1)  BLTZALL  Branch on Less Than Zero Likely(1)  BLTZL  Branch on Less Than Zero Likely(1)  BLTZL  Branch on Less Than Zero Likely(1)  BLTZL  Branch on Less Than Zero Likely(1)  BNE  Branch on Not Equal  BNE  Branch on Not Equal  BNE  Branch on Not Equal Likely(1)  BNE  Branch on Not Equal Likely(1)  BREAK  Breakpoint  CLO  Count Leading Ones  CLZ  Count Leading Ones  CLZ  Count Leading Zeroes  Return from Debug Exception  DIV  Divide  DIV  Divide  LO = (int)Rs / (int)Rt HI = (int)Rs / (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rt HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI = (int)Rs & (int)Rs HI | BLTZ        | Branch on Less Than Zero                                   |                                                                                                          |

| If Rs[31]   PC += (int) offset else   Else   Ignore Next Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BLTZAL      | Branch on Less Than Zero and Link                          | if Rs[31]                                                                                                |

| BNE Branch on Not Equal if Rs != Rt PC += (int)offset else Ignore Next Instruction  BNE Branch on Not Equal if Rs != Rt PC += (int)offset  BNEL Branch on Not Equal Likely(1) if Rs != Rt PC += (int)offset else Ignore Next Instruction  BREAK Breakpoint Break Exception  CLO Count Leading Ones Rd = NumLeadingOnes(Rs)  CLZ Count Leading Zeroes Rd = NumLeadingZeroes(Rs)  DERET Return from Debug Exception PC = DEPC Exit Debug Mode  DI Atomically Disable Interrupts Rt = Status; Status; = 0  DIV Divide LO = (int)Rs / (int)Rt HI = (int)Rs % (int)Rt  DIVU Unsigned Divide LO = (uns)Rs / (uns)Rt HI = (uns)Rs % (uns)Rt  EHB Execution Hazard Barrier Stop instruction execution until execution hazards are cleared  EI Atomically Enable Interrupts Rt = Status; Status; = 1  ERET Return from Exception if Status; = 0  EXT Extract Bit Field Rt = ExtractField(Rs, pos, size)  INS Insert Bit Field Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BLTZALL     | Branch on Less Than Zero and Link Likely <sup>(1)</sup>    | <pre>if Rs[31]   PC += (int)offset else</pre>                                                            |

| BNEL Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Equal Likely(1)  Branch on Not Instruction  Branch on Not Instruction  Brank Exception  Branch on Not Instruction  Branch on Not Equal Likely(1)  Branch Professor (Rs)  Brank Exception  Brank Exception  Branch on Not Equal Likely(1)  Branch Professor (Rs)  Rd = NumLeadingOnes (Rs)  Brank Exception  Brank Exception  Branch on Not Instruction  Branch on Not Instruction  Branch on Not Instruction  Branch Exception  Branch on Not Instruction  Branch Professor (Rs)  Brank Exception  Branch Professor (Rs)  Brank Exception  Branch Professor (Rs)  Rd = NumLeadingOnes (Rs)  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Branch Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Brank Exception  Bra | BLTZL       | Branch on Less Than Zero Likely <sup>(1)</sup>             | PC += (int)offset else                                                                                   |

| BREAK Breakpoint Break Exception  CLO Count Leading Ones Rd = NumLeadingOnes(Rs)  CLZ Count Leading Zeroes Rd = NumLeadingZeroes(Rs)  DERET Return from Debug Exception PC = DEPC Exit Debug Mode  DI Atomically Disable Interrupts Rt = Status; Status_{IE} = 0  DIV Divide LO = (int)Rs / (int)Rt HI = (int)Rs % (int)Rt  DIVU Unsigned Divide LO = (uns)Rs / (uns)Rt  EHB Execution Hazard Barrier Stop instruction execution until execution hazards are cleared  EI Atomically Enable Interrupts Rt = Status; Status_{IE} = 1  ERET Return from Exception if Status_{ERL} PC = ErrorEPC else PC = EPC Status_{ERL} = 0  Status_{ERL} = 0  LL = 0  EXT Extract Bit Field Rt = ExtractField(Rs, pos, size)  INS Insert Bit Field Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BNE         | Branch on Not Equal                                        |                                                                                                          |

| CLO Count Leading Ones  Rd = NumLeadingOnes(Rs)  CLZ Count Leading Zeroes  Rd = NumLeadingZeroes(Rs)  PC = DEPC Exit Debug Mode  DI Atomically Disable Interrupts  Rt = Status; Status_IE = 0  DIV Divide  LO = (int)Rs / (int)Rt HI = (int)Rs % (int)Rt HI = (uns)Rs / (uns)Rt HI = (uns)Rs % (uns)Rt HI = (uns)Rs % (uns)Rt HI = (struction execution until execution hazards are cleared  EI Atomically Enable Interrupts  Rt = Status; Status_IE = 1  ERET  Return from Exception  if Status_ERL PC = ErrorEPC else PC = EPC Status_EXL = 0 Status_EXL = 0 LL = 0  EXT Extract Bit Field  Rt = ExtractField(Rs, pos, size)  INS Insert Bit Field  Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BNEL        | Branch on Not Equal Likely <sup>(1)</sup>                  | PC += (int)offset else                                                                                   |

| CLZ       Count Leading Zeroes       Rd = NumLeadingZeroes(Rs)         DERET       Return from Debug Exception       PC = DEPC         Exit Debug Mode       DI       Atomically Disable Interrupts       Rt = Status; Status_IE = 0         DIV       Divide       LO = (int)Rs / (int)Rt         HI = (int)Rs % (int)Rt       HI = (uns)Rs / (uns)Rt         EHB       Execution Hazard Barrier       Stop instruction execution until execution hazards are cleared         EI       Atomically Enable Interrupts       Rt = Status; Status_IE = 1         ERET       Return from Exception       if Status_ERL PC = ErrorEPC else PC = EPC Status_ERL = 0 LL = 0         EXT       Extract Bit Field       Rt = ExtractField(Rs, pos, size)         INS       Insert Bit Field       Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BREAK       | Breakpoint                                                 | Break Exception                                                                                          |

| DERET       Return from Debug Exception       PC = DEPC Exit Debug Mode         DI       Atomically Disable Interrupts       Rt = Status; Status_IE = 0         DIV       Divide       L0 = (int)Rs / (int)Rt HI = (int)Rs % (int)Rt         DIVU       Unsigned Divide       L0 = (uns)Rs / (uns)Rt HI = (uns)Rs % (uns)Rt         EHB       Execution Hazard Barrier       Stop instruction execution until execution hazards are cleared         EI       Atomically Enable Interrupts       Rt = Status; Status_IE = 1         ERET       Return from Exception       if Status_ERL PC = ErrorEPC else         EVE       Extract Bit Field       Rt = ExtractField(Rs, pos, size)         INS       Insert Bit Field       Rt = InsertField(Rs, Rt, posize)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CLO         | Count Leading Ones                                         | Rd = NumLeadingOnes(Rs)                                                                                  |

| Exit Debug Mode  DI Atomically Disable Interrupts  Rt = Status; Status_IE = 0  DIV Divide  LO = (int)Rs / (int)Rt HI = (int)Rs % (int)Rt HI = (uns)Rs % (uns)Rt HI = (uns)Rs % (uns)Rt HI = (uns)Rs % (uns)Rt Stop instruction execution until execution hazards are cleared  EI Atomically Enable Interrupts  Rt = Status; Status_IE = 1  ERET Return from Exception  if Status_ERL PC = ErrorEPC else PC = EPC Status_EXL = 0 Status_EXL = 0 LL = 0  EXT Extract Bit Field  Rt = ExtractField(Rs, pos, size)  INS Insert Bit Field  Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLZ         | Count Leading Zeroes                                       | Rd = NumLeadingZeroes(Rs)                                                                                |

| DIV Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DERET       | Return from Debug Exception                                |                                                                                                          |

| HI = (int)Rs % (int)Rt  DIVU Unsigned Divide LO = (uns)Rs / (uns)Rt HI = (uns)Rs % (uns)Rt EHB Execution Hazard Barrier Stop instruction execution until execution hazards are cleared  EI Atomically Enable Interrupts Rt = Status; Status_{IE} = 1  ERET Return from Exception if Status_{ERL} PC = ErrorEPC else PC = EPC Status_{ERL} = 0 Status_{ERL} = 0 LL = 0  EXT Extract Bit Field Rt = ExtractField(Rs, pos, size)  INS Insert Bit Field Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DI          | Atomically Disable Interrupts                              | Rt = Status; Status <sub>IE</sub> = 0                                                                    |

| EHB Execution Hazard Barrier Stop instruction execution until execution hazards are cleared  EI Atomically Enable Interrupts Rt = Status; Status_{IE} = 1  ERET Return from Exception if Status_{ERL} PC = ErrorEPC else PC = EPC Status_{EXL} = 0 Status_{EXL} = 0 LL = 0  EXT Extract Bit Field Rt = ExtractField(Rs, pos, size)  INS Insert Bit Field Rt = InsertField(Rs, Rt, pos, size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIV         | Divide                                                     |                                                                                                          |