Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

|                            |                                                                                   |

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 40MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx420f032ht-40v-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® ICD 2, MPLAB ICD 3 or MPLAB REAL ICE™.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "MPLAB® ICD 2 In-Circuit Debugger User's Guide" DS51331

- "Using MPLAB® ICD 2" (poster) DS51265

- "MPLAB® ICD 2 Design Advisory" DS51566

- "Using MPLAB® ICD 3" (poster) DS51765

- "MPLAB® ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS51616

- "Using MPLAB® REAL ICE™" (poster) DS51749

#### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

#### 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

#### 2.8 External Oscillator Pins

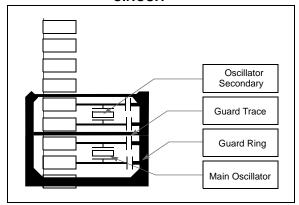

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

FIGURE 2-3: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

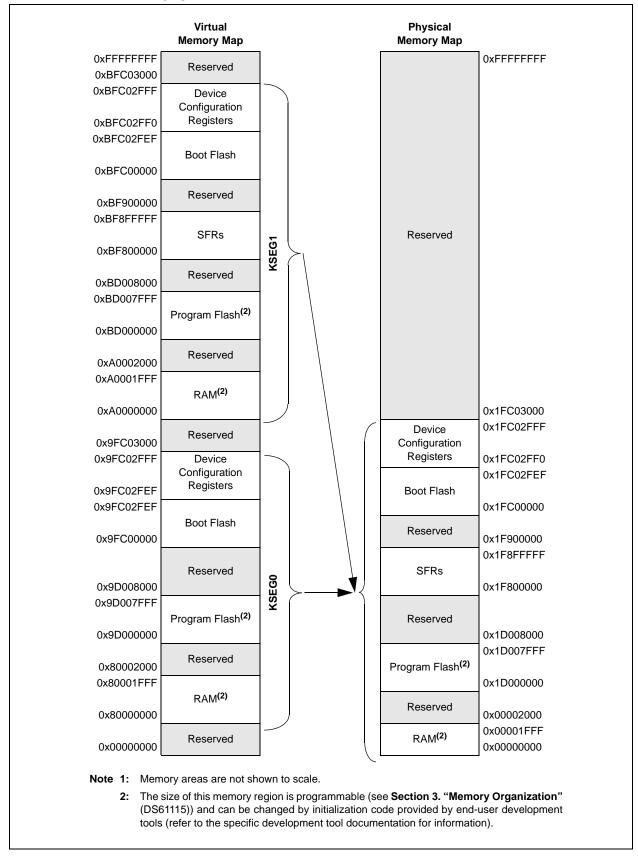

FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX320F032H AND PIC32MX420F032H DEVICES<sup>(1)</sup>

TABLE 4-1: BUS MATRIX REGISTERS MAP

| ess                         | _                    | Bits       |                         |       |       |       |       |           |      |      |         |          |      |           |           |           |            |          |               |

|-----------------------------|----------------------|------------|-------------------------|-------|-------|-------|-------|-----------|------|------|---------|----------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name     | Bit Range  | 31/15                   | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7    | 22/6     | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        |                      | 31:16      | _                       | _     | _     | _     | _     | BMXCHEDMA | _    | _    | _       | _        | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | CON <sup>(1)</sup>   | 15:0       | _                       | _     | _     | _     | _     | _         | -    | _    | _       | BMXWSDRM | _    | _         | -         | ВІ        | MXARB<2:0> |          | 0042          |

| 0040                        | DIVIA                | 31:16      | _                       | _     | _     | _     | _     | _         | 1    | _    | _       | 1        | _    | _         | 1         | _         | _          | _        | 0000          |

| 2010                        | DKPBA <sup>(1)</sup> | 15:0       |                         |       |       |       |       |           |      | BM   | IXDKPBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             | DIVIA                | 31:16      |                         | _     | _     | _     | _     | _         | 1    | _    | _       | _        | _    | _         | _         | _         | _          | _        | 0000          |

| 2020                        | DUDBA <sup>(1)</sup> | 15:0       |                         |       |       |       |       |           |      | BM   | IXDUDBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             |                      | 31:16      | _                       | _     | _     | _     | _     | _         | 1    | _    | _       | _        | _    | _         | -         | _         | _          | _        | 0000          |

| 2030                        | DUPBA <sup>(1)</sup> | 15:0       |                         |       |       |       |       |           |      | BM   | IXDUPBA | <15:0>   |      |           |           |           |            |          | 0000          |

| 00.40                       | BMX                  | 31:16      |                         |       |       |       |       |           |      |      |         | 0.4.0    |      |           |           |           |            |          | xxxx          |

| 2040                        | DRMSZ                | 15:0       |                         |       |       |       |       |           |      | BIV  | IXDRMSZ | <31:0>   |      |           |           |           |            |          | xxxx          |

| 2252                        | DIVIA                | 31:16      |                         | _     | _     | _     | _     | _         | 1    | _    | _       | _        | _    | _         |           | BMXPUPB/  | <19:16>    |          | 0000          |

| 2050                        | PUPBA <sup>(1)</sup> | 15:0       |                         |       |       |       |       |           |      | BM   | IXPUPBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             | BMX                  | 31:16      | 16 xxxx                 |       |       |       |       |           |      |      |         |          |      |           |           |           |            |          |               |

| 2060                        | PFMSZ                | 15:0       | 5:0 BMXPFMSZ<31:0> xxxx |       |       |       |       |           |      |      |         |          |      | xxxx      |           |           |            |          |               |

| 0070                        | BMX                  | 31:16 0000 |                         |       |       |       |       |           |      |      |         |          |      |           |           |           |            |          |               |

| 2070                        | BOOTSZ               | 15:0       | BMXBOOTSZ<31:0> 3000    |       |       |       |       |           |      |      |         |          |      |           |           |           |            |          |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| P          |

|------------|

| C          |

| <b>32</b>  |

| M          |

| <b>X</b> 3 |

| X          |

| <b>//</b>  |

| X          |

| ×          |

| <b>TABLE 4-8:</b> | INPLIT | CAPTURE1- | REGISTERS MAP   |

|-------------------|--------|-----------|-----------------|

| IADLL 4-0.        | HALOI  | CALIDITE  | INCUIDICING MAR |

| SSS                         |                       | _             |                                                                                                                            |                           |       |       |       |       |       | В       | its                 |      |       |      |       |      |          |      |            |

|-----------------------------|-----------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|-------|-------|-------|-------|---------|---------------------|------|-------|------|-------|------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15                                                                                                                      | 30/14                     | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8    | 23/7                | 22/6 | 21/5  | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         | _                                                                                                                          | _                         | _     | _     | _     | _     | _     | _       | _                   | _    | _     | _    | _     | _    | _        | _    | 0000       |

| 2000                        | .0.00.1               | 15:0          | ON                                                                                                                         | _                         | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR               | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2010                        | IC1BUF                | 31:16<br>15:0 |                                                                                                                            | IC1BUF<31:0>   XXXX  XXXX |       |       |       |       |       |         |                     |      |       |      |       |      |          |      |            |

| 2000                        | 100001(1)             | 31:16         | _                                                                                                                          | _                         | _     | _     | _     | _     | _     | _       | _                   | _    | _     | _    | _     | _    | _        | _    | 0000       |

| 2200                        | IC2CON <sup>(1)</sup> | 15:0          | ON                                                                                                                         | _                         | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR               | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2210                        | IC2BUF                | 31:16<br>15:0 |                                                                                                                            |                           |       |       |       |       |       | IC2BUF  | <31:0>              |      |       |      |       |      |          |      | xxxx       |

| 0400                        | IC3CON <sup>(1)</sup> | 31:16         | _                                                                                                                          | _                         | _     | _     | _     | _     | _     | _       | _                   | _    | _     | _    | _     | _    | _        | _    | 0000       |

| 2400                        | IC3CON**              | 15:0          | ON                                                                                                                         | _                         | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR               | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2410                        | IC3BUF                | 31:16<br>15:0 |                                                                                                                            |                           |       |       |       |       |       | IC3BUF  | <del>-</del> <31:0> |      |       |      |       |      |          |      | xxxx       |

| 2000                        | IC4CON <sup>(1)</sup> | 31:16         | _                                                                                                                          | _                         | _     | _     | _     | _     | _     | _       | _                   | _    | _     | _    | _     | _    | _        | _    | 0000       |

| 2600                        | IC4CON**              | 15:0          | ON                                                                                                                         | _                         | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR               | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2610                        | IC4BUF                | 31:16<br>15:0 |                                                                                                                            |                           |       |       |       |       |       | IC4BUF  | <31:0>              |      |       |      |       |      |          |      | xxxx       |

|                             | (1)                   | 31:16         | _                                                                                                                          | _                         | _     | _     | _     | _     | _     | _       | _                   | _    | _     | _    | _     | _    | _        | _    | 0000       |

| 2800                        | IC5CON <sup>(1)</sup> | 15:0          | ON                                                                                                                         | _                         | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR               | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2810                        | IC5BUF                | 31:16         |                                                                                                                            | 1                         |       | 1     |       | 1     | l l   | ICEBLIE | -21.0-              |      |       |      | 1     |      |          |      | xxxx       |

| Legend                      |                       | 15:0          | IC5BUF<31:0>  IC5BUF<31:0>  XXXX  www.value.on.Reset — = unimplemented read as '0'. Reset values are shown in hexadecimal. |                           |       |       |       |       |       |         |                     |      |       |      |       |      |          |      |            |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| TABLE 4 40. | DEVICE |     | DEVICION | 10 | CLIBABAADV |

|-------------|--------|-----|----------|----|------------|

| TABLE 4-42: | DEVICE | AND | REVISION | ıυ | SUMMARY    |

| ess                       |                  | e e       |       |                            |       |       |       |       |      | Bi   | ts   |      |      |      |      |      |      |      | S          |

|---------------------------|------------------|-----------|-------|----------------------------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14                      | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| F220                      | DEVID            | 31:16     |       | VER<3:0> DEVID<27:16> xxxx |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

| F220                      | DEVID            | 15:0      |       | DEVID<15:0> xxxx           |       |       |       |       |      |      |      |      |      |      |      |      |      |      |            |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

TABLE 4-43: USB REGISTERS MAP<sup>(1)</sup>

| SSS                         |                       |           |       |       |       |       |                    |       |      |      | Bits                   |                    |                       |             |           |          |          |          |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|--------------------|-------|------|------|------------------------|--------------------|-----------------------|-------------|-----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11              | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6               | 21/5                  | 20/4        | 19/3      | 18/2     | 17/1     | 16/0     | All Resets |

| 5040                        | U10TG                 | 31:16     | _     | _     | -     | _     | _                  | _     | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        |            |

| 3040                        | IR <sup>(2)</sup>     | 15:0      | _     | 1     | 1     | 1     |                    | 1     | 1    | _    | IDIF                   | T1MSECIF           | LSTATEIF              | ACTVIF      | SESVDIF   | SESENDIF | _        | VBUSVDIF | 0000       |

| 5050                        | U1OTG                 | 31:16     | _     | _     | _     | _     | _                  | _     | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 0000                        | IE                    | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE              | ACTVIE      | SESVDIE   | SESENDIE | _        | VBUSVDIE | 0000       |

| 5060                        | U1OTG                 | 31:16     | _     | _     | _     | _     | _                  | _     | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 0000                        | STAT <sup>(3)</sup>   | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | ID                     | _                  | LSTATE                | _           | SESVD     | SESEND   | _        | VBUSVD   | 0000       |

| 5070                        | U1OTG                 | 31:16     | _     |       |       | _     | _                  |       | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

|                             | CON                   | 15:0      | _     |       | 1     | _     | _                  |       | _    | _    | DPPULUP                | DMPULUP            | DPPULDWN              | DMPULDWN    | VBUSON    | OTGEN    | VBUSCHG  | VBUSDIS  | 0000       |

| 5080                        | U1PWRC                | 31:16     | _     |       | 1     | _     | _                  |       | _    | _    | _                      | _                  | _                     | _           | -         | _        | _        | _        | 0000       |

|                             |                       | 15:0      |       | _     | _     |       | _                  | _     |      | _    | UACTPND <sup>(4)</sup> | _                  | _                     | USLPGRD     |           | _        | USUSPEND | USBPWR   | 0000       |

|                             | (4)                   | 31:16     | _     |       | 1     | _     | _                  |       | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 5200                        | U1IR <sup>(2)</sup>   | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | STALLIF                | ATTACHIF           | RESUMEIF              | IDLEIF      | TRNIF     | SOFIF    | UERRIF   | URSTIF   | 0000       |

|                             |                       |           |       |       |       |       |                    |       |      |      | •                      |                    |                       |             |           |          |          | DETACHIF | 0000       |

|                             |                       | 31:16     | _     |       | 1     | _     | _                  |       | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 5210                        | U1IE                  | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE              | IDLEIE      | TRNIE     | SOFIE    | UERRIE   | URSTIE   | 0000       |

|                             |                       |           |       |       |       |       |                    |       |      |      | •                      |                    |                       |             |           |          |          | DETACHIE | 0000       |

|                             |                       | 31:16     | _     |       | 1     | _     | _                  |       | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 5220                        | U1EIR                 | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | BTSEF                  | BMXEF              | DMAEF                 | BTOEF       | DFN8EF    | CRC16EF  | CRC5EF   | PIDEF    | 0000       |

|                             |                       |           |       |       |       |       |                    |       |      |      |                        |                    |                       |             |           |          | EOFEF    |          | 0000       |

|                             |                       | 31:16     |       | _     | _     | _     | _                  | _     |      | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 5230                        | U1EIE                 | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | BTSEE                  | BMXEE              | DMAEE                 | BTOEE       | DFN8EE    | CRC16EE  | CRC5EE   | PIDEE    | 0000       |

|                             |                       |           |       |       |       |       |                    |       |      |      |                        |                    |                       |             |           |          | EOFEE    |          | 0000       |

| 5240                        | U1STAT <sup>(3)</sup> | 31:16     |       | _     | _     | _     | _                  | _     |      | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

|                             |                       | 15:0      | _     | 1     | 1     | _     | _                  | -     | -    | _    |                        | ENDP               | Γ<3:0> <sup>(4)</sup> |             | DIR       | PPBI     | _        | _        | 0000       |

|                             |                       | 31:16     |       | _     | _     |       | _                  | _     |      | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 5250                        | U1CON                 | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | PKTDIS                | USBRST      | HOSTEN    | RESUME   | PPBRST   | USBEN    | 0000       |

|                             |                       | .0.0      |       |       |       |       |                    |       |      |      | 0017112                | 020                | TOKBUSY               | 002.101     |           |          |          | SOFEN    | 0000       |

| 5260                        | U1ADDR                | 31:16     | _     | _     | _     | _     | _                  | _     | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 3200                        |                       | 15:0      | _     | _     | _     | _     | _                  | _     | _    | _    | LSPDEN                 |                    |                       | DE          | VADDR<6:0 | )>       |          |          | 0000       |

| 5270                        | U1BDTP1               | 31:16     | _     | _     | -     | _     | _                  | _     | _    | _    | _                      | _                  | _                     | _           | _         | _        | _        | _        | 0000       |

| 32.10                       |                       | 15:0      | _     | _     | _     | _     | —<br>as '0'. Reset | _     | _    | _    |                        |                    | В                     | DTPTRL<7:1> |           |          |          | _        | 0000       |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

<sup>:</sup> This register does not have associated CLR, SET, and INV registers.

<sup>3:</sup> All bits in this register are read-only; therefore, CLR, SET, and INV registers are not supported.

<sup>4:</sup> The reset value for this bit is undefined.

#### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS61121) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

PIC32MX3XX/4XX devices contain an internal program Flash memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self Programming (RTSP)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- EJTAG Programming

RTSP is performed by software executing from either Flash or RAM memory. EJTAG is performed using the EJTAG port of the device and a EJTAG capable programmer. ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP. RTSP techniques are described in this chapter. The ICSP and EJTAG methods are described in the "PIC32MX Flash Programming Specification" (DS61145), which can be downloaded from the Microchip web site.

Flash LVD Delay (LVDstartup) must be taken into account between setting up and executing any Flash command operation. See Example 5-1 for a code example to set up and execute a Flash command operation.

#### **EXAMPLE 5-1:**

Note:

#### 6.0 RESETS

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Resets" (DS61118) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

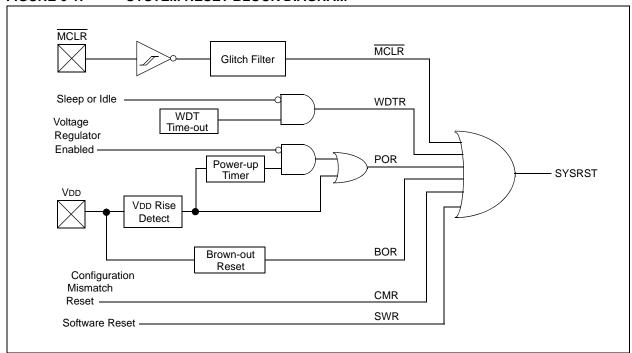

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

· POR: Power-on Reset

MCLR: Master Clear Reset Pin

• SWR: Software Reset

· WDTR: Watchdog Timer Reset

• BOR: Brown-out Reset

· CMR: Configuration Mismatch Reset

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

NOTES:

#### 25.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS61130) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This section describes power-saving for the PIC32MX3XX/4XX. The PIC32MX devices offer a total of nine methods and modes that are organized into two categories that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

### 25.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK, and by individually disabling modules. These methods are grouped into the following modes:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

- Peripheral Bus Scaling mode: peripherals are clocked at programmable fraction of the CPU clock (SYSCLK).

#### 25.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- Posc Idle Mode: the system clock is derived from the Posc. The system clock source continues to operate.

- Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle Mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle Mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle Mode: the system clock is derived from the LPRC.

- Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep Mode: the CPU, the system clock source, and any peripherals that operate from the system clock source, are halted.

- Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

#### 25.3 Power-Saving Operation

The purpose of all power-saving is to reduce power consumption by reducing the device clock frequency. To achieve this, low-frequency clock sources can be selected. In addition, the peripherals and CPU can be halted or disabled to further reduce power consumption.

#### 25.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device Power-Saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep mode.

Sleep mode includes the following characteristics:

- · The CPU is halted.

- The system clock source is typically shut down.

See Section 25.3.2 "Idle Mode" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit, if enabled, remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator, e.g., RTCC and Timer 1.

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to Section 11.0 "USB On-The-Go (OTG)" for specific details.

- Some modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.

#### REGISTER 26-6: DDPCON: DEBUG DATA PORT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-x               | r-x               | r-x               | r-x               | r-x               | r-x               | r-x              | r-x              |

| 31:24        |                   | _                 |                   | _                 | -                 | -                 | _                | _                |

| 22.40        | r-x               | r-x               | r-x               | r-x               | r-x               | r-x               | r-x              | r-x              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | r-x               | r-x               | r-x               | r-x               | r-x               | r-x               | r-x              | r-x              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-0             | r-x              | r-x              |

| 7:0          | DDPUSB            | DDPU1             | DDPU2             | DDPSPI1           | JTAGEN            | TROEN             | _                | _                |

Legend:

R = Readable bit W = Writable bit P = Programmable bit r = Reserved bit

U = Unimplemented bit -n = Bit Value at POR: ('0', '1', x = Unknown)

bit 31-8 Reserved: Write '0'; ignore read

bit 7 DDPUSB: Debug Data Port Enable for USB bit

1 = USB peripheral ignores USBFRZ (U1CNFG1<5>) setting

0 = USB peripheral follows USBFRZ setting

bit 6 DDPU1: Debug Data Port Enable for UART1 bit

1 = UART1 peripheral ignores FRZ (U1MODE<14>) setting

0 = UART1 peripheral follows FRZ setting

bit 5 DDPU2: Debug Data Port Enable for UART2 bit

1 = UART2 peripheral ignores FRZ (U2MODE<14>) setting

0 = UART2 peripheral follows FRZ setting

bit 4 DDPSPI1: Debug Data Port Enable for SPI1 bit

1 = SPI1 peripheral ignores FRZ (SPI1CON<14>) setting

0 = SPI1 peripheral follows FRZ setting

bit 3 JTAGEN: JTAG Port Enable bit

1 = Enable JTAG Port

0 = Disable JTAG Port

bit 2 TROEN: Trace Output Enable bit

1 = Enable Trace Port

0 = Disable Trace Port

bit 1-0 Reserved: Write '1'; ignore read

#### 27.0 INSTRUCTION SET

The PIC32MX3XX/4XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. PIC32MX does not support the following features:

- · CoreExtend instructions

- · Coprocessor 1 instructions

- · Coprocessor 2 instructions

Table 27-1 provides a summary of the instructions that are implemented by the PIC32MX3XX/4XX family core.

Note: Refer to "MIPS32® Architecture for Programmers Volume II: The MIPS32® Instruction Set" at www.mips.com for more information.

## TABLE 27-1: MIPS32® INSTRUCTION SET

| Instruction | Description                                                            | Function                                                                                    |

|-------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| ADD         | Integer Add                                                            | Rd = Rs + Rt                                                                                |

| ADDI        | Integer Add Immediate                                                  | Rt = Rs + Immed                                                                             |

| ADDIU       | Unsigned Integer Add Immediate                                         | $Rt = Rs +_{U} Immed$                                                                       |

| ADDU        | Unsigned Integer Add                                                   | Rd = Rs + <sub>U</sub> Rt                                                                   |

| AND         | Logical AND                                                            | Rd = Rs & Rt                                                                                |

| ANDI        | Logical AND Immediate                                                  | $Rt = Rs \& (0_{16} \mid   Immed)$                                                          |

| В           | Unconditional Branch (Assembler idiom for: BEQ r0, r0, offset)         | PC += (int)offset                                                                           |

| BAL         | Branch and Link<br>(Assembler idiom for: BGEZAL r0, offset)            | <pre>GPR[31] = PC + 8 PC += (int)offset</pre>                                               |

| BEQ         | Branch on Equal                                                        | <pre>if Rs == Rt   PC += (int)offset</pre>                                                  |

| BEQL        | Branch on Equal Likely <sup>(1)</sup>                                  | <pre>if Rs == Rt   PC += (int)offset else   Ignore Next Instruction</pre>                   |

| BGEZ        | Branch on Greater Than or Equal to Zero                                | <pre>if !Rs[31]   PC += (int)offset</pre>                                                   |

| BGEZAL      | Branch on Greater Than or Equal to Zero and Link                       | <pre>GPR[31] = PC + 8 if !Rs[31]    PC += (int)offset</pre>                                 |

| BGEZALL     | Branch on Greater Than or Equal to Zero and Link Likely <sup>(1)</sup> | <pre>GPR[31] = PC + 8 if !Rs[31]   PC += (int)offset else   Ignore Next Instruction</pre>   |

| BGEZL       | Branch on Greater Than or Equal to Zero Likely <sup>(1)</sup>          | <pre>if !Rs[31]   PC += (int)offset else   Ignore Next Instruction</pre>                    |

| BGTZ        | Branch on Greater Than Zero                                            | <pre>if !Rs[31] &amp;&amp; Rs != 0   PC += (int)offset</pre>                                |

| BGTZL       | Branch on Greater Than Zero Likely <sup>(1)</sup>                      | <pre>if !Rs[31] &amp;&amp; Rs != 0   PC += (int)offset else   Ignore Next Instruction</pre> |

| BLEZ        | Branch on Less Than or Equal to Zero                                   | if Rs[31]    Rs == 0<br>PC += (int)offset                                                   |

Note 1: This instruction is deprecated and should not be used.

NOTES:

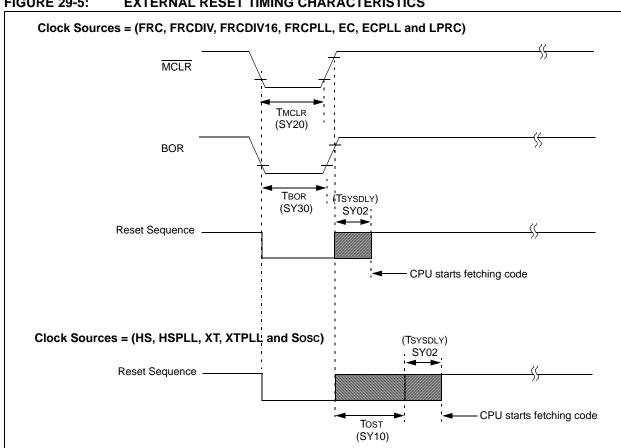

**FIGURE 29-5: EXTERNAL RESET TIMING CHARACTERISTICS**

**TABLE 29-22: RESETS TIMING**

| AC CHA        | ARACTER | ISTICS                                                                                                                         | Standard Operating Conditions: 2.3V to 3.6V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+105°C for V-Temp |                                 |      |       |                |  |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|-------|----------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                                                                                 | Min.                                                                                                                                                       | Typical <sup>(2)</sup>          | Max. | Units | Conditions     |  |  |  |  |

| SY00          | Tpu     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                          |                                                                                                                                                            | 400                             | 600  | μs    | -40°C to +85°C |  |  |  |  |

| SY01          | TPWRT   | Power-up Period External Vcore Applied (Power-Up-Timer Active)                                                                 | 48                                                                                                                                                         | 64                              | 80   | ms    | -40°C to +85°C |  |  |  |  |

| SY02          | TSYSDLY | System Delay Period: Time required to reload Device Configuration Fuses plus SYSCLK delay before first instruction is fetched. |                                                                                                                                                            | 1 μs<br>+<br>8 sysclκ<br>cycles | _    | 1     | -40°C to +85°C |  |  |  |  |

| SY20          | TMCLR   | MCLR Pulse Width (low)                                                                                                         | _                                                                                                                                                          | 2                               | _    | μs    | -40°C to +85°C |  |  |  |  |

| SY30          | TBOR    | BOR Pulse Width (low)                                                                                                          |                                                                                                                                                            | 1                               | _    | μs    | -40°C to +85°C |  |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

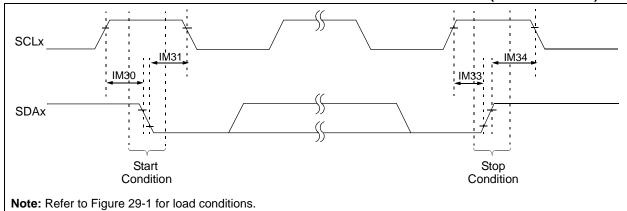

#### FIGURE 29-14: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

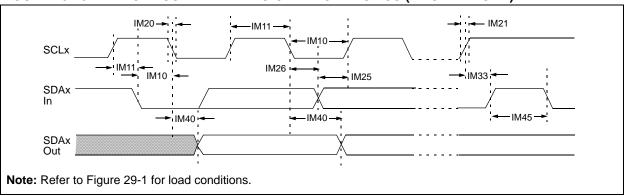

### FIGURE 29-15: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

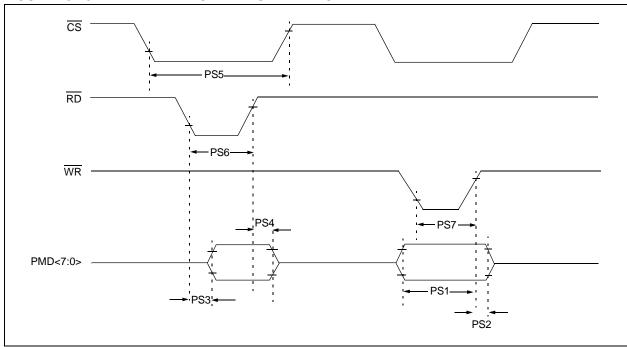

FIGURE 29-20: PARALLEL SLAVE PORT TIMING

TABLE 29-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CHA        | ARACTERIS | STICS                                                 | Standard Operating Conditions: 2.3V to 3.6V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+105°C for V-Temp |         |      |       |            |  |  |  |

|---------------|-----------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol    | Characteristics <sup>(1)</sup>                        | Min.                                                                                                                                                       | Typical | Max. | Units | Conditions |  |  |  |

| PS1           | TdtV2wrH  | Data In Valid before WR or CS Inactive (setup time)   | 20                                                                                                                                                         | _       | _    | ns    | _          |  |  |  |

| PS2           | TwrH2dtl  | WR or CS Inactive to Data –<br>In Invalid (hold time) | 40                                                                                                                                                         |         | _    | ns    | _          |  |  |  |

| PS3           | TrdL2dtV  | RD and CS Active to Data –<br>Out Valid               | _                                                                                                                                                          |         | 60   | ns    | _          |  |  |  |

| PS4           | TrdH2dtI  | RD Active or CS Inactive to Data – Out Invalid        | 0                                                                                                                                                          |         | 10   | ns    | _          |  |  |  |

| PS5           | Tcs       | CS Active Time                                        | Трв + 40                                                                                                                                                   | _       |      | ns    | _          |  |  |  |

| PS6           | Twr       | WR Active Time                                        | TpB + 25                                                                                                                                                   |         | _    | ns    |            |  |  |  |

| PS7           | TRD       | RD Active Time                                        | TpB + 25                                                                                                                                                   |         | 1    | ns    | _          |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

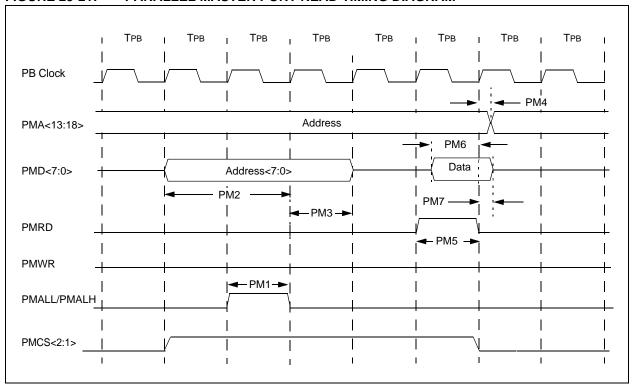

FIGURE 29-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

TABLE 29-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                   | Standard Operating Conditions: 2.3V to 3.6V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+105°C for V-Temp |         |      |       |            |

|--------------------|---------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                    | Min.                                                                                                                                                       | Typical | Max. | Units | Conditions |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                           | _                                                                                                                                                          | 1 Трв   | _    | _     | _          |

| PM2                | TADSU   | Address Out Valid to PMALL/PMALH Invalid (address setup time)     | _                                                                                                                                                          | 2 Трв   | _    | _     | _          |

| РМ3                | TADHOLD | PMALL/PMALH Invalid to Address<br>Out Invalid (address hold time) |                                                                                                                                                            | 1 Трв   | l    |       |            |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)    | 5                                                                                                                                                          |         | _    | ns    |            |

| PM5                | TRD     | PMRD Pulse Width                                                  | _                                                                                                                                                          | 1 Трв   | _    | _     | _          |

| PM6                | TDSU    | PMRD or PMENB Active to Data In Valid (data setup time)           | 15                                                                                                                                                         | _       | _    | ns    | _          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)        | _                                                                                                                                                          | 80      | _    | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### 30.2 Package Details

The following sections give the technical details of the packages.

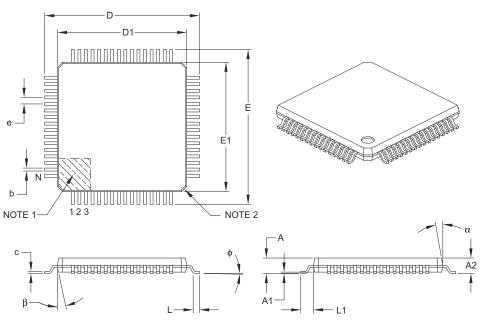

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS   |           |      |      |  |

|--------------------------|---------------|-----------|------|------|--|

| Dim                      | ension Limits | MIN       | NOM  | MAX  |  |

| Number of Leads          | N             | 64        |      |      |  |

| Lead Pitch               | е             | 0.50 BSC  |      |      |  |

| Overall Height           | А             | -         | _    | 1.20 |  |

| Molded Package Thickness | A2            | 0.95      | 1.00 | 1.05 |  |

| Standoff                 | A1            | 0.05      | _    | 0.15 |  |

| Foot Length              | L             | 0.45      | 0.60 | 0.75 |  |

| Footprint                | L1            | 1.00 REF  |      |      |  |

| Foot Angle               | ф             | 0°        | 3.5° | 7°   |  |

| Overall Width            | E             | 12.00 BSC |      |      |  |

| Overall Length           | D             | 12.00 BSC |      |      |  |

| Molded Package Width     | E1            | 10.00 BSC |      |      |  |

| Molded Package Length    | D1            | 10.00 BSC |      |      |  |

| Lead Thickness           | С             | 0.09      | _    | 0.20 |  |

| Lead Width               | b             | 0.17      | 0.22 | 0.27 |  |

| Mold Draft Angle Top     | α             | 11°       | 12°  | 13°  |  |

| Mold Draft Angle Bottom  | β             | 11°       | 12°  | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

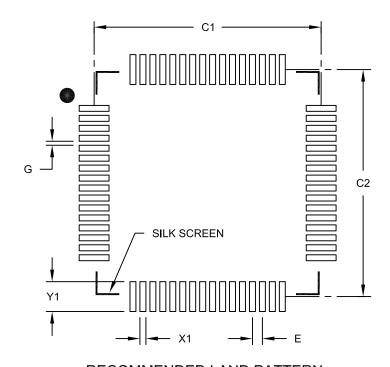

## 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units |          |       | MILLIMETERS |  |  |  |

|--------------------------|-------|----------|-------|-------------|--|--|--|

| Dimension Limits         |       | MIN      | NOM   | MAX         |  |  |  |

| Contact Pitch            | Е     | 0.50 BSC |       |             |  |  |  |

| Contact Pad Spacing      | C1    |          | 11.40 |             |  |  |  |

| Contact Pad Spacing      | C2    |          | 11.40 |             |  |  |  |

| Contact Pad Width (X64)  | X1    |          |       | 0.30        |  |  |  |

| Contact Pad Length (X64) | Y1    |          |       | 1.50        |  |  |  |

| Distance Between Pads    | G     | 0.20     |       |             |  |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

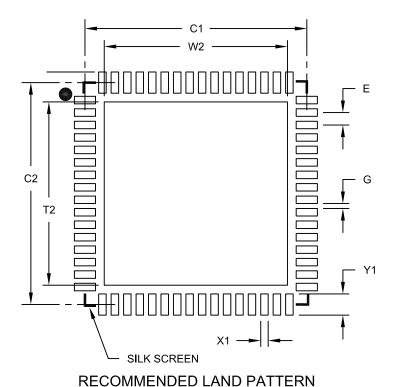

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | Е           | 0.50 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 7.35 |

| Optional Center Pad Length | T2          |          |      | 7.35 |

| Contact Pad Spacing        | C1          |          | 8.90 |      |

| Contact Pad Spacing        | C2          |          | 8.90 |      |

| Contact Pad Width (X64)    | X1          |          |      | 0.30 |

| Contact Pad Length (X64)   | Y1          |          |      | 0.85 |

| Distance Between Pads      | G           | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2149A