Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

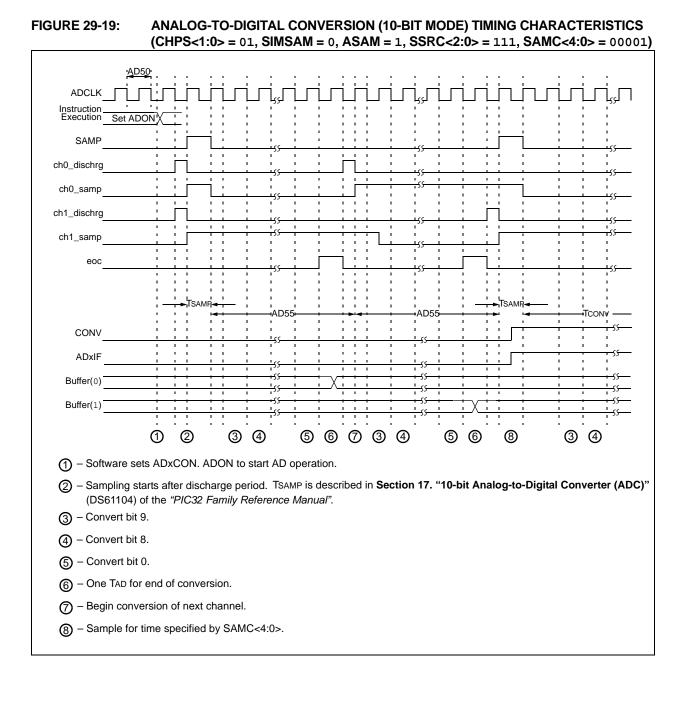

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx440f128ht-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1:PIC32MX GENERAL PURPOSE – FEATURES

|                 | GENERAL PURPOSE |                         |     |                         |                  |                        |                              |      |       |                             |                 |             |         |      |

|-----------------|-----------------|-------------------------|-----|-------------------------|------------------|------------------------|------------------------------|------|-------|-----------------------------|-----------------|-------------|---------|------|

| Device          | Pins            | Packages <sup>(2)</sup> | ZHW | Program Memory (KB)     | Data Memory (KB) | Timers/Capture/Compare | Programmable DMA<br>Channels | VREG | Trace | EUART/SPI/I <sup>2</sup> C™ | 10-bit ADC (ch) | Comparators | dSd/dWd | JTAG |

| PIC32MX320F032H | 64              | PT, MR                  | 40  | 32 + 12 <sup>(1)</sup>  | 8                | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX320F064H | 64              | PT, MR                  | 80  | 64 + 12 <sup>(1)</sup>  | 16               | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX320F128H | 64              | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 16               | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX340F128H | 64              | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX340F256H | 64              | PT, MR                  | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX340F512H | 64              | PT, MR                  | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX320F128L | 100<br>121      | PT<br>BG                | 80  | 128 + 12 <sup>(1)</sup> | 16               | 5/5/5                  | 0                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100             | PT                      | 00  | 400 + 40(1)             | 20               | _ /_ /_                | 4                            | Vee  | Nia   | 0/0/0                       | 40              | 0           | Vee     | Vee  |

| PIC32MX340F128L | 121             | BG                      | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100             | PT                      |     | 0.50 (0(1)              |                  |                        |                              |      |       | 0/0/5                       |                 |             |         |      |

| PIC32MX360F256L | 121             | BG                      | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100             | PT                      |     | 540 40(1)               |                  | - (- (-                |                              |      |       | 0/0/5                       |                 |             |         |      |

| PIC32MX360F512L | 121             | BG                      | 80  | $512 + 12^{(1)}$        | 32               | 5/5/5                  | 4                            | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

Legend: PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB Boot Flash memory.

2: See Legend for an explanation of the acronyms. See Section 30.0 "Packaging Information" for details.

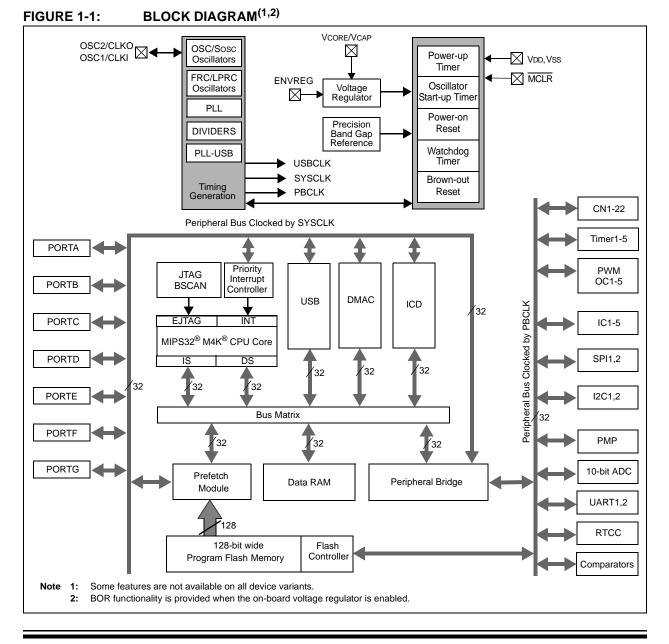

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the PIC32MX3XX/4XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX3XX/4XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| Register<br>Number | -                       | Function                                |

|--------------------|-------------------------|-----------------------------------------|

| 17-22              | Reserved                | Reserved                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception |

| 25-29              | Reserved                | Reserved                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register       |

#### TABLE 3-2:COPROCESSOR 0 REGISTERS (CONTINUED)

Note 1: Registers used in exception processing.

2: Registers used during debug.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 shows the exception types in order of priority.

### TABLE 3-3: PIC32MX3XX/4XX FAMILY CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR)                                                                                                |

| DSS       | EJTAG Debug Single Step                                                                                                                 |

| DINT      | EJTAG Debug Interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input, or by setting the EjtagBrk bit in the ECR register |

| NMI       | Assertion of NMI signal                                                                                                                 |

| Interrupt | Assertion of unmasked hardware or software interrupt signal                                                                             |

| DIB       | EJTAG debug hardware instruction break matched                                                                                          |

| AdEL      | Fetch address alignment error<br>Fetch reference to protected address                                                                   |

| IBE       | Instruction fetch bus error                                                                                                             |

| DBp       | EJTAG Breakpoint (execution of SDBBP instruction)                                                                                       |

| Sys       | Execution of SYSCALL instruction                                                                                                        |

| Вр        | Execution of BREAK instruction                                                                                                          |

| RI        | Execution of a Reserved Instruction                                                                                                     |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled                                                            |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled                                                                      |

| Ov        | Execution of an arithmetic instruction that overflowed                                                                                  |

| Tr        | Execution of a trap (when trap condition is true)                                                                                       |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG Data Value Break on Store (address + value)                                            |

| AdEL      | Load address alignment error<br>Load reference to protected address                                                                     |

| AdES      | Store address alignment error<br>Store to protected address                                                                             |

| DBE       | Load or store bus error                                                                                                                 |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare                                                                             |

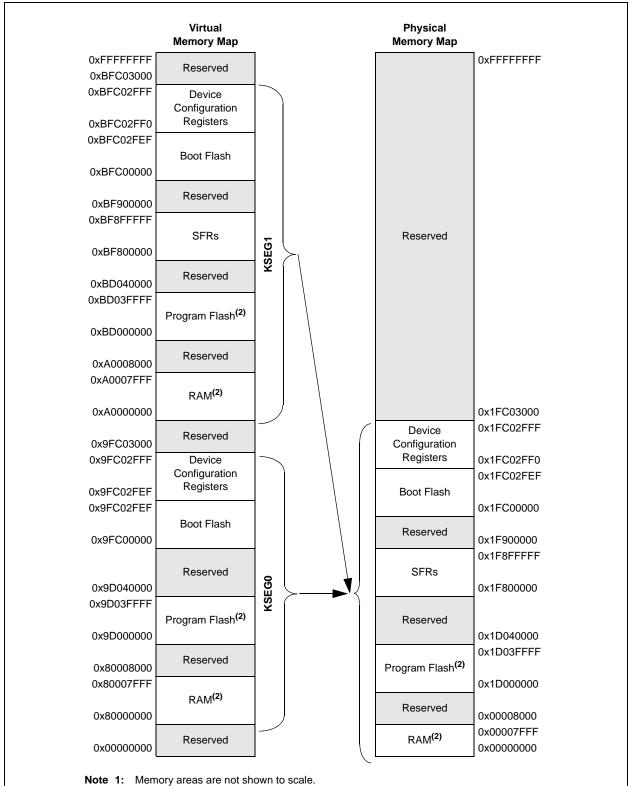

#### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX340F256H, PIC32MX360F256L, PIC32MX440F256H AND PIC32MX460F256L DEVICES<sup>(1)</sup>

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| SS                          |                        |               |                   |                  |                   |                |                            |                |                 | В                | its           |                |                |                         |                          |                         |                |                 |            |

|-----------------------------|------------------------|---------------|-------------------|------------------|-------------------|----------------|----------------------------|----------------|-----------------|------------------|---------------|----------------|----------------|-------------------------|--------------------------|-------------------------|----------------|-----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15             | 30/14            | 29/13             | 28/12          | 27/11                      | 26/10          | 25/9            | 24/8             | 23/7          | 22/6           | 21/5           | 20/4                    | 19/3                     | 18/2                    | 17/1           | 16/0            | All Resets |

| 1000                        | INTCON                 | 31:16         | —                 | —                | —                 | —              | -                          | —              | -               | —                | —             | —              | _              | -                       | -                        | -                       | -              | SS0             | 000        |

|                             |                        | 15:0<br>31:16 | _                 | _                |                   | MVEC           |                            | _              | TPC<2:0>        | _                |               | _              | _              | INT4EP                  | INT3EP                   | INT2EP                  | INT1EP         | INT0EP          | 000        |

| 1010                        | INTSTAT <sup>(2)</sup> | 15:0          | _                 | _                | _                 |                |                            |                |                 |                  |               |                | _              | _                       | 000                      |                         |                |                 |            |

| 1020                        | IPTMR                  | 31:16<br>15:0 |                   |                  |                   |                |                            |                |                 |                  | R<31:0>       |                |                |                         |                          |                         |                |                 | 000        |

| 1030                        | IFS0                   | 31:16<br>15:0 | I2C1MIF<br>INT3IF | I2C1SIF<br>OC3IF | I2C1BIF<br>IC3IF  | U1TXIF<br>T3IF | U1RXIF<br>INT2IF           | U1EIF<br>OC2IF | –<br>IC2IF      | —<br>T2IF        | —<br>INT1IF   | OC5IF<br>OC1IF | IC5IF<br>IC1IF | T5IF<br>T1IF            | INT4IF                   | OC4IF<br>CS1IF          | IC4IF<br>CS0IF | T4IF<br>CTIF    | 000        |

| 1040                        | IFS1                   | 31:16<br>15:0 | - RTCCIF          | -<br>FSCMIF      | –<br>I2C2MIF      | –<br>I2C2SIF   | –<br>I2C2BIF               | U2TXIF         | USBIF<br>U2RXIF | FCEIF<br>U2EIF   | —<br>SPI2RXIF | —<br>SPI2TXIF  | —<br>SPI2EIF   | —<br>CMP2IF             | —<br>CMP1IF              | –<br>PMPIF              | AD1IF          | —<br>CNIF       | 000        |

| 1060                        | IEC0                   | 31:16         | I2C1MIE           | I2C1SIE          | I2C1BIE           | U1TXIE         | U1RXIE                     | U1EIE          | _               | _                | —             | OC5IE          | IC5IE          | T5IE                    | INT4IE                   | OC4IE                   | IC4IE          | T4IE            | 000        |

| 1070                        | IEC1                   | 15:0<br>31:16 | INT3IE<br>—       | OC3IE            | IC3IE             | T3IE           | INT2IE                     | OC2IE          | IC2IE<br>USBIE  | T2IE<br>FCEIE    | INT1IE        | OC1IE          | IC1IE          | T1IE                    |                          | CS1IE                   | CS0IE          | CTIE            | 000        |

|                             | 0.                     | 15:0          | RTCCIE            | FSCMIE           | I2C2MIE           | I2C2SIE        | I2C2BIE                    | U2TXIE         | U2RXIE          | U2EIE            | SPI2RXIE      | SPI2TXIE       | SPI2EIE        | CMP2IE                  | CMP1IE                   | PMPIE                   | AD1IE          | CNIE            | 000        |

| 1090                        | IPC0                   | 31:16<br>15:0 | _                 |                  |                   |                | INT0IP<2:0><br>CS0IP<2:0>  |                |                 | S<1:0><br>S<1:0> |               |                | _              | CS1IP<2:0><br>CTIP<2:0> |                          | CS1IS<1:0><br>CTIS<1:0> |                | 000             |            |

|                             |                        | 31:16         | _                 |                  | _                 |                | INT1IP<2:0>                |                |                 | S<1:0>           |               | _              |                | OC1IP<2:0>              |                          | OC1IS<1:0>              |                | 000             |            |

| 10A0                        | IPC1                   | 15:0          | _                 | _                | _                 |                | IC1IP<2:0>                 |                |                 | <1:0>            | _             | _              | _              | T1IP<2:0>               |                          | T1IS<1:0>               |                | 000             |            |

| 10B0                        | IPC2                   | 31:16<br>15:0 | _                 | _                | -                 |                | INT2IP<2:0><br>IC2IP<2:0>  | •              |                 | S<1:0><br>i<1:0> | _             | _              | -              | OC2IP<2:0><br>T2IP<2:0> |                          |                         | OC2IS<br>T2IS  |                 | 000        |

|                             |                        | 31:16         | _                 |                  | _                 |                | INT3IP<2:0>                | ,              |                 | S<1:0>           |               |                |                |                         | OC3IP<2:0>               |                         | OC315          |                 | 000        |

| 10C0                        | IPC3                   | 15:0          | _                 | _                | _                 |                | IC3IP<2:0>                 |                |                 | <1:0>            | _             | _              | _              | T3IP<2:0>               |                          |                         | T3IS-          |                 | 000        |

| 10D0                        | IPC4                   | 31:16         | _                 | _                | _                 |                | INT4IP<2:0>                | •              | INT4IS          | S<1:0>           | -             | _              | _              |                         | OC4IP<2:0>               |                         | OC4IS          | S<1:0>          | 000        |

| TODO                        | IPC4                   | 15:0          | _                 | _                | _                 |                | IC4IP<2:0>                 |                | IC4IS           | i<1:0>           | _             | _              | _              |                         | T4IP<2:0>                |                         | T4IS-          |                 | 000        |

| 10E0                        | IPC5                   | 31:16         | -                 | —                | —                 |                | —                          | —              | -               | —                | -             | —              | -              | OC5IP<2:0>              |                          |                         | OC5IS          |                 | 000        |

|                             |                        | 15:0          | _                 | —                | —                 |                | IC5IP<2:0>                 |                |                 | <1:0>            | —             | —              | —              |                         | T5IP<2:0>                |                         | T5IS-          |                 | 000        |

| 10F0                        | IPC6                   | 31:16         | -                 | _                | _                 |                | AD1IP<2:0>                 |                |                 | S<1:0>           |               |                |                |                         | CNIP<2:0>                |                         |                | <1:0>           | 000        |

|                             |                        | 15:0<br>31:16 | _                 |                  |                   |                | I2C1IP<2:0><br>SPI2IP<2:0> |                |                 | S<1:0><br>S<1:0> |               |                | _              |                         | U1IP<2:0><br>CMP2IP<2:0: |                         | U1IS           | <1:0><br>S<1:0> | 000        |

| 1100                        | IPC7                   | 15:0          | _                 |                  |                   |                | SPIZIP<2:0><br>CMP1IP<2:0: |                |                 | S<1:0><br>S<1:0> |               | _              |                |                         | PMPIP<2:03               | 2                       | PMPIS          |                 | 000        |

|                             |                        | 31:16         | _                 |                  |                   |                | RTCCIP<2:0:                |                |                 | S<1:0>           | _             | _              |                | FSCMIP<2:0>             |                          |                         | S<1:0>         | 000             |            |

| 1110                        | IPC8                   | 15:0          | _                 |                  | _                 |                | 12C2IP<2:0>                |                |                 | S<1:0>           | _             | _              | _              |                         | U2IP<2:0>                |                         |                | <1:0>           | 000        |

| 1140                        | IPC11                  | 31:16         | _                 | —                | —                 | —              |                            | —              | -               | —                | —             | —              | —              | —                       | —                        | _                       | —              |                 | 000        |

| Legen                       |                        | 15:0          | —                 | —                | —<br>Inimplemente |                | USBIP<2:0>                 |                |                 | S<1:0>           | -             | —              | -              |                         | FCEIP<2:0>               |                         | FCEIS          | 6<1:0>          | 0000       |

#### INTERRUPT REGISTERS MAP FOR THE PIC32MY420E032H DEVICE ONI V(1) TADIE 1.6.

© 2011 Microchip Technology Inc.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

PIC32MX3XX/4XX

This register does not have associated CLR, SET, and INV registers. 2:

NOTES:

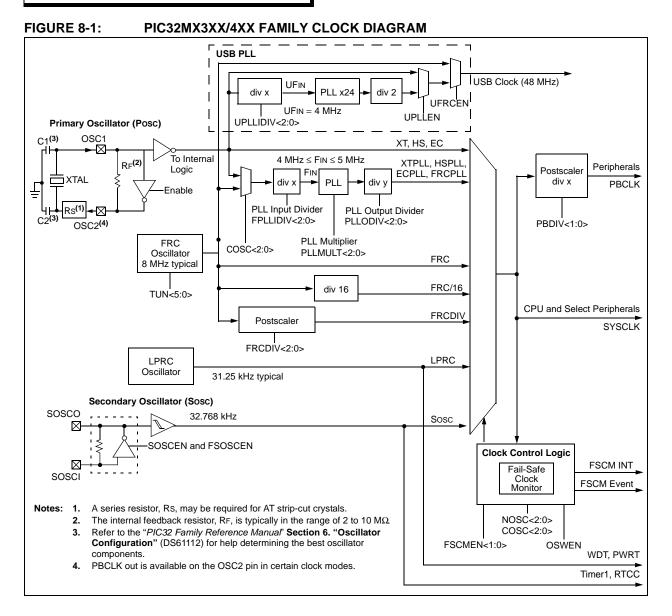

## 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"* Section 6. *"Oscillator Configuration"* (DS61112), which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC32MX oscillator system has the following modules and features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL (phase-locked loop) with userselectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shut down

- Dedicated on-chip PLL for USB peripheral

NOTES:

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset.

- On a WDT time-out. See Section 26.2 "Watchdog Timer (WDT)".

If the interrupt priority is lower than or equal to current priority, the CPU will remain halted, but the PBCLK will start running and the device will enter into Idle mode.

Note: There is no FRZ mode for this module.

### 25.3.2 IDLE MODE

In the Idle mode, the CPU is halted but the System clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is halted. Peripherals can be individually configured to halt when entering Idle by setting their respective SIDL bit. Latency when exiting Idle mode is very low due to the CPU oscillator source remaining active.

PBCLK divider Note: Changing the ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in PB divisor ratio. Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to

> LPRC just prior to entering Sleep in order to save power. No oscillator start-up delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator startup/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of CPU. If the priority of the interrupt event is lower than or equal to current priority of CPU, the CPU will remain halted and the device will remain in Idle mode.

- On any source of device Reset.

- On a WDT time-out interrupt. See Section 26.2 "Watchdog Timer (WDT)".

#### 25.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK-to-PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as USB, Interrupt Controller, DMA, Bus Matrix and Prefetch Cache are clocked directly from SYSCLK, as a result, they are not affected by PBCLK divisor changes

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements such as baud rate accuracy should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

#### REGISTER 26-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |  |

| 31:24        | _                 | _                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 00.40        | R/P               | r-1               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 23:16        | FWDTEN            | _                 | _                 | WDTPS<4:0>        |                   |                   |                  |                  |  |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |  |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDIV<1:0>       |                   | —                 | OSCIOFNC          | POSCMOD<1:0>     |                  |  |  |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |  |

| 7:0          | IESO              | _                 | FSOSCEN           |                   |                   |                   | FNOSC<2:0>       |                  |  |  |  |

#### Legend:

R = Readable bit

W = Writable bit P = Programmable bit

r = Reserved bit

U = Unimplemented bit -n = Bit Value at POR: ('0', '1', x = Unknown)

bit 31-24 Reserved: Write '1'

bit 23 **FWDTEN:** Watchdog Timer Enable bit

1 = The WDT is enabled and cannot be disabled by software

0 = The WDT is not enabled; it can be enabled in software

- bit 22-21 Reserved: Write '1'

- bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 | = | 1:1048576 |

|-------|---|-----------|

| 10011 | = | 1:524288  |

| 10010 | = | 1:262144  |

| 10001 | = | 1:131072  |

| 10000 | = | 1:65536   |

| 01111 | = | 1:32768   |

| 01110 | = | 1:16384   |

| 01101 | = | 1:8192    |

| 01100 | = | 1:4096    |

| 01011 | = | 1:2048    |

| 01010 | = | 1:1024    |

| 01001 | = | 1:512     |

| 01000 | = | 1:256     |

| 00111 | = | 1:128     |

| 00110 | = | 1:64      |

| 00101 | = | 1:32      |

| 00100 | = | 1:16      |

| 00011 | = | 1:8       |

| 00010 | = | 1:4       |

| 00001 | = | 1:2       |

| 00000 | _ | 1.1       |

00000 = 1:1

All other combinations not shown result in operation = '10100'

bit 15-14 **FCKSM<1:0>:** Clock Switching and Monitor Selection Configuration bits 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 =Clock switching is enabled, Fail-Safe Clock Monitor is enabled

**Note 1:** Do not disable Posc (POSCMOD = 00) when using this oscillator source.

### REGISTER 26-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output signal active on the OSCO pin; primary oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 OR 00)

- 0 = CLKO output disabled

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary oscillator disabled

- 10 = HS oscillator mode selected

- 01 = XT oscillator mode selected

- 00 = External clock mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode enabled (Two-Speed Start-up enabled)

- 0 = Internal External Switchover mode disabled (Two-Speed Start-up disabled)

- bit 6 Reserved: Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable Posc (POSCMOD = 00) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |

| 31:24        | _                 | —                 | _                 |                   | —                 | —                 | —                | —                |  |  |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |

| 23:16        | _                 | —                 | —                 | —                 | —                 | FF                | )>               |                  |  |  |

| 45.0         | R/P               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |

| 15:8         | UPLLEN            | —                 | —                 | —                 | —                 | U                 | UPLLIDIV<2:0>    |                  |  |  |

| 7.0          | r-1               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |  |

| 7:0          | _                 | F                 | PLLMUL<2:0        | >                 | _                 | FPLLIDIV<2:0>     |                  |                  |  |  |

#### REGISTER 26-3: DEVCFG2: DEVICE CONFIGURATION WORD 2

#### Legend:

R = Readable bitW = Writable bitP = Programmable bitr = Reserved bitU = Unimplemented bit-n = Bit Value at POR: ('0', '1', x = Unknown)

#### bit 18-16 FPLLODIV<2:0>: Default Postscaler for PLL bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1

- bit 15 UPLLEN: USB PLL Enable bit 1 = Disable and bypass USB PLL 0 = Enable USB PLL

- bit 14-11 **Reserved:** Write '1'

- bit 10-8 UPLLIDIV<2:0>: PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

- bit 7 Reserved: Write '1'

#### bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

- 111 = 24x multiplier 110 = 21x multiplier 101 = 20x multiplier 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier

- 000 = 15x multiplier

- bit 3 Reserved: Write '1'

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider011 = 4x divider

- 011 = 4x divider 010 = 3x divider

- 010 = 3x divider001 = 2x divider

- 001 = 2x divider 000 = 1x divider

bit 31-19 Reserved: Write '1'

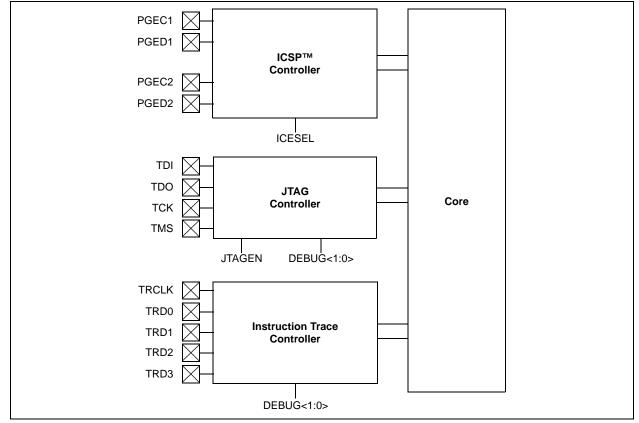

## 26.4 Programming and Diagnostics

PIC32MX3XX/4XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32MX devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

### FIGURE 26-3: BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

| TABLE 27-1: | MIPS32 <sup>®</sup> INSTRUCTION SET (CONTINUE | ED)                                                                                            |  |  |  |  |  |

|-------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Instruction | Description                                   | Function                                                                                       |  |  |  |  |  |

| RDPGPR      | Read GPR from Previous Shadow Set             | Rt = SGPR[SRSCtl <sub>PSS</sub> , Rd]                                                          |  |  |  |  |  |

| ROTR        | Rotate Word Right                             | $Rd = Rt_{sa-10}    Rt_{31sa}$                                                                 |  |  |  |  |  |

| ROTRV       | Rotate Word Right Variable                    | $Rd = Rt_{Rs-10}    Rt_{31Rs}$                                                                 |  |  |  |  |  |

| SB          | Store Byte                                    | (byte)Mem[Rs+offset] = Rt                                                                      |  |  |  |  |  |

| SC          | Store Conditional Word                        | <pre>if LL<sub>bit</sub> = 1     mem[Rs+offset&gt; = Rt     Rt = LL<sub>bit</sub></pre>        |  |  |  |  |  |

| SDBBP       | Software Debug Break Point                    | Trap to SW Debug Handler                                                                       |  |  |  |  |  |

| SEB         | Sign-Extend Byte                              | Rd = SignExtend (Rs-70)                                                                        |  |  |  |  |  |

| SEH         | Sign-Extend Half                              | Rd = SignExtend (Rs-150)                                                                       |  |  |  |  |  |

| SH          | Store Half                                    | (half)Mem[Rs+offset> = Rt                                                                      |  |  |  |  |  |

| SLL         | Shift Left Logical                            | Rd = Rt << sa                                                                                  |  |  |  |  |  |

| SLLV        | Shift Left Logical Variable                   | Rd = Rt << Rs[4:0]                                                                             |  |  |  |  |  |

| SLT         | Set on Less Than                              | <pre>if (int)Rs &lt; (int)Rt   Rd = 1 else   Rd = 0</pre>                                      |  |  |  |  |  |

| SLTI        | Set on Less Than Immediate                    | <pre>if (int)Rs &lt; (int)Immed   Rt = 1 else   Rt = 0</pre>                                   |  |  |  |  |  |

| SLTIU       | Set on Less Than Immediate Unsigned           | <pre>if (uns)Rs &lt; (uns)Immed     Rt = 1 else     Rt = 0</pre>                               |  |  |  |  |  |

| SLTU        | Set on Less Than Unsigned                     | <pre>if (uns)Rs &lt; (uns)Immed   Rd = 1 else   Rd = 0</pre>                                   |  |  |  |  |  |

| SRA         | Shift Right Arithmetic                        | Rd = (int)Rt >> sa                                                                             |  |  |  |  |  |

| SRAV        | Shift Right Arithmetic Variable               | Rd = (int)Rt >> Rs[4:0]                                                                        |  |  |  |  |  |

| SRL         | Shift Right Logical                           | Rd = (uns)Rt >> sa                                                                             |  |  |  |  |  |

| SRLV        | Shift Right Logical Variable                  | Rd = (uns)Rt >> Rs[4:0]                                                                        |  |  |  |  |  |

| SSNOP       | Superscalar Inhibit No Operation              | NOP                                                                                            |  |  |  |  |  |

| SUB         | Integer Subtract                              | Rt = (int)Rs - (int)Rd                                                                         |  |  |  |  |  |

| SUBU        | Unsigned Subtract                             | Rt = (uns)Rs - (uns)Rd                                                                         |  |  |  |  |  |

| SW          | Store Word                                    | Mem[Rs+offset] = Rt                                                                            |  |  |  |  |  |

|             | Store Word Left                               | Mem[Rs+offset] = Rt                                                                            |  |  |  |  |  |

| SWL         | Store Word Right                              | Mem[Rs+ofIset] = Rt<br>Mem[Rs+offset] = Rt                                                     |  |  |  |  |  |

| SWR         | -                                             |                                                                                                |  |  |  |  |  |

| SYNC        | Synchronize                                   | Orders the cached coherent and<br>uncached loads and stores for access to<br>the shared memory |  |  |  |  |  |

| SYSCALL     | System Call                                   | SystemCallException                                                                            |  |  |  |  |  |

| TEQ         | Trap if Equal                                 | if Rs == Rt<br>TrapException                                                                   |  |  |  |  |  |

| TEQI        | Trap if Equal Immediate                       | if Rs == (int)Immed<br>TrapException                                                           |  |  |  |  |  |

## TABLE 27-1: MIPS32<sup>®</sup> INSTRUCTION SET (CONTINUED)

**Note 1:** This instruction is deprecated and should not be used.

## 28.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 28.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 29.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC32MX3XX/4XX electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX3XX/4XX are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings (Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C       |

|---------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                             | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                              | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V        |

| Voltage on VCORE with respect to VSS                                            | 0.3V to 2.0V         |

| Voltage on VBUS with respect to VSS                                             |                      |

| Maximum current out of Vss pin(s)                                               | 300 mA               |

| Maximum current into Vod pin(s) (Note 2)                                        | 300 mA               |

| Maximum output current sunk by any I/O pin                                      | 25 mA                |

| Maximum output current sourced by any I/O pin                                   | 25 mA                |

| Maximum current sunk by all ports                                               | 200 mA               |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA               |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 29-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

## TABLE 29-13: COMPARATOR SPECIFICATIONS

| DC CHA        | ARACTERI | STICS                                 | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |      |       |                                                                                         |  |  |

|---------------|----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol   | Characteristics                       | Min.                                                                                                                                                                                     | Typical | Max. | Units | Comments                                                                                |  |  |

| D300          | VIOFF    | Input Offset Voltage                  | -                                                                                                                                                                                        | ±7.5    | ±25  | mV    | AVdd = Vdd,<br>AVss = Vss                                                               |  |  |

| D301          | VICM     | Input Common Mode Voltage             | 0                                                                                                                                                                                        | —       | Vdd  | V     | AVDD = VDD,<br>AVSS = VSS<br>(Note 2)                                                   |  |  |

| D302          | CMRR     | Common Mode Rejection Ratio           | 55                                                                                                                                                                                       | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |  |

| D303          | TRESP    | Response Time                         | —                                                                                                                                                                                        | 150     | 400  | ns    | AVDD = VDD,<br>AVss = Vss<br>(Notes 1,2)                                                |  |  |

| D304          | ON2ov    | Comparator Enabled to Output<br>Valid | _                                                                                                                                                                                        | -       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit.<br>(Note 2) |  |  |

| D305          | IVREF    | Internal Voltage Reference            | 0.57                                                                                                                                                                                     | 0.6     | 0.63 | V     | —                                                                                       |  |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

### TABLE 29-14: VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        | RACTERIS | STICS                        | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |        |       |          |  |  |  |

|---------------|----------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-------|----------|--|--|--|

| Param.<br>No. | Symbol   | Characteristics              | Min.                                                                                                                                                                                     | Typical | Max.   | Units | Comments |  |  |  |

| D310          | VRES     | Resolution                   | Vdd/24                                                                                                                                                                                   | _       | VDD/32 | LSb   | —        |  |  |  |

| D311          | VRAA     | Absolute Accuracy            | —                                                                                                                                                                                        | _       | 1/2    | LSb   | —        |  |  |  |

| D312          | TSET     | Settling Time <sup>(1)</sup> | _                                                                                                                                                                                        |         | 10     | μs    | _        |  |  |  |

**Note 1:** Settling time measured while CVRR = 1 and CVR3:CVR0 transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

### TABLE 29-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 |      | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)       (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |      |       |                                                   |  |

|--------------------|--------|---------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min. | Typical                                                                                                                                                                                                                | Max. | Units | Comments                                          |  |

| D320               | VCORE  | Regulator Output Voltage        | 1.62 | 1.80                                                                                                                                                                                                                   | 1.98 | V     | _                                                 |  |

| D321               | CEFC   | External Filter Capacitor Value | 8    | 10                                                                                                                                                                                                                     | _    | μF    | Capacitor must be low series resistance (< 1 Ohm) |  |

| D322               | TPWRT  | Power-up Timer Period           |      | 64                                                                                                                                                                                                                     |      | ms    | ENVREG = 0                                        |  |

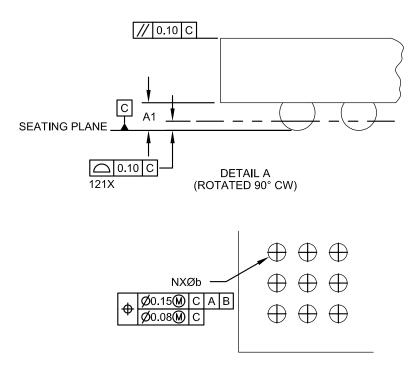

## 121-Lead Plastic Thin Profile Ball Grid Array (BG) - 10x10x1.10 mm Body [XBGA]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL B

|                          | MILLIMETERS |           |      |      |  |

|--------------------------|-------------|-----------|------|------|--|

| Dimensior                | MIN         | NOM       | MAX  |      |  |

| Number of Contacts       | N           | 121       |      |      |  |

| Contact Pitch            | e           | 0.80 BSC  |      |      |  |

| Overall Height           | A           | 1.00      | 1.10 | 1.20 |  |

| Standoff                 | A1          | 0.25      | 0.30 | 0.35 |  |

| Molded Package Thickness | A2          | 0.55      | 0.60 | 0.65 |  |

| Overall Width            | E           | 10.00 BSC |      |      |  |

| Array Width              | E1          | 8.00 BSC  |      |      |  |

| Overall Length           | D           | 10.00 BSC |      |      |  |

| Array Length             | D1          | 8.00 BSC  |      |      |  |

| Contact Diameter         | b           | 0.40 TYP  |      |      |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

3. The outer rows and colums of balls are located with respect to datums A and B.

Microchip Technology Drawing C04-148 Rev B Sheet 2 of 2

## TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                            | Update Description                                                                                                                                                                             |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "Special Features"         | Modified bit names and locations in <b>Register 26-5</b> " <b>DEVID: Device and Revision ID Register</b> ".                                                                                    |

|                                         | Replaced "TSTARTUP" with "TPU", and "64-ms nominal delay" with "TPWRT", in Section 26.3.1 "On-Chip Regulator and POR".                                                                         |

|                                         | The information that appeared in the Watchdog Timer and the Programming and Diagnostics sections of 61143E version of this data sheet has been incorporated into the Special Features section: |

|                                         | <ul> <li>Section 26.2 "Watchdog Timer (WDT)"</li> </ul>                                                                                                                                        |

|                                         | Section 26.4 "Programming and Diagnostics"                                                                                                                                                     |

| Section 29.0 "Electrical                | Added the 64-Lead QFN package to Table 29-3.                                                                                                                                                   |

| Characteristics"                        | Updated data in Table 29-5.                                                                                                                                                                    |

|                                         | Updated data in Table 29-7.                                                                                                                                                                    |

|                                         | Updated data in Table 29-4, Table 29-5, Table 29-7 and Table 29-8.                                                                                                                             |

|                                         | Updated data in Table 29-11.                                                                                                                                                                   |

|                                         | Added OS42 parameter to Table 29-17.                                                                                                                                                           |

|                                         | Replaced Table 29-23.                                                                                                                                                                          |

|                                         | Replaced Table 29-24.                                                                                                                                                                          |

|                                         | Replaced Table 29-25.                                                                                                                                                                          |

|                                         | Updated Table 29-36.                                                                                                                                                                           |

| Section 30.0 "Packaging<br>Information" | Added 64-Lead QFN package marking information to <b>Section 30.1 "Package Marking Information"</b> .                                                                                           |

|                                         | Added the 64-Lead QFN (MR) package drawing and land pattern to <b>Section 30.2 "Package Details"</b> .                                                                                         |

| "Product Identification System"         | Added the MR package designator for the 64-Lead (9x9x0.9) QFN.                                                                                                                                 |