Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              |                                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx440f128lt-80v-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 1<br>RE4<br>NC | 2                                                          | 3                                                                                                            | 4                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                     |

|----------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                                            |                                                                                                              |                                                                                            | <b>.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                                                                                                                                                                                  |

|                | RE3                                                        | RG13                                                                                                         | RE0                                                                                        | RG0                                                                                                                                                                                                                                                                                                                                                                                                                                              | RF1                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>R</b> D12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RD2                                                                                                                                                                                                                                                                                                                                                                                                | RD1                                                                                                                                                                                                                                                 |

| NC             | RG15                                                       | RE2                                                                                                          | RE1                                                                                        | RA7                                                                                                                                                                                                                                                                                                                                                                                                                                              | RF0                                                                                                                                                                                                                                                                                                                                                                                                                                              | VCORE/<br>VCAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RD5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )<br>Vss                                                                                                                                                                                                                                                                                                                                                                                           | O<br>RC14                                                                                                                                                                                                                                           |

| RE6            | O<br>VDD                                                   | RG12                                                                                                         | RG14                                                                                       | RA6                                                                                                                                                                                                                                                                                                                                                                                                                                              | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD7                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | O<br>RC13                                                                                                                                                                                                                                                                                                                                                                                          | RD11                                                                                                                                                                                                                                                |

| RC1            | RE7                                                        | RE5                                                                                                          | ⊖<br>Vss                                                                                   | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC                                                                                                                                                                                                                                                                                                                                                                                                 | <b>R</b> D10                                                                                                                                                                                                                                        |

| RC4            | RC3                                                        | RG6                                                                                                          | RC2                                                                                        | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | RG1                                                                                                                                                                                                                                                                                                                                                                                                                                              | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RA15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RD8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RD9                                                                                                                                                                                                                                                                                                                                                                                                | RA14                                                                                                                                                                                                                                                |

| MCLR           | RG8                                                        | RG9                                                                                                          | RG7                                                                                        | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | O<br>RC12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                           | O<br>RC15                                                                                                                                                                                                                                           |

| RE8            | RE9                                                        | RA0                                                                                                          | NC                                                                                         | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                         | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RA3                                                                                                                                                                                                                                                                                                                                                                                                | RA4                                                                                                                                                                                                                                                 |

| O<br>RB5       | O<br>RB4                                                   | ⊖<br>Vss                                                                                                     | O<br>Vdd                                                                                   | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RF7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RF6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RG2                                                                                                                                                                                                                                                                                                                                                                                                | RA2                                                                                                                                                                                                                                                 |

| O<br>RB3       | O<br>RB2                                                   | O<br>RB7                                                                                                     | O<br>AVDD                                                                                  | O<br>RB11                                                                                                                                                                                                                                                                                                                                                                                                                                        | O<br>RA1                                                                                                                                                                                                                                                                                                                                                                                                                                         | O<br>RB12                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RF8                                                                                                                                                                                                                                                                                                                                                                                                | O<br>RG3                                                                                                                                                                                                                                            |

| O<br>RB1       | O<br>RB0                                                   | O<br>RA10                                                                                                    | O<br>RB8                                                                                   | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | RF12                                                                                                                                                                                                                                                                                                                                                                                                                                             | O<br>RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RF3                                                                                                                                                                                                                                                                                                                                                                                                | RF2                                                                                                                                                                                                                                                 |

| O<br>RB6       | O<br>RA9                                                   | O<br>AVss                                                                                                    | O<br>RB9                                                                                   | O<br>RB10                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>R</b> F13                                                                                                                                                                                                                                                                                                                                                                                                                                     | O<br>RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | O<br>RB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RD14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RF4                                                                                                                                                                                                                                                                                                                                                                                                | RF5                                                                                                                                                                                                                                                 |

|                | RC1<br>RC4<br>ACLR<br>RE8<br>RB5<br>RB5<br>RB3<br>RB1<br>C | RC1   RE7     RC4   RC3     ACLR   RG8     RE8   RE9     RB5   RB4     RB3   RB2     RB1   RB0     RB3   RB0 | RC1RE7RE5RC4RC3RG6ACLRRG8RG9ACLRRG8RG9RE8RE9RA0RB5RB4VSSRB3RB2RB7RB1RB0RA10OOOOORB1RB0RA10 | RC1       RE7       RE5       VSS         RC4       RC3       RG6       RC2         ACLR       RG8       RG9       RG7         RE8       RE9       RA0       NC         RB5       RB4       VSS       VDD         RB3       RB2       RB7       AVDD         RB1       RB0       RA10       RB8         O       O       O       O         O       O       O       O         O       O       O       O         RB1       RB0       RA10       RB8 | RC1       RE7       RE5       VSS       VSS         RC4       RC3       RG6       RC2       VDD         ACLR       RG8       RG9       RG7       VSS         RE8       RE9       RA0       NC       VDD         RB5       RB4       VSS       VDD       NC         RB3       RB2       RB7       AVDD       RB11         RB0       RA10       RB8       NC         O       O       O       O         RB1       RB0       RA10       RB8       NC | RC1       RE7       RE5       VSS       NC         RC4       RC3       RG6       RC2       VDD       RG1         ACLR       RG8       RG9       RG7       VSS       NC         RE8       RE9       RA0       NC       VDD       VSS         RB5       RB4       VSS       VDD       NC       VDD         RB3       RB2       RB7       AVDD       RB11       RA1         RB1       RB0       RA10       RB8       NC       RF12         O       O       O       O       O       P | RC1       RE7       RE5       VSS       VSS       NC       RD6         RC4       RC3       RG6       RC2       VDD       RG1       VSS         ACLR       RG8       RG9       RG7       VSS       NC       NC         RE8       RE9       RA0       NC       VDD       VSS       VSS         RB5       RB4       VSS       VDD       NC       VDD       NC         RB3       RB2       RB7       AVDD       RB11       RA1       RB12         RB1       RB0       RA10       RB8       NC       RF12       RB14 | RC1       RE7       RE5       VSS       VSS       NC       RD6       RD13         RC4       RC3       RG6       RC2       VDD       RG1       VSS       RA15         ACLR       RG8       RG9       RG7       VSS       NC       NC       VDD         RE8       RE9       RA0       NC       VDD       VSS       VSS       NC       NC         RB5       RB4       VSS       VDD       NC       VDD       NC       RF7         RB3       RB2       RB7       AVDD       RB11       RA1       RB12       NC         RB1       RB0       RA10       RB8       NC       RF12       RB14       VDD         NC       O       O       O       O       O       O       O       O         RB1       RB0       RA10       RB8       NC       RF12       RB14       VDD | RC1RE7RE5VSSVSSNCRD6RD13RD0RC4RC3RG6RC2VDDRG1VSSRA15RD8ACLRRG8RG9RG7VSSNCNCVD0RC12RE8RE9RA0NCVDDVSSVSSNCRA0RB5RB4VSSVDDNCVDDNCRF7RF6RB3RB2RB7AVDDRB11RA1RB12NCMCRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOPRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOPPRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOOPRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOOOORB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOOOORB1RB0RA10RB8NCRF12RB14VDDRD15 | RC1RE7RE5VSSVSSNCRD6RD13RD0NCRC4RC3RG6RC2VDDRG1VSSRA15RD8RD9ACLRRG8RG9RG7VSSNCNCVDDRC12VSSRE8RE9RA0NCVDDVSSVSSNCRA5RA3RB5RB4VSSVDDNCVDDNCRF7RF6RG2RB3RB2RB7AVDDRB11RA1RB12NCNCRF8RB1RB0RA10RB8NCRF12RB14VDDRD15RF3RB1RB0RA10RB8NCRF12RB14VDDRD15RF3 |

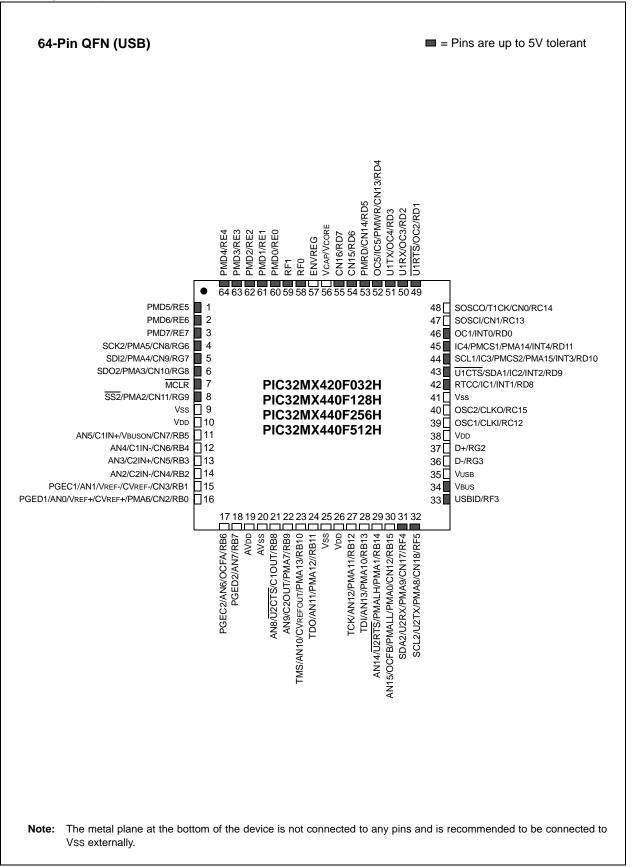

## Pin Diagrams (Continued)

#### **Pin Diagrams (Continued)**

|            |            |            |              |            | F128L<br>F256L<br>F512L |          |                     |           |           |           |              |

|------------|------------|------------|--------------|------------|-------------------------|----------|---------------------|-----------|-----------|-----------|--------------|

|            | 1          | 2          | 3            | 4          | 5                       | 6        | 7                   | 8         | 9         | 10        | 11           |

| <b>x</b> ( | RE4        | RE3        | <b>R</b> G13 | RE0        | RG0                     | RF1      |                     | O<br>Vss  | RD12      | RD2       | RD1          |

| 3          | NC         | RG15       | RE2          | RE1        | RA7                     | RF0      | O<br>Vcore/<br>Vcap | RD5       | RD3       | O<br>Vss  | O<br>RC14    |

| ;          | RE6        | O<br>VDD   | RG12         | RG14       | RA6                     | NC       | RD7                 | RD4       | O<br>Vdd  | O<br>RC13 | RD11         |

|            | RC1        | RE7        | RE5          | O<br>Vss   | ⊖<br>Vss                | NC       | RD6                 | RD13      | RD0       | NC        | <b>R</b> D10 |

|            | RC4        | RC3        | RG6          | RC2        | O<br>Vdd                | RG1      | ⊖<br>Vss            | RA15      | RD8       | RD9       | RA14         |

| -          | MCLR       | RG8        | RG9          | RG7        | O<br>Vss                | NC       | NC                  |           | C<br>RC12 | O<br>Vss  | O<br>RC15    |

| •          | RE8        | RE9        | RA0          | NC         | VDD                     | O<br>Vss | O<br>Vss            | NC        | RA5       | RA3       | RA4          |

| 1          | C<br>RB5   | C<br>RB4   | O<br>Vss     | O<br>Vdd   |                         | O<br>VDD | NC                  | VBUS      | UUSB      | RG2       | RA2          |

| J          | C<br>RB3   | C<br>RB2   | C<br>RB7     |            | C<br>RB11               | O<br>RA1 | O<br>RB12           | NC        | NC        | RF8       | C<br>RG3     |

| ¢          | C)<br>RB1  | O<br>RB0   | ○<br>RA10    | C)<br>RB8  | NC                      | RF12     | O<br>RB14           |           | RD15      | RF3       | RF2          |

| -          | C)<br>RB6  | RA9        | AVss         | RB9        | RB10                    | RF13     | RB13                | C<br>RB15 | RD14      | RF4       | RF5          |

| L          | lote 1: Re | efer to Ta | ble 4 for    | full pin r | names.                  |          |                     |           |           |           |              |

## Pin Diagrams (Continued)

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

|          | Pin                                       | Number <sup>(</sup> | 1)              |             | Deff           |                                                         |  |  |  |  |

|----------|-------------------------------------------|---------------------|-----------------|-------------|----------------|---------------------------------------------------------|--|--|--|--|

| Pin Name | 64-pin<br>QFN/TQFP                        | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type | Buffer<br>Type | Description                                             |  |  |  |  |

| CN0      | 48                                        | 74                  | B11             | I           | ST             | Change notification inputs.                             |  |  |  |  |

| CN1      | 47                                        | 73                  | C10             | -           | ST             | Can be software programmed for internal weak            |  |  |  |  |

| CN2      | 16                                        | 25                  | K2              | I           | ST             | pull-ups on all inputs.                                 |  |  |  |  |

| CN3      | 15                                        | 24                  | K1              | I           | ST             |                                                         |  |  |  |  |

| CN4      | 14                                        | 23                  | J2              | I           | ST             |                                                         |  |  |  |  |

| CN5      | 13                                        | 22                  | J1              | I           | ST             |                                                         |  |  |  |  |

| CN6      | 12                                        | 21                  | H2              | I           | ST             |                                                         |  |  |  |  |

| CN7      | 11                                        | 20                  | H1              | I           | ST             |                                                         |  |  |  |  |

| CN8      | 4                                         | 10                  | E3              | I           | ST             |                                                         |  |  |  |  |

| CN9      | 5                                         | 11                  | F4              | I           | ST             |                                                         |  |  |  |  |

| CN10     | 6                                         | 12                  | F2              | I           | ST             |                                                         |  |  |  |  |

| CN11     | 8                                         | 14                  | F3              | I           | ST             |                                                         |  |  |  |  |

| CN12     | 30                                        | 44                  | L8              | Ι           | ST             |                                                         |  |  |  |  |

| CN13     | 52                                        | 81                  | C8              | -           | ST             |                                                         |  |  |  |  |

| CN14     | 53                                        | 82                  | B8              | Ι           | ST             |                                                         |  |  |  |  |

| CN15     | 54                                        | 83                  | D7              | Ι           | ST             |                                                         |  |  |  |  |

| CN16     | 55                                        | 84                  | C7              | Ι           | ST             |                                                         |  |  |  |  |

| CN17     | 31                                        | 49                  | L10             | -           | ST             |                                                         |  |  |  |  |

| CN18     | 32                                        | 50                  | L11             | -           | ST             |                                                         |  |  |  |  |

| CN19     | _                                         | 80                  | D8              | -           | ST             |                                                         |  |  |  |  |

| CN20     | _                                         | 47                  | L9              | -           | ST             |                                                         |  |  |  |  |

| CN21     | _                                         | 48                  | K9              | -           | ST             |                                                         |  |  |  |  |

| IC1      | 42                                        | 68                  | E9              | I           | ST             | Capture inputs 1-5.                                     |  |  |  |  |

| IC2      | 43                                        | 69                  | E10             | I           | ST             |                                                         |  |  |  |  |

| IC3      | 44                                        | 70                  | D11             | I           | ST             |                                                         |  |  |  |  |

| IC4      | 45                                        | 71                  | C11             | -           | ST             |                                                         |  |  |  |  |

| IC5      | 52                                        | 79                  | A9              | -           | ST             |                                                         |  |  |  |  |

| OCFA     | 17                                        | 26                  | L1              | -           | ST             | Output Compare Fault A Input.                           |  |  |  |  |

| OC1      | 46                                        | 72                  | D9              | 0           |                | Output Compare output 1.                                |  |  |  |  |

| OC2      | 49                                        | 76                  | A11             | 0           | —              | Output Compare output 2                                 |  |  |  |  |

| OC3      | 50                                        | 77                  | A10             | 0           |                | Output Compare output 3.                                |  |  |  |  |

| OC4      | 51                                        | 78                  | B9              | 0           | —              | Output Compare output 4.                                |  |  |  |  |

| OC5      | 52                                        | 81                  | C8              | 0           |                | Output Compare output 5.                                |  |  |  |  |

| OCFB     | 30                                        | 44                  | L8              |             | ST             | Output Compare Fault B Input.                           |  |  |  |  |

| INT0     | 35,46                                     | 55,72               | H9,D9           |             | ST             | External interrupt 0.                                   |  |  |  |  |

| INT1     | 42                                        | 18                  | 61              | -           | ST             | External interrupt 1.                                   |  |  |  |  |

| INT2     | 43                                        | 19                  | 62              | I           | ST             | External interrupt 2.                                   |  |  |  |  |

| -        | CMOS = CM<br>ST = Schmitt<br>TTL = TTL in | Trigger in          |                 |             |                | Analog = Analog input P = Power<br>D = Output I = Input |  |  |  |  |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------|

|            |                                     |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

|          | Pin                                       | Number <sup>(</sup> | 1)              | Pin         | D              |                                                        |

|----------|-------------------------------------------|---------------------|-----------------|-------------|----------------|--------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/TQFP                        | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type | Buffer<br>Type | Description                                            |

| RD0      | 46                                        | 72                  | D9              | I/O         | ST             | PORTD is a bidirectional I/O port.                     |

| RD1      | 49                                        | 76                  | A11             | I/O         | ST             |                                                        |

| RD2      | 50                                        | 77                  | A10             | I/O         | ST             |                                                        |

| RD3      | 51                                        | 78                  | B9              | I/O         | ST             |                                                        |

| RD4      | 52                                        | 81                  | C8              | I/O         | ST             |                                                        |

| RD5      | 53                                        | 82                  | B8              | I/O         | ST             |                                                        |

| RD6      | 54                                        | 83                  | D7              | I/O         | ST             |                                                        |

| RD7      | 55                                        | 84                  | C7              | I/O         | ST             |                                                        |

| RD8      | 42                                        | 68                  | E9              | I/O         | ST             | 1                                                      |

| RD9      | 43                                        | 69                  | E10             | I/O         | ST             | 1                                                      |

| RD10     | 44                                        | 70                  | D11             | I/O         | ST             | 1                                                      |

| RD11     | 45                                        | 71                  | C11             | I/O         | ST             | 1                                                      |

| RD12     | _                                         | 79                  | A9              | I/O         | ST             | 1                                                      |

| RD13     | _                                         | 80                  | D8              | I/O         | ST             | 1                                                      |

| RD14     | _                                         | 47                  | L9              | I/O         | ST             |                                                        |

| RD15     | _                                         | 48                  | K9              | I/O         | ST             |                                                        |

| RE0      | 60                                        | 93                  | A4              | I/O         | ST             | PORTE is a bidirectional I/O port.                     |

| RE1      | 61                                        | 94                  | B4              | I/O         | ST             |                                                        |

| RE2      | 62                                        | 98                  | B3              | I/O         | ST             |                                                        |

| RE3      | 63                                        | 99                  | A2              | I/O         | ST             |                                                        |

| RE4      | 64                                        | 100                 | A1              | I/O         | ST             |                                                        |

| RE5      | 1                                         | 3                   | D3              | I/O         | ST             |                                                        |

| RE6      | 2                                         | 4                   | C1              | I/O         | ST             |                                                        |

| RE7      | 3                                         | 5                   | D2              | I/O         | ST             |                                                        |

| RE8      | _                                         | 18                  | G1              | I/O         | ST             | 1                                                      |

| RE9      | _                                         | 19                  | G2              | I/O         | ST             | 1                                                      |

| RF0      | 58                                        | 87                  | B6              | I/O         | ST             | PORTF is a bidirectional I/O port.                     |

| RF1      | 59                                        | 88                  | A6              | I/O         | ST             | 1                                                      |

| RF2      | 34                                        | 52                  | K11             | I/O         | ST             | ]                                                      |

| RF3      | 33                                        | 51                  | K10             | I/O         | ST             | ]                                                      |

| RF4      | 31                                        | 49                  | L10             | I/O         | ST             | 1                                                      |

| RF5      | 32                                        | 50                  | L11             | I/O         | ST             | 1                                                      |

| RF6      | 35                                        | 55                  | H9              | I/O         | ST             | ]                                                      |

| RF7      | —                                         | 54                  | H8              | I/O         | ST             | 1                                                      |

| RF8      | —                                         | 53                  | J10             | I/O         | ST             | 1                                                      |

| RF12     | —                                         | 40                  | K6              | I/O         | ST             | 1                                                      |

| RF13     | —                                         | 39                  | L6              | I/O         | ST             | 1                                                      |

| -        | CMOS = CM<br>ST = Schmitt<br>TTL = TTL in | Trigger in          |                 |             |                | nalog = Analog input P = Power<br>) = Output I = Input |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> | CONTINUED) |

|------------|----------------------------------|------------|

|            |                                  | •••••••••  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

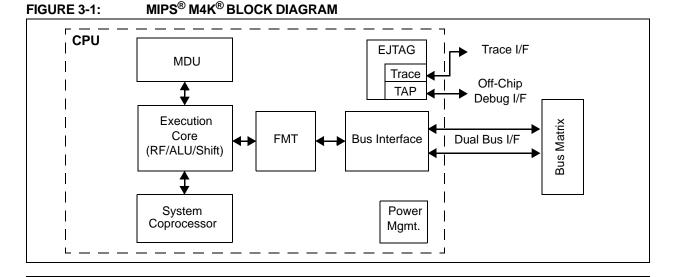

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS61113) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Core are available Processor at: www.mips.com/products/cores/ 32-64-bit-cores/mips32-m4k/.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX3XX/4XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

#### 3.1 Features

- 5-stage pipeline

- 32-bit Address and Data Paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-Accumulate and Multiply-Subtract Instructions

- Targeted Multiply Instruction

- Zero/One Detect Instructions

- WAIT Instruction

- Conditional Move Instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE & RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- Simple Dual Bus Interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 34 clock latency (dividend (*rs*) sign extension-dependent)