Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx440f512ht-80i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: PIC32MX USB – FEATURES

|                 | USB  |                         |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

|-----------------|------|-------------------------|-----|-------------------------|------------------|------------------------|------------------------------|-------------------------------|------|-------|-----------------------------|-----------------|-------------|---------|------|

| Device          | Pins | Packages <sup>(2)</sup> | MHz | Program Memory (KB)     | Data Memory (KB) | Timers/Capture/Compare | Programmable DMA<br>Channels | Dedicated USB DMA<br>Channels | VREG | Trace | EUART/SPI/I <sup>2</sup> C™ | 10-bit ADC (ch) | Comparators | dSd/dWd | JTAG |

| PIC32MX420F032H | 64   | PT, MR                  | 40  | 32 + 12 <sup>(1)</sup>  | 8                | 5/5/5                  | 0                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F128H | 64   | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F256H | 64   | PT, MR                  | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F512H | 64   | PT, MR                  | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

| PIC32MX440F128L | 121  | BG                      | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

| PIC32MX460F256L | 121  | BG                      | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     | (1)                     |                  |                        |                              | _                             |      |       |                             |                 | _           |         |      |

| PIC32MX460F512L | 121  | BG                      | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

Legend: PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB Boot Flash memory.

2: See Legend for an explanation of the acronyms. See Section 30.0 "Packaging Information" for details.

| 1<br>RE4<br>NC | 2                                                          | 3                                                                                                            | 4                                                                                          | 5                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                     |  |  |

|----------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                |                                                            |                                                                                                              |                                                                                            | <b>.</b>                                                                                                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                                                                                                                                                                                  |  |  |

|                | RE3                                                        | RG13                                                                                                         | RE0                                                                                        | RG0                                                                                                                                                                                                                                                                                             | RF1                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>R</b> D12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RD2                                                                                                                                                                                                                                                                                                                                                                                                | RD1                                                                                                                                                                                                                                                 |  |  |

| NC             | RG15                                                       | RE2                                                                                                          | RE1                                                                                        | RA7                                                                                                                                                                                                                                                                                             | RF0                                                                                                                                                                                                                                                                                                                                                                                                                                              | VCORE/<br>VCAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RD5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )<br>Vss                                                                                                                                                                                                                                                                                                                                                                                           | O<br>RC14                                                                                                                                                                                                                                           |  |  |

| RE6            | O<br>VDD                                                   | RG12                                                                                                         | RG14                                                                                       | RA6                                                                                                                                                                                                                                                                                             | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD7                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | O<br>RC13                                                                                                                                                                                                                                                                                                                                                                                          | RD11                                                                                                                                                                                                                                                |  |  |

| RC1            | RE7                                                        | RE5                                                                                                          | ⊖<br>Vss                                                                                   | ⊖<br>Vss                                                                                                                                                                                                                                                                                        | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RD13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC                                                                                                                                                                                                                                                                                                                                                                                                 | <b>R</b> D10                                                                                                                                                                                                                                        |  |  |

| RC4            | RC3                                                        | RG6                                                                                                          | RC2                                                                                        | O<br>Vdd                                                                                                                                                                                                                                                                                        | RG1                                                                                                                                                                                                                                                                                                                                                                                                                                              | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RA15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RD8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RD9                                                                                                                                                                                                                                                                                                                                                                                                | RA14                                                                                                                                                                                                                                                |  |  |

| MCLR           | RG8                                                        | RG9                                                                                                          | RG7                                                                                        | ⊖<br>Vss                                                                                                                                                                                                                                                                                        | NC                                                                                                                                                                                                                                                                                                                                                                                                                                               | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | O<br>RC12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                           | O<br>RC15                                                                                                                                                                                                                                           |  |  |

| RE8            | RE9                                                        | RA0                                                                                                          | NC                                                                                         | O<br>Vdd                                                                                                                                                                                                                                                                                        | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                         | ⊖<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RA3                                                                                                                                                                                                                                                                                                                                                                                                | RA4                                                                                                                                                                                                                                                 |  |  |

| O<br>RB5       | O<br>RB4                                                   | ⊖<br>Vss                                                                                                     | O<br>Vdd                                                                                   | NC                                                                                                                                                                                                                                                                                              | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RF7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RF6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RG2                                                                                                                                                                                                                                                                                                                                                                                                | RA2                                                                                                                                                                                                                                                 |  |  |

| O<br>RB3       | O<br>RB2                                                   | O<br>RB7                                                                                                     | O<br>AVDD                                                                                  | O<br>RB11                                                                                                                                                                                                                                                                                       | O<br>RA1                                                                                                                                                                                                                                                                                                                                                                                                                                         | O<br>RB12                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RF8                                                                                                                                                                                                                                                                                                                                                                                                | O<br>RG3                                                                                                                                                                                                                                            |  |  |

| O<br>RB1       | O<br>RB0                                                   | O<br>RA10                                                                                                    | O<br>RB8                                                                                   | NC                                                                                                                                                                                                                                                                                              | RF12                                                                                                                                                                                                                                                                                                                                                                                                                                             | O<br>RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | O<br>Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RF3                                                                                                                                                                                                                                                                                                                                                                                                | RF2                                                                                                                                                                                                                                                 |  |  |

| O<br>RB6       | O<br>RA9                                                   | O<br>AVss                                                                                                    | O<br>RB9                                                                                   | O<br>RB10                                                                                                                                                                                                                                                                                       | <b>R</b> F13                                                                                                                                                                                                                                                                                                                                                                                                                                     | O<br>RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | O<br>RB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RD14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RF4                                                                                                                                                                                                                                                                                                                                                                                                | RF5                                                                                                                                                                                                                                                 |  |  |

|                | RC1<br>RC4<br>ACLR<br>RE8<br>RB5<br>RB5<br>RB3<br>RB1<br>C | RC1   RE7     RC4   RC3     ACLR   RG8     RE8   RE9     RB5   RB4     RB3   RB2     RB1   RB0     RB3   RB0 | RC1RE7RE5RC4RC3RG6ACLRRG8RG9ACLRRG8RG9RE8RE9RA0RB5RB4VSSRB3RB2RB7RB1RB0RA10OOOOORB1RB0RA10 | RC1       RE7       RE5       VSS         RC4       RC3       RG6       RC2         ACLR       RG8       RG9       RG7         RE8       RE9       RA0       NC         RB5       RB4       VSS       VDD         RB3       RB2       RB7       AVDD         RB1       RB0       RA10       RB8 | RC1       RE7       RE5       VSS       VSS         RC4       RC3       RG6       RC2       VDD         ACLR       RG8       RG9       RG7       VSS         RE8       RE9       RA0       NC       VDD         RB5       RB4       VSS       VDD       NC         RB3       RB2       RB7       AVDD       RB11         RB0       RA10       RB8       NC         O       O       O       O         RB1       RB0       RA10       RB8       NC | RC1       RE7       RE5       VSS       NC         RC4       RC3       RG6       RC2       VDD       RG1         ACLR       RG8       RG9       RG7       VSS       NC         RE8       RE9       RA0       NC       VDD       VSS         RB5       RB4       VSS       VDD       NC       VDD         RB3       RB2       RB7       AVDD       RB11       RA1         RB1       RB0       RA10       RB8       NC       RF12         O       O       O       O       O       P | RC1       RE7       RE5       VSS       VSS       NC       RD6         RC4       RC3       RG6       RC2       VDD       RG1       VSS         ACLR       RG8       RG9       RG7       VSS       NC       NC         RE8       RE9       RA0       NC       VDD       VSS       VSS         RB5       RB4       VSS       VDD       NC       VDD       NC         RB3       RB2       RB7       AVDD       RB11       RA1       RB12         RB1       RB0       RA10       RB8       NC       RF12       RB14 | RC1       RE7       RE5       VSS       VSS       NC       RD6       RD13         RC4       RC3       RG6       RC2       VDD       RG1       VSS       RA15         ACLR       RG8       RG9       RG7       VSS       NC       NC       VDD         RE8       RE9       RA0       NC       VDD       VSS       VSS       NC       NC         RB5       RB4       VSS       VDD       NC       VDD       NC       RF7         RB3       RB2       RB7       AVDD       RB11       RA1       RB12       NC         RB1       RB0       RA10       RB8       NC       RF12       RB14       VDD         NC       O       O       O       O       O       O       O       O         RB1       RB0       RA10       RB8       NC       RF12       RB14       VDD | RC1RE7RE5VSSVSSNCRD6RD13RD0RC4RC3RG6RC2VDDRG1VSSRA15RD8ACLRRG8RG9RG7VSSNCNCVD0RC12RE8RE9RA0NCVDDVSSVSSNCRA0RB5RB4VSSVDDNCVDDNCRF7RF6RB3RB2RB7AVDDRB11RA1RB12NCMCRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOPRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOPPRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOOPRB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOOOORB1RB0RA10RB8NCRF12RB14VDDRD15OOOOOOOOOORB1RB0RA10RB8NCRF12RB14VDDRD15 | RC1RE7RE5VSSVSSNCRD6RD13RD0NCRC4RC3RG6RC2VDDRG1VSSRA15RD8RD9ACLRRG8RG9RG7VSSNCNCVDDRC12VSSRE8RE9RA0NCVDDVSSVSSNCRA5RA3RB5RB4VSSVDDNCVDDNCRF7RF6RG2RB3RB2RB7AVDDRB11RA1RB12NCNCRF8RB1RB0RA10RB8NCRF12RB14VDDRD15RF3RB1RB0RA10RB8NCRF12RB14VDDRD15RF3 |  |  |

## Pin Diagrams (Continued)

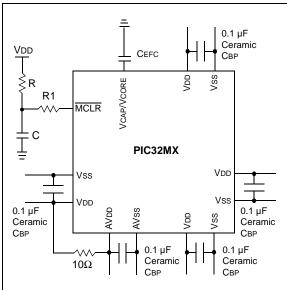

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

#### 2.3 Capacitor on Internal Voltage Regulator (VCAP/VCORE)

### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (< 1 Ohm) capacitor is required on the VCAP/VCORE pin, which is used to stabilize the internal voltage regulator output. The VCAP/VCORE pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 29.0** "**Electrical Characteristics**" for additional information on CEFC specifications. This mode is enabled by connecting the ENVREG pin to VDD.

### 2.3.2 EXTERNAL REGULATOR MODE

In this mode the core voltage is supplied externally through the VCORE/VCAP pin. A low-ESR capacitor of 10  $\mu F$  is recommended on the VCAP/VCORE pin. This mode is enabled by grounding the ENVREG pin.

The placement of this capacitor should be close to the VCAP/VCORE. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 26.3** "**On-Chip Voltage Regulator**" for details.

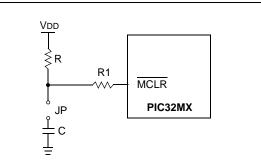

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| FIGURE 2-2: | EXAMPLE OF MCLR PIN |

|-------------|---------------------|

|             | CONNECTIONS         |

- Note 1: R ≤10 kΩ is recommended. A suggested starting value is 10 kΩ Ensure that the MCLR pin VIH and VIL specifications are met.

- 2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

- **3:** The capacitor can be sized to prevent unintentional resets from brief glitches or to extend the device reset period during POR.

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

## TABLE 3-1:MIPS<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER<br/>MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the general purpose register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, multiply-add (MADD) and multiplysubtract (MSUB), are used to perform the multiplyaccumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (kernel, user and debug), and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                |

|--------------------|-------------------------|-------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count                                                   |

| 10                 | Reserved                | Reserved                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception                                       |

| 15                 | PRId                    | Processor identification and revision                                   |

| 15                 | EBASE                   | Exception vector base register                                          |

| 16                 | Config                  | Configuration register                                                  |

| 16                 | Config1                 | Configuration register 1                                                |

| 16                 | Config2                 | Configuration register 2                                                |

| 16                 | Config3                 | Configuration register 3                                                |

TABLE 3-2: COPROCESSOR 0 REGISTERS

### 4.0 MEMORY ORGANIZATION

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Memory Organization" (DS61115) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX3XX/4XX microcontrollers provide 4 GB of unified virtual memory address space. All memory regions including program, data memory, SFRs and Configuration registers reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX3XX/4XX to execute from data memory.

#### 4.1 Key Features

- 32-bit native data width

- Separate User and Kernel mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable and non-cacheable address regions

#### 4.2 PIC32MX3XX/4XX Memory Layout

PIC32MX3XX/4XX microcontrollers implement two address spaces: Virtual and Physical. All hardware resources such as program memory, data memory and peripherals are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by peripherals such as DMA and Flash controller that access memory independently of CPU.

#### TABLE 4-1: BUS MATRIX REGISTERS MAP

| ess                         |                      | 6         |                 |                     |       |       |       |           |      |      | Bits    |          |      |           |           |           |            |          |               |

|-----------------------------|----------------------|-----------|-----------------|---------------------|-------|-------|-------|-----------|------|------|---------|----------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name     | Bit Range | 31/15           | 30/14               | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7    | 22/6     | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        |                      | 31:16     |                 |                     |       | _     |       | BMXCHEDMA | _    | _    | _       | _        |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | CON <sup>(1)</sup>   | 15:0      | —               | _                   | —     | _     | _     | _         | _    | —    | _       | BMXWSDRM |      | —         | _         | BI        | MXARB<2:0> |          | 0042          |

| 2010                        |                      | 31:16     | _               |                     | _     |       |       | _         | _    | _    | _       | _        |      | _         |           | _         | _          | _        | 0000          |

| 2010                        | DKPBA <sup>(1)</sup> | 15:0      |                 | BMXDKPBA<15:0> 0000 |       |       |       |           |      |      |         |          |      |           | 0000      |           |            |          |               |

|                             |                      | 31:16     | _               |                     | _     |       |       | _         | -    | _    | _       | _        |      | _         |           | _         | _          | _        | 0000          |

| 2020                        | DUDBA <sup>(1)</sup> | 15:0      |                 |                     |       |       |       |           |      | BN   | IXDUDBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             |                      | 31:16     |                 |                     | _     | -     |       | —         | -    | _    | _       | -        |      | _         | _         | _         | _          | _        | 0000          |

| 2030                        | DUPBA <sup>(1)</sup> | 15:0      |                 |                     |       |       |       |           |      | BN   | IXDUPBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             | BMX                  | 31:16     |                 |                     |       |       |       |           |      |      |         |          |      |           |           |           |            |          | xxxx          |

| 2040                        | DRMSZ                | 15:0      |                 |                     |       |       |       |           |      | BN   | IXDRMSZ | <31:0>   |      |           |           |           |            |          | xxxx          |

|                             |                      | 31:16     |                 | _                   | _     | _     | _     | _         | -    | _    | _       | _        | _    | _         |           | BMXPUPBA  | \<19:16>   |          | 0000          |

| 2050                        | PUPBA <sup>(1)</sup> | 15:0      |                 |                     |       |       |       |           |      | BN   | IXPUPBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             | BMX                  | 31:16     |                 |                     |       |       |       |           |      |      |         |          |      |           |           |           |            |          | xxxx          |

| 2060                        | PFMSZ                | 15:0      |                 | BMXPFMSZ<31:0>      |       |       |       |           |      |      |         |          |      |           |           |           |            |          |               |

| 0070                        | BMX                  | 31:16     |                 |                     |       |       |       |           | _    | -    |         |          |      |           |           |           |            |          | 0000          |

| 2070                        | BOOTSZ               | 15:0      | BMXBOOTSZ<31:0> |                     |       |       |       |           |      |      |         |          |      |           |           |           |            |          |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| ess                         |                        |               |         |         |         |         |                             |        |            | Bi       | ts       |          |         |        |               |        |        |        |            |

|-----------------------------|------------------------|---------------|---------|---------|---------|---------|-----------------------------|--------|------------|----------|----------|----------|---------|--------|---------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15   | 30/14   | 29/13   | 28/12   | 27/11                       | 26/10  | 25/9       | 24/8     | 23/7     | 22/6     | 21/5    | 20/4   | 19/3          | 18/2   | 17/1   | 16/0   | All Resets |

| 1000                        | INTCON                 | 31:16         | _       | —       | —       |         |                             | —      | -          |          | _        | —        | _       | -      | —             |        | —      | SS0    | 00         |

| 1000                        | INTCOM                 | 15:0          |         | —       | —       | MVEC    | _                           |        | TPC<2:0>   |          | _        | _        | _       | INT4EP | INT3EP        | INT2EP | INT1EP | INT0EP | 00         |

| 1010                        | INTSTAT <sup>(2)</sup> | 31:16         | _       | _       | _       |         | _                           |        | _          |          |          | _        |         |        | _             | _      | _      | _      | 00         |

| 1010                        | INIGIAI                | 15:0          | —       | _       | _       |         |                             |        | SRIPL<2:0> |          |          | _        |         |        | VEC           | <5:0>  |        |        | 00         |

| 1020                        | IPTMR                  | 31:16<br>15:0 |         |         |         |         |                             |        |            | IPTMR    | <31:0>   |          |         |        |               |        |        |        | 00         |

|                             |                        | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF | U1TXIF  | U1RXIF                      | U1EIF  | SPI1RXIF   | SPI1TXIF | SPI1EIF  | OC5IF    | IC5IF   | T5IF   | INT4IF        | OC4IF  | IC4IF  | T4IF   | 00         |

| 1030                        | IFS0                   | 15:0          | INT3IF  | OC3IF   | IC3IF   | T3IF    | INT2IF                      | OC2IF  | IC2IF      | T2IF     | INT1IF   | OC1IF    | IC1IF   | T1IF   | INT0IF        | CS1IF  | CS0IF  | CTIF   | 00         |

|                             | 1504                   | 31:16         | _       | _       | _       | _       | _                           | _      | USBIF      | FCEIF    | _        | _        | _       | _      | <b>DMA3IF</b> | DMA2IF | DMA1IF | DMA0IF | 00         |

| 1040                        | IFS1                   | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF | I2C2SIF | I2C2BIF                     | U2TXIF | U2RXIF     | U2EIF    | SPI2RXIF | SPI2TXIF | SPI2EIF | CMP2IF | CMP1IF        | PMPIF  | AD1IF  | CNIF   | 00         |

| 4000                        | 15.00                  | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE | U1TXIE  | U1RXIE                      | U1EIE  | SPI1RXIE   | SPI1TXIE | SPI1EIE  | OC5IE    | IC5IE   | T5IE   | INT4IE        | OC4IE  | IC4IE  | T4IE   | 00         |

| 1060                        | IEC0                   | 15:0          | INT3IE  | OC3IE   | IC3IE   | T3IE    | INT2IE                      | OC2IE  | IC2IE      | T2IE     | INT1IE   | OC1IE    | IC1IE   | T1IE   | INT0IE        | CS1IE  | CS0IE  | CTIE   | 00         |

| 4070                        | IEC1                   | 31:16         | —       | —       | _       |         |                             | -      | USBIE      | FCEIE    |          | —        |         |        | DMA3IE        | DMA2IE | DMA1IE | DMA0IE | 00         |

| 1070                        | IECT                   | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE | I2C2SIE | I2C2BIE                     | U2TXIE | U2RXIE     | U2EIE    | SPI2RXIE | SPI2TXIE | SPI2EIE | CMP2IE | CMP1IE        | PMPIE  | AD1IE  | CNIE   | 00         |

| 1090                        | IPC0                   | 31:16         | —       | —       | —       |         | NT0IP<2:0>                  |        | INTOIS     | S<1:0>   | _        | —        | _       |        | CS1IP<2:0>    |        | CS1IS  | S<1:0> | 00         |

| 1090                        | IFCU                   | 15:0          | _       | -       | -       |         | CS0IP<2:0>                  |        | CSOIS      | i<1:0>   | _        | -        | _       |        | CTIP<2:0>     |        | CTIS   | <1:0>  | 00         |

| 10A0                        | IPC1                   | 31:16         | —       | -       | -       |         | NT1IP<2:0>                  |        | INT1IS     | S<1:0>   |          | -        | -       |        | OC1IP<2:0>    |        | OC1IS  | S<1:0> | 00         |

| IUAU                        | 1101                   | 15:0          | —       | _       | _       |         | IC1IP<2:0>                  |        | IC1IS      | <1:0>    |          | -        |         |        | T1IP<2:0>     |        | T1IS   | <1:0>  | 00         |

| 10B0                        | IPC2                   | 31:16         | —       | —       | —       |         | NT2IP<2:0>                  |        | INT2IS     | S<1:0>   | —        | —        | —       |        | OC2IP<2:0>    |        | OC2IS  | S<1:0> | 00         |

| TODO                        | 11 02                  | 15:0          | _       | —       | —       |         | IC2IP<2:0>                  |        | IC2IS      | <1:0>    | _        | —        | _       |        | T2IP<2:0>     |        | T2IS   | <1:0>  | 00         |

| 10C0                        | IPC3                   | 31:16         | _       | —       | —       |         | NT3IP<2:0>                  |        |            | S<1:0>   | _        | —        | _       |        | OC3IP<2:0>    |        |        | S<1:0> | 00         |