Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | -                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx460f256l-80i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# High-Performance, General Purpose and USB 32-bit Flash Microcontrollers

### High-Performance 32-bit RISC CPU:

- MIPS32<sup>®</sup> M4K<sup>®</sup> 32-bit core with 5-stage pipeline

- 80 MHz maximum frequency

- 1.56 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state Flash access

- Single-cycle multiply and high-performance divide unit

- MIPS16e<sup>®</sup> mode for up to 40% smaller code size

- Two sets of 32 core register files (32-bit) to reduce interrupt latency

- Prefetch Cache module to speed execution from Flash

# **Microcontroller Features:**

- Operating temperature range of -40°C to +105°C

- Operating voltage range of 2.3V to 3.6V

- 32K to 512K Flash memory (plus an additional 12 KB of boot Flash)

- 8K to 32K SRAM memory

- Pin-compatible with most PIC24/dsPIC<sup>®</sup> DSC devices

- Multiple power management modes

- Multiple interrupt vectors with individually programmable priority

- Fail-Safe Clock Monitor Mode

- Configurable Watchdog Timer with on-chip Low-Power RC Oscillator for reliable operation

# **Peripheral Features:**

- Atomic SET, CLEAR and INVERT operation on select peripheral registers

- Up to 4-channel hardware DMA with automatic data size detection

- USB 2.0-compliant full-speed device and On-The-Go (OTG) controller

- USB has a dedicated DMA channel

- 3 MHz to 25 MHz crystal oscillator

- Internal 8 MHz and 32 kHz oscillators

- Separate PLLs for CPU and USB clocks

- Two I<sup>2</sup>C<sup>™</sup> modules

- Two UART modules with:

- RS-232, RS-485 and LIN support

- IrDA<sup>®</sup> with on-chip hardware encoder and decoder

- Up to two SPI modules

- Parallel Master and Slave Port (PMP/PSP) with 8-bit and 16-bit data and up to 16 address lines

- Hardware Real-Time Clock and Calendar (RTCC)

- Five 16-bit Timers/Counters (two 16-bit pairs combine to create two 32-bit timers)

- · Five capture inputs

- Five compare/PWM outputs

- Five external interrupt pins

- High-Speed I/O pins capable of toggling at up to 80 MHz

- High-current sink/source (18 mA/18 mA) on all I/O pins

- Configurable open-drain output on digital I/O pins

### **Debug Features:**

- Two programming and debugging Interfaces:

- 2-wire interface with unintrusive access and real-time data exchange with application

- 4-wire  $\mathsf{MIPS}^{\texttt{®}}$  standard enhanced JTAG interface

- Unintrusive hardware-based instruction trace

- IEEE Standard 1149.2-compatible (JTAG) boundary scan

# **Analog Features:**

- Up to 16-channel 10-bit Analog-to-Digital Converter:

- 1000 ksps conversion rate

- Conversion available during Sleep, Idle

- Two Analog Comparators

#### TABLE 2: PIC32MX USB – FEATURES

|                 | USB  |                         |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

|-----------------|------|-------------------------|-----|-------------------------|------------------|------------------------|------------------------------|-------------------------------|------|-------|-----------------------------|-----------------|-------------|---------|------|

| Device          | Pins | Packages <sup>(2)</sup> | MHz | Program Memory (KB)     | Data Memory (KB) | Timers/Capture/Compare | Programmable DMA<br>Channels | Dedicated USB DMA<br>Channels | VREG | Trace | EUART/SPI/I <sup>2</sup> C™ | 10-bit ADC (ch) | Comparators | dSd/dWd | JTAG |

| PIC32MX420F032H | 64   | PT, MR                  | 40  | 32 + 12 <sup>(1)</sup>  | 8                | 5/5/5                  | 0                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F128H | 64   | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F256H | 64   | PT, MR                  | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F512H | 64   | PT, MR                  | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

| PIC32MX440F128L | 121  | BG                      | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

| PIC32MX460F256L | 121  | BG                      | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     | (1)                     |                  |                        |                              | _                             |      |       |                             |                 | _           |         |      |

| PIC32MX460F512L | 121  | BG                      | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

Legend: PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB Boot Flash memory.

2: See Legend for an explanation of the acronyms. See Section 30.0 "Packaging Information" for details.

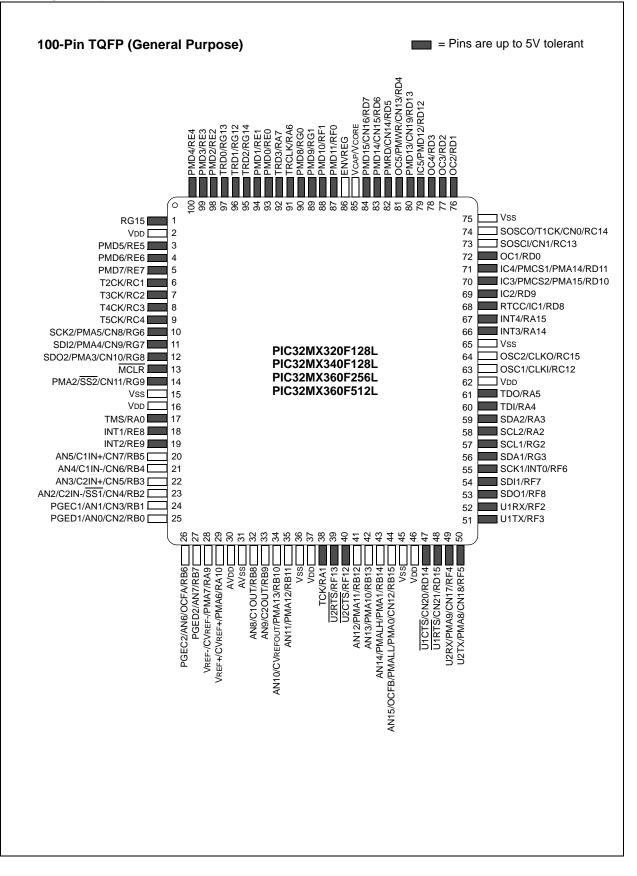

### **Pin Diagrams (Continued)**

|          | Pin                                       | Number <sup>(</sup> | 1)              | - Pin<br>Type | Deff           |                                                        |

|----------|-------------------------------------------|---------------------|-----------------|---------------|----------------|--------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/TQFP                        | 100-pin<br>TQFP     | 121-pin<br>XBGA | Pin<br>Type   | Buffer<br>Type | Description                                            |

| RD0      | 46                                        | 72                  | D9              | I/O           | ST             | PORTD is a bidirectional I/O port.                     |

| RD1      | 49                                        | 76                  | A11             | I/O           | ST             |                                                        |

| RD2      | 50                                        | 77                  | A10             | I/O           | ST             |                                                        |

| RD3      | 51                                        | 78                  | B9              | I/O           | ST             |                                                        |

| RD4      | 52                                        | 81                  | C8              | I/O           | ST             |                                                        |

| RD5      | 53                                        | 82                  | B8              | I/O           | ST             |                                                        |

| RD6      | 54                                        | 83                  | D7              | I/O           | ST             |                                                        |

| RD7      | 55                                        | 84                  | C7              | I/O           | ST             |                                                        |

| RD8      | 42                                        | 68                  | E9              | I/O           | ST             | 1                                                      |

| RD9      | 43                                        | 69                  | E10             | I/O           | ST             | 1                                                      |

| RD10     | 44                                        | 70                  | D11             | I/O           | ST             | 1                                                      |

| RD11     | 45                                        | 71                  | C11             | I/O           | ST             | 1                                                      |

| RD12     | _                                         | 79                  | A9              | I/O           | ST             | 1                                                      |

| RD13     | _                                         | 80                  | D8              | I/O           | ST             | 1                                                      |

| RD14     | _                                         | 47                  | L9              | I/O           | ST             |                                                        |

| RD15     | _                                         | 48                  | K9              | I/O           | ST             |                                                        |

| RE0      | 60                                        | 93                  | A4              | I/O           | ST             | PORTE is a bidirectional I/O port.                     |

| RE1      | 61                                        | 94                  | B4              | I/O           | ST             |                                                        |

| RE2      | 62                                        | 98                  | B3              | I/O           | ST             |                                                        |

| RE3      | 63                                        | 99                  | A2              | I/O           | ST             |                                                        |

| RE4      | 64                                        | 100                 | A1              | I/O           | ST             |                                                        |

| RE5      | 1                                         | 3                   | D3              | I/O           | ST             |                                                        |

| RE6      | 2                                         | 4                   | C1              | I/O           | ST             |                                                        |

| RE7      | 3                                         | 5                   | D2              | I/O           | ST             |                                                        |

| RE8      | _                                         | 18                  | G1              | I/O           | ST             | 1                                                      |

| RE9      | _                                         | 19                  | G2              | I/O           | ST             | 1                                                      |

| RF0      | 58                                        | 87                  | B6              | I/O           | ST             | PORTF is a bidirectional I/O port.                     |

| RF1      | 59                                        | 88                  | A6              | I/O           | ST             | 1                                                      |

| RF2      | 34                                        | 52                  | K11             | I/O           | ST             | ]                                                      |

| RF3      | 33                                        | 51                  | K10             | I/O           | ST             | ]                                                      |

| RF4      | 31                                        | 49                  | L10             | I/O           | ST             | 1                                                      |

| RF5      | 32                                        | 50                  | L11             | I/O           | ST             | 1                                                      |

| RF6      | 35                                        | 55                  | H9              | I/O           | ST             | ]                                                      |

| RF7      | —                                         | 54                  | H8              | I/O           | ST             | 1                                                      |

| RF8      | —                                         | 53                  | J10             | I/O           | ST             | 1                                                      |

| RF12     | —                                         | 40                  | K6              | I/O           | ST             | 1                                                      |

| RF13     | —                                         | 39                  | L6              | I/O           | ST             | 1                                                      |

| -        | CMOS = CM<br>ST = Schmitt<br>TTL = TTL in | Trigger in          |                 |               |                | nalog = Analog input P = Power<br>) = Output I = Input |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> | CONTINUED) |

|------------|----------------------------------|------------|

|            |                                  | •••••••••  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

| TABLE 1-1:       PINOUT I/O DESCRIPTIONS (CONTINUED) |                                           |                     |                 |      |        |                                                                                                              |  |  |  |

|------------------------------------------------------|-------------------------------------------|---------------------|-----------------|------|--------|--------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                      | Pin                                       | Number <sup>(</sup> | 1)              | Pin  | Buffer |                                                                                                              |  |  |  |

| Pin Name                                             | 64-pin<br>QFN/TQFP                        | 100-pin<br>TQFP     | 121-pin<br>XBGA | Туре | Туре   | Description                                                                                                  |  |  |  |

| PMD0                                                 | 60                                        | 93                  | A4              | I/O  | TTL/ST | Parallel Master Port Data (De-multiplexed Master                                                             |  |  |  |

| PMD1                                                 | 61                                        | 94                  | B4              | I/O  | TTL/ST | mode) or Address/Data (Multiplexed Master modes                                                              |  |  |  |

| PMD2                                                 | 62                                        | 98                  | B3              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD3                                                 | 63                                        | 99                  | A2              | I/O  | TTL/ST | 1                                                                                                            |  |  |  |

| PMD4                                                 | 64                                        | 100                 | A1              | I/O  | TTL/ST | 1                                                                                                            |  |  |  |

| PMD5                                                 | 1                                         | 3                   | D3              | I/O  | TTL/ST | 1                                                                                                            |  |  |  |

| PMD6                                                 | 2                                         | 4                   | C1              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD7                                                 | 3                                         | 5                   | D2              | I/O  | TTL/ST | 1                                                                                                            |  |  |  |

| PMD8                                                 | _                                         | 90                  | A5              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD9                                                 |                                           | 89                  | E6              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD10                                                | _                                         | 88                  | A6              | I/O  | TTL/ST | 1                                                                                                            |  |  |  |

| PMD11                                                |                                           | 87                  | B6              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD12                                                |                                           | 79                  | A9              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD13                                                | _                                         | 80                  | D8              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD14                                                |                                           | 83                  | D7              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMD15                                                |                                           | 84                  | C7              | I/O  | TTL/ST |                                                                                                              |  |  |  |

| PMRD                                                 | 53                                        | 82                  | B8              | 0    |        | Parallel Master Port Read Strobe.                                                                            |  |  |  |

| PMWR                                                 | 52                                        | 81                  | C8              | 0    | _      | Parallel Master Port Write Strobe.                                                                           |  |  |  |

| PMALL                                                | 30                                        | 44                  | L8              | 0    |        | Parallel Master Port Address Latch Enable low-byte (Multiplexed Master modes).                               |  |  |  |

| PMALH                                                | 29                                        | 43                  | K7              | 0    |        | Parallel Master Port Address Latch Enable high-byte<br>(Multiplexed Master modes).                           |  |  |  |

| Vbus                                                 | 34                                        | 54                  | H8              | I    | Analog | USB Bus Power Monitor.                                                                                       |  |  |  |

| Vusb                                                 | 35                                        | 55                  | H9              | Ρ    | _      | USB Internal Transceiver Supply. If the USB module<br>is <i>not</i> used, this pin must be connected to VDD. |  |  |  |

| VBUSON                                               | 11                                        | 20                  | H1              | 0    | —      | USB Host and OTG Bus Power Control Output.                                                                   |  |  |  |

| D+                                                   | 37                                        | 57                  | H10             | I/O  | Analog | USB D+.                                                                                                      |  |  |  |

| D-                                                   | 36                                        | 56                  | J11             | I/O  | Analog | USB D                                                                                                        |  |  |  |

| USBID                                                | 33                                        | 51                  | K10             | I    | ST     | USB OTG ID Detect.                                                                                           |  |  |  |

| ENVREG                                               | 57                                        | 86                  | A7              | I    | ST     | Enable for On-Chip Voltage Regulator.                                                                        |  |  |  |

| TRCLK                                                | —                                         | 91                  | C5              | 0    | —      | Trace Clock.                                                                                                 |  |  |  |

| TRD0                                                 | _                                         | 97                  | A3              | 0    | _      | Trace Data Bits 0-3.                                                                                         |  |  |  |

| TRD1                                                 | _                                         | 96                  | C3              | 0    | _      |                                                                                                              |  |  |  |

| TRD2                                                 | _                                         | 95                  | C4              | 0    | —      |                                                                                                              |  |  |  |

| TRD3                                                 | —                                         | 92                  | B5              | 0    | —      |                                                                                                              |  |  |  |

| PGED1                                                | 16                                        | 25                  | K2              | I/O  | ST     | Data I/O pin for programming/debugging<br>communication channel 1.                                           |  |  |  |

| PGEC1                                                | 15                                        | 24                  | K1              | I    | ST     | Clock input pin for programming/debugging communication channel 1.                                           |  |  |  |

|                                                      | CMOS = CM<br>ST = Schmitt<br>TTL = TTL in | Trigger in          |                 |      |        | nalog = Analog input P = Power<br>) = Output I = Input                                                       |  |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX3XX/4XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP/VCORE

(see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.8 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins used when external voltage reference for ADC module is implemented

Note: The AVDD and AVSS pins must be connected independent of ADC use and ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| SS                          |                        |               |                   |                  |                   |                |                            |                |                 | В                | its           |                |                |              |                          |                |                |                 |            |

|-----------------------------|------------------------|---------------|-------------------|------------------|-------------------|----------------|----------------------------|----------------|-----------------|------------------|---------------|----------------|----------------|--------------|--------------------------|----------------|----------------|-----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15             | 30/14            | 29/13             | 28/12          | 27/11                      | 26/10          | 25/9            | 24/8             | 23/7          | 22/6           | 21/5           | 20/4         | 19/3                     | 18/2           | 17/1           | 16/0            | All Resets |

| 1000                        | INTCON                 | 31:16         | —                 | —                | —                 | —              | -                          | —              | -               | —                | —             | —              | _              | -            | -                        | -              | -              | SS0             | 000        |

|                             |                        | 15:0<br>31:16 | _                 | _                |                   | MVEC           |                            | _              | TPC<2:0>        | _                |               | _              | _              | INT4EP       | INT3EP                   | INT2EP         | INT1EP         | INT0EP          | 000        |

| 1010                        | INTSTAT <sup>(2)</sup> | 15:0          | _                 | _                | _                 |                | _                          |                | SRIPL<2:0>      |                  |               |                |                | _            | VEC-                     | :5:0>          | _              | _               | 000        |

| 1020                        | IPTMR                  | 31:16<br>15:0 |                   |                  |                   |                |                            |                |                 |                  | R<31:0>       |                |                |              |                          |                |                |                 | 000        |

| 1030                        | IFS0                   | 31:16<br>15:0 | I2C1MIF<br>INT3IF | I2C1SIF<br>OC3IF | I2C1BIF<br>IC3IF  | U1TXIF<br>T3IF | U1RXIF<br>INT2IF           | U1EIF<br>OC2IF | –<br>IC2IF      | —<br>T2IF        | —<br>INT1IF   | OC5IF<br>OC1IF | IC5IF<br>IC1IF | T5IF<br>T1IF | INT4IF                   | OC4IF<br>CS1IF | IC4IF<br>CS0IF | T4IF<br>CTIF    | 000        |

| 1040                        | IFS1                   | 31:16<br>15:0 | - RTCCIF          | -<br>FSCMIF      | –<br>I2C2MIF      | –<br>I2C2SIF   | –<br>I2C2BIF               | U2TXIF         | USBIF<br>U2RXIF | FCEIF<br>U2EIF   | —<br>SPI2RXIF | —<br>SPI2TXIF  | —<br>SPI2EIF   | —<br>CMP2IF  | —<br>CMP1IF              | –<br>PMPIF     | AD1IF          | —<br>CNIF       | 000        |

| 1060                        | IEC0                   | 31:16         | I2C1MIE           | I2C1SIE          | I2C1BIE           | U1TXIE         | U1RXIE                     | U1EIE          | _               | _                | —             | OC5IE          | IC5IE          | T5IE         | INT4IE                   | OC4IE          | IC4IE          | T4IE            | 000        |

| 1070                        | IEC1                   | 15:0<br>31:16 | INT3IE<br>—       | OC3IE            | IC3IE             | T3IE           | INT2IE                     | OC2IE          | IC2IE<br>USBIE  | T2IE<br>FCEIE    | INT1IE        | OC1IE          | IC1IE          | T1IE         |                          | CS1IE          | CS0IE          | CTIE            | 000        |

|                             | 0.                     | 15:0          | RTCCIE            | FSCMIE           | I2C2MIE           | I2C2SIE        | I2C2BIE                    | U2TXIE         | U2RXIE          | U2EIE            | SPI2RXIE      | SPI2TXIE       | SPI2EIE        | CMP2IE       | CMP1IE                   | PMPIE          | AD1IE          | CNIE            | 000        |

| 1090                        | IPC0                   | 31:16<br>15:0 | _                 |                  |                   |                | INT0IP<2:0><br>CS0IP<2:0>  |                |                 | S<1:0><br>S<1:0> |               |                | _              |              | CS1IP<2:0><br>CTIP<2:0>  |                | CS1IS<br>CTIS  | S<1:0>          | 000        |

|                             |                        | 31:16         | _                 |                  | _                 |                | INT1IP<2:0>                |                |                 | S<1:0>           |               |                |                |              | OC1IP<2:0>               |                | OC1IS          |                 | 000        |

| 10A0                        | IPC1                   | 15:0          | _                 | _                | _                 |                | IC1IP<2:0>                 |                |                 | <1:0>            | _             | _              | _              |              | T1IP<2:0>                |                | T1IS           |                 | 000        |

| 10B0                        | IPC2                   | 31:16<br>15:0 | _                 | _                | -                 |                | INT2IP<2:0><br>IC2IP<2:0>  | •              |                 | S<1:0><br>i<1:0> | _             | _              | -              |              | OC2IP<2:0><br>T2IP<2:0>  |                | OC2IS<br>T2IS  |                 | 000        |

|                             |                        | 31:16         | _                 |                  | _                 |                | INT3IP<2:0>                | ,              |                 | S<1:0>           |               |                |                |              | OC3IP<2:0>               |                | OC315          |                 | 000        |

| 10C0                        | IPC3                   | 15:0          | _                 | _                | _                 |                | IC3IP<2:0>                 |                |                 | <1:0>            | _             | _              | _              |              | T3IP<2:0>                |                | T3IS-          |                 | 000        |

| 10D0                        | IPC4                   | 31:16         | _                 | _                | _                 |                | INT4IP<2:0>                | •              | INT4IS          | S<1:0>           | -             | _              | _              |              | OC4IP<2:0>               |                | OC4IS          | S<1:0>          | 000        |

| TODU                        | IPC4                   | 15:0          | _                 | _                | _                 |                | IC4IP<2:0>                 |                | IC4IS           | i<1:0>           | _             | _              | _              |              | T4IP<2:0>                |                | T4IS-          |                 | 000        |

| 10E0                        | IPC5                   | 31:16         | -                 | —                | —                 |                | —                          | —              | -               | —                | -             | —              | -              |              | OC5IP<2:0>               |                | OC5IS          |                 | 000        |

|                             |                        | 15:0          | _                 | —                | —                 |                | IC5IP<2:0>                 |                |                 | <1:0>            | —             | —              | —              |              | T5IP<2:0>                |                | T5IS-          |                 | 000        |

| 10F0                        | IPC6                   | 31:16         | -                 | _                | _                 |                | AD1IP<2:0>                 |                |                 | S<1:0>           |               |                |                |              | CNIP<2:0>                |                |                | <1:0>           | 000        |

|                             |                        | 15:0<br>31:16 | _                 |                  |                   |                | I2C1IP<2:0><br>SPI2IP<2:0> |                |                 | S<1:0><br>S<1:0> |               |                | _              |              | U1IP<2:0><br>CMP2IP<2:0: |                | U1IS           | <1:0><br>S<1:0> | 000        |

| 1100                        | IPC7                   | 15:0          | _                 |                  |                   |                | SPIZIP<2:0><br>CMP1IP<2:0: |                |                 | S<1:0><br>S<1:0> |               | _              |                |              | PMPIP<2:03               | 2              | PMPIS          |                 | 000        |

|                             |                        | 31:16         | _                 |                  |                   |                | RTCCIP<2:0:                |                |                 | S<1:0>           | _             | _              |                |              | SCMIP<2:0                | >              |                | S<1:0>          | 000        |

| 1110                        | IPC8                   | 15:0          | _                 |                  | _                 |                | 12C2IP<2:0>                |                |                 | S<1:0>           | _             | _              | _              |              | U2IP<2:0>                |                |                | <1:0>           | 000        |

| 1140                        | IPC11                  | 31:16         | _                 | —                | —                 | —              |                            | —              | —               | —                | —             | —              | —              | —            | —                        | _              | —              |                 | 000        |

| Legen                       |                        | 15:0          | —                 | —                | —<br>Inimplemente |                | USBIP<2:0>                 |                |                 | S<1:0>           | -             | —              | -              |              | FCEIP<2:0>               |                | FCEIS          | 6<1:0>          | 0000       |

#### INTERRUPT REGISTERS MAP FOR THE PIC32MY420E032H DEVICE ONI V(1) TADIE 1.6.

© 2011 Microchip Technology Inc.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

PIC32MX3XX/4XX

This register does not have associated CLR, SET, and INV registers. 2:

# TABLE 4-16: DMA CHANNELS 0-3 REGISTERS MAP FOR PIC32MX340FXXXX/360FXXXX/440FXXXX/460XXXX DEVICES ONLY<sup>(1)</sup> (CONTINUED)

| riy                   | H1DSA - | Bit Kange     | 31/15 | 30/14 | 29/13 | 28/12 |        |       |      |        |        |        |        |        |        |        |        |        | ця,        |

|-----------------------|---------|---------------|-------|-------|-------|-------|--------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| 3160 DCH              | H1DSA - |               |       |       |       | 20/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3170 DCH              |         | 15:0          |       |       |       | ·     |        |       |      | CHDSA  | <31:0> |        |        |        |        |        |        |        | 0000       |

| 3170 DCH              |         | 31:16         | —     | —     | _     | —     | _      | —     | _    | —      | _      | _      | —      | _      | —      | —      | —      | —      | 0000       |

|                       | HISSIZ  | 15:0          | —     |       | —     | —     |        | —     | —    | —      |        |        |        | CHSSI  | Z<7:0> |        |        |        | 0000       |

| 3180 DCH <sup>2</sup> | H1DSIZ  | 31:16         | _     | _     | —     | —     |        | —     | —    | —      | —      |        |        | —      | —      | —      | —      | _      | 0000       |

| 3160 DCH              |         | 15:0          | -     |       | _     | _     | —      | —     | _    | —      |        |        |        | CHDSI  | Z<7:0> |        |        |        | 0000       |

| 3190 DCH1             | HISPTR  | 31:16         | _     |       | _     | _     | —      | -     | _    | _      | _      |        |        | —      |        | —      |        | -      | 0000       |

| ST30 DCITI            |         | 15:0          | —     |       | —     | _     | —      | _     | —    | _      |        |        |        | CHSPT  | R<7:0> |        |        |        | 0000       |

| 31A0 DCH1             |         | 31:16         | —     |       | —     | —     | —      | —     | —    | —      | —      |        |        | —      | -      | —      |        | _      | 0000       |

| SIA0 DOM              |         | 15:0          | —     | -     | —     | —     | —      | —     | —    | —      |        |        |        | CHDPT  | R<7:0> |        |        |        | 0000       |

| 31B0 DCH              | H1CSIZ  | 31:16         | —     | _     | —     | —     | _      | —     | —    | —      | —      | _      | —      | —      | —      | —      | —      | —      | 0000       |

| olbo Doll             | 1110012 | 15:0          | —     | —     | —     | —     |        | —     | —    | —      |        |        |        | CHCSI  | Z<7:0> |        |        | -      | 0000       |

| 31C0 DCH1             | H1CPTR  | 31:16         | —     | _     | —     | —     | _      | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      |        | 0000       |

| 0.00 20               |         | 15:0          | —     | -     | —     | —     | —      | —     | —    | —      |        |        |        | CHCPT  | R<7:0> |        |        |        | 0000       |

| 31D0 DCH              | H1DAT   | 31:16         | —     | _     | —     | —     | _      | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      |        | 0000       |

| 0.00 000              |         | 15:0          | —     |       | —     | —     | —      | —     | —    | —      |        |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 31E0 DCH              | H2CON   | 31:16         | —     | -     | —     | —     | —      | —     | —    | —      | —      | -      | _      | —      | —      | —      | —      | —      | 0000       |

|                       |         | 15:0          | —     |       | —     | —     | —      | —     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | l<1:0> | 0000       |

| 31F0 DCH2             | 12ECON  | 31:16         | —     | —     | —     | —     | —      | —     | —    | —      |        |        |        | CHAIR  | r      |        |        |        | 00FF       |

|                       |         | 15:0          |       |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | —      | —      | FF00       |

| 3200 DCH              | CH2INT  | 31:16         | —     | —     | —     | _     | _      | —     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE |            |

|                       |         | 15:0          |       |       |       |       |        | —     |      |        | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF |            |

| 3210 DCH              | H2SSA - | 31:16         |       |       |       |       |        |       |      | CHSSA  | <31:0> |        |        |        |        |        |        |        | 0000       |

|                       |         | 15:0          |       |       |       |       |        |       |      |        |        |        |        |        |        |        |        |        | 0000       |

| 3220 DCH              | H2DSA   | 31:16<br>15:0 |       |       |       |       |        |       |      | CHDSA  | <31:0> |        |        |        |        |        |        |        | 0000       |

| 2220 DCH              |         | 31:16         | —     | —     | —     | —     |        | —     | —    | —      | —      |        |        | —      | —      | —      | —      | _      | 0000       |

| 3230 DCH2             | H2SSIZ  | 15:0          | _     | —     | —     | —     |        | —     | —    | —      |        |        |        | CHSSI  | Z<7:0> |        |        |        | 0000       |

| 3240 DCH2             | H2DSIZ  | 31:16         | —     | —     | —     | —     |        | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —      | 0000       |

| 3240 DCH              | nzuəiz  | 15:0          | —     |       | —     | —     |        | —     | —    | —      |        |        |        | CHDSI  | Z<7:0> |        |        |        | 0000       |

| 2250 0042             | H2SPTR- | 31:16         | _     | —     | —     | —     |        | —     | —    | —      | —      |        | —      | —      | —      | —      | —      | —      | 0000       |

| 3250 DCH2             | nzəfi k | 15:0          | —     |       | —     | —     | _      | —     | —    | —      |        |        |        | CHSPT  | R<7:0> |        |        |        | 0000       |

All registers except DCHxSPTR, DCHxDPTR and DCHxCPTR have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, Note 1: SET and INV Registers" for more information.

# TABLE 4-42: DEVICE AND REVISION ID SUMMARY

| ess                       |                  | e         |                                                                                        |                  |       |       |       |       |      | Bi   | ts   |       |         |      |      |      |      |      | ø         |

|---------------------------|------------------|-----------|----------------------------------------------------------------------------------------|------------------|-------|-------|-------|-------|------|------|------|-------|---------|------|------|------|------|------|-----------|

| Virtual Addro<br>(BF80_#) | Register<br>Name | Bit Range | 31/15                                                                                  | 30/14            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5    | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 5000                      | DEVID            | 31:16     |                                                                                        | VER              | <3:0> |       |       |       |      |      |      | DEVID | <27:16> |      |      |      |      |      | xxxx      |

| F220                      | DEVID            | 15:0      |                                                                                        | DEVID<15:0> xxxx |       |       |       |       |      |      |      |       |         |      |      |      |      |      |           |

| Legend                    | l: x = u         | nknown    | value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                  |       |       |       |       |      |      |      |       |         |      |      |      |      |      |           |

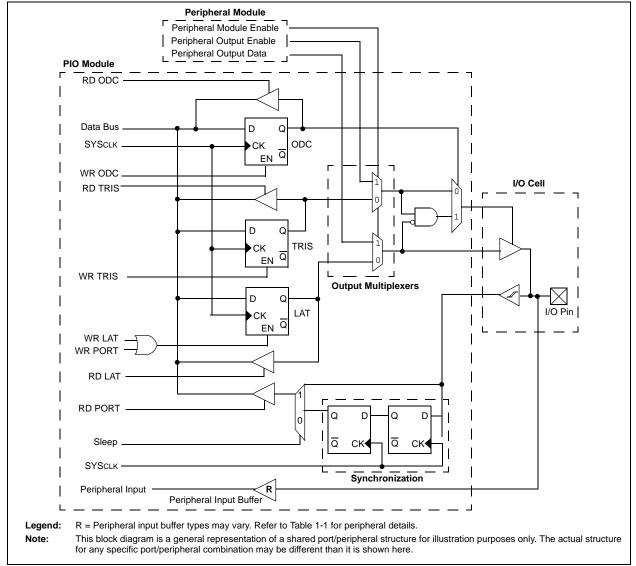

# 12.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS61120) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Following are some of the key features of this module:

- Individual Output Pin Open-drain Enable/Disable

- Individual Input Pin Weak Pull-up Enable/Disable

- Monitor Selective Inputs and Generate Interrupt when Change in Pin State is Detected

- Operation during CPU Sleep and Idle modes

- Fast Bit Manipulation using CLR, SET and INV Registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

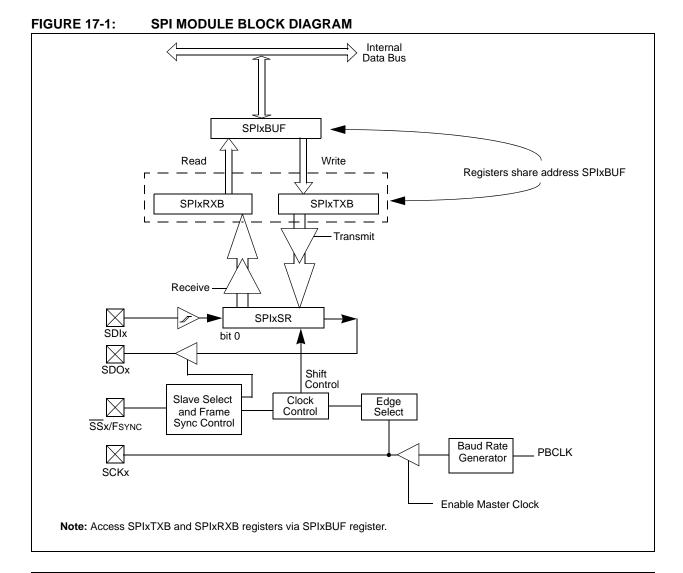

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32MX SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Following are some of the key features of this module:

- Master and Slave Modes Support

- Four Different Clock Formats

- Framed SPI Protocol Support

- User Configurable 8-bit, 16-bit and 32-bit Data

Width

- Separate SPI Data Registers for Receive and Transmit

- Programmable Interrupt Event on every 8-bit, 16-bit and 32-bit Data Transfer

- Operation during CPU Sleep and Idle Mode

- Fast Bit Manipulation using CLR, SET and INV Registers

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS61107) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

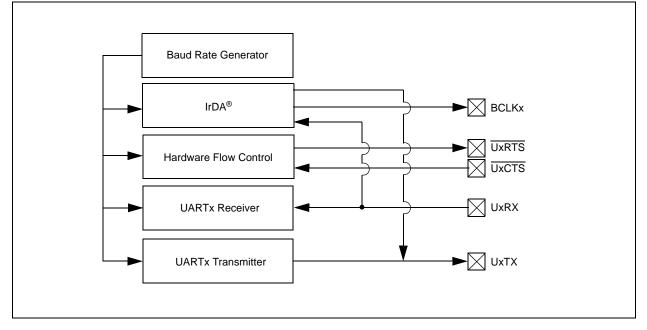

The UART module is one of the serial I/O modules available in PIC32MX3XX/4XX family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols such as RS-232, RS-485, LIN 1.2 and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 20 Mbps at 80 MHz

- 4-level-deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-level-deep FIFO Receive Data Buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

# 26.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX3XX/4XX family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-up Timer" (DS61114), Section 32. "Configuration" (DS61124) and Section 33. "Programming and Diagnostics" (DS61129) of the "PIC32 Family Reference Manual", which is available from Microchip the web site (www.microchip.com/PIC32).

PIC32MX3XX/4XX devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- Flexible Device Configuration

- Watchdog Timer

- JTAG Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

### 26.1 Configuration Bits

The Configuration bits can be programmed to select various device configurations.

| REGISTE      | :R 26-1: D        | EVCFG0: D         | EVICE CON         | FIGURATIO         | N WORD 0          |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | R/P              |

| 31:24        | —                 | —                 | —                 | CP                | _                 | —                 | —                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |

| 23:16        | —                 | —                 | —                 | —                 |                   | PWP               | <7:4>            |                  |

| 15:8         | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |

| 10.0         |                   | PWP<              | <3:0>             |                   |                   |                   | —                | —                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | R/P               | r-1               | R/P              | R/P              |

| 7:0          |                   | —                 | —                 | _                 | ICESEL            |                   | DEBU             | G<1:0>           |

|              |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | P = Progran       | nmable bit        | r = Reserve      | d bit            |

| U = Unim     | plemented bit     |                   | -n = Bit Valu     | e at POR: ('0'    | , '1', x = Unk    | nown)             |                  |                  |

#### REGISTER 26-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

- bit 31 **Reserved:** Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection disabled

- 0 = Protection enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | —                 | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | _                 |                   | —                 | _                 | —                 | _                | —                |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 15:8         |                   |                   |                   | USERID            | <15:8>            |                   |                  |                  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 7:0          |                   |                   |                   | USERID            | <7:0>             |                   |                  |                  |

#### REGISTER 26-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

# Legend:

| 3                     |                             |                      |                  |

|-----------------------|-----------------------------|----------------------|------------------|

| R = Readable bit      | W = Writable bit            | P = Programmable bit | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: ('0' | ', '1', x = Unknown) |                  |

bit 31-16 Reserved: Write '1'

bit 15-0 USERID<15:0>: This is a 16-bit value that is user defined and is readable via ICSP™ and JTAG

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|-------------------|----------------------|-------------------|-----------------------|------------------|

| 04-04        | R                 | R                 | R                  | R                 | R                    | R                 | R                     | R                |

| 31:24        |                   | VER<3             | :0> <sup>(1)</sup> |                   |                      | DEVID<2           | 27:24> <sup>(1)</sup> |                  |

| 00.40        | R                 | R                 | R                  | R                 | R                    | R                 | R                     | R                |

| 23:16        |                   |                   |                    | DEVID<2           | 3:16> <sup>(1)</sup> |                   |                       |                  |

| 45.0         | R                 | R                 | R                  | R                 | R                    | R                 | R                     | R                |

| 15:8         |                   |                   |                    | DEVID<1           | 5:8> <sup>(1)</sup>  |                   |                       |                  |

| 7.0          | R                 | R                 | R                  | R                 | R                    | R                 | R                     | R                |

| 7:0          |                   |                   |                    | DEVID<            | 7:0> <sup>(1)</sup>  |                   |                       |                  |

#### **REGISTER 26-5: DEVID: DEVICE AND REVISION ID REGISTER**

| Legend:               |                             |                      |                  |

|-----------------------|-----------------------------|----------------------|------------------|

| R = Readable bit      | W = Writable bit            | P = Programmable bit | r = Reserved bit |

| U = Unimplemented bit | -n = Bit Value at POR: ('0' | , '1',  x = Unknown) |                  |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID<sup>(1)</sup>

Note 1: See the "PIC32MX Flash Programming Specification" (DS61145) for a list of Revision and Device ID values.

NOTES:

# 28.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 28.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| DC CHAR              | ACTERISTIC             | S                   | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                                |                           |       |                           |  |  |  |

|----------------------|------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------|-------|---------------------------|--|--|--|

| Param.<br>No.        | Typical <sup>(3)</sup> | Max.                | Units                                                                                                                                                                                  | its Conditions                 |                           |       |                           |  |  |  |

| Operating            | Current (ID            | o) <sup>(1,2)</sup> |                                                                                                                                                                                        |                                |                           |       |                           |  |  |  |

| DC20                 | 8.5                    | 13                  | mA                                                                                                                                                                                     | A Code executing from Flash +8 |                           | _     | 4 MHz                     |  |  |  |

|                      | 9                      | 15                  |                                                                                                                                                                                        |                                | +105⁰C                    |       |                           |  |  |  |

| DC20c                | 4.0                    |                     | mA                                                                                                                                                                                     | Code executing from SRAM       | —                         |       |                           |  |  |  |

| DC21                 | 23.5                   | 32                  | mA                                                                                                                                                                                     | Code executing from Flash      |                           |       | 20 MHz<br>(Note 4)        |  |  |  |

| DC21c                | 16.4                   | _                   | mA                                                                                                                                                                                     | Code executing from SRAM       |                           |       |                           |  |  |  |

| DC22                 | 48                     | 61                  | mA                                                                                                                                                                                     | Code executing from Flash      |                           |       | 60 MHz                    |  |  |  |

| DC22c                | 45                     | —                   | mA                                                                                                                                                                                     | Code executing from SRAM       |                           |       | (Note 4)                  |  |  |  |

| DC23 55 75<br>60 100 |                        | 75                  | mA                                                                                                                                                                                     | Code executing from Flash      | -40°C,<br>+25°C,<br>+85°C | 2.3V  | 80 MHz                    |  |  |  |

|                      |                        | 100                 |                                                                                                                                                                                        |                                | +105⁰C                    |       |                           |  |  |  |

| DC23c                | 55                     |                     | mA                                                                                                                                                                                     | Code executing from SRAM       |                           | _     |                           |  |  |  |

| DC24                 | —                      | 100                 | μA                                                                                                                                                                                     | —                              | -40°C                     |       |                           |  |  |  |

| DC24a                | —                      | 130                 | μA                                                                                                                                                                                     | —                              | +25°C                     | 2.3V  |                           |  |  |  |

| DC24b                | —                      | 670                 | μA                                                                                                                                                                                     | —                              | +85°C                     |       |                           |  |  |  |

| DC24c                | —                      | 850                 | μA                                                                                                                                                                                     | —                              | +105°C                    |       |                           |  |  |  |

| DC25                 | 94                     | _                   | μA                                                                                                                                                                                     | —                              | -40°C                     |       |                           |  |  |  |

| DC25a                | 125                    | _                   | μA                                                                                                                                                                                     | —                              | +25°C                     | 0.01/ |                           |  |  |  |

| DC25b                | 302                    |                     |                                                                                                                                                                                        | _                              | +85°C                     | 3.3V  | LPRC (31 kHz)<br>(Note 4) |  |  |  |

| DC25d                | 400                    | _                   | μA                                                                                                                                                                                     |                                |                           | ]     |                           |  |  |  |

| DC25c                | 71                     | _                   | μA                                                                                                                                                                                     | Code executing from SRAM       | _                         |       | ]                         |  |  |  |