Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx460f256l-80i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3: PIN NAMES: PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F128L, AND PIC32MX360F512L DEVICES (CONTINUED)

| Pin<br>Number | Full Pin Name         |

|---------------|-----------------------|

| K4            | AN8/C1OUT/RB8         |

| K5            | No Connect (NC)       |

| K6            | U2CTS/RF12            |

| K7            | AN14/PMALH/PMA1/RB14  |

| K8            | VDD                   |

| K9            | U1RTS/CN21/RD15       |

| K10           | U1TX/RF3              |

| K11           | U1RX/RF2              |

| L1            | PGEC2/AN6/OCFA/RB6    |

| L2            | VREF-/CVREF-/PMA7/RA9 |

| Pin<br>Number | Full Pin Name                  |

|---------------|--------------------------------|

| L3            | AVss                           |

| L4            | AN9/C2OUT/RB9                  |

| L5            | AN10/CVREFOUT/PMA13/RB10       |

| L6            | U2RTS/RF13                     |

| L7            | AN13/PMA10/RB13                |

| L8            | AN15/OCFB/PMALL/PMA0/CN12/RB15 |

| L9            | CN20/U1CTS/RD14                |

| L10           | U2RX/PMA9/CN17/RF4             |

| L11           | U2TX/PMA8/CN18/RF5             |

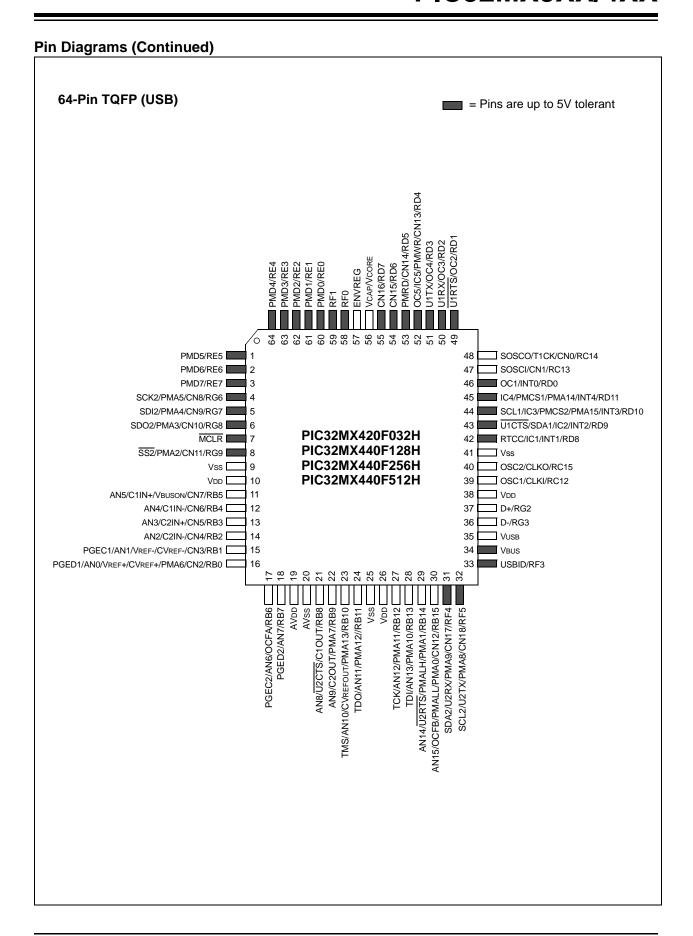

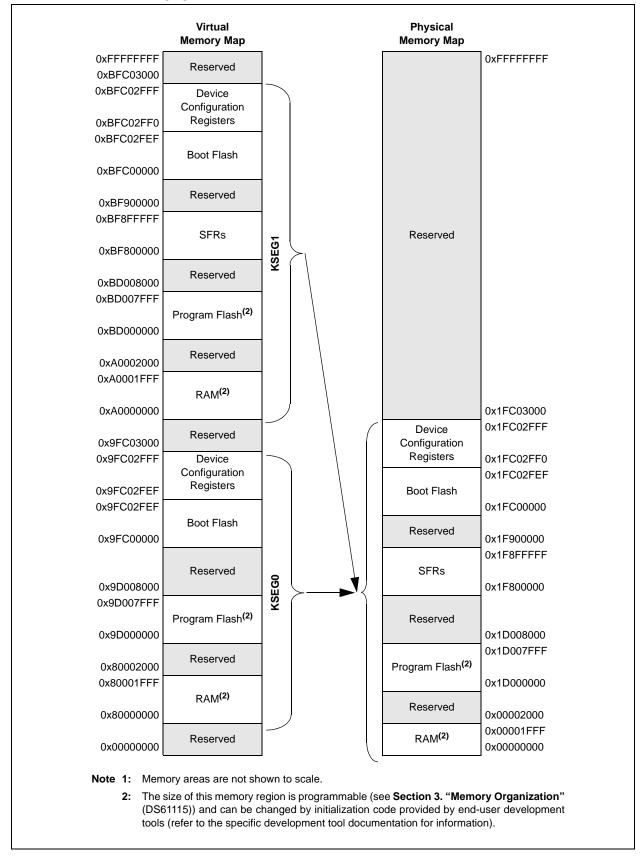

FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX320F032H AND PIC32MX420F032H DEVICES<sup>(1)</sup>

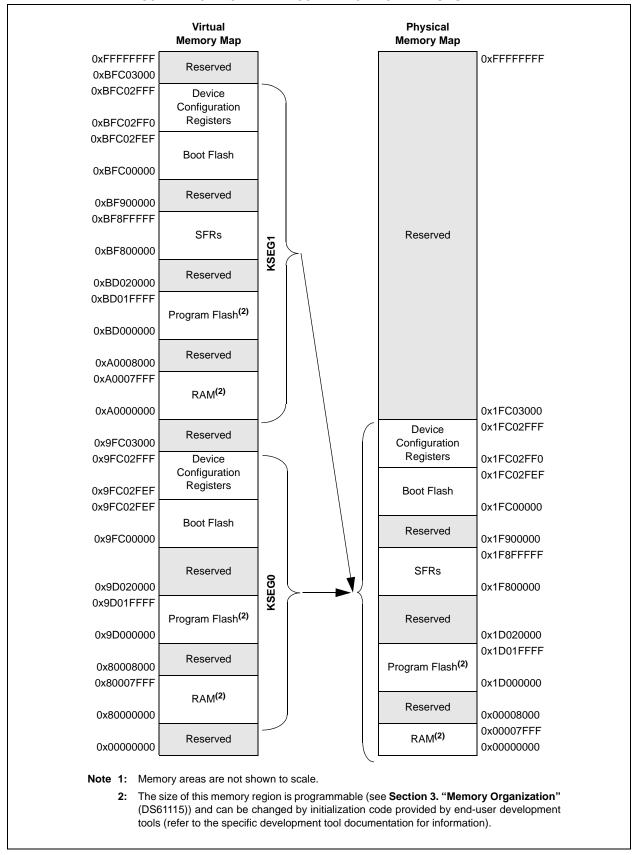

FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX340F128H, PIC32MX340F128L, PIC32MX440F128H AND PIC32MX440F128L DEVICES<sup>(1)</sup>

TABLE 4-1: BUS MATRIX REGISTERS MAP

| ess                         | _                    | ø.        |       |       |       |       |       |           |      |      | Bits    |          |      |           |           |           |            |          |               |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-----------|------|------|---------|----------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7    | 22/6     | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        |                      | 31:16     | _     | _     | _     | _     | _     | BMXCHEDMA | _    | _    | _       | _        | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | CON <sup>(1)</sup>   | 15:0      | _     | _     | _     | _     | _     | _         | -    | _    | _       | BMXWSDRM | _    | _         | -         | ВІ        | MXARB<2:0> |          | 0042          |

| 0040                        | DIVIA                | 31:16     | _     | _     | _     | _     | _     | _         | 1    | _    | _       | 1        | _    | _         | 1         | _         | _          | _        | 0000          |

| 2010                        | DKPBA <sup>(1)</sup> | 15:0      |       |       |       |       |       |           |      | BM   | IXDKPBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             | DIVIA                | 31:16     |       | _     | _     | _     | _     | _         | 1    | _    | _       | _        | _    | _         | _         | _         | _          | _        | 0000          |

| 2020                        | DUDBA <sup>(1)</sup> | 15:0      |       |       |       |       |       |           |      | BM   | IXDUDBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             |                      | 31:16     | _     | _     | _     | _     | _     | _         | 1    | _    | _       | _        | _    | _         | -         | _         | _          | _        | 0000          |

| 2030                        | DUPBA <sup>(1)</sup> | 15:0      |       |       |       |       |       |           |      | BM   | IXDUPBA | <15:0>   |      |           |           |           |            |          | 0000          |

| 00.40                       | BMX                  | 31:16     |       |       |       |       |       |           |      |      |         | 0.4.0    |      |           |           |           |            |          | xxxx          |

| 2040                        | DRMSZ                | 15:0      |       |       |       |       |       |           |      | BIV  | IXDRMSZ | <31:0>   |      |           |           |           |            |          | xxxx          |

| 2252                        | DIVIA                | 31:16     |       | _     | _     | _     | _     | _         | 1    | _    | _       | _        | _    | _         |           | BMXPUPB/  | <19:16>    |          | 0000          |

| 2050                        | PUPBA <sup>(1)</sup> | 15:0      |       |       |       |       |       |           |      | BM   | IXPUPBA | <15:0>   |      |           |           |           |            |          | 0000          |

|                             | BMX                  | 31:16     |       |       |       |       |       |           |      | 5.   |         | 04.0     |      |           |           |           |            |          | xxxx          |

| 2060                        | PFMSZ                | 15:0      |       |       |       |       |       |           |      | BIV  | IXPFMSZ | <31:0>   |      |           |           |           |            |          | xxxx          |

| 0070                        | BMX                  | 31:16     |       |       |       |       |       |           |      | 5    | VDOOTO  | 7 04 0   |      |           |           |           |            |          | 0000          |

| 2070                        | BOOTSZ               | 15:0      |       |       |       |       |       |           |      | BM.  | XBOOTSZ | Z<31:0>  |      |           |           |           |            |          | 3000          |

PIC32MX3XX/4XX

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET, and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| IABL | _E 4-7: | TIMER1-5 REGISTERS MAP |

|------|---------|------------------------|

| SS   |         |                        |

| sse                         |                  |           |            |       |        |             |       |       |             | В    | ts       |      |            |        |      |       |                    |      |            |

|-----------------------------|------------------|-----------|------------|-------|--------|-------------|-------|-------|-------------|------|----------|------|------------|--------|------|-------|--------------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15      | 30/14 | 29/13  | 28/12       | 27/11 | 26/10 | 25/9        | 24/8 | 23/7     | 22/6 | 21/5       | 20/4   | 19/3 | 18/2  | 17/1               | 16/0 | All Resets |

| 0600                        | T1CON            | 31:16     | _          |       | _      | _           | 1     | 1     | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

| 0000                        | 110011           | 15:0      | ON         | _     | SIDL   | TWDIS       | TWIP  |       | _           | _    | TGATE    | _    | TCKPS      | S<1:0> | _    | TSYNC | TCS                | _    | 0000       |

| 0610                        | TMR1             | 31:16     | _          | _     | _      | _           |       | _     | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

| 0010                        | 11411111         | 15:0      |            |       |        |             |       |       |             | TMR1 | <15:0>   |      |            |        |      |       |                    |      | 0000       |

| 0620                        | PR1              | 31:16     | _          | _     | _      | _           |       | _     | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

| 0020                        |                  | 15:0      |            |       |        |             |       |       |             | PR1< | 15:0>    |      |            |        |      |       |                    |      | FFFF       |

| 0800                        | T2CON            | 31:16     | _          | _     | _      | _           | ı     | -     | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             | .200             | 15:0      | ON         | _     | SIDL   | _           | _     | _     | _           | _    | TGATE    |      | TCKPS<2:0> | •      | T32  | _     | TCS <sup>(2)</sup> | _    | 0000       |

| 0810                        | TMR2             | 31:16     | _          |       | _      | _           | -     |       | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             |                  | 15:0      |            |       |        |             |       |       |             | TMR2 | <15:0>   |      |            |        |      |       |                    | 1    | 0000       |

| 0820                        | PR2              | 31:16     | _          |       | _      | _           | -     |       | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             |                  | 15:0      |            |       |        | I           |       |       |             | PR2< | 15:0>    |      | 1          |        | I    | 1     |                    |      | FFFF       |

| 0A00                        | T3CON            | 31:16     | _          |       | _      | _           |       |       |             | _    | _        | _    | _          | _      | _    | _     | -                  |      | 0000       |

|                             |                  | 15:0      | ON         | _     | SIDL   | _           |       |       |             | _    | TGATE    | ,    | TCKPS<2:0> | •      | _    | _     | TCS <sup>(2)</sup> |      | 0000       |

| 0A10                        | TMR3             | 31:16     | _          | _     | _      | _           |       | _     | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             | _                | 15:0      |            |       |        | 1           |       |       |             | TMR3 | <15:0>   |      |            |        | 1    |       | 1                  |      | 0000       |

| 0A20                        | PR3              | 31:16     | _          | _     | _      | _           |       | _     | _           | _    | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             |                  | 15:0      |            |       |        |             |       |       |             | PR3< | 15:0>    |      |            |        |      |       |                    |      | FFFF       |

| 0C00                        | T4CON            | 31:16     | _          | _     | _      | _           |       | _     | _           | _    | _        | _    | _          | _      | _    | _     | — (2)              |      | 0000       |

|                             |                  | 15:0      | ON         | _     | SIDL   | _           |       |       | _           | _    | TGATE    |      | TCKPS<2:0> | •      | T32  | _     | TCS <sup>(2)</sup> |      | 0000       |

| 0C10                        | TMR4             | 31:16     | _          |       | _      | _           |       |       | _           |      | _        | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             |                  | 15:0      |            |       |        |             |       |       |             | TMR4 | <15:0>   |      |            |        |      |       |                    |      | 0000       |

| 0C20                        | PR4              | 31:16     | _          |       | _      | _           |       |       | _           |      |          | _    | _          | _      | _    | _     | _                  | _    | 0000       |

|                             |                  | 15:0      |            |       |        |             |       |       |             | PR4< |          |      |            |        |      |       |                    |      | FFFF       |

| 0E00                        | T5CON            | 31:16     | -          | _     | —<br>— | _           |       | _     |             | _    |          | _    |            | _      | _    | _     | —<br>Too(2)        |      | 0000       |

|                             |                  | 15:0      | ON         |       | SIDL   | _           |       |       |             | _    | TGATE    |      | TCKPS<2:0> | •      | _    | _     | TCS <sup>(2)</sup> | _    | 0000       |

| 0E10                        | TMR5             | 31:16     | _          |       | _      | _           |       |       | _           |      |          | _    | _          | _      | _    | _     | _                  |      | 0000       |

|                             |                  | 15:0      |            |       |        |             |       |       |             | TMR5 |          |      |            |        |      |       |                    |      | 0000       |

| 0E20                        | PR5              | 31:16     | _          |       | _      | _           |       |       | _           |      | <u> </u> | _    | _          | _      | _    | _     | _                  |      | 0000       |

| Legend                      |                  | 15:0      | n value on |       |        | ted read as | (-1 D |       | wn in hevad | PR5< | 15:0>    |      |            |        |      |       |                    |      | FFFF       |

PIC32MX3XX/4XX

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> This bit is not available on 64-pin devices.

TABLE 4-23: PORTC REGISTERS MAP FOR PIC32MX320F128L, PIC32MX340F128L, PIC32MX360F256L, PIC32MX360F512L, PIC32MX440F128L, PIC32MX460F256L AND PIC32MX460F512L DEVICES ONLY<sup>(1)</sup>

| ess                         |                  |           |         |         |         |         |       |       |      | Ві   | ts   |      |      |        |        |        |        |      |            |

|-----------------------------|------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|--------|--------|--------|--------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3   | 18/2   | 17/1   | 16/0 | All Resets |

|                             | TRISC            | 31:16     | 1       | _       | _       | _       |       | _     | _    |      | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 6080                        | IKISC            | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | _    | _    | _    | TRISC4 | TRISC3 | TRISC2 | TRISC1 | _    | F01E       |

| 6090                        | PORTC            | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 0090                        | FORTC            | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | _    | _    | _    | _    | _    | RC4    | RC3    | RC2    | RC1    | _    | xxxx       |

| 60A0                        | LATC             | 31:16     | -       | -       | 1       | -       | 1     | 1     | _    | 1    | -    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| OUAU                        | LAIC             | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | -     | _    | _    | _    | _    | _    | LATC4  | LATC3  | LATC2  | LATC1  | _    | xxxx       |

| 60B0                        | ODCC             | 31:16     | _       | _       | 1       | _       | -     | _     | _    | 1    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| OODO                        | ODCC             | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | I     |       | _    | ı    | -    | _    | _    | ODCC4  | ODCC3  | ODCC2  | ODCC1  | _    | 0000       |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

TABLE 4-24: PORTC REGISTERS MAP FOR PIC32MX320F032H, PIC32MX320F064H, PIC32MX320F128H, PIC32MX340F128H, PIC32MX340F128H, PIC32MX340F256H, PIC32MX340F512H, PIC32MX420F032H, PIC32MX440F128H, PIC32MX440F256H AND PIC32MX440F512H DEVICES ONLY<sup>(1)</sup>

|                             |                  |           | DEVICE  | 0 0111  |         |         |       |       |      |      |      |      |      |      |      |      |      |      |            |

|-----------------------------|------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| ess                         |                  |           |         |         |         |         |       |       |      | Ві   | ts   |      |      |      |      |      |      |      | _          |

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 6080                        | TRISC            | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    |      | _    | _    |      | _    | _    | _    | _    | 0000       |

| 0000                        | INISC            | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | -    | _    | _    | ı    | _    | _    | _    | _    | F000       |

| 6090                        | PORTC            | 31:16     | -       | _       | _       | _       | _     | -     | -    | _    | 1    | _    | _    | 1    | -    | _    | _    | _    | 0000       |

| 0090                        | FORTC            | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx       |

| 60A0                        | LATC             | 31:16     | ı       | _       | _       | _       | _     | 1     | ı    | ı    | I    | ı    | _    | I    | 1    | _    | ı    | _    | 0000       |

| OUAU                        | LAIC             | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | 1     | I    | 1    | l    | 1    | _    | I    | 1    | _    | 1    | _    | xxxx       |

| 60B0                        | ODCC             | 31:16     | ı       | _       | _       | _       | _     | 1     | ı    | 1    | l    | 1    | _    | l    | 1    | _    | 1    | _    | 0000       |

| 0000                        | ODCC             | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

PIC32MX3XX/4XX

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

DS61143H-page 81

| TARIF 1-12. | DEVICE A | ND BEVISION | ID SUMMARY      |

|-------------|----------|-------------|-----------------|

| IADLE 4-42. | DEVICEA  | ND VEAISION | ID SUIVIIVIAN I |

| ess                       |                  | 9         |       |                  |       |       |       |       |      | Bi   | ts   |        |         |      |      |      |      |      |            |

|---------------------------|------------------|-----------|-------|------------------|-------|-------|-------|-------|------|------|------|--------|---------|------|------|------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5    | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| F220                      | DEVID            | 31:16     |       | VER-             | <3:0> |       |       |       |      |      |      | DEVID- | <27:16> |      |      |      |      |      | xxxx       |

| F220                      | DEVID            | 15:0      |       | DEVID<15:0> xxxx |       |       |       |       |      |      |      |        |         |      |      |      |      |      |            |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

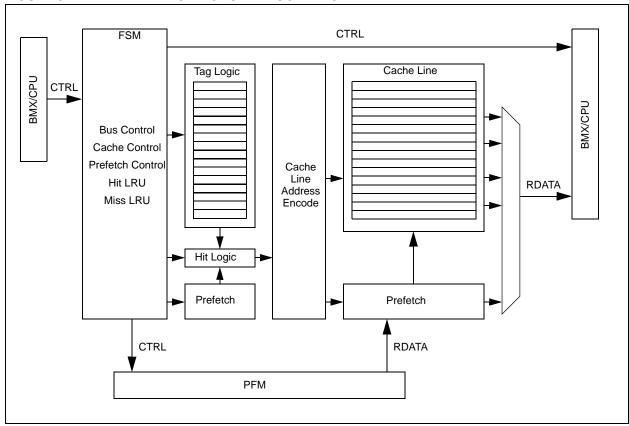

## 9.0 PREFETCH CACHE

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS61119) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

#### 9.1 Features

- 16 Fully Associative Lockable Cache Lines

- 16-byte Cache Lines

- Up to four Cache Lines Allocated to Data

- Two Cache Lines with Address Mask to hold repeated instructions

- Pseudo LRU replacement policy

- · All Cache Lines are software writable

- 16-byte parallel memory fetch

- · Predictive Instruction Prefetch

#### FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

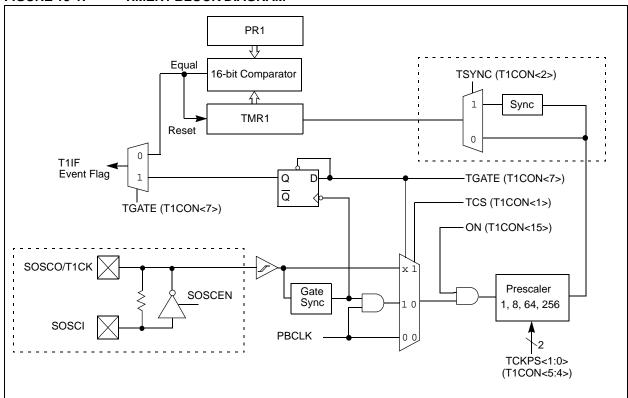

## 13.0 TIMER1

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS61105) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This family of PIC32MX devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Secondary Oscillator (Sosc) for real-time clock applications. The following modes are supported:

- · Synchronous Internal Timer

- · Synchronous Internal Gated Timer

- · Synchronous External Timer

- · Asynchronous External Timer

# 13.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

FIGURE 13-1: TIMER1 BLOCK DIAGRAM<sup>(1)</sup>

Note 1: The default state of the SOSCEN (OSCCON<1>) during a device Reset is controlled by the FSOSCEN bit in Configuration Word DEVCFG1.

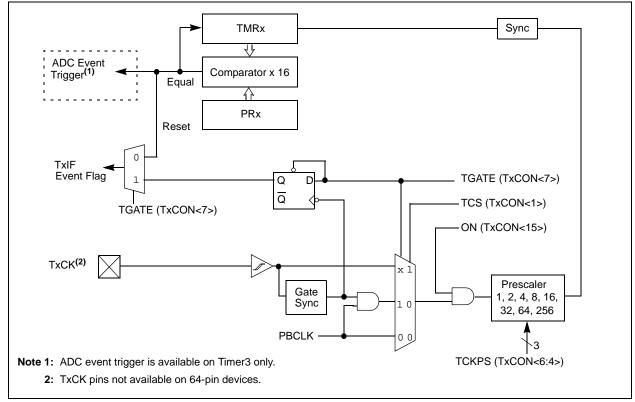

## **14.0 TIMER2/3 AND TIMER4/5**

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS61105) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This family of PIC32MX devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous Internal 16-bit Timer

- · Synchronous Internal 16-bit Gated Timer

- Synchronous External 16-bit Timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous Internal 32-bit Timer

- Synchronous Internal 32-bit Gated Timer

- Synchronous External 32-bit Timer

Throughout this chapter, references to registers TxCON, TMRx and PRx use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

# 14.1 Additional Supported Features

· Selectable clock prescaler

Note:

- · Timers operational during CPU Idle

- Time base for input capture and output compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 only)

- Fast bit manipulation using CLR, SET and INV registers

FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

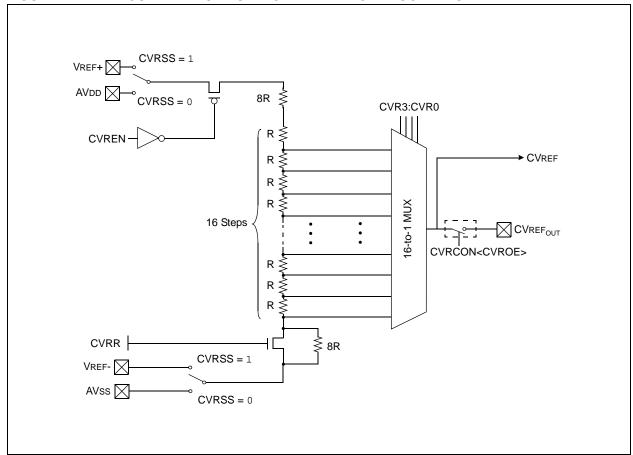

# 24.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. Refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS61109) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CVREF is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them.

A block diagram of the module is illustrated in Figure 24-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

FIGURE 24-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

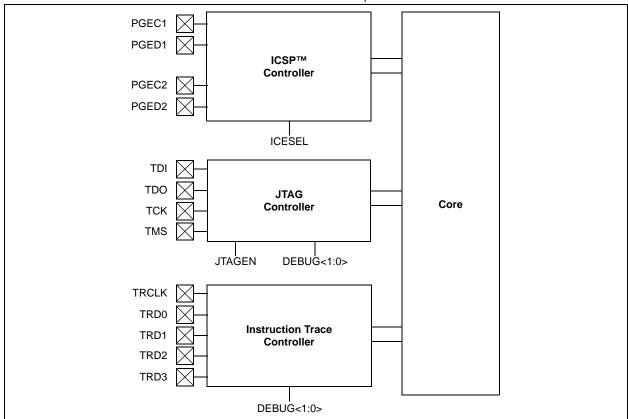

# 26.4 Programming and Diagnostics

PIC32MX3XX/4XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming™ (ICSP™) interfaces

- · Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32MX devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 26-3: BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

## 28.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers and dsPIC® digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>TM</sup> Assembler

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- · Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

# 28.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows® operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

TABLE 29-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA      | ACTERISTIC             | es                  | (unless  | d Operating Conditions: 2.3V totherwise stated) g temperature -40°C ≤TA ≤+85 -40°C ≤TA ≤+10 | °C for Indus              |       |                           |

|---------------|------------------------|---------------------|----------|---------------------------------------------------------------------------------------------|---------------------------|-------|---------------------------|

| Param.<br>No. | Typical <sup>(3)</sup> | Max.                | Units    | C                                                                                           | Conditions                |       |                           |

| Operating     | Current (IDI           | o) <sup>(1,2)</sup> |          |                                                                                             |                           |       |                           |

| DC20          | 8.5                    | 13                  | mA       | Code executing from Flash                                                                   | -40°C,<br>+25°C,<br>+85°C | _     | 4 MHz                     |

|               | 9                      | 15                  |          |                                                                                             | +105°C                    |       |                           |

| DC20c         | 4.0                    | _                   | mA       | Code executing from SRAM                                                                    | _                         |       |                           |

| DC21          | 23.5                   | 32                  | mA       | Code executing from Flash                                                                   |                           |       | 20 MHz                    |

| DC21c         | 16.4                   |                     | mA       | Code executing from SRAM                                                                    |                           |       | (Note 4)                  |

| DC22          | 48                     | 61                  | mA       | Code executing from Flash                                                                   | _                         | _     | 60 MHz                    |

| DC22c         | 45                     | _                   | mA       | Code executing from SRAM                                                                    |                           |       | (Note 4)                  |

| DC23          | 55                     | 75                  | mA       | Code executing from Flash                                                                   | -40°C,<br>+25°C,<br>+85°C | 2.3V  | 80 MHz                    |

|               | 60                     | 100                 |          |                                                                                             | +105°C                    |       |                           |

| DC23c         | 55                     | _                   | mA       | Code executing from SRAM                                                                    | _                         | _     |                           |

| DC24          | _                      | 100                 | μA       | _                                                                                           | -40°C                     |       |                           |

| DC24a         | _                      | 130                 | μA       | _                                                                                           | +25°C                     | 2.3V  |                           |

| DC24b         | _                      | 670                 | μA       | _                                                                                           | +85°C                     | 2.3 V |                           |

| DC24c         | _                      | 850                 | μA       | _                                                                                           | +105°C                    |       |                           |

| DC25          | 94                     | _                   | μA       | _                                                                                           | -40°C                     |       |                           |

| DC25a         | 125                    | _                   | μA       | _                                                                                           | +25°C                     | 3.3V  | 1000 (04 111 )            |

| DC25b         | 302                    | _                   | μA       | _                                                                                           | +85°C                     | 3.3V  | LPRC (31 kHz)<br>(Note 4) |

| DC25d         | 400                    | _                   | μA       | _                                                                                           | +105°C                    |       | (14010 4)                 |

| DC25c         | 71                     |                     | μΑ       | Code executing from SRAM                                                                    | _                         |       |                           |

| DC26          |                        | 110                 | μΑ       | _                                                                                           | -40°C                     |       |                           |

| DC26a         | _                      | 180                 | B0 μA +2 | +25°C                                                                                       | 3.6V                      |       |                           |

| DC26b         |                        |                     | μΑ       | _                                                                                           | +85°C                     | 3.0 v |                           |

| DC26c — 900   |                        | μΑ                  | _        | +105°C                                                                                      |                           |       |                           |

- Note 1: A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type as well as temperature can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows: Oscillator mode = EC+PLL with OSC1 driven by external square wave from rail to rail and PBCLK divisor = 1:8. CPU, Program Flash and SRAM data memory are operational, Program Flash memory Wait states = 7, program cache and prefetch are disabled and SRAM data memory Wait states = 1. All peripheral modules are disabled (ON bit = 0). WDT and FSCM are disabled. All I/O pins are configured as inputs and pulled to Vss. MCLR = VDD.

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

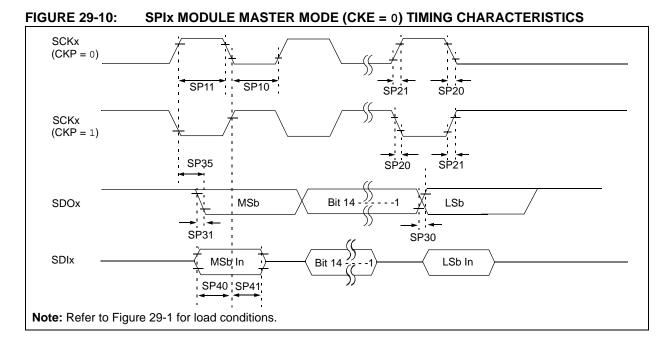

TABLE 29-28: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | ARACTERIST            | rics                                       | (unless o | d Operating<br>otherwise sta<br>g temperatu | ated)<br>ure -4 | 0°C ≤Ta : | <b>3V to 3.6V</b><br>≤+85°C for Industrial<br>≤+105°C for V-Temp |

|---------------|-----------------------|--------------------------------------------|-----------|---------------------------------------------|-----------------|-----------|------------------------------------------------------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.      | Typical <sup>(2)</sup>                      | Max.            | Units     | Conditions                                                       |

| SP10          | TscL                  | SCKx Output Low Time <sup>(3)</sup>        | Tsck/2    | _                                           | _               | ns        | _                                                                |

| SP11          | TscH                  | SCKx Output High Time <sup>(3)</sup>       | Tsck/2    | _                                           | _               | ns        | _                                                                |

| SP20          | TscF                  | SCKx Output Fall Time <sup>(4)</sup>       | _         | _                                           | _               | ns        | See parameter DO32                                               |

| SP21          | TscR                  | SCKx Output Rise Time <sup>(4)</sup>       | _         | _                                           | _               | ns        | See parameter DO31                                               |

| SP30          | TDOF                  | SDOx Data Output Fall Time(4)              | _         | _                                           | _               | ns        | See parameter DO32                                               |

| SP31          | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>  | _         | _                                           | _               | ns        | See parameter DO31                                               |

| SP35          | TscH2DoV,             | SDOx Data Output Valid after               | _         | _                                           | 15              | ns        | VDD > 2.7V                                                       |

|               | TscL2doV              | SCKx Edge                                  | _         | _                                           | 20              | ns        | VDD < 2.7V                                                       |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10        | _                                           | _               | ns        | _                                                                |

| SP41          | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10        | _                                           | _               | ns        | _                                                                |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

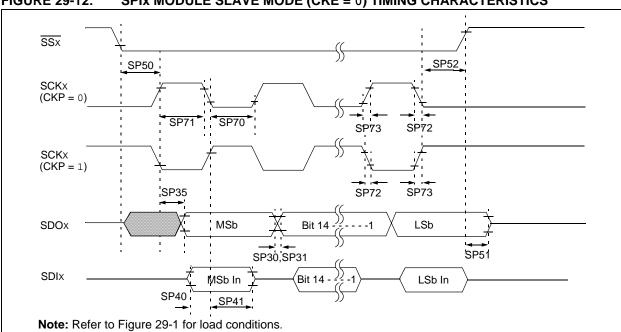

FIGURE 29-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 29-30: SPIx MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS             | Standard Operating Conditions: 2.3V to 3.6V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+105°C for V-Temp |           |                        |      |       |                    |  |

|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|------|-------|--------------------|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                                                                                                             | Min.      | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70          | TscL                  | SCKx Input Low Time(3)                                                                                                                                     | Tsck/2    |                        | -    | ns    | _                  |  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                                                                                                                        | Tsck/2    | _                      | _    | ns    | _                  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                                                                                                                       |           |                        |      | ns    | See parameter DO32 |  |

| SP73          | TscR                  | SCKx Input Rise Time                                                                                                                                       | _         | _                      | _    | ns    | See parameter DO31 |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time(4)                                                                                                                              | _         | _                      | _    | ns    | See parameter DO32 |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time(4)                                                                                                                              | _         | _                      | _    | ns    | See parameter DO31 |  |

| SP35          | TscH2DoV,<br>TscL2DoV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                  | _         | _                      | 15   | ns    | VDD > 2.7V         |  |

|               |                       |                                                                                                                                                            | _         | _                      | 20   | ns    | VDD < 2.7V         |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                 | 10        | _                      | _    | ns    | _                  |  |

| SP41          | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                  | 10        | _                      | _    | ns    | _                  |  |

| SP50          | TssL2scH,<br>TssL2scL | SSx ↓to SCKx ↑ or SCKx Input                                                                                                                               | 175       | _                      | _    | ns    | _                  |  |

| SP51          | TssH2DoZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(3)</sup>                                                                                                      | 5         | _                      | 25   | ns    | _                  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                                                                                                        | Tsck + 20 | _                      | _    | ns    | _                  |  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- 4: Assumes 50 pF load on all SPIx pins.

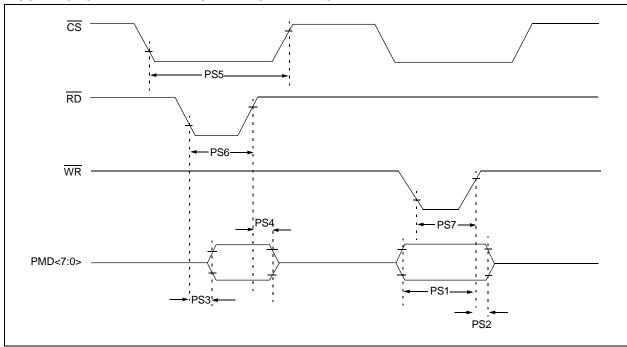

FIGURE 29-20: PARALLEL SLAVE PORT TIMING

TABLE 29-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CHARACTERISTICS |          |                                                       | Standard Operating Conditions: 2.3V to 3.6V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+105°C for V-Temp |         |      |       |            |  |

|--------------------|----------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol   | Characteristics <sup>(1)</sup>                        | Min.                                                                                                                                                       | Typical | Max. | Units | Conditions |  |

| PS1                | TdtV2wrH | Data In Valid before WR or CS Inactive (setup time)   | 20                                                                                                                                                         | _       | _    | ns    | _          |  |

| PS2                | TwrH2dtl | WR or CS Inactive to Data –<br>In Invalid (hold time) | 40                                                                                                                                                         |         | _    | ns    | _          |  |

| PS3                | TrdL2dtV | RD and CS Active to Data –<br>Out Valid               | _                                                                                                                                                          |         | 60   | ns    | _          |  |

| PS4                | TrdH2dtI | RD Active or CS Inactive to Data – Out Invalid        | 0                                                                                                                                                          |         | 10   | ns    | _          |  |

| PS5                | Tcs      | CS Active Time                                        | Трв + 40                                                                                                                                                   | _       |      | ns    | _          |  |

| PS6                | Twr      | WR Active Time                                        | TpB + 25                                                                                                                                                   |         | _    | ns    |            |  |

| PS7                | TRD      | RD Active Time                                        | TpB + 25                                                                                                                                                   |         | 1    | ns    | _          |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

#### 30.0 PACKAGING INFORMATION

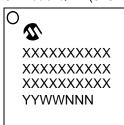

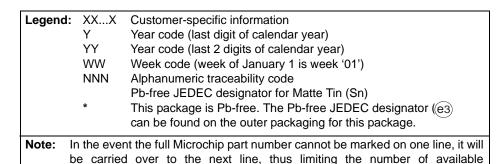

# 30.1 Package Marking Information

64-Lead TQFP (10x10x1 mm)

100-Lead TQFP (12x12x1 mm)

64-Lead QFN (9x9x0.9 mm)

121-Lead XBGA (10x10x1.1 mm)

Example

Example

Example

Example

characters for customer-specific information.

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support