Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | -                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx460f256l-80v-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 2: PIC32MX USB – FEATURES

|                 | USB  |                         |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

|-----------------|------|-------------------------|-----|-------------------------|------------------|------------------------|------------------------------|-------------------------------|------|-------|-----------------------------|-----------------|-------------|---------|------|

| Device          | Pins | Packages <sup>(2)</sup> | MHz | Program Memory (KB)     | Data Memory (KB) | Timers/Capture/Compare | Programmable DMA<br>Channels | Dedicated USB DMA<br>Channels | VREG | Trace | EUART/SPI/I <sup>2</sup> C™ | 10-bit ADC (ch) | Comparators | dSd/dWd | JTAG |

| PIC32MX420F032H | 64   | PT, MR                  | 40  | 32 + 12 <sup>(1)</sup>  | 8                | 5/5/5                  | 0                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F128H | 64   | PT, MR                  | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F256H | 64   | PT, MR                  | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

| PIC32MX440F512H | 64   | PT, MR                  | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/1/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

| PIC32MX440F128L | 121  | BG                      | 80  | 128 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | No    | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     |                         |                  |                        |                              |                               |      |       |                             |                 |             |         |      |

| PIC32MX460F256L | 121  | BG                      | 80  | 256 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

|                 | 100  | PT                      |     | (1)                     |                  |                        |                              | _                             |      |       |                             |                 | _           |         |      |

| PIC32MX460F512L | 121  | BG                      | 80  | 512 + 12 <sup>(1)</sup> | 32               | 5/5/5                  | 4                            | 2                             | Yes  | Yes   | 2/2/2                       | 16              | 2           | Yes     | Yes  |

Legend: PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB Boot Flash memory.

2: See Legend for an explanation of the acronyms. See Section 30.0 "Packaging Information" for details.

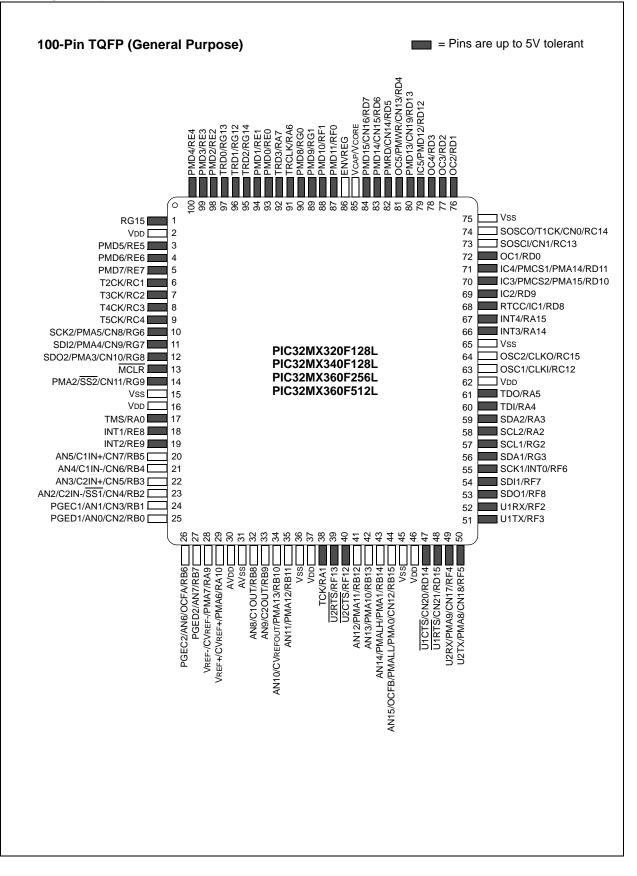

## **Pin Diagrams (Continued)**

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide" DS51331

- "Using MPLAB<sup>®</sup> ICD 2" (poster) DS51265

- "MPLAB<sup>®</sup> ICD 2 Design Advisory" DS51566

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms. Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternately, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0** "**Oscillator Configuration**" for details).

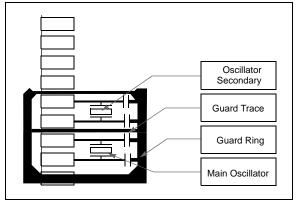

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

NOTES:

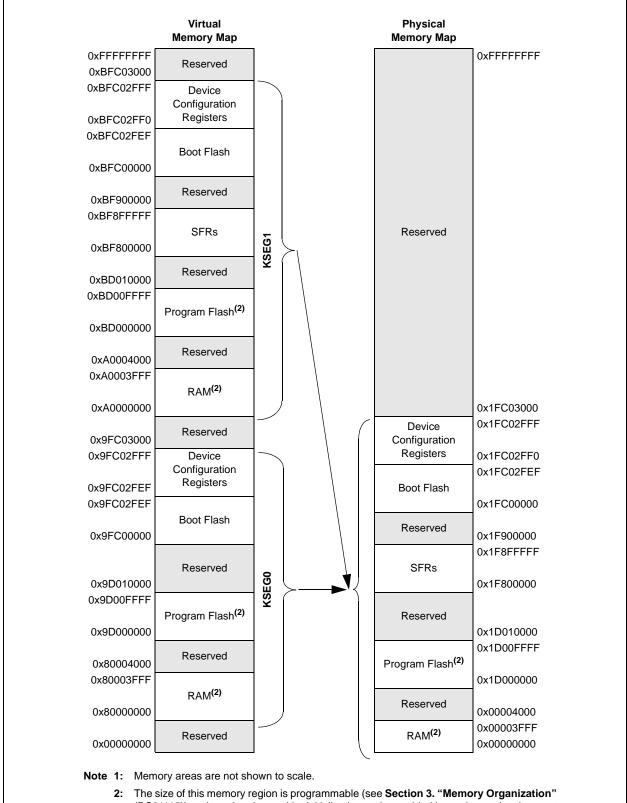

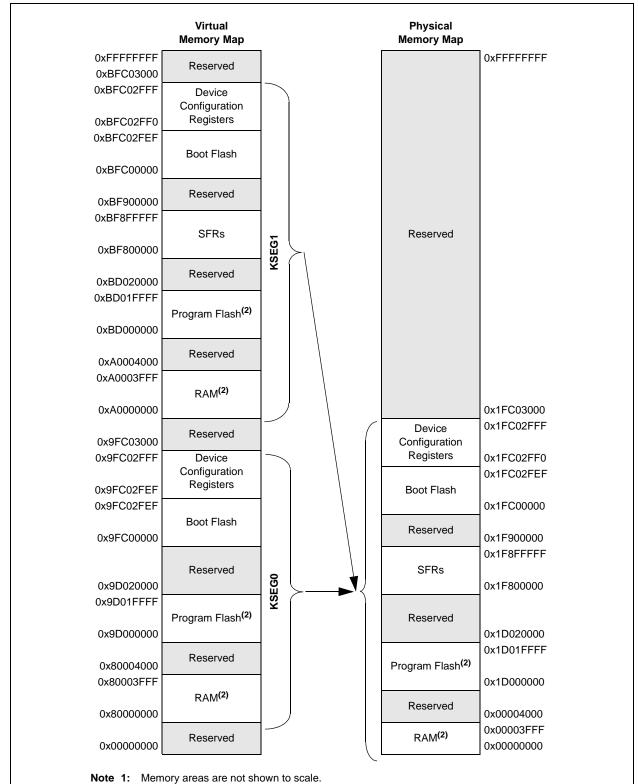

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX320F064H DEVICE<sup>(1)</sup>

(DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

# FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX320F128H AND PIC32MX320F128L DEVICES<sup>(1)</sup>

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| SSS                         |                        |               |         |         |         |               |                          |        |                         | В        | its        |               |            |             |            |        |            |        |            |

|-----------------------------|------------------------|---------------|---------|---------|---------|---------------|--------------------------|--------|-------------------------|----------|------------|---------------|------------|-------------|------------|--------|------------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15   | 30/14   | 29/13   | 28/12         | 27/11                    | 26/10  | 25/9                    | 24/8     | 23/7       | 22/6          | 21/5       | 20/4        | 19/3       | 18/2   | 17/1       | 16/0   | All Recets |

|                             | INTCON                 | 31:16         | _       | —       | _       | _             | _                        | _      | —                       | _        | —          | —             | _          | —           | —          | —      | _          | SS0    | 00         |

| 1000                        | INTCON                 | 15:0          | —       | —       | —       | MVEC          | —                        |        | TPC<2:0>                | •        | —          | —             | -          | INT4EP      | INT3EP     | INT2EP | INT1EP     | INT0EP | 00         |

| 1010                        | INTSTAT <sup>(2)</sup> | 31:16         | _       | _       | -       | _             | -                        | _      |                         | —        | _          | _             | -          | _           | _          | _      | _          | _      | 00         |

| 1010                        | INTSTAT                | 15:0          | _       | —       | —       | _             |                          |        | SRIPL<2:0>              | <b>`</b> | _          | —             |            |             | VEC        | <5:0>  |            |        | 00         |

| 1020                        | IPTMR                  | 31:16<br>15:0 |         |         |         |               |                          |        |                         | IPTMF    | <31:0>     |               |            |             |            |        |            |        | 00         |

|                             | 1500                   | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF | <b>U1TXIF</b> | U1RXIF                   | U1EIF  | _                       | _        | _          | OC5IF         | IC5IF      | T5IF        | INT4IF     | OC4IF  | IC4IF      | T4IF   | 00         |

| 1030                        | IFS0                   | 15:0          | INT3IF  | OC3IF   | IC3IF   | T3IF          | INT2IF                   | OC2IF  | IC2IF                   | T2IF     | INT1IF     | OC1IF         | IC1IF      | T1IF        | INT0IF     | CS1IF  | CS0IF      | CTIF   | 00         |

| 1010                        | IFS1                   | 31:16         | _       | —       | _       | _             | _                        |        | USBIF                   | FCEIF    | -          | _             | -          | —           | DMA3IF     | DMA2IF | DMA1IF     | DMA0IF | 00         |

| 1040                        | IF51                   | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF | I2C2SIF       | I2C2BIF                  | U2TXIF | U2RXIF                  | U2EIF    | SPI2RXIF   | SPI2TXIF      | SPI2EIF    | CMP2IF      | CMP1IF     | PMPIF  | AD1IF      | CNIF   | 00         |

| 1060                        | IEC0                   | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE | U1TXIE        | U1RXIE                   | U1EIE  | —                       | -        | -          | OC5IE         | IC5IE      | T5IE        | INT4IE     | OC4IE  | IC4IE      | T4IE   | 00         |

| 1060                        | IEC0                   | 15:0          | INT3IE  | OC3IE   | IC3IE   | T3IE          | INT2IE                   | OC2IE  | IC2IE                   | T2IE     | INT1IE     | OC1IE         | IC1IE      | T1IE        | INT0IE     | CS1IE  | CS0IE      | CTIE   | 00         |

| 1070                        |                        | 31:16         | —       | —       | _       | —             | _                        |        | USBIE                   | FCEIE    | —          | _             | -          | —           | DMA3IE     | DMA2IE | DMA1IE     | DMA0IE | 00         |

| 1070                        | IEC1                   | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE | I2C2SIE       | I2C2BIE                  | U2TXIE | U2RXIE                  | U2EIE    | SPI2RXIE   | SPI2TXIE      | SPI2EIE    | CMP2IE      | CMP1IE     | PMPIE  | AD1IE      | CNIE   | 00         |

| 1090                        | IPC0                   | 31:16         | —       | _       | _       | INT0IP<2:0>   |                          | INTOIS | S<1:0>                  | _        | _          | _             | CS1IP<2:0> |             |            | CS1IS  | <1:0>      | 00     |            |

| 1090                        | IPCU                   | 15:0          | —       | —       | —       |               | CS0IP<2:0>               |        | CSOIS                   | S<1:0>   | —          | —             | —          | CTIP<2:0>   |            |        | CTIS<1:0>  |        | 00         |

| 10A0                        | IPC1                   | 31:16         | —       | -       | -       |               | NT1IP<2:0>               |        | INT1IS                  | S<1:0>   | _          | _             | -          | OC1IP<2:0>  |            |        | OC1IS<1:0> |        | 00         |

| IUAU                        | 1 01                   | 15:0          | —       | _       | _       |               | IC1IP<2:0>               |        | IC1IS                   | 5<1:0>   |            | — — T1IP<2:0> |            |             | T1IS<1:0>  |        | 00         |        |            |

| 10B0                        | IPC2                   | 31:16         | —       | _       | _       |               | NT2IP<2:0>               |        | INT2IS<1:0>             |          | -          | _             |            |             | OC2IP<2:0> |        | OC2IS<1:0> |        | 00         |

| I O D O                     | 11 02                  | 15:0          | _       | —       | —       |               | IC2IP<2:0>               |        | IC2IS<1:0>              |          | —          | —             | _          | T2IP<2:0>   |            | T2IS-  | <1:0>      | 00     |            |

| 10C0                        | IPC3                   | 31:16         | —       | —       | _       |               | NT3IP<2:0>               |        | INT3IS<1:0> — — — OC3IP |          | OC3IP<2:0> |               | OC3IS      | 5<1:0>      | 00         |        |            |        |            |

| 1000                        |                        | 15:0          | _       | _       | _       |               | IC3IP<2:0> IC3IS<1:0> T3 |        | T3IP<2:0>               |          | T3IS-      |               | 00         |             |            |        |            |        |            |

| 10D0                        | IPC4                   | 31:16         | _       | _       | _       |               | NT4IP<2:0>               |        | INT4I                   | S<1:0>   | —          | —             | _          |             | OC4IP<2:0> | •      | OC4IS      | 5<1:0> | 00         |

|                             |                        | 15:0          | —       | —       | —       |               | IC4IP<2:0>               |        | IC4IS                   | 5<1:0>   | —          | —             | -          |             | T4IP<2:0>  |        | T4IS-      |        | 00         |

| 10E0                        | IPC5                   | 31:16         | —       | _       | —       | —             | —                        | —      | —                       | —        | —          | —             | —          |             | OC5IP<2:0> |        | OC5IS      | -      | 00         |

|                             |                        | 15:0          | _       | —       | —       |               | IC5IP<2:0>               |        |                         | 5<1:0>   | —          | —             | _          |             | T5IP<2:0>  |        | T5IS-      | -      | 00         |

| 10F0                        | IPC6                   | 31:16         | —       | _       | _       |               | AD1IP<2:0>               |        |                         | S<1:0>   | _          | —             | _          |             | CNIP<2:0>  |        | CNIS       |        | 00         |

|                             |                        | 15:0          | _       | —       | —       |               | 2C1IP<2:0>               |        |                         | S<1:0>   | —          | —             | _          |             | U1IP<2:0>  |        | U1IS-      | -      | 00         |

| 1100                        | IPC7                   | 31:16         | _       | —       | —       |               | SPI2IP<2:0>              |        | -                       | S<1:0>   | —          | —             |            |             | CMP2IP<2:0 |        | CMP2I      |        | 00         |

|                             |                        | 15:0          | _       | —       | —       |               | CMP1IP<2:0>              |        |                         | S<1:0>   | —          | —             |            | PMPIP<2:0>  |            | PMPIS  |            | 00     |            |

| 1110                        | IPC8                   | 31:16         | —       | _       | _       |               | RTCCIP<2:0>              |        |                         | S<1:0>   | —          | —             | _          | FSCMIP<2:0> |            | FSCMI  |            | 00     |            |

|                             |                        | 15:0          | _       | _       | _       |               | I2C2IP<2:0>              |        |                         | S<1:0>   | -          | _             | _          | U2IP<2:0>   |            |        | U2IS<1:0>  |        | 00         |

| 1120                        | IPC9                   | 31:16         | _       | —       | —       |               | MA3IP<2:0:               |        | -                       | S<1:0>   | —          | —             | —          | DMA2IP<2:0> |            | DMA2I  |            | 00     |            |

|                             |                        | 15:0          | _       | _       | _       |               | MA1IP<2:0:               | >      | DMA1                    | S<1:0>   | -          | _             | -          | [           | DMA0IP<2:0 |        | DMA0I      | 5<1:0> | 00         |

|                             | IPC11                  | 31:16         |         | _       | _       |               | _                        | —      |                         |          |            |               |            |             |            |        |            |        | 00         |

Except where noted, all registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8, and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

This register does not have associated CLR, SET, and INV registers. 2:

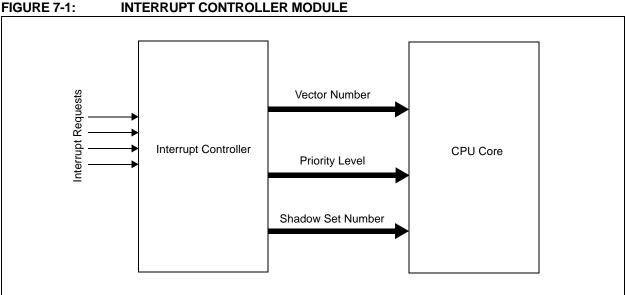

#### 7.0 INTERRUPT CONTROLLER

- **Note 1:** This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS61108) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

PIC32MX3XX/4XX devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX3XX/4XX interrupts module includes the following features:

- · Up to 96 interrupt sources

- Up to 64 interrupt vectors

- · Single and Multi-Vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Module Freeze in Debug mode

- Seven user-selectable priority levels for each vector

- · Four user-selectable subpriority levels within each priority

- Dedicated shadow set for highest priority level

- Software can generate any interrupt

- · User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

#### Several of the registers cited in this section are not in the interrupt controller module. These registers (and Note: bits) are associated with the CPU. Details about them are available in Section 3.0 "CPU".

To avoid confusion, a typographic distinction is made for registers in the CPU. The register names in this section, and all other sections of this manual, are signified by uppercase letters only. The CPU register names are signified by upper and lowercase letters. For example, INTSTAT is an Interrupts register; whereas, IntCtl is a CPU register.

### FIGURE 7-1:

### © 2011 Microchip Technology Inc.

NOTES:

# 11.0 USB ON-THE-GO (OTG)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS61126) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 fullspeed and low-speed embedded host, full-speed device, or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32MX USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers, and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32MX USB module includes the following features:

- USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB OTG Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- Integrated USB Transceiver

- Transaction Handshaking Performed by Hardware

- Endpoint Buffering Anywhere in System RAM

- Integrated DMA to Access System RAM and Flash

Note: The implementation and use of the USB specifications, as well as other third-party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

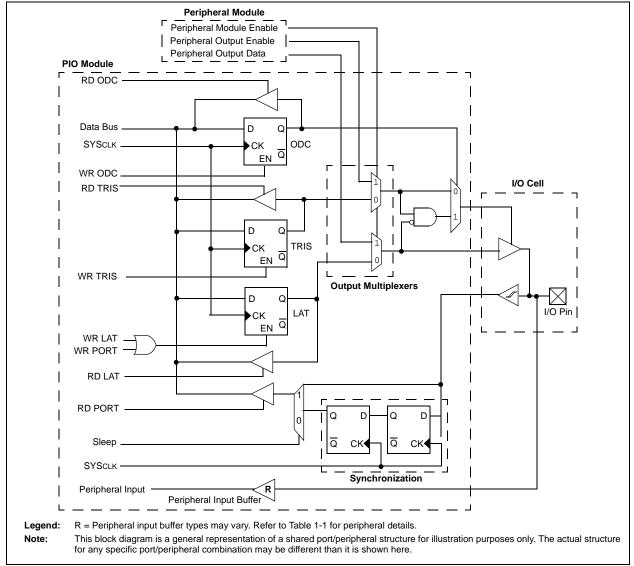

# 12.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS61120) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Following are some of the key features of this module:

- Individual Output Pin Open-drain Enable/Disable

- Individual Input Pin Weak Pull-up Enable/Disable

- Monitor Selective Inputs and Generate Interrupt when Change in Pin State is Detected

- Operation during CPU Sleep and Idle modes

- Fast Bit Manipulation using CLR, SET and INV Registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

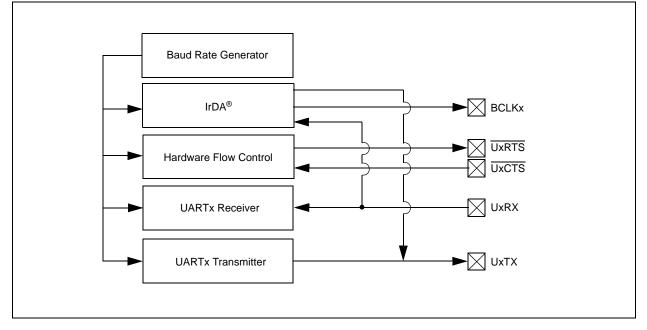

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS61107) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The UART module is one of the serial I/O modules available in PIC32MX3XX/4XX family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols such as RS-232, RS-485, LIN 1.2 and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 20 Mbps at 80 MHz

- 4-level-deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-level-deep FIFO Receive Data Buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

## FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

## 28.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 28.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 28.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 28.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 28.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## TABLE 29-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                                                                  | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                        |                            |            |                                         |  |  |  |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|------------|-----------------------------------------|--|--|--|

| Param.<br>No.      | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max.                       | Units      | Conditions                              |  |  |  |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                  |                        | <sub>50</sub> (3)<br>50(5) | MHz<br>MHz | EC (Note 5)<br>ECPLL (Note 4)           |  |  |  |

| OS11               |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                        | —                      | 10                         | MHz        | XT (Note 5)                             |  |  |  |

| OS12               |               |                                                                                                                  | 4                                                                                                                                                                                        | _                      | 10                         | MHz        | XTPLL<br>(Notes 4, 5)                   |  |  |  |

| OS13               |               |                                                                                                                  | 10                                                                                                                                                                                       | —                      | 25                         | MHz        | HS (Note 5)                             |  |  |  |

| OS14               |               |                                                                                                                  | 10                                                                                                                                                                                       | _                      | 25                         | MHz        | HSPLL<br>(Notes 4, 5)                   |  |  |  |

| OS15               |               |                                                                                                                  | 32                                                                                                                                                                                       | 32.768                 | 100                        | kHz        | Sosc (Note 5)                           |  |  |  |

| OS20               | Tosc          | Tosc = 1/Fosc = Tcy <sup>(2)</sup>                                                                               | _                                                                                                                                                                                        |                        | _                          | _          | See parameter<br>OS10 for Fosc<br>value |  |  |  |

| OS30               | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                              | —                      | _                          | ns         | EC (Note 5)                             |  |  |  |

| OS31               | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                        | —                      | 0.05 x Tosc                | ns         | EC (Note 5)                             |  |  |  |

| OS40               | Тоят          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                        | 1024                   | _                          | Tosc       | (Note 5)                                |  |  |  |

| OS41               | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                        | 2                      |                            | ms         | (Note 5)                                |  |  |  |

| OS42               | Gм            | External Oscillator<br>Transconductance                                                                          | —                                                                                                                                                                                        | 12                     |                            | mA/V       | VDD = 3.3V<br>TA = +25°C<br>(Note 5)    |  |  |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- **3:** 40 MHz maximum for PIC32MX320F032H and PIC32MX420F032H devices.

- **4:** PLL input requirements: 4 MHz ≤FPLLIN ≤5 MHz (use PLL prescaler to reduce FOSC). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 5: This parameter is characterized, but not tested in manufacturing.

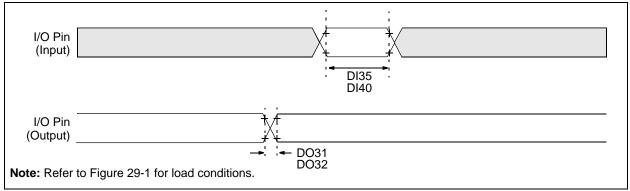

## FIGURE 29-3: I/O TIMING CHARACTERISTICS

## TABLE 29-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                              | Standard Ope<br>(unless otherw<br>Operating tem | vise stated)<br>perature | -40°C ≤TA ≤++<br>-40°C ≤TA ≤++ | 85°C for Ind |         |            |

|--------------------|--------|------------------------------|-------------------------------------------------|--------------------------|--------------------------------|--------------|---------|------------|

| Param.<br>No.      | Symbol | Characteris                  | stics <sup>(2)</sup>                            | Min.                     | Typical <sup>(1)</sup>         | Max.         | Units   | Conditions |

| DO31               | TIOR   | Port Output Rise Tir         | ne                                              | _                        | 5                              | 15           | ns      | Vdd < 2.5V |

|                    |        |                              |                                                 | _                        | 5                              | 10           | ns      | VDD > 2.5V |

| DO32               | TIOF   | Port Output Fall Tim         | ne                                              | —                        | 5                              | 15           | ns      | Vdd < 2.5V |

|                    |        |                              |                                                 | _                        | 5                              | 10           | ns      | VDD > 2.5V |

| DI35               | TINP   | INTx Pin High or Low Time    |                                                 | 10                       | _                              | _            | ns      |            |

| DI40               | Trbp   | CNx High or Low Time (input) |                                                 | 2                        | _                              | _            | TSYSCLK |            |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

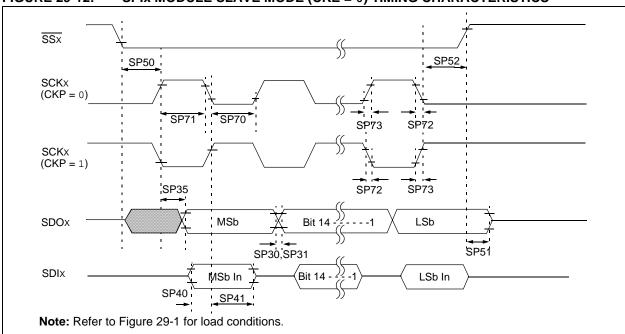

### FIGURE 29-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

### TABLE 29-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS    |                                                               |           | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |      |       |                    |  |  |  |

|---------------|-----------------------|---------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                | Min.      | Typical <sup>(2)</sup>                                                                                                                                                                   | Max. | Units | Conditions         |  |  |  |

| SP70          | TscL                  | SCKx Input Low Time <sup>(3)</sup>                            | Тѕск/2    | _                                                                                                                                                                                        |      | ns    | _                  |  |  |  |

| SP71          | TscH                  | SCKx Input High Time <sup>(3)</sup>                           | Тѕск/2    | _                                                                                                                                                                                        |      | ns    | —                  |  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                          |           | _                                                                                                                                                                                        |      | ns    | See parameter DO32 |  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                          | _         | _                                                                                                                                                                                        | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                     |           |                                                                                                                                                                                          |      | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>                     | _         | _                                                                                                                                                                                        | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                  | _         | —                                                                                                                                                                                        | 15   | ns    | Vdd > 2.7V         |  |  |  |

|               | TscL2doV              | SCKx Edge                                                     | _         | —                                                                                                                                                                                        | 20   | ns    | Vdd < 2.7V         |  |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                    | 10        | _                                                                                                                                                                                        | —    | ns    | —                  |  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                     | 10        | _                                                                                                                                                                                        | _    | ns    | _                  |  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow $ to SCKx $\uparrow$ or SCKx Input | 175       | _                                                                                                                                                                                        | _    | ns    | _                  |  |  |  |

| SP51          | TssH2doZ              | SSx                                                           | 5         | —                                                                                                                                                                                        | 25   | ns    | —                  |  |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                           | Тѕск + 20 | _                                                                                                                                                                                        |      | ns    | —                  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

| AC CHARACTERISTICS |           |                                                                                         | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |                        |         |       |                                                                          |  |  |  |

|--------------------|-----------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|-------|--------------------------------------------------------------------------|--|--|--|

| Param.<br>No.      | Symbol    | Characteristics                                                                         | Min.                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                               |  |  |  |

| Clock P            | arameter  | S                                                                                       |                                                                                                                                                                                          |                        |         |       | ·                                                                        |  |  |  |

| AD50               | Tad       | Analog-to-Digital Clock Period                                                          | 65                                                                                                                                                                                       | _                      | —       | ns    | See Table 29-35 and Note 2                                               |  |  |  |

| AD51               | TRC       | Analog-to-Digital Internal RC<br>Oscillator Period                                      | —                                                                                                                                                                                        | 250                    | —       | ns    | See Note 3                                                               |  |  |  |

| Conver             | sion Rate |                                                                                         |                                                                                                                                                                                          |                        |         |       |                                                                          |  |  |  |

| AD55               | TCONV     | Conversion Time                                                                         | —                                                                                                                                                                                        | 12 Tad                 | —       |       | —                                                                        |  |  |  |

| AD56               |           |                                                                                         | —                                                                                                                                                                                        | —                      | 1000    | KSPS  | AVDD = 3.0V to 3.6V                                                      |  |  |  |

|                    | (Sar      | (Sampling Speed)                                                                        |                                                                                                                                                                                          | _                      | 400     | KSPS  | AVDD = 2.5V to 3.6V                                                      |  |  |  |

| AD57               | TSAMP     | Sample Time                                                                             | 1 Tad                                                                                                                                                                                    |                        | —       | —     | TSAMP must be $\geq$ 132 ns.                                             |  |  |  |

| Timing             | Paramete  | rs                                                                                      | 1                                                                                                                                                                                        |                        | II      |       | I                                                                        |  |  |  |

| AD60               | TPCS      | Conversion Start from Sample<br>Trigger                                                 | _                                                                                                                                                                                        | 1.0 Tad                | —       |       | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected.<br>See Note 3 |  |  |  |

| AD61               | TPSS      | Sample Start from Setting<br>Sample (SAMP) bit                                          | 0.5 Tad                                                                                                                                                                                  | —                      | 1.5 TAD | —     | —                                                                        |  |  |  |

| AD62               | TCSS      | Conversion Completion to<br>Sample Start (ASAM = 1)                                     | —                                                                                                                                                                                        | 0.5 Tad                | —       | _     | See Note 3                                                               |  |  |  |

| AD63               | TDPU      | Time to Stabilize Analog Stage<br>from Analog-to-Digital OFF to<br>Analog-to-Digital ON | —                                                                                                                                                                                        | —                      | 2       | μs    | See Note 3                                                               |  |  |  |

## TABLE 29-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

# TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                            | Update Description                                                                                                                                                                             |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "Special Features"         | Modified bit names and locations in <b>Register 26-5</b> " <b>DEVID: Device and Revision ID Register</b> ".                                                                                    |

|                                         | Replaced "TSTARTUP" with "TPU", and "64-ms nominal delay" with "TPWRT", in Section 26.3.1 "On-Chip Regulator and POR".                                                                         |

|                                         | The information that appeared in the Watchdog Timer and the Programming and Diagnostics sections of 61143E version of this data sheet has been incorporated into the Special Features section: |

|                                         | <ul> <li>Section 26.2 "Watchdog Timer (WDT)"</li> </ul>                                                                                                                                        |

|                                         | Section 26.4 "Programming and Diagnostics"                                                                                                                                                     |

| Section 29.0 "Electrical                | Added the 64-Lead QFN package to Table 29-3.                                                                                                                                                   |

| Characteristics"                        | Updated data in Table 29-5.                                                                                                                                                                    |

|                                         | Updated data in Table 29-7.                                                                                                                                                                    |

|                                         | Updated data in Table 29-4, Table 29-5, Table 29-7 and Table 29-8.                                                                                                                             |

|                                         | Updated data in Table 29-11.                                                                                                                                                                   |

|                                         | Added OS42 parameter to Table 29-17.                                                                                                                                                           |

|                                         | Replaced Table 29-23.                                                                                                                                                                          |

|                                         | Replaced Table 29-24.                                                                                                                                                                          |

|                                         | Replaced Table 29-25.                                                                                                                                                                          |

|                                         | Updated Table 29-36.                                                                                                                                                                           |

| Section 30.0 "Packaging<br>Information" | Added 64-Lead QFN package marking information to <b>Section 30.1 "Package Marking Information"</b> .                                                                                           |

|                                         | Added the 64-Lead QFN (MR) package drawing and land pattern to <b>Section 30.2 "Package Details"</b> .                                                                                         |

| "Product Identification System"         | Added the MR package designator for the 64-Lead (9x9x0.9) QFN.                                                                                                                                 |