Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx460f512lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U S A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-61341-149-0

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mnufacture of development systems is ISO 9001:2000 certified.

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX3XX/4XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP/VCORE

- (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.8 "External Oscillator Pins")

- Additionally, the following pins may be required:

- VREF+/VREF- pins used when external voltage reference for ADC module is implemented

**Note:** The AVDD and AVSS pins must be connected independent of ADC use and ADC voltage reference source.

#### 2.2 Decoupling Capacitors

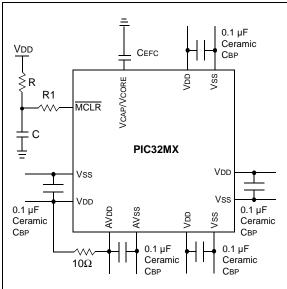

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

#### 2.3 Capacitor on Internal Voltage Regulator (VCAP/VCORE)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (< 1 Ohm) capacitor is required on the VCAP/VCORE pin, which is used to stabilize the internal voltage regulator output. The VCAP/VCORE pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 29.0** "**Electrical Characteristics**" for additional information on CEFC specifications. This mode is enabled by connecting the ENVREG pin to VDD.

#### 2.3.2 EXTERNAL REGULATOR MODE

In this mode the core voltage is supplied externally through the VCORE/VCAP pin. A low-ESR capacitor of 10  $\mu F$  is recommended on the VCAP/VCORE pin. This mode is enabled by grounding the ENVREG pin.

The placement of this capacitor should be close to the VCAP/VCORE. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 26.3** "**On-Chip Voltage Regulator**" for details.

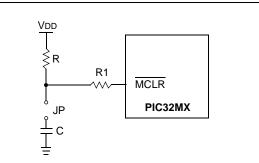

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Note 1: R ≤10 kΩ is recommended. A suggested starting value is 10 kΩ Ensure that the MCLR pin VIH and VIL specifications are met.

- <u>R1 ≤ 470Ω</u> will limit any current flowing into MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

- **3:** The capacitor can be sized to prevent unintentional resets from brief glitches or to extend the device reset period during POR.

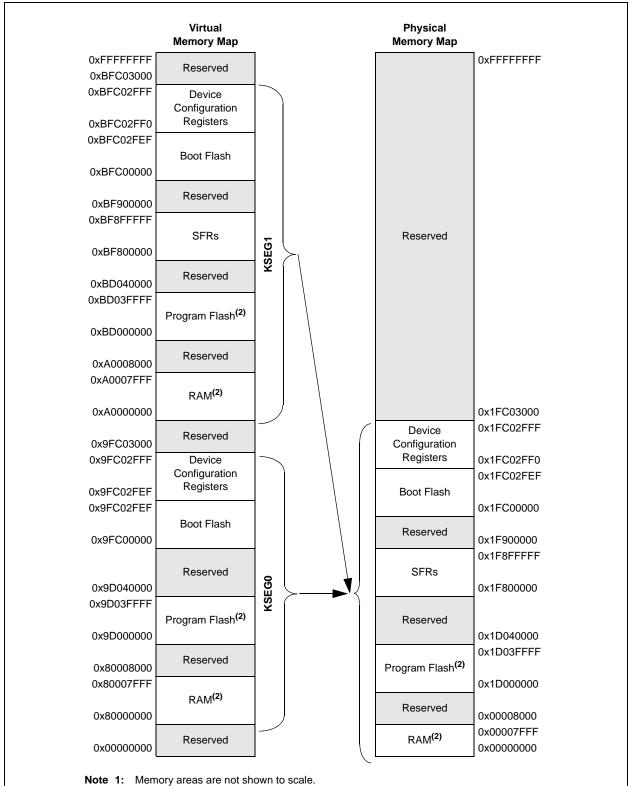

#### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX340F256H, PIC32MX360F256L, PIC32MX440F256H AND PIC32MX460F256L DEVICES<sup>(1)</sup>

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS61115)) and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| SS                          |                        |               |                   |                  |                  |                |                           |                |                 | В                | its           |                |                |              |                          |                |                |              |            |

|-----------------------------|------------------------|---------------|-------------------|------------------|------------------|----------------|---------------------------|----------------|-----------------|------------------|---------------|----------------|----------------|--------------|--------------------------|----------------|----------------|--------------|------------|

| VIITUAI Address<br>(BF88_#) | Register<br>Name       | Bit Range     | 31/15             | 30/14            | 29/13            | 28/12          | 27/11                     | 26/10          | 25/9            | 24/8             | 23/7          | 22/6           | 21/5           | 20/4         | 19/3                     | 18/2           | 17/1           | 16/0         | All Pacate |

| 1000                        | INTCON                 | 31:16         | _                 | _                | _                | —              | _                         | —              |                 | —                | —             | —              | _              | —            | -                        | -              | -              | SS0          | 00         |

|                             |                        | 15:0<br>31:16 | _                 | _                |                  | MVEC           |                           | _              | TPC<2:0>        |                  |               |                |                | INT4EP       | INT3EP                   | INT2EP         | INT1EP         | INT0EP       | 0          |

| 010                         | INTSTAT <sup>(2)</sup> | 15:0          | _                 | _                | _                |                |                           |                | SRIPL<2:0>      |                  | _             | _              |                |              | VEC-                     | <5:0>          |                |              | 0          |

| 020                         | IPTMR                  | 31:16<br>15:0 |                   |                  |                  |                |                           | 1              |                 | IPTMF            | ₹<31:0>       |                |                |              |                          |                |                |              | 0          |

| 030                         | IFS0                   | 31:16<br>15:0 | I2C1MIF<br>INT3IF | I2C1SIF<br>OC3IF | I2C1BIF<br>IC3IF | U1TXIF<br>T3IF | U1RXIF<br>INT2IF          | U1EIF<br>OC2IF | –<br>IC2IF      | —<br>T2IF        | —<br>INT1IF   | OC5IF<br>OC1IF | IC5IF<br>IC1IF | T5IF<br>T1IF | INT4IF<br>INT0IF         | OC4IF<br>CS1IF | IC4IF<br>CS0IF | T4IF<br>CTIF | 0          |

| 040                         | IFS1                   | 31:16<br>15:0 | - RTCCIF          | - FSCMIF         | –<br>I2C2MIF     | –<br>I2C2SIF   | –<br>I2C2BIF              | U2TXIF         | USBIF<br>U2RXIF | FCEIF<br>U2EIF   | —<br>SPI2RXIF | -<br>SPI2TXIF  | —<br>SPI2EIF   | —<br>CMP2IF  | —<br>CMP1IF              | –<br>PMPIF     | AD1IF          | —<br>CNIF    | 0          |

| 060                         | IEC0                   | 31:16         | I2C1MIE           | I2C1SIE          | I2C1BIE          | U1TXIE         | U1RXIE                    | U1EIE          |                 | _                | —             | OC5IE          | IC5IE          | T5IE         | INT4IE                   | OC4IE          | IC4IE          | T4IE         | (          |

| 070                         | IEC1                   | 15:0<br>31:16 | INT3IE<br>—       | OC3IE            | IC3IE            | T3IE           | INT2IE                    | OC2IE          | IC2IE<br>USBIE  | T2IE<br>FCEIE    | INT1IE        | OC1IE          | IC1IE          | T1IE         | INTOIE                   | CS1IE          | CS0IE          | CTIE         | (          |

| 0.0                         |                        | 15:0          | RTCCIE            | FSCMIE           | I2C2MIE          | I2C2SIE        | I2C2BIE                   | U2TXIE         | U2RXIE          | U2EIE            | SPI2RXIE      | SPI2TXIE       | SPI2EIE        | CMP2IE       | CMP1IE                   | PMPIE          | AD1IE          | CNIE         | (          |

| 090                         | IPC0                   | 31:16<br>15:0 | _                 | _                |                  |                | INT0IP<2:0><br>CS0IP<2:0> |                |                 | S<1:0><br>S<1:0> |               |                | _              |              | CS1IP<2:0><br>CTIP<2:0>  |                | CS1IS<br>CTIS  |              | (          |

|                             |                        | 31:16         | _                 | _                | _                |                | INT1IP<2:0>               |                |                 | S<1:0>           | _             | _              | _              |              | OC1IP<2:0>               |                | OC1IS          |              | -          |

| 0A0                         | IPC1                   | 15:0          | _                 | _                | _                |                | IC1IP<2:0>                |                |                 | <1:0>            | _             | _              | _              |              | T1IP<2:0>                |                | T1IS-          |              |            |

| )B0                         | IPC2                   | 31:16         | —                 | _                | —                |                | INT2IP<2:0>               |                |                 | S<1:0>           | —             | _              | —              |              | OC2IP<2:0>               |                | OC2IS          |              |            |

|                             |                        | 15:0<br>31:16 | _                 | _                |                  |                | IC2IP<2:0><br>INT3IP<2:0> |                |                 | S<1:0><br>S<1:0> |               |                |                |              | T2IP<2:0><br>OC3IP<2:0>  |                | T2IS-<br>OC3IS |              |            |

| 0C0                         | IPC3                   | 15:0          | _                 | _                | _                |                | IC3IP<2:0>                |                |                 | <1:0>            | _             | _              | _              |              | T3IP<2:0>                |                | T3IS-          |              |            |

| DD0                         | IPC4                   | 31:16         | —                 | _                | _                |                | INT4IP<2:0>               | >              | INT4I           | S<1:0>           | —             | —              | _              |              | OC4IP<2:0>               |                | OC4IS          | 6<1:0>       |            |

| 500                         | 11 04                  | 15:0          | —                 | -                | -                |                | IC4IP<2:0>                |                | IC4IS           | <1:0>            | —             | -              |                |              | T4IP<2:0>                |                | T4IS           |              |            |

| 0E0                         | IPC5                   | 31:16         | —                 | —                | —                |                | —                         | —              | -               | —                | —             | -              | -              |              | OC5IP<2:0>               |                | OC5IS          |              | 1          |

|                             |                        | 15:0          | —                 | —                | —                |                | IC5IP<2:0>                |                |                 | <1:0>            | —             |                | _              |              | T5IP<2:0>                |                | T5IS-          |              | 1          |

| 0F0                         | IPC6                   | 31:16         | —                 | _                | —                |                | AD1IP<2:0>                |                |                 | 6<1:0>           | —             | _              | —              |              | CNIP<2:0>                |                | CNIS           |              | (          |

|                             |                        | 15:0          | _                 |                  |                  |                | 12C1IP<2:0>               |                |                 | S<1:0>           | _             |                |                |              | U1IP<2:0>                |                |                | <1:0>        | 1          |

| 100                         | IPC7                   | 31:16<br>15:0 | _                 |                  |                  |                | SPI2IP<2:0><br>CMP1IP<2:0 |                |                 | S<1:0><br>S<1:0> |               |                |                |              | CMP2IP<2:0<br>PMPIP<2:0> |                | PMPIS          | S<1:0>       | 1          |

|                             |                        | 31:16         | _                 | _                |                  |                | RTCCIP<2:0                |                |                 | S<1:0>           | _             | _              |                |              | SCMIP<2:0                |                | FSCMI          |              | (          |

| 110                         | IPC8                   | 15:0          | _                 | _                | _                |                | 12C2IP<2:0>               |                |                 | S<1:0>           | _             | _              | _              |              | U2IP<2:0>                |                | U2IS           |              | (          |

| 4.40                        | 10044                  | 31:16         | _                 | _                | _                | —              | _                         | —              | _               | _                | -             | _              | _              | —            | _                        | —              | _              |              | (          |

| 1140                        | IPC11                  | 15:0          | _                 | _                | _                |                | USBIP<2:0>                |                | USBI            | S<1:0>           | _             | L _            | _              |              | FCEIP<2:0>               |                | FCEIS          | S<1.0>       | (          |

#### INTERRIPT REGISTERS MAP FOR THE PIC32MX420E032H DEVICE ONI V(1) TADIE 1.6.

© 2011 Microchip Technology Inc.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

PIC32MX3XX/4XX

This register does not have associated CLR, SET, and INV registers. 2:

### TABLE 4-42: DEVICE AND REVISION ID SUMMARY

| ess                       |                                                                                                            | e                | Bits                     |       |       |       |       |       |      |         |      |      |      |      | ø    |      |      |      |           |

|---------------------------|------------------------------------------------------------------------------------------------------------|------------------|--------------------------|-------|-------|-------|-------|-------|------|---------|------|------|------|------|------|------|------|------|-----------|

| Virtual Addro<br>(BF80_#) | Register<br>Name                                                                                           | Bit Range        | 31/15                    | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 5000                      | DEVID                                                                                                      | 31:16            | 16 VER<3:0> DEVID<27:16> |       |       |       |       | xxxx  |      |         |      |      |      |      |      |      |      |      |           |

| F220                      | DEVID                                                                                                      | 15:0 DEVID<15:0> |                          |       |       |       |       |       |      |         |      | xxxx |      |      |      |      |      |      |           |

| Legend                    | Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                  |                          |       |       |       |       |       |      | · · · · |      |      |      |      |      |      |      |      |           |

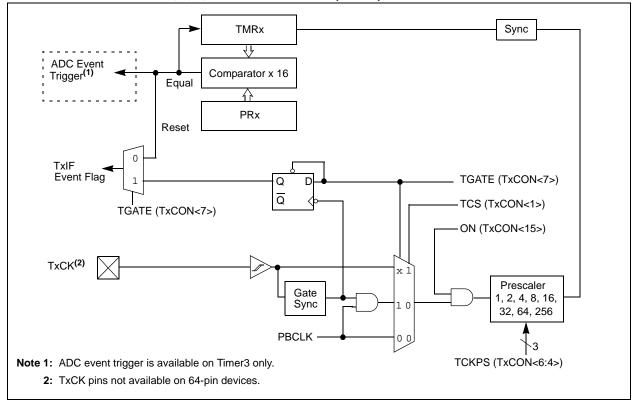

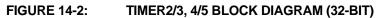

#### 14.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS61105) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This family of PIC32MX devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous Internal 16-bit Timer

- Synchronous Internal 16-bit Gated Timer

- Synchronous External 16-bit Timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous Internal 32-bit Timer

- Synchronous Internal 32-bit Gated Timer

- Synchronous External 32-bit Timer

- Note: Throughout this chapter, references to registers TxCON, TMRx and PRx use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

#### 14.1 Additional Supported Features

- · Selectable clock prescaler

- Timers operational during CPU Idle

- Time base for input capture and output compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 only)

- Fast bit manipulation using CLR, SET and INV registers

#### FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

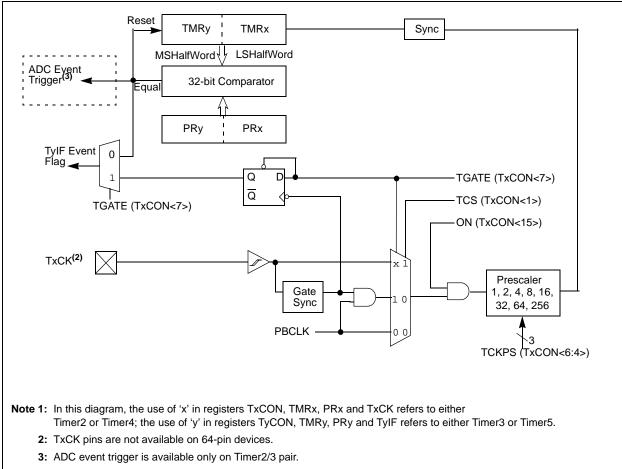

#### 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC32MX3XX/4XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32MX SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Following are some of the key features of this module:

- Master and Slave Modes Support

- Four Different Clock Formats

- Framed SPI Protocol Support

- User Configurable 8-bit, 16-bit and 32-bit Data

Width

- Separate SPI Data Registers for Receive and Transmit

- Programmable Interrupt Event on every 8-bit, 16-bit and 32-bit Data Transfer

- Operation during CPU Sleep and Idle Mode

- Fast Bit Manipulation using CLR, SET and INV Registers

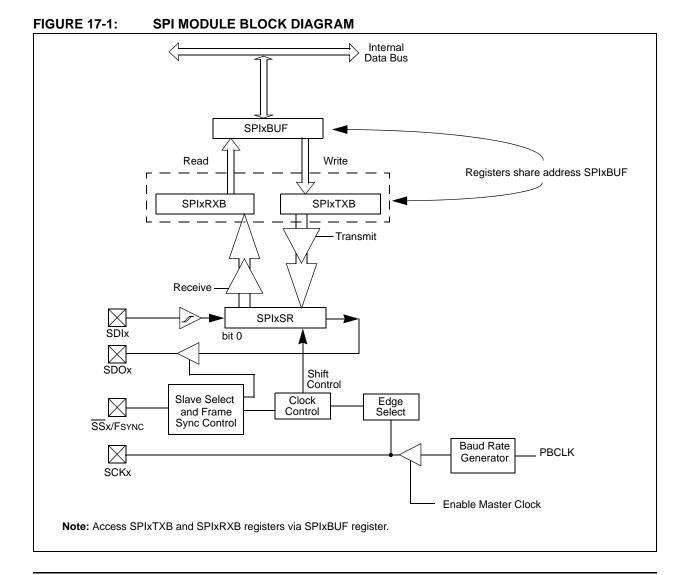

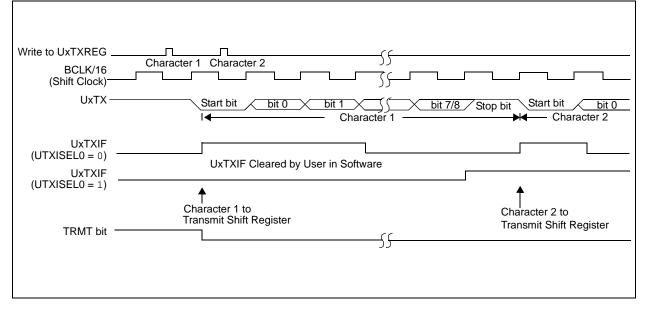

#### FIGURE 19-2: TRANSMISSION (8-BIT OR 9-BIT DATA)

NOTES:

| TABLE 27-1: | MIPS32 <sup>®</sup> INSTRUCTION SET (CONTINUED)            |                                                                                                                                   |

|-------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Instruction | Description                                                | Function                                                                                                                          |

| BLEZL       | Branch on Less Than or Equal to Zero Likely <sup>(1)</sup> | <pre>if Rs[31]    Rs == 0     PC += (int)offset else     Ignore Next Instruction</pre>                                            |

| BLTZ        | Branch on Less Than Zero                                   | if Rs[31]<br>PC += (int)offset                                                                                                    |

| BLTZAL      | Branch on Less Than Zero and Link                          | GPR[31] = PC + 8<br>if Rs[31]<br>PC += (int)offset                                                                                |

| BLTZALL     | Branch on Less Than Zero and Link Likely <sup>(1)</sup>    | <pre>GPR[31] = PC + 8 if Rs[31]     PC += (int)offset else     Ignore Next Instruction</pre>                                      |

| BLTZL       | Branch on Less Than Zero Likely <sup>(1)</sup>             | if Rs[31]<br>PC += (int)offset<br>else<br>Ignore Next Instruction                                                                 |

| BNE         | Branch on Not Equal                                        | if Rs != Rt<br>PC += (int)offset                                                                                                  |

| BNEL        | Branch on Not Equal Likely <sup>(1)</sup>                  | if Rs != Rt<br>PC += (int)offset<br>else<br>Ignore Next Instruction                                                               |

| BREAK       | Breakpoint                                                 | Break Exception                                                                                                                   |

| CLO         | Count Leading Ones                                         | Rd = NumLeadingOnes(Rs)                                                                                                           |

| CLZ         | Count Leading Zeroes                                       | Rd = NumLeadingZeroes(Rs)                                                                                                         |

| DERET       | Return from Debug Exception                                | PC = DEPC<br>Exit Debug Mode                                                                                                      |

| DI          | Atomically Disable Interrupts                              | Rt = Status; Status <sub>IE</sub> = 0                                                                                             |

| DIV         | Divide                                                     | LO = (int)Rs / (int)Rt<br>HI = (int)Rs % (int)Rt                                                                                  |

| DIVU        | Unsigned Divide                                            | LO = (uns)Rs / (uns)Rt<br>HI = (uns)Rs % (uns)Rt                                                                                  |

| EHB         | Execution Hazard Barrier                                   | Stop instruction execution<br>until execution hazards are<br>cleared                                                              |

| EI          | Atomically Enable Interrupts                               | Rt = Status; Status <sub>IE</sub> = 1                                                                                             |

| ERET        | Return from Exception                                      | if Status <sub>ERL</sub><br>PC = ErrorEPC<br>else<br>PC = EPC<br>Status <sub>ERL</sub> = 0<br>Status <sub>ERL</sub> = 0<br>LL = 0 |

| EXT         | Extract Bit Field                                          | <pre>Rt = ExtractField(Rs, pos,<br/>size)</pre>                                                                                   |

| INS         | Insert Bit Field                                           | Rt = InsertField(Rs, Rt, pos, size)                                                                                               |

| J           | Unconditional Jump                                         | PC = PC[31:28]    offset<<2                                                                                                       |

|             |                                                            |                                                                                                                                   |

### <u></u>

**Note 1:** This instruction is deprecated and should not be used.

#### 28.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 28.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 28.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 28.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 28.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### TABLE 29-13: COMPARATOR SPECIFICATIONS

| DC CHA        | ARACTERI | STICS                                 | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |      |       |                                                                                         |  |  |

|---------------|----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol   | Characteristics                       | Min.                                                                                                                                                                                     | Typical | Max. | Units | Comments                                                                                |  |  |

| D300          | VIOFF    | Input Offset Voltage                  | -                                                                                                                                                                                        | ±7.5    | ±25  | mV    | AVdd = Vdd,<br>AVss = Vss                                                               |  |  |

| D301          | VICM     | Input Common Mode Voltage             | 0                                                                                                                                                                                        | —       | Vdd  | V     | AVDD = VDD,<br>AVSS = VSS<br>(Note 2)                                                   |  |  |

| D302          | CMRR     | Common Mode Rejection Ratio           | 55                                                                                                                                                                                       | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |  |

| D303          | TRESP    | Response Time                         | —                                                                                                                                                                                        | 150     | 400  | ns    | AVDD = VDD,<br>AVss = Vss<br>(Notes 1,2)                                                |  |  |

| D304          | ON2ov    | Comparator Enabled to Output<br>Valid | _                                                                                                                                                                                        | -       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit.<br>(Note 2) |  |  |

| D305          | IVREF    | Internal Voltage Reference            | 0.57                                                                                                                                                                                     | 0.6     | 0.63 | V     | —                                                                                       |  |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

#### TABLE 29-14: VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        | RACTERIS | STICS                        | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |        |       |          |  |  |

|---------------|----------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-------|----------|--|--|

| Param.<br>No. | Symbol   | Characteristics              | Min.                                                                                                                                                                                     | Typical | Max.   | Units | Comments |  |  |

| D310          | VRES     | Resolution                   | Vdd/24                                                                                                                                                                                   | _       | VDD/32 | LSb   | —        |  |  |

| D311          | VRAA     | Absolute Accuracy            | —                                                                                                                                                                                        | _       | 1/2    | LSb   | —        |  |  |

| D312          | TSET     | Settling Time <sup>(1)</sup> | _                                                                                                                                                                                        |         | 10     | μs    | _        |  |  |

**Note 1:** Settling time measured while CVRR = 1 and CVR3:CVR0 transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

#### TABLE 29-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHA        | RACTERIS | STICS                           | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |         |      |       |                                                   |  |

|---------------|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|---------------------------------------------------|--|

| Param.<br>No. | Symbol   | Characteristics                 | Min.                                                                                                                                                                                     | Typical | Max. | Units | Comments                                          |  |

| D320          | VCORE    | Regulator Output Voltage        | 1.62                                                                                                                                                                                     | 1.80    | 1.98 | V     | _                                                 |  |

| D321          | CEFC     | External Filter Capacitor Value | 8                                                                                                                                                                                        | 10      | _    | μF    | Capacitor must be low series resistance (< 1 Ohm) |  |

| D322          | TPWRT    | Power-up Timer Period           |                                                                                                                                                                                          | 64      |      | ms    | ENVREG = 0                                        |  |

#### TABLE 29-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

|               |           |                                      |                             |                   | Standard Operating Conditions: 2.3V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+105°C for V-Temp |   |            |                                      |                                           |  |  |

|---------------|-----------|--------------------------------------|-----------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|--------------------------------------|-------------------------------------------|--|--|

| Param.<br>No. | Symbol    | Chara                                | cteristic                   | s <sup>(1)</sup>  | Min. Max. Units                                                                                                                                                                        |   | Conditions |                                      |                                           |  |  |

| TB10          | ТтхН      | TxCK<br>High<br>Time                 | Synchr<br>with pre          | onous,<br>escaler | [(12.5 ns or 1ТРВ)/N]<br>+ 25 ns                                                                                                                                                       |   | ns         | Must also meet<br>parameter<br>TB15. | N = prescale<br>value<br>(1, 2, 4, 8, 16, |  |  |

| TB11          | TTXL      | TxCK<br>Low<br>Time                  | Synchronous, with prescaler |                   | [(12.5 ns or 1ТРВ)/N]<br>+ 25 ns                                                                                                                                                       | — | ns         | Must also meet<br>parameter<br>TB15. | 32, 64, 256)                              |  |  |

| TB15          | ΤτχΡ      | oynom                                |                             | onous,<br>escaler | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns                                                                                                                                             | _ | ns         | VDD > 2.7V                           |                                           |  |  |

|               |           |                                      |                             |                   | [(Greater of 25 ns or<br>2 Трв)/N] + 50 ns                                                                                                                                             | _ | ns         | VDD < 2.7V                           | _                                         |  |  |

| TB20          | TCKEXTMRL | Delay fror<br>TxCK Clo<br>Timer Inci | ck Edge                     |                   |                                                                                                                                                                                        | 1 | Трв        | _                                    | -                                         |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

#### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

For the most current package drawings, please see the Microchip Packaging Specification located at Note: http://www.microchip.com/packaging

|                        | Units |      |          |      |  |  |  |

|------------------------|-------|------|----------|------|--|--|--|

| Dimens                 | MIN   | NOM  | MAX      |      |  |  |  |

| Number of Pins         | N     |      | 64       |      |  |  |  |

| Pitch                  | е     |      | 0.50 BSC |      |  |  |  |

| Overall Height         | A     | 0.80 | 0.90     | 1.00 |  |  |  |

| Standoff               | A1    | 0.00 | 0.02     | 0.05 |  |  |  |

| Contact Thickness      | A3    |      | 0.20 REF |      |  |  |  |

| Overall Width          | E     |      | 9.00 BSC |      |  |  |  |

| Exposed Pad Width      | E2    | 7.05 | 7.15     | 7.50 |  |  |  |

| Overall Length         | D     |      | 9.00 BSC |      |  |  |  |

| Exposed Pad Length     | D2    | 7.05 | 7.15     | 7.50 |  |  |  |

| Contact Width          | b     | 0.18 | 0.25     | 0.30 |  |  |  |

| Contact Length         | L     | 0.30 | 0.40     | 0.50 |  |  |  |

| Contact-to-Exposed Pad | K     | 0.20 | -        | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

### INDEX

| 1 | ۱. |

|---|----|

| r | ۰. |

| AC Characteristics                      | . 161 |

|-----------------------------------------|-------|

| Internal RC Accuracy                    | . 163 |

| AC Electrical Specifications            |       |

| Parallel Master Port Read Requirements  | . 186 |

| Parallel Master Port Write Requirements | . 187 |

| Parallel Slave Port Requirements        | . 185 |

| Assembler                               |       |

| MPASM Assembler                         | . 148 |

|                                         |       |

#### В

| Block Diagrams                             |             |

|--------------------------------------------|-------------|

| ADC Module                                 | 123         |

| Comparator I/O Operating Modes             | 125         |

| Comparator Voltage Reference               | 127         |

| Connections for On-Chip Voltage Regulator. |             |

| Input Capture                              |             |

| JTAG Compliant Application Showing         |             |

| Daisy-Chaining of Components               |             |

| Output Compare Module                      | 109         |

| Reset System                               |             |

| RTCC                                       |             |

| Type B Timer                               | 37, 95, 105 |

| UART                                       |             |

| WDT                                        |             |

| Brown-out Reset (BOR)                      |             |

| and On-Chip Voltage Regulator              |             |

#### С

| C Compilers                          |     |

|--------------------------------------|-----|

| •                                    |     |

| MPLAB C18                            |     |

| Comparator                           |     |

| Operation                            | 126 |

| Comparator Voltage Reference         |     |

| Configuring                          |     |

| CPU Module                           |     |

| Customer Change Notification Service |     |

| Customer Notification Service        |     |

| Customer Support                     |     |

|                                      |     |

### D

| -                                      |          |

|----------------------------------------|----------|

| DC Characteristics                     |          |

| I/O Pin Input Specifications           | 157      |

| I/O Pin Output Specifications          |          |

| Idle Current (IIDLE)                   | 154      |

| Operating Current (IDD)                | 153      |

| Power-Down Current (IPD)               | 155      |

| Program Memory                         | 159      |

| Temperature and Voltage Specifications | 152      |

| Development Support                    | 147      |

| E                                      |          |

| Electrical Characteristics             | 151      |

| AC                                     | 161      |

| Errata                                 | 19       |

| F                                      |          |

| Flash Program Memory                   | 85       |

| RTSP Operation                         |          |

| I                                      |          |

| I/O Ports                              | 101, 115 |

| Parallel I/O (PIO)                     |          |

| Internet Address                       |          |

### Μ

| Microchip Internet Web Site                                  |

|--------------------------------------------------------------|

| P                                                            |

|                                                              |

| Packaging 191                                                |

| Details 192                                                  |

| Marking 191                                                  |

| PIC32 Family USB Interface Diagram 100                       |

| Pinout I/O Descriptions (table)                              |

| Power-on Reset (POR)                                         |

|                                                              |

| and On-Chip Voltage Regulator                                |

| R                                                            |

| Reader Response                                              |

|                                                              |

| S                                                            |

| Serial Peripheral Interface (SPI) 87, 97, 111, 119, 121, 130 |

| Software Simulator (MPLAB SIM) 149                           |

| Special Features                                             |

| Special realures                                             |

| Т                                                            |

| Timer1 Module                                                |

| Timing Diagrams                                              |

| 10-bit Analog-to-Digital Conversion (CHPS<1:0> = 01,         |

|                                                              |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000) 183                   |

| 10-bit Analog-to-Digital Conversion (CHPS<1:0> = 01,         |

| SIMSAM = 0, $ASAM = 1$ , $SSRC<2:0> = 111$ ,                 |

| SAMC<4:0> = 00001)                                           |

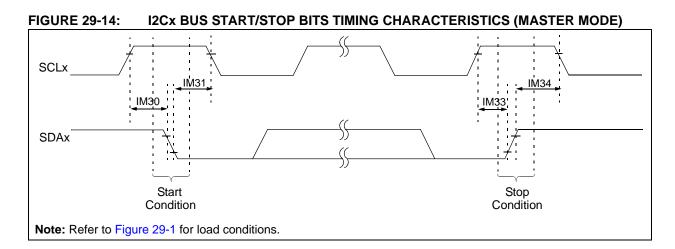

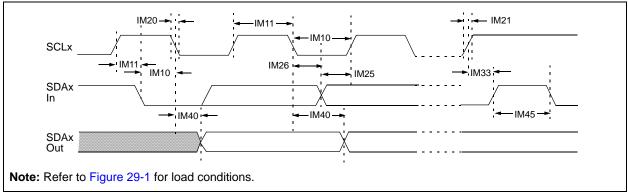

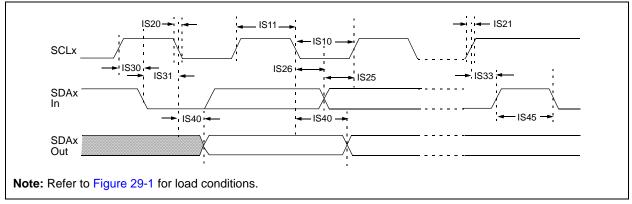

| I2Cx Bus Data (Master Mode) 175                              |

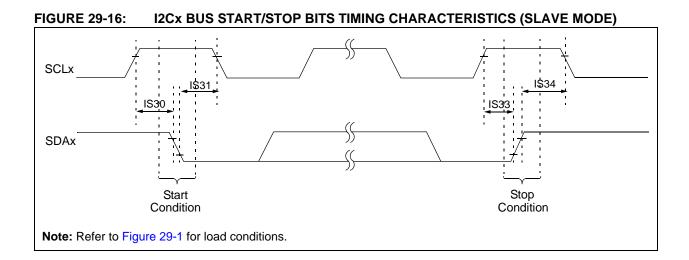

| I2Cx Bus Data (Slave Mode) 177                               |

| I2Cx Bus Start/Stop Bits (Master Mode) 175                   |

| I2Cx Bus Start/Stop Bits (Slave Mode)                        |

| Input Capture (CAPx)                                         |

|                                                              |

| OC/PWM                                                       |

| Output Compare (OCx) 169                                     |

| Parallel Master Port Write 186, 187                          |

| Parallel Slave Port 185                                      |

| SPIx Master Mode (CKE = 0) 171                               |

| SPIx Master Mode (CKE = 1) 172                               |

| SPIx Slave Mode (CKE = 0) 173                                |

| SPIx Slave Mode (CKE = 1)                                    |

|                                                              |

| Timer1, 2, 3, 4, 5 External Clock                            |

| Transmission (8-bit or 9-bit Data) 116                       |

| UART Reception with Receive Overrun 117                      |

| Timing Requirements                                          |

| CLKO and I/O 164                                             |

| Timing Specifications                                        |

| I2Cx Bus Data Requirements (Master Mode) 175                 |

| I2Cx Bus Data Requirements (Slave Mode) 178                  |

| Output Compare Requirements 169                              |

| Simple OC/PWM Mode Requirements 170                          |

| SPIx Master Mode (CKE = 0) Requirements                      |

| SPIx Master Mode (CKE = 1) Requirements                      |

| SPIx Slave Mode (CKE = 1) Requirements                       |

|                                                              |

| V                                                            |

| VCORE/VCAP Pin                                               |

| Voltage Reference Specifications                             |

Voltage Regulator (On-Chip) ..... 138

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3180 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-213-7830 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820