Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Active                                                         |

| Number of LABs/CLBs            | 5820                                                           |

| Number of Logic Elements/Cells | 74496                                                          |

| Total RAM Bits                 | 5750784                                                        |

| Number of I/O                  | 360                                                            |

| Number of Gates                | -                                                              |

| Voltage - Supply               | 0.95V ~ 1.05V                                                  |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 784-BBGA, FCBGA                                                |

| Supplier Device Package        | 784-FCBGA (29x29)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc6vlx75t-3ffg784c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 4: Typical Quiescent Supply Current (Cont'd)

| Cumbal              | Description                  | Davisa                    |        | Spee           | d and Tem  | perature Gra              | de      |                        | Units  |

|---------------------|------------------------------|---------------------------|--------|----------------|------------|---------------------------|---------|------------------------|--------|

| Symbol              | Description                  | Device                    | -3 (C) | -2 (C, E, & I) | -1 (C & I) | -1 (I & M) <sup>(2)</sup> | -1L (C) | -1L (I) <sup>(1)</sup> | Uiilis |

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> | XC6VLX75T                 | 45     | 45             | 45         | N/A                       | 45      | 45                     | mA     |

|                     | supply current               | XC6VLX130T                | 75     | 75             | 75         | N/A                       | 75      | 75                     | mA     |

|                     |                              | XC6VLX195T                | 113    | 113            | 113        | N/A                       | 113     | 113                    | mA     |

|                     |                              | XC6VLX240T                | 135    | 135            | 135        | N/A                       | 135     | 135                    | mA     |

|                     |                              | XC6VLX365T                | 191    | 191            | 191        | N/A                       | 191     | 191                    | mA     |

|                     |                              | XC6VLX550T <sup>(3)</sup> | N/A    | 286            | 286        | N/A                       | 286     | 286                    | mA     |

|                     |                              | XC6VLX760 <sup>(3)</sup>  | N/A    | 387            | 387        | N/A                       | 387     | 387                    | mA     |

|                     |                              | XC6VSX315T                | 186    | 186            | 186        | N/A                       | 186     | 186                    | mA     |

|                     |                              | XC6VSX475T(3)             | N/A    | 279            | 279        | N/A                       | 279     | 279                    | mA     |

|                     |                              | XC6VHX250T                | 152    | 152            | 152        | N/A                       | N/A     | N/A                    | mA     |

|                     |                              | XC6VHX255T                | 152    | 152            | 152        | N/A                       | N/A     | N/A                    | mA     |

|                     |                              | XC6VHX380T <sup>(4)</sup> | 227    | 227            | 227        | N/A                       | N/A     | N/A                    | mA     |

|                     |                              | XC6VHX565T(5)             | N/A    | 315            | 315        | N/A                       | N/A     | N/A                    | mA     |

|                     |                              | XQ6VLX130T <sup>(6)</sup> | N/A    | 75             | N/A        | 75                        | N/A     | 75                     | mA     |

|                     |                              | XQ6VLX240T <sup>(6)</sup> | N/A    | 135            | N/A        | 135                       | N/A     | 135                    | mA     |

|                     |                              | XQ6VLX550T <sup>(7)</sup> | N/A    | N/A            | N/A        | 286                       | N/A     | 286                    | mA     |

|                     |                              | XQ6VSX315T <sup>(6)</sup> | N/A    | 186            | N/A        | 186                       | N/A     | 186                    | mA     |

|                     |                              | XQ6VSX475T <sup>(7)</sup> | N/A    | N/A            | N/A        | 279                       | N/A     | 279                    | mA     |

- 1. Typical values are specified at nominal voltage, 85°C junction temperatures (T<sub>j</sub>). -1 and -2 industrial (I) grade devices have the same typical values as commercial (C) grade devices at 85°C, but higher values at 100°C. Use the XPE tool to calculate 100°C values. -1L industrial temperature range devices have the values specified in this column.

- 2. Use the XPE tool to calculate 125°C values for -1M temperature range devices.

- 3. The -2E extended temperature range ( $T_j = 0$ °C to +100°C) is only available in these devices. The -2I temperature range ( $T_j = -40$ °C to +100°C) is available for all other devices except the XC6VHX565T.

- 4. The XC6VHX380T is available with both -2E and -2I temperature ranges.

- 5. The XC6VHX565T is only available in the following temperature ranges: -1C, -1I, -2C, and -2E.

- 6. The XQ6VLX130T, XQ6VLX240T, and XQ6VSX315T are available in -2I, -1I, -1M, and -1LI temperature ranges.

- 7. The XQ6VLX550T and the XQ6VSX475T are only available in -1I and -1LI temperature ranges.

- 8. Typical values are for blank configured devices with no output current loads, no active input pull-up resistors, all I/O pins are 3-state and floating.

- If DCI or differential signaling is used, more accurate quiescent current estimates can be obtained by using the XPE or XPower Analyzer (XPA) tools.

### **Power-On Power Supply Requirements**

Xilinx FPGAs require a certain amount of supply current during power-on to insure proper device initialization. The actual current consumed depends on the power-on sequence and ramp rate of the power supply.

The recommended power-on sequence for Virtex-6 devices is  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  to meet the power-up current requirements listed in Table 5.  $V_{CCINT}$  can be powered up or down at any time, but power up current specifications can vary from Table 5. The device will have no physical damage or reliability concerns if  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  sequence cannot be followed.

If the recommended power-up sequence cannot be followed and the I/Os must remain 3-stated throughout configuration, then  $V_{CCAUX}$  must be powered prior to  $V_{CCO}$  or  $V_{CCAUX}$  and  $V_{CCO}$  must be powered by the same supply. Similarly, for power-down, the reverse  $V_{CCAUX}$  and  $V_{CCO}$  sequence is recommended if the I/Os are to remain 3-stated.

The GTH transceiver supplies must be powered using a MGTHAVCC, MGTHAVCCRX, MGTHAVCCPLL, and MGTHAVTT sequence. There are no sequencing requirement for these supplies with respect to the other FPGA supply voltages. For more detail see Table 27: GTH Transceiver Power Supply Sequencing. There are no sequencing requirements for the GTX transceivers power supplies.

Table 5 shows the minimum current, in addition to  $I_{CCQ}$ , that are required by Virtex-6 devices for proper power-on and configuration. If the current minimums shown in Table 4 and Table 5 are met, the device powers on after all three supplies have passed through their power-on reset threshold voltages. The FPGA must be configured after applying  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  for the appropriate configuration banks. Once initialized and configured, use the XPE tools to estimate current drain on these supplies.

Table 5: Power-On Current for Virtex-6 Devices

| Device     | I <sub>CCINTMIN</sub> Typ <sup>(1)</sup> | I <sub>CCAUXMIN</sub><br>Typ <sup>(1)</sup> | I <sub>CCOMIN</sub> Typ <sup>(1)</sup> | Units |

|------------|------------------------------------------|---------------------------------------------|----------------------------------------|-------|

| XC6VLX75T  | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 10                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VLX130T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 10                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VLX195T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VLX240T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VLX365T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VLX550T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VLX760  | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VSX315T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VSX475T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 50                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VHX250T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VHX255T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VHX380T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XC6VHX565T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 40                    | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XQ6VLX130T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 100                   | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XQ6VLX240T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 100                   | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XQ6VLX550T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 100                   | I <sub>CCOQ</sub> + 30 mA per bank     | mA    |

| XQ6VSX315T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 100                   | I <sub>CCOQ</sub> + 40 mA per bank     | mA    |

| XQ6VSX475T | See I <sub>CCINTQ</sub> in Table 4       | I <sub>CCAUXQ</sub> + 100                   | I <sub>CCOQ</sub> + 40 mA per bank     | mA    |

- 1. Typical values are specified at nominal voltage, 25°C.

- 2. Use the XPower Estimator (XPE) spreadsheet tool (download at http://www.xilinx.com/power) to calculate maximum power-on currents.

# **HT DC Specifications (HT\_25)**

Table 8: HT DC Specifications

| Symbol             | DC Parameter                               | Conditions                                             | Min  | Тур | Max  | Units |

|--------------------|--------------------------------------------|--------------------------------------------------------|------|-----|------|-------|

| V <sub>CCO</sub>   | Supply Voltage                             |                                                        | 2.38 | 2.5 | 2.63 | V     |

| V <sub>OD</sub>    | Differential Output Voltage for XC devices | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 480  | 600 | 885  | mV    |

|                    | Differential Output Voltage for XQ devices |                                                        | 480  | 600 | 930  | mV    |

| $\Delta V_{OD}$    | Change in V <sub>OD</sub> Magnitude        |                                                        | -15  | _   | 15   | mV    |

| V <sub>OCM</sub>   | Output Common Mode Voltage                 | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 440  | 600 | 760  | mV    |

| Δ V <sub>OCM</sub> | Change in V <sub>OCM</sub> Magnitude       |                                                        | -15  | _   | 15   | mV    |

| V <sub>ID</sub>    | Input Differential Voltage                 |                                                        | 200  | 600 | 1000 | mV    |

| ΔV <sub>ID</sub>   | Change in V <sub>ID</sub> Magnitude        |                                                        | -15  | _   | 15   | mV    |

| V <sub>ICM</sub>   | Input Common Mode Voltage                  |                                                        | 440  | 600 | 780  | mV    |

| Δ V <sub>ICM</sub> | Change in V <sub>ICM</sub> Magnitude       |                                                        | -15  | _   | 15   | mV    |

# LVDS DC Specifications (LVDS\_25)

Table 9: LVDS DC Specifications

| Symbol             | DC Parameter                                                                                                             | Conditions                                             | Min   | Тур   | Max   | Units |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply Voltage                                                                                                           |                                                        | 2.38  | 2.5   | 2.63  | ٧     |

| V <sub>OH</sub>    | Output High Voltage for Q and Q                                                                                          | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | _     | _     | 1.675 | ٧     |

| V <sub>OL</sub>    | Output Low Voltage for Q and Q                                                                                           | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 0.825 | _     | _     | ٧     |

| V <sub>ODIFF</sub> | Differential Output Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High }$ | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 247   | 350   | 600   | mV    |

| V <sub>OCM</sub>   | Output Common-Mode Voltage for XC devices                                                                                | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 1.075 | 1.250 | 1.425 | ٧     |

|                    | Output Common-Mode Voltage for XQ devices                                                                                |                                                        | 1.000 | 1.250 | 1.425 | ٧     |

| V <sub>IDIFF</sub> | Differential Input Voltage $(Q - \overline{Q})$ , $Q = High$ $(\overline{Q} - Q)$ , $\overline{Q} = High$                |                                                        | 100   | 350   | 600   | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                                                                                                |                                                        | 0.3   | 1.2   | 2.2   | V     |

# **Extended LVDS DC Specifications (LVDSEXT\_25)**

Table 10: Extended LVDS DC Specifications

| Symbol             | DC Parameter                                                                                                                            | Conditions                                             | Min   | Тур   | Max   | Units |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply Voltage                                                                                                                          |                                                        | 2.38  | 2.5   | 2.63  | V     |

| V <sub>OH</sub>    | Output High Voltage for Q and Q                                                                                                         | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | _     | _     | 1.785 | V     |

| V <sub>OL</sub>    | Output Low Voltage for Q and Q                                                                                                          | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 0.715 | _     | _     | V     |

| V <sub>ODIFF</sub> | Differential Output Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High }$ for XC devices | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 350   | _     | 840   | mV    |

|                    | Differential Output Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High }$ for XQ devices |                                                        | 350   | _     | 850   | mV    |

| V <sub>OCM</sub>   | Output Common-Mode Voltage for XC devices                                                                                               | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 1.075 | 1.250 | 1.425 | V     |

|                    | Output Common-Mode Voltage for XQ devices                                                                                               |                                                        | 1.000 | 1.250 | 1.425 | V     |

| V <sub>IDIFF</sub> | Differential Input Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High }$                 | Common-mode input voltage = 1.25V                      | 100   | _     | 1000  | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                                                                                                               | Differential input voltage = ±350 mV                   | 0.3   | 1.2   | 2.2   | V     |

# **GTH Transceiver Specifications**

### **GTH Transceiver DC Characteristics**

Table 25: Absolute Maximum Ratings for GTH Transceivers (1)

| Symbol                 | Description                                                                         |      | Max   | Units |

|------------------------|-------------------------------------------------------------------------------------|------|-------|-------|

| MGTHAVCC               | Analog supply voltage for the GTH transmitter, receiver, and common analog circuits | -0.5 | 1.125 | V     |

| MGTHAVCCRX             | Analog supply voltage for the GTH receiver circuits and common analog circuits      | -0.5 | 1.125 | V     |

| MGTHAVTT               | Analog supply voltage for the GTH transmitter termination circuits                  | -0.5 | 1.32  | V     |

| MGTHAVCCPLL            | Analog supply voltage for the GTH receiver and PLL circuits                         | -0.5 | 1.935 | V     |

| V <sub>IN</sub>        | Receiver (RXP/RXN) and Transmitter (TXP/TXN) absolute input voltage                 | -0.5 | 1.125 | ٧     |

| V <sub>MGTREFCLK</sub> | Reference clock absolute input voltage                                              | -0.5 | 1.935 | V     |

#### Notes:

Table 26: Recommended Operating Conditions for GTH Transceivers (1)(2)

| Symbol      | Description                                                                               |       | Тур | Max   | Units |

|-------------|-------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| MGTHAVCC    | Analog supply voltage for the GTH transmitter, receiver, and common analog circuits       | 1.075 | 1.1 | 1.125 | V     |

| MGTHAVCCRX  | MGTHAVCCRX Analog supply voltage for the GTH receiver circuits and common analog circuits |       | 1.1 | 1.125 | V     |

| MGTHAVTT    | Analog supply voltage for the GTH transmitter termination circuits                        | 1.140 | 1.2 | 1.26  | V     |

| MGTHAVCCPLL | Analog supply voltage for the GTH receiver and PLL circuit                                | 1.710 | 1.8 | 1.89  | V     |

#### Notes:

- 1. Each voltage listed requires the filter circuit described in UG371: Virtex-6 FPGA GTH Transceivers User Guide.

- 2. Voltages are specified for the temperature range of  $T_i = -40$ °C to +100°C.

Table 27: GTH Transceiver Power Supply Sequencing (1)(2)(3)

| Symbol                        | Description                                                                  | Min | Max | Units |

|-------------------------------|------------------------------------------------------------------------------|-----|-----|-------|

| T <sub>HAVCC2HAVCCRX</sub>    | Maximum time between powering MGTHAVCC to when MGTHAVCCRX must be powered.   | 0   | 5   | ms    |

| T <sub>HAVCCRX2HAVCCPLL</sub> | Minimum time between powering MGTHAVCCRX to when MGTHAVCCPLL can be powered. | 10  | -   | μs    |

| T <sub>HAVCCRX2HAVTT</sub>    | Minimum time between powering MGTHAVCCRX to when MGTHAVTT can be powered.    | 10  | _   | μs    |

- MGTHAVCCRX must be powered simultaneously or within T<sub>HAVCC2HAVCCRX</sub> of MGTHAVCC, but it must not precede MGTHAVCC.

- MGTHAVCC and MGTHAVCCRX must be powered before MGTHAVCCPLL and MGTHAVTT. This minimum time is defined by THAVCCRX2HAVCCPLL and THAVCCRX2HAVTT.

- 3. At any time, the condition of MGTHAVCC being present and MGTHAVCCRX not being present should not occur for more than the maximum Thavcc2havccrx.

Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

### **GTH Transceiver Switching Characteristics**

Consult <u>UG371</u>: Virtex-6 FPGA GTH Transceivers User Guide for further information.

Table 32: GTH Transceiver Maximum Data Rate and PLL Frequency Range

| Symbol               | Description                                      | Conditions             | 5      | Units  |       |       |

|----------------------|--------------------------------------------------|------------------------|--------|--------|-------|-------|

|                      |                                                  | Conditions             | -3     | -2     | -1    | Units |

| _                    | Maximum GTH transceiver data rate                | PLL Output Divider = 1 | 11.182 | 11.182 | 10.32 | Gb/s  |

| F <sub>GTHMAX</sub>  | waximum GTH transcerver data rate                | PLL Output Divider = 4 | 2.795  | 2.795  | 2.58  | Gb/s  |

| F                    | Minimum CTI I transposition data vata(1)         | PLL Output Divider = 1 | 9.92   | 9.92   | 9.92  | Gb/s  |

| F <sub>GTHMIN</sub>  | Minimum GTH transceiver data rate <sup>(1)</sup> | PLL Output Divider = 4 | 2.48   | 2.48   | 2.48  | Gb/s  |

| F <sub>GPLLMAX</sub> | Maximum GTH PLL frequency                        |                        | 5.591  | 5.591  | 5.16  | GHz   |

| F <sub>GPLLMIN</sub> | Minimum GTH PLL frequency                        |                        | 4.96   | 4.96   | 4.96  | GHz   |

Table 33: GTH Transceiver Dynamic Reconfiguration Port (DRP) Switching Characteristics

| Symbol Descri          | Description                 | 8  | Speed Grad | е  | Units  |

|------------------------|-----------------------------|----|------------|----|--------|

|                        | Description                 | -3 | -2         | -1 | Uiilis |

| F <sub>GTHDRPCLK</sub> | GTHDRPCLK maximum frequency | 70 | 70         | 60 | MHz    |

Table 34: GTH Transceiver Reference Clock Switching Characteristics

| Cumbal             | Description                               | Conditions                                               | All | Units |     |       |

|--------------------|-------------------------------------------|----------------------------------------------------------|-----|-------|-----|-------|

| Symbol             | Description                               | Conditions                                               | Min | Тур   | Max | Units |

| _                  | Peteronee clock frequency ronge           | -1 speed grade                                           | 150 | -     | 645 | MHz   |

| F <sub>GCLK</sub>  | Reference clock frequency range           | -2 and -3 speed grades                                   | 150 | _     | 700 | MHz   |

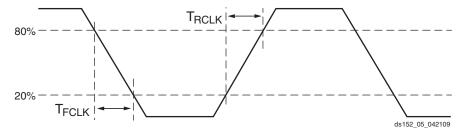

| T <sub>RCLK</sub>  | Reference clock rise time                 | 20% – 80%                                                | -   | 200   | _   | ps    |

| T <sub>FCLK</sub>  | Reference clock fall time                 | 80% – 20%                                                | _   | 200   | _   | ps    |

| T <sub>DCREF</sub> | Reference clock duty cycle                | CLK                                                      | 45  | 50    | 55  | %     |

| T <sub>LOCK</sub>  | Clock recovery frequency acquisition time | Initial PLL lock                                         | _   | _     | 2   | ms    |

| T <sub>PHASE</sub> | Clock recovery phase acquisition time     | Lock to data after PLL has locked to the reference clock | -   | _     | 20  | μs    |

Figure 5: Reference Clock Timing Parameters

<sup>1.</sup> Lower data rates can be achieved using FPGA logic based oversampling designs.

Table 37: GTH Transceiver Receiver Switching Characteristics

| Symbol                   |                    | Description                      | Min | Тур | Max | Units |

|--------------------------|--------------------|----------------------------------|-----|-----|-----|-------|

| R <sub>XRL</sub>         | Run length (CID)   | Run length (CID)                 |     |     | _   | UI    |

| R <sub>XPPMTOL</sub>     | Data/REFCLK PPM of | Data/REFCLK PPM offset tolerance |     | _   | 200 | ppm   |

| SJ Jitter Tolerance(1)(2 | )(3)(4)            |                                  |     |     | *   |       |

| JT_SJ <sub>11.18</sub>   | Sinusoidal Jitter  | 11.18 Gb/s                       | 0.3 | _   | _   | UI    |

| JT_SJ <sub>10.32</sub>   | Sinusoidal Jitter  | 10.32 Gb/s                       | 0.3 | _   | -   | UI    |

| JT_SJ <sub>9.95</sub>    | Sinusoidal Jitter  | 9.95 Gb/s                        | 0.3 | _   | -   | UI    |

| JT_SJ <sub>2.667</sub>   | Sinusoidal Jitter  | 2.667 Gb/s                       | 0.5 | _   | _   | UI    |

| JT_SJ <sub>2.48</sub>    | Sinusoidal Jitter  | 2.48 Gb/s                        | 0.5 | _   | _   | UI    |

- 1. These values are NOT intended for protocol specific compliance determinations.

- All jitter values are based on a bit error ratio of 1e<sup>-12</sup>.

- 3. The frequency of the injected sinusoidal jitter is 80 MHz.

- 4. High-frequency jitter tolerance including 6 db of channel loss at a high frequency of the data rate divided by two.

# **Ethernet MAC Switching Characteristics**

Consult <u>UG368</u>: Virtex-6 FPGA Embedded Tri-mode Ethernet MAC User Guide for further information.

Table 38: Maximum Ethernet MAC Performance

| Comple el                | Description                | Conditions               |                    | Speed              | Grade              |                    | l lesite |

|--------------------------|----------------------------|--------------------------|--------------------|--------------------|--------------------|--------------------|----------|

| Symbol                   | Description                | Conditions               | -3                 | -2                 | -1                 | -1L                | Units    |

| F <sub>TEMACCLIENT</sub> | Client interface maximum   | 10 Mb/s – 8-bit width    | 2.5 <sup>(1)</sup> | 2.5 <sup>(1)</sup> | 2.5 <sup>(1)</sup> | 2.5 <sup>(1)</sup> | MHz      |

|                          | frequency                  | 100 Mb/s – 8-bit width   | 25 <sup>(2)</sup>  | 25 <sup>(2)</sup>  | 25 <sup>(2)</sup>  | 25 <sup>(2)</sup>  | MHz      |

|                          |                            | 1000 Mb/s - 8-bit width  | 125                | 125                | 125                | 125                | MHz      |

|                          |                            | 1000 Mb/s - 16-bit width | 62.5               | 62.5               | 62.5               | 62.5               | MHz      |

|                          |                            | 2000 Mb/s - 16-bit width | 125                | 125                | 125                | N/A                | MHz      |

|                          |                            | 2500 Mb/s - 16-bit width | 156.25             | 156.25             | 156.25             | N/A                | MHz      |

| F <sub>TEMACPHY</sub>    | Physical interface maximum | 10 Mb/s – 4-bit width    | 2.5                | 2.5                | 2.5                | 2.5                | MHz      |

|                          | frequency                  | 100 Mb/s – 4-bit width   | 25                 | 25                 | 25                 | 25                 | MHz      |

|                          |                            | 1000 Mb/s - 8-bit width  | 125                | 125                | 125                | 125                | MHz      |

|                          |                            | 2000 Mb/s - 8-bit width  | 250                | 250                | 250                | N/A                | MHz      |

|                          |                            | 2500 Mb/s - 8-bit width  | 312.5              | 312.5              | 312.5              | N/A                | MHz      |

- 1. When not using clock enable, the  $F_{MAX}$  is lowered to 1.25 MHz.

- When not using clock enable, the F<sub>MAX</sub> is lowered to 12.5 MHz.

### **Performance Characteristics**

This section provides the performance characteristics of some common functions and designs implemented in Virtex-6 devices. The numbers reported here are worst-case values; they have all been fully characterized. These values are subject to the same guidelines as the Switching Characteristics, page 26.

Table 41: Interface Performances

| Deparintion                                                                |           | Speed     | Grade     |          |

|----------------------------------------------------------------------------|-----------|-----------|-----------|----------|

| Description                                                                | -3        | -2        | -1        | -1L      |

| Networking Applications                                                    |           |           |           |          |

| SDR LVDS transmitter (using OSERDES; DATA_WIDTH = 4 to 8)                  | 710 Mb/s  | 710 Mb/s  | 650 Mb/s  | 585 Mb/s |

| DDR LVDS transmitter (using OSERDES; DATA_WIDTH = 4 to 10)                 | 1.4 Gb/s  | 1.3 Gb/s  | 1.25 Gb/s | 1.1 Gb/s |

| SDR LVDS receiver (SFI-4.1) <sup>(1)</sup>                                 | 710 Mb/s  | 710 Mb/s  | 650 Mb/s  | 585 Mb/s |

| DDR LVDS receiver (SPI-4.2) <sup>(1)</sup>                                 | 1.4 Gb/s  | 1.3 Gb/s  | 1.1 Gb/s  | 0.9 Gb/s |

| Maximum Physical Interface (PHY) Rate for Memory Interfaces <sup>(2)</sup> | (3)(4)    |           |           |          |

| DDR2                                                                       | 800 Mb/s  | 800 Mb/s  | 800 Mb/s  | 606 Mb/s |

| DDR3                                                                       | 1066 Mb/s | 1066 Mb/s | 800 Mb/s  | 800 Mb/s |

| QDR II + SRAM                                                              | 400 MHz   | 350 MHz   | 300 MHz   | _        |

| RLDRAM II                                                                  | 500 MHz   | 400 MHz   | 350 MHz   | _        |

- 1. LVDS receivers are typically bounded with certain applications where specific DPA algorithms dominate deterministic performance.

- 2. Verified on Xilinx memory characterization platforms designed according to the guidelines in UG: Virtex-6 FPGA Memory Interface Solutions User Guide.

- 3. Consult DS186: Virtex-6 FPGA Memory Interface Solutions Data Sheet for performance and feature information on memory interface cores (controller plus PHY).

- 4. Memory Interface data rates have not been tested over the junction temperature operating range for military (M) temperature devices. Customers are responsible for specifying and testing their specific M temperature grade memory implementation.

Table 44: IOB Switching Characteristics for the Commercial (XC) Virtex-6 Devices (Cont'd)

|                       |      | T <sub>I</sub> | OPI   |      |      | T <sub>IC</sub> | ОР    |      |      | T <sub>IC</sub> | OTP   |      |       |

|-----------------------|------|----------------|-------|------|------|-----------------|-------|------|------|-----------------|-------|------|-------|

| I/O Standard          |      | Speed          | Grade |      |      | Speed           | Grade |      |      | Speed           | Grade |      | Units |

|                       | -3   | -2             | -1    | -1L  | -3   | -2              | -1    | -1L  | -3   | -2              | -1    | -1L  |       |

| LVCMOS25, Fast, 24 mA | 0.51 | 0.57           | 0.66  | 0.70 | 1.66 | 1.79            | 1.99  | 1.96 | 1.66 | 1.79            | 1.99  | 1.96 | ns    |

| LVCMOS18, Slow, 2 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 4.21 | 4.47            | 4.87  | 4.30 | 4.21 | 4.47            | 4.87  | 4.30 | ns    |

| LVCMOS18, Slow, 4 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 2.79 | 2.96            | 3.21  | 2.94 | 2.79 | 2.96            | 3.21  | 2.94 | ns    |

| LVCMOS18, Slow, 6 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 2.30 | 2.43            | 2.64  | 2.47 | 2.30 | 2.43            | 2.64  | 2.47 | ns    |

| LVCMOS18, Slow, 8 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 2.01 | 2.11            | 2.27  | 2.24 | 2.01 | 2.11            | 2.27  | 2.24 | ns    |

| LVCMOS18, Slow, 12 mA | 0.55 | 0.61           | 0.71  | 0.73 | 1.88 | 1.99            | 2.15  | 2.10 | 1.88 | 1.99            | 2.15  | 2.10 | ns    |

| LVCMOS18, Slow, 16 mA | 0.55 | 0.61           | 0.71  | 0.73 | 1.84 | 1.95            | 2.11  | 2.04 | 1.84 | 1.95            | 2.11  | 2.04 | ns    |

| LVCMOS18, Fast, 2 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 4.00 | 4.23            | 4.57  | 4.08 | 4.00 | 4.23            | 4.57  | 4.08 | ns    |

| LVCMOS18, Fast, 4 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 2.62 | 2.76            | 2.97  | 2.74 | 2.62 | 2.76            | 2.97  | 2.74 | ns    |

| LVCMOS18, Fast, 6 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 2.15 | 2.28            | 2.46  | 2.32 | 2.15 | 2.28            | 2.46  | 2.32 | ns    |

| LVCMOS18, Fast, 8 mA  | 0.55 | 0.61           | 0.71  | 0.73 | 1.90 | 1.99            | 2.13  | 2.14 | 1.90 | 1.99            | 2.13  | 2.14 | ns    |

| LVCMOS18, Fast, 12 mA | 0.55 | 0.61           | 0.71  | 0.73 | 1.69 | 1.80            | 1.97  | 1.88 | 1.69 | 1.80            | 1.97  | 1.88 | ns    |

| LVCMOS18, Fast, 16 mA | 0.55 | 0.61           | 0.71  | 0.73 | 1.63 | 1.74            | 1.91  | 1.88 | 1.63 | 1.74            | 1.91  | 1.88 | ns    |

| LVCMOS15, Slow, 2 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 3.43 | 3.77            | 4.29  | 3.91 | 3.43 | 3.77            | 4.29  | 3.91 | ns    |

| LVCMOS15, Slow, 4 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 2.58 | 2.79            | 3.10  | 2.93 | 2.58 | 2.79            | 3.10  | 2.93 | ns    |

| LVCMOS15, Slow, 6 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 2.08 | 2.32            | 2.68  | 2.50 | 2.08 | 2.32            | 2.68  | 2.50 | ns    |

| LVCMOS15, Slow, 8 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 1.81 | 1.98            | 2.23  | 2.24 | 1.81 | 1.98            | 2.23  | 2.24 | ns    |

| LVCMOS15, Slow, 12 mA | 0.64 | 0.73           | 0.85  | 0.85 | 1.76 | 1.91            | 2.13  | 2.07 | 1.76 | 1.91            | 2.13  | 2.07 | ns    |

| LVCMOS15, Slow, 16 mA | 0.64 | 0.73           | 0.85  | 0.85 | 1.69 | 1.83            | 2.04  | 1.98 | 1.69 | 1.83            | 2.04  | 1.98 | ns    |

| LVCMOS15, Fast, 2 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 3.44 | 3.77            | 4.28  | 3.91 | 3.44 | 3.77            | 4.28  | 3.91 | ns    |

| LVCMOS15, Fast, 4 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 2.37 | 2.53            | 2.78  | 2.66 | 2.37 | 2.53            | 2.78  | 2.66 | ns    |

| LVCMOS15, Fast, 6 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 1.80 | 2.05            | 2.42  | 2.16 | 1.80 | 2.05            | 2.42  | 2.16 | ns    |

| LVCMOS15, Fast, 8 mA  | 0.64 | 0.73           | 0.85  | 0.85 | 1.76 | 1.90            | 2.11  | 2.04 | 1.76 | 1.90            | 2.11  | 2.04 | ns    |

| LVCMOS15, Fast, 12 mA | 0.64 | 0.73           | 0.85  | 0.85 | 1.64 | 1.77            | 1.97  | 1.90 | 1.64 | 1.77            | 1.97  | 1.90 | ns    |

| LVCMOS15, Fast, 16 mA | 0.64 | 0.73           | 0.85  | 0.85 | 1.62 | 1.76            | 1.96  | 1.92 | 1.62 | 1.76            | 1.96  | 1.92 | ns    |

| LVCMOS12, Slow, 2 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 3.14 | 3.39            | 3.75  | 3.54 | 3.14 | 3.39            | 3.75  | 3.54 | ns    |

| LVCMOS12, Slow, 4 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 2.43 | 2.63            | 2.93  | 2.79 | 2.43 | 2.63            | 2.93  | 2.79 | ns    |

| LVCMOS12, Slow, 6 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 1.92 | 2.11            | 2.41  | 2.26 | 1.92 | 2.11            | 2.41  | 2.26 | ns    |

| LVCMOS12, Slow, 8 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 1.87 | 2.02            | 2.25  | 2.17 | 1.87 | 2.02            | 2.25  | 2.17 | ns    |

| LVCMOS12, Fast, 2 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 2.71 | 2.98            | 3.39  | 3.11 | 2.71 | 2.98            | 3.39  | 3.11 | ns    |

| LVCMOS12, Fast, 4 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 1.93 | 2.16            | 2.51  | 2.31 | 1.93 | 2.16            | 2.51  | 2.31 | ns    |

| LVCMOS12, Fast, 6 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 1.75 | 1.89            | 2.11  | 2.05 | 1.75 | 1.89            | 2.11  | 2.05 | ns    |

| LVCMOS12, Fast, 8 mA  | 0.72 | 0.81           | 0.93  | 0.95 | 1.69 | 1.82            | 2.02  | 1.98 | 1.69 | 1.82            | 2.02  | 1.98 | ns    |

| LVDCI_25              | 0.51 | 0.57           | 0.66  | 0.70 | 2.05 | 2.14            | 2.26  | 2.26 | 2.05 | 2.14            | 2.26  | 2.26 | ns    |

| LVDCI_18              | 0.55 | 0.61           | 0.71  | 0.73 | 2.07 | 2.23            | 2.47  | 2.38 | 2.07 | 2.23            | 2.47  | 2.38 | ns    |

| LVDCI_15              | 0.64 | 0.73           | 0.85  | 0.85 | 1.85 | 2.01            | 2.24  | 2.18 | 1.85 | 2.01            | 2.24  | 2.18 | ns    |

Table 45: IOB Switching Characteristics for the Defense-grade (XQ) Virtex-6 Devices (Cont'd)

|                      |             | T <sub>IOPI</sub> |             | T <sub>IOOP</sub> |      |             | T <sub>IOTP</sub> |      |       |    |

|----------------------|-------------|-------------------|-------------|-------------------|------|-------------|-------------------|------|-------|----|

| I/O Standard         | Speed Grade |                   | Speed Grade |                   |      | Speed Grade |                   |      | Units |    |

|                      | -2          | -1                | -1L         | -2                | -1   | -1L         | -2                | -1   | -1L   |    |

| DIFF_SSTL18_II       | 0.94        | 1.09              | 1.08        | 1.50              | 2.27 | 1.66        | 1.50              | 2.27 | 1.66  | ns |

| DIFF_SSTL18_II_DCI   | 0.94        | 1.09              | 1.08        | 1.47              | 2.20 | 1.62        | 1.47              | 2.20 | 1.62  | ns |

| DIFF_SSTL18_II_T_DCI | 0.94        | 1.09              | 1.08        | 1.51              | 2.30 | 1.65        | 1.51              | 2.30 | 1.65  | ns |

| DIFF_SSTL15          | 0.91        | 1.06              | 1.06        | 1.54              | 2.25 | 1.69        | 1.54              | 2.25 | 1.69  | ns |

| DIFF_SSTL15_DCI      | 0.91        | 1.06              | 1.06        | 1.52              | 2.25 | 1.66        | 1.52              | 2.25 | 1.66  | ns |

| DIFF_SSTL15_T_DCI    | 0.91        | 1.06              | 1.06        | 1.52              | 2.25 | 1.66        | 1.52              | 2.25 | 1.66  | ns |

Table 46: IOB 3-state ON Output Switching Characteristics (T<sub>IOTPHZ</sub>)

| Symbol              | Description                   |      | Units |      |      |       |

|---------------------|-------------------------------|------|-------|------|------|-------|

| Symbol              | Description                   | -3   | -2    | -1   | -1L  | Units |

| T <sub>IOTPHZ</sub> | T input to Pad high-impedance | 0.86 | 0.92  | 0.99 | 0.99 | ns    |

## I/O Standard Adjustment Measurement Methodology

### **Input Delay Measurements**

Table 47 shows the test setup parameters used for measuring input delay.

Table 47: Input Delay Measurement Methodology

| Description                                                     | I/O Standard Attribute | V <sub>L</sub> <sup>(1)(2)</sup> | V <sub>H</sub> <sup>(1)(2)</sup> | V <sub>MEAS</sub> (1)(4)(5) | V <sub>REF</sub> (1)(3)(5) |

|-----------------------------------------------------------------|------------------------|----------------------------------|----------------------------------|-----------------------------|----------------------------|

| LVCMOS, 2.5V                                                    | LVCMOS25               | 0                                | 2.5                              | 1.25                        | _                          |

| LVCMOS, 1.8V                                                    | LVCMOS18               | 0                                | 1.8                              | 0.9                         | _                          |

| LVCMOS, 1.5V                                                    | LVCMOS15               | 0                                | 1.5                              | 0.75                        | _                          |

| HSTL (High-Speed Transceiver Logic),<br>Class I & II            | HSTL_I, HSTL_II        | V <sub>REF</sub> – 0.5           | V <sub>REF</sub> + 0.5           | V <sub>REF</sub>            | 0.75                       |

| HSTL, Class III                                                 | HSTL_III               | V <sub>REF</sub> - 0.5           | V <sub>REF</sub> + 0.5           | $V_{REF}$                   | 0.90                       |

| HSTL, Class I & II, 1.8V                                        | HSTL_I_18, HSTL_II_18  | V <sub>REF</sub> - 0.5           | V <sub>REF</sub> + 0.5           | V <sub>REF</sub>            | 0.90                       |

| HSTL, Class III 1.8V                                            | HSTL_III_18            | V <sub>REF</sub> – 0.5           | V <sub>REF</sub> + 0.5           | $V_{REF}$                   | 1.08                       |

| SSTL (Stub Terminated Transceiver Logic),<br>Class I & II, 3.3V | SSTL3_I, SSTL3_II      | V <sub>REF</sub> – 1.00          | V <sub>REF</sub> + 1.00          | V <sub>REF</sub>            | 1.5                        |

| SSTL, Class I & II, 2.5V                                        | SSTL2_I, SSTL2_II      | V <sub>REF</sub> – 0.75          | V <sub>REF</sub> + 0.75          | $V_{REF}$                   | 1.25                       |

| SSTL, Class I & II, 1.8V                                        | SSTL18_I, SSTL18_II    | V <sub>REF</sub> - 0.5           | V <sub>REF</sub> + 0.5           | V <sub>REF</sub>            | 0.90                       |

| LVDS (Low-Voltage Differential Signaling), 2.5V                 | LVDS_25                | 1.2 - 0.125                      | 1.2 + 0.125                      | 0(6)                        | _                          |

| LVDSEXT (LVDS Extended Mode), 2.5V                              | LVDSEXT_25             | 1.2 - 0.125                      | 1.2 + 0.125                      | 0(6)                        | _                          |

| HT (HyperTransport), 2.5V                                       | LDT_25                 | 0.6 - 0.125                      | 0.6 + 0.125                      | 0(6)                        | _                          |

- The input delay measurement methodology parameters for LVDCI are the same for LVCMOS standards of the same voltage. Input delay

measurement methodology parameters for HSLVDCI are the same as for HSTL\_II standards of the same voltage. Parameters for all other

DCI standards are the same for the corresponding non-DCI standards.

- 2. Input waveform switches between  $V_I$  and  $V_H$ .

- Measurements are made at typical, minimum, and maximum V<sub>REF</sub> values. Reported delays reflect worst case of these measurements. V<sub>REF</sub> values listed are typical.

- 4. Input voltage level from which measurement starts.

- 5. This is an input voltage reference that bears no relation to the V<sub>REF</sub> / V<sub>MEAS</sub> parameters found in IBIS models and/or noted in Figure 6.

- 6. The value given is the differential input voltage.

Table 48: Output Delay Measurement Methodology (Cont'd)

| Description                                                  | I/O Standard<br>Attribute     | R <sub>REF</sub> (Ω) | C <sub>REF</sub> <sup>(1)</sup><br>(pF) | V <sub>MEAS</sub> (V) | V <sub>REF</sub> (V) |

|--------------------------------------------------------------|-------------------------------|----------------------|-----------------------------------------|-----------------------|----------------------|

| HT (HyperTransport), 2.5V                                    | LDT_25                        | 100                  | 0                                       | 0(2)                  | 0.6                  |

| LVPECL (Low-Voltage Positive Emitter-Coupled Logic), 2.5V    | LVPECL_25                     | 100                  | 0                                       | 0(2)                  | 0                    |

| LVDCI/HSLVDCI, 2.5V                                          | LVDCI_25, HSLVDCI_25          | 1M                   | 0                                       | 1.25                  | 0                    |

| LVDCI/HSLVDCI, 1.8V                                          | LVDCI_18, HSLVDCI_18          | 1M                   | 0                                       | 0.9                   | 0                    |

| LVDCI/HSLVDCI, 1.5V                                          | LVDCI_15, HSLVDCI_15          | 1M                   | 0                                       | 0.75                  | 0                    |

| HSTL (High-Speed Transceiver Logic), Class I & II, with DCI  | HSTL_I_DCI, HSTL_II_DCI       | 50                   | 0                                       | V <sub>REF</sub>      | 0.75                 |

| HSTL, Class III, with DCI                                    | HSTL_III_DCI                  | 50                   | 0                                       | 0.9                   | 1.5                  |

| HSTL, Class I & II, 1.8V, with DCI                           | HSTL_I_DCI_18, HSTL_II_DCI_18 | 50                   | 0                                       | $V_{REF}$             | 0.9                  |

| HSTL, Class III, 1.8V, with DCI                              | HSTL_III_DCI_18               | 50                   | 0                                       | 1.1                   | 1.8                  |

| SSTL (Stub Series Termi.Logic), Class I & II, 1.8V, with DCI | SSTL18_I_DCI, SSTL18_II_DCI   | 50                   | 0                                       | $V_{REF}$             | 0.9                  |

| SSTL, Class I & II, 2.5V, with DCI                           | SSTL2_I_DCI, SSTL2_II_DCI     | 50                   | 0                                       | $V_{REF}$             | 1.25                 |

- 1. C<sub>REF</sub> is the capacitance of the probe, nominally 0 pF.

- 2. The value given is the differential output voltage.

# **Input/Output Logic Switching Characteristics**

Table 49: ILOGIC Switching Characteristics

| Symbol                                   | Decembries                                                    |                | Speed          | Grade          |                | Units   |

|------------------------------------------|---------------------------------------------------------------|----------------|----------------|----------------|----------------|---------|

| Symbol                                   | Description                                                   | -3             | -2             | -1             | -1L            | Units   |

| Setup/Hold                               |                                                               |                |                |                |                |         |

| T <sub>ICE1CK</sub> /T <sub>ICKCE1</sub> | CE1 pin Setup/Hold with respect to CLK                        | 0.21/<br>0.03  | 0.25/<br>0.04  | 0.27/<br>0.04  | 0.31/<br>0.05  | ns      |

| T <sub>ISRCK</sub> /T <sub>ICKSR</sub>   | SR pin Setup/Hold with respect to CLK                         | 0.66/<br>-0.08 | 0.78/<br>-0.08 | 0.96/<br>-0.08 | 1.09/<br>-0.11 | ns      |

| T <sub>IDOCK</sub> /T <sub>IOCKD</sub>   | D pin Setup/Hold with respect to CLK without Delay            | 0.07/<br>0.41  | 0.08/<br>0.46  | 0.10/<br>0.54  | 0.11/<br>0.64  | ns      |

| T <sub>IDOCKD</sub> /T <sub>IOCKDD</sub> | DDLY pin Setup/Hold with respect to CLK (using IODELAY)       | 0.10/<br>0.32  | 0.12/<br>0.36  | 0.14/<br>0.42  | 0.16/<br>0.50  | ns      |

| Combinatorial                            |                                                               |                |                |                |                |         |

| T <sub>IDI</sub>                         | D pin to O pin propagation delay, no Delay                    | 0.15           | 0.17           | 0.20           | 0.23           | ns      |

| T <sub>IDID</sub>                        | DDLY pin to O pin propagation delay (using IODELAY)           | 0.19           | 0.22           | 0.25           | 0.28           | ns      |

| Sequential Delays                        |                                                               |                |                |                |                |         |

| T <sub>IDLO</sub>                        | D pin to Q1 pin using flip-flop as a latch without Delay      | 0.48           | 0.54           | 0.64           | 0.73           | ns      |

| T <sub>IDLOD</sub>                       | DDLY pin to Q1 pin using flip-flop as a latch (using IODELAY) | 0.52           | 0.58           | 0.68           | 0.78           | ns      |

| T <sub>ICKQ</sub>                        | CLK to Q outputs                                              | 0.54           | 0.61           | 0.70           | 0.93           | ns      |

| T <sub>RQ_ILOGIC</sub>                   | SR pin to OQ/TQ out                                           | 0.85           | 0.97           | 1.15           | 1.32           | ns      |

| T <sub>GSRQ_ILOGIC</sub>                 | Global Set/Reset to Q outputs                                 | 7.60           | 7.60           | 10.51          | 10.51          | ns      |

| Set/Reset                                |                                                               |                |                |                |                |         |

| T <sub>RPW_ILOGIC</sub>                  | Minimum Pulse Width, SR inputs                                | 0.78           | 0.95           | 1.20           | 1.30           | ns, Min |

### **CLB Distributed RAM Switching Characteristics (SLICEM Only)**

Table 55: CLB Distributed RAM Switching Characteristics

| Symbol                               | Description                  |            | Speed      | Grade      |            | Units   |

|--------------------------------------|------------------------------|------------|------------|------------|------------|---------|

| Syllibol                             | Description                  | -3         | -2         | -1         | -1L        | Ullits  |

| Sequential Delays                    |                              |            |            |            |            |         |

| T <sub>SHCKO</sub>                   | Clock to A – B outputs       | 0.92       | 1.10       | 1.36       | 1.49       | ns, Max |

| T <sub>SHCKO_1</sub>                 | Clock to AMUX – BMUX outputs | 1.19       | 1.40       | 1.71       | 1.87       | ns, Max |

| Setup and Hold Time                  | es Before/After Clock CLK    |            |            |            |            |         |

| T <sub>DS</sub> /T <sub>DH</sub>     | A – D inputs to CLK          | 0.62/0.18  | 0.72/0.20  | 0.88/0.22  | 0.98/0.23  | ns, Min |

| T <sub>AS</sub> /T <sub>AH</sub>     | Address An inputs to clock   | 0.19/0.52  | 0.22/0.59  | 0.27/0.66  | 0.30/0.75  | ns, Min |

| T <sub>WS</sub> /T <sub>WH</sub>     | WE input to clock            | 0.27/0.00  | 0.32/0.00  | 0.40/0.00  | 0.47/-0.03 | ns, Min |

| T <sub>CECK</sub> /T <sub>CKCE</sub> | CE input to CLK              | 0.28/-0.01 | 0.34/-0.01 | 0.41/-0.01 | 0.48/-0.05 | ns, Min |

| Clock CLK                            |                              |            |            |            |            |         |

| T <sub>MPW</sub>                     | Minimum pulse width          | 0.70       | 0.82       | 1.00       | 1.04       | ns, Min |

| T <sub>MCP</sub>                     | Minimum clock period         | 1.40       | 1.64       | 2.00       | 2.08       | ns, Min |

#### Notes:

### **CLB Shift Register Switching Characteristics (SLICEM Only)**

Table 56: CLB Shift Register Switching Characteristics

| Comple of                            | Description                         |            | Speed      | Grade      |           | Heita   |

|--------------------------------------|-------------------------------------|------------|------------|------------|-----------|---------|

| Symbol                               | Description                         | -3         | -2         | -1         | -1L       | Units   |

| Sequential Delays                    |                                     |            |            |            |           |         |

| T <sub>REG</sub>                     | Clock to A – D outputs              | 1.11       | 1.30       | 1.58       | 1.74      | ns, Max |

| T <sub>REG_MUX</sub>                 | Clock to AMUX – DMUX output         | 1.37       | 1.60       | 1.93       | 2.12      | ns, Max |

| T <sub>REG_M31</sub>                 | Clock to DMUX output via M31 output | 1.08       | 1.27       | 1.55       | 1.74      | ns, Max |

| Setup and Hold Ti                    | mes Before/After Clock CLK          |            |            |            |           |         |

| T <sub>WS</sub> /T <sub>WH</sub>     | WE input                            | 0.05/0.00  | 0.07/0.00  | 0.09/0.00  | 0.11/0.03 | ns, Min |

| T <sub>CECK</sub> /T <sub>CKCE</sub> | CE input to CLK                     | 0.06/-0.01 | 0.08/-0.01 | 0.10/-0.01 | 0.12/0.02 | ns, Min |

| T <sub>DS</sub> /T <sub>DH</sub>     | A – D inputs to CLK                 | 0.64/0.18  | 0.76/0.21  | 0.94/0.24  | 1.07/0.23 | ns, Min |

| Clock CLK                            |                                     |            |            |            |           |         |

| T <sub>MPW</sub>                     | Minimum pulse width                 | 0.60       | 0.70       | 0.85       | 0.89      | ns, Min |

### Notes:

A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

<sup>2.</sup> T<sub>SHCKO</sub> also represents the CLK to XMUX output. Refer to TRACE report for the CLK to XMUX path.

Table 59: Configuration Switching Characteristics (Cont'd)

| Symbol                                                     | Description                                                                                                                               |               | Speed         | Grade         |               | Units       |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|-------------|

| Symbol                                                     | Description                                                                                                                               | -3            | -2            | -1            | -1L           | Units       |

| Т <sub>ЅМСКВҮ</sub>                                        | CCLK to BUSY out in readback at 2.5V                                                                                                      | 6             | 6             | 6             | 7             | ns, Max     |

|                                                            | CCLK to BUSY out in readback at 1.8V                                                                                                      | 6             | 6             | 6             | 7             | ns, Max     |

| F <sub>SMCCK</sub>                                         | Maximum Frequency with respect to nominal CCLK                                                                                            | 100           | 100           | 100           | 70            | MHz, Max    |

| F <sub>RBCCK</sub>                                         | Maximum Readback Frequency with respect to nominal CCLK                                                                                   | 100           | 100           | 100           | 60            | MHz, Max    |

| F <sub>MCCKTOL</sub>                                       | Frequency tolerance, master mode with respect to nominal CCLK                                                                             | 55            | 55            | 55            | 60            | %           |

| Boundary-Scan Port 1                                       | iming Specifications                                                                                                                      | l             | 11            | 1             |               |             |

| T <sub>TAPTCK</sub> /T <sub>TCKTAP</sub>                   | TMS and TDI Setup time before TCK/ Hold time after TCK                                                                                    | 3.0/2.0       | 3.0/2.0       | 3.0/2.0       | 4.0/2.0       | ns, Min     |

| Ттскто                                                     | TCK falling edge to TDO output valid at 2.5V                                                                                              | 6             | 6             | 6             | 7             | ns, Max     |

|                                                            | TCK falling edge to TDO output valid at 1.8V                                                                                              | 6             | 6             | 6             | 7             | ns, Max     |

| F <sub>TCK</sub>                                           | Maximum configuration TCK clock frequency                                                                                                 | 66            | 66            | 66            | 33            | MHz, Max    |

| F <sub>TCKB_MIN</sub>                                      | Minimum boundary-scan TCK clock frequency when using IEEE Std 1149.6 (AC-JTAG). Minimum operating temperature for IEEE Std 1149.6 is 0°C. | 15            | 15            | 15            | 15            | MHz, Min    |

| F <sub>TCKB</sub>                                          | Maximum boundary-scan TCK clock frequency                                                                                                 | 66            | 66            | 66            | 33            | MHz, Max    |

|                                                            | e Programming Switching                                                                                                                   |               |               |               |               |             |

| T <sub>BPICCO</sub> <sup>(2)</sup>                         | ADDR[25:0], RS[1:0], FCS_B, FOE_B, FWE_B outputs valid after CCLK rising edge at 2.5V                                                     | 6             | 6             | 6             | 7             | ns          |

|                                                            | ADDR[25:0], RS[1:0], FCS_B, FOE_B, FWE_B outputs valid after CCLK rising edge at 1.8V                                                     | 6             | 6             | 6             | 7             | ns          |

| T <sub>BPIDCC</sub> /T <sub>BPICCD</sub>                   | Setup/Hold on D[15:0] data input pins                                                                                                     | 4.0/0.0       | 4.0/0.0       | 4.0/0.0       | 5.0/0.0       | ns          |

| T <sub>INITADDR</sub>                                      | Minimum period of initial ADDR[25:0] address cycles                                                                                       | 3             | 3             | 3             | 3             | CCLK cycles |

| SPI Master Flash Mod                                       | e Programming Switching                                                                                                                   |               |               |               |               |             |

| T <sub>SPIDCC</sub> /T <sub>SPIDCCD</sub>                  | DIN Setup/Hold before/after the rising CCLK edge                                                                                          | 3.0/0.0       | 3.0/0.0       | 3.0/0.0       | 3.5/0.0       | ns          |

| T <sub>SPICCM</sub>                                        | MOSI clock to out at 2.5V                                                                                                                 | 6             | 6             | 6             | 7             | ns          |

|                                                            | MOSI clock to out at 1.8V                                                                                                                 | 6             | 6             | 6             | 7             | ns          |

| T <sub>SPICCFC</sub>                                       | FCS_B clock to out at 2.5V                                                                                                                | 6             | 6             | 6             | 7             | ns          |

|                                                            | FCS_B clock to out at 1.8V                                                                                                                | 6             | 6             | 6             | 7             | ns          |

| T <sub>FSINIT</sub> /T <sub>FSINITH</sub>                  | FS[2:0] to INIT_B rising edge Setup and Hold                                                                                              | 2             | 2             | 2             | 2             | μs          |

| CCLK Output (Master                                        | Modes)                                                                                                                                    |               |               |               |               |             |

| T <sub>MCCKL</sub>                                         | Master CCLK clock Low time duty cycle                                                                                                     | 45/55         | 45/55         | 45/55         | 40/60         | %, Min/Max  |

| T <sub>MCCKH</sub>                                         | Master CCLK clock High time duty cycle                                                                                                    | 45/55         | 45/55         | 45/55         | 40/60         | %, Min/Max  |

| CCLK Input (Slave Mo                                       | des)                                                                                                                                      | I             | ı             | I             |               |             |

| T <sub>SCCKL</sub>                                         | Slave CCLK clock minimum Low time                                                                                                         | 2.5           | 2.5           | 2.5           | 2.5           | ns, Min     |

| T <sub>SCCKH</sub>                                         | Slave CCLK clock minimum High time                                                                                                        | 2.5           | 2.5           | 2.5           | 2.5           | ns, Min     |

| Dynamic Reconfigura                                        | tion Port (DRP) for MMCM Before and After DCLK                                                                                            |               | 1             | 1             | 1             | +           |

| F <sub>DCK</sub>                                           | Maximum frequency for DCLK                                                                                                                | 200           | 200           | 200           | 200           | MHz         |

| T <sub>MMCMDCK_DADDR</sub> /<br>T <sub>MMCMCKD_DADDR</sub> | DADDR Setup/Hold                                                                                                                          | 1.25/<br>0.00 | 1.40/<br>0.00 | 1.63/<br>0.00 | 1.64/<br>0.00 | ns          |

# Virtex-6 Device Pin-to-Pin Input Parameter Guidelines

All devices are 100% functionally tested. The representative values for typical pin locations and normal clock loading are listed in Table 68. Values are expressed in nanoseconds unless otherwise noted.

Table 68: Global Clock Input Setup and Hold Without MMCM

| Cumbal                                | Description                                                                                          | Davies          |                | Speed Grade    |                |                |       |

|---------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|----------------|----------------|----------------|----------------|-------|

| Symbol                                |                                                                                                      | Device          | -3             | -2             | -1             | -1L            | Units |

| Input Setup and                       | Hold Time Relative to Global Clock Input Signa                                                       | al for LVCMOS25 | Standard.      | (1)            |                |                |       |

| T <sub>PSFD</sub> / T <sub>PHFD</sub> | Full Delay (Legacy Delay or Default Delay)<br>Global Clock Input and IFF <sup>(2)</sup> without MMCM | XC6VLX75T       | 1.33/<br>0.03  | 1.44/<br>0.03  | 1.75/<br>0.03  | 2.18/<br>-0.22 | ns    |

|                                       |                                                                                                      | XC6VLX130T      | 1.31/<br>-0.08 | 1.54/<br>-0.08 | 1.88/<br>-0.08 | 2.31/<br>-0.12 | ns    |

|                                       |                                                                                                      | XC6VLX195T      | 1.36/<br>-0.11 | 1.60/<br>-0.11 | 1.97/<br>-0.11 | 2.40/<br>-0.25 | ns    |

|                                       |                                                                                                      | XC6VLX240T      | 1.36/<br>-0.11 | 1.60/<br>-0.11 | 1.97/<br>-0.11 | 2.40/<br>-0.25 | ns    |

|                                       |                                                                                                      | XC6VLX365T      | 1.79/<br>-0.28 | 1.87/<br>-0.28 | 2.17/<br>-0.28 | 2.48/<br>-0.24 | ns    |

|                                       |                                                                                                      | XC6VLX550T      | N/A            | 2.22/<br>-0.12 | 2.36/<br>-0.12 | 2.77/<br>-0.26 | ns    |

|                                       |                                                                                                      | XC6VLX760       | N/A            | 2.19/<br>-0.24 | 2.35/<br>-0.24 | 2.71/<br>-0.21 | ns    |

|                                       |                                                                                                      | XC6VSX315T      | 1.75/<br>-0.09 | 1.85/<br>-0.09 | 2.06/<br>-0.09 | 2.47/<br>-0.24 | ns    |

|                                       |                                                                                                      | XC6VSX475T      | N/A            | 2.14/<br>-0.14 | 2.31/<br>-0.14 | 2.71/<br>-0.30 | ns    |

|                                       |                                                                                                      | XC6VHX250T      | 1.93/<br>-0.22 | 2.04/<br>-0.22 | 2.25/<br>-0.22 | N/A            | ns    |

|                                       |                                                                                                      | XC6VHX255T      | 1.81/<br>-0.33 | 2.11/<br>-0.33 | 2.56/<br>-0.33 | N/A            | ns    |

|                                       |                                                                                                      | XC6VHX380T      | 1.93/<br>-0.11 | 2.04/<br>-0.11 | 2.25/<br>-0.11 | N/A            | ns    |

|                                       |                                                                                                      | XC6VHX565T      | N/A            | 2.20/<br>-0.12 | 2.39/<br>-0.12 | N/A            | ns    |

|                                       |                                                                                                      | XQ6VLX130T      | N/A            | 1.54/<br>-0.08 | 1.88/<br>-0.08 | 2.31/<br>-0.12 | ns    |

|                                       |                                                                                                      | XQ6VLX240T      | N/A            | 1.60/<br>-0.11 | 1.97/<br>-0.11 | 2.40/<br>-0.25 | ns    |

|                                       |                                                                                                      | XQ6VLX550T      | N/A            | N/A            | 2.36/<br>-0.12 | 2.77/<br>-0.26 | ns    |

|                                       |                                                                                                      | XQ6VSX315T      | N/A            | 1.85/<br>-0.09 | 2.06/<br>-0.09 | 2.47/<br>-0.24 | ns    |

|                                       |                                                                                                      | XQ6VSX475T      | N/A            | N/A            | 2.31/<br>-0.14 | 2.71/<br>-0.30 | ns    |

- Setup and Hold times are measured over worst case conditions (process, voltage, temperature). Setup time is measured relative to the Global Clock input signal using the slowest process, highest temperature, and lowest voltage. Hold time is measured relative to the Global Clock input signal using the fastest process, lowest temperature, and highest voltage.

- 2. IFF = Input Flip-Flop or Latch

- 3. A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

Table 69: Global Clock Input Setup and Hold With MMCM

| Symbol                                           | Description                                                                                                    | Device                                   | Speed Grade    |                     |                | Units          |    |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|---------------------|----------------|----------------|----|

| Symbol                                           | Description                                                                                                    | Device                                   | -3             | -2 -1 -1L           | -1L            | Onits          |    |

| Input Setup and H                                | old Time Relative to Global Clock Input                                                                        | Signal for LVCMC                         | S25 Stand      | ard. <sup>(1)</sup> |                |                |    |

| T <sub>PSMMCMGC</sub> /<br>T <sub>PHMMCMGC</sub> | No Delay Global Clock Input and IFF <sup>(2)</sup> with MMCM                                                   | XC6VLX75T                                | 1.45/<br>-0.18 | 1.57/<br>-0.18      | 1.72/<br>-0.18 | 1.78/<br>-0.08 | ns |

|                                                  |                                                                                                                | XC6VLX130T                               | 1.53/<br>-0.18 | 1.65/<br>-0.18      | 1.81/<br>-0.18 | 1.87/<br>-0.07 | ns |

|                                                  |                                                                                                                | XC6VLX195T                               | 1.54/<br>-0.17 | 1.66/<br>-0.17      | 1.82/<br>-0.17 | 1.87/<br>-0.08 | ns |

|                                                  |                                                                                                                | XC6VLX240T                               | 1.54/<br>-0.17 | 1.66/<br>-0.17      | 1.82/<br>-0.17 | 1.87/<br>-0.08 | ns |