Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1694                                                       |

| Number of Logic Elements/Cells | 33880                                                      |

| Total RAM Bits                 | 1369728                                                    |

| Number of I/O                  | 361                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30cf780c3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

SIIGX51001-1.6

The Stratix® II GX family of devices is Altera's third generation of FPGAs to combine high-speed serial transceivers with a scalable, high-performance logic array. Stratix II GX devices include 4 to 20 high-speed transceiver channels, each incorporating clock and data recovery unit (CRU) technology and embedded SERDES capability at data rates of up to 6.375 gigabits per second (Gbps). The transceivers are grouped into four-channel transceiver blocks and are designed for low power consumption and small die size. The Stratix II GX FPGA technology is built upon the Stratix II architecture and offers a 1.2-V logic array with unmatched performance, flexibility, and time-to-market capabilities. This scalable, high-performance architecture makes Stratix II GX devices ideal for high-speed backplane interface, chip-to-chip, and communications protocol-bridging applications.

# **Features**

This section lists the Stratix II GX device features.

#### Main device features:

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers with performance up to 550 MHz

- Up to 16 global clock networks with up to 32 regional clock networks per device region

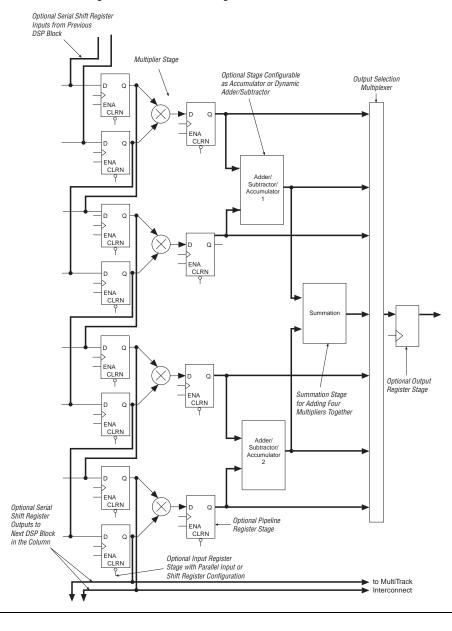

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to four enhanced PLLs per device provide spread spectrum, programmable bandwidth, clock switch-over, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed source-synchronous differential I/O support on up to 71 channels

- Support for source-synchronous bus standards, including SPI-4 Phase 2 (POS-PHY Level 4), SFI-4.1, XSBI, UTOPIA IV, NPSI, and CSIX-L1

- Support for high-speed external memory, including quad data rate (QDR and QDRII) SRAM, double data rate (DDR and DDR2) SDRAM, and single data rate (SDR) SDRAM

|                         | Clock           | Resource          |                        | Transceiver            |                        |                        |                        |  |  |  |  |  |

|-------------------------|-----------------|-------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|--|

| Region                  | Global<br>Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O | Bank 15<br>8 clock I/O | Bank 16<br>8 Clock I/O | Bank 17<br>8 Clock I/O |  |  |  |  |  |

| Region0<br>8 LRIO clock | <b>✓</b>        | RCLK 20-27        | <b>✓</b>               |                        |                        |                        |                        |  |  |  |  |  |

| Region1<br>8 LRIO clock | ~               | RCLK 20-27        |                        | <b>✓</b>               |                        |                        |                        |  |  |  |  |  |

| Region2<br>8 LRIO clock | ~               | RCLK 12-19        |                        |                        | ✓                      | ~                      |                        |  |  |  |  |  |

| Region3<br>8 LRIO clock | ~               | RCLK 12-19        |                        |                        |                        | ~                      | <b>✓</b>               |  |  |  |  |  |

### **Other Transceiver Features**

Other important features of the Stratix II GX transceivers are the power down and reset capabilities, external voltage reference and bias circuitry, and hot swapping.

#### Calibration Block

The Stratix II GX device uses the calibration block to calibrate the on-chip termination for the PLLs and their associated output buffers and the terminating resistors on the transceivers. The calibration block counters the effects of process, voltage, and temperature (PVT). The calibration block references a derived voltage across an external reference resistor to calibrate the on-chip termination resistors on the Stratix II GX device. The calibration block can be powered down. However, powering down the calibration block during operations may yield transmit and receive data errors.

## Dynamic Reconfiguration

This feature allows you to dynamically reconfigure the PMA portion and the channel parameters, such as data rate and functional mode, of the Stratix II GX transceiver. The PMA reconfiguration allows you to quickly optimize the settings for the transceiver's PMA to achieve the intended bit error rate (BER).

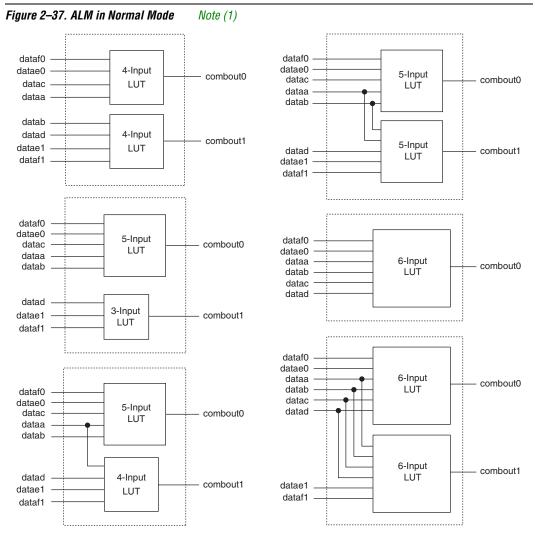

Note to Figure 2-37:

(1) Combinations of functions with less inputs than those shown are also supported. For example, combinations of functions with the following number of inputs are supported: 4 and 3, 3 and 2, 5 and 2, etc.

The normal mode provides complete backward compatibility with four-input LUT architectures. Two independent functions of four inputs or less can be implemented in one Stratix II GX ALM. In addition, a five-input function and an independent three-input function can be implemented without sharing inputs.

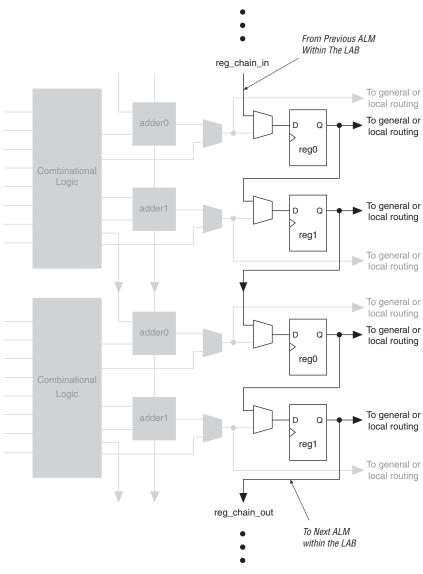

Figure 2–45. Register Chain within a LAB Note (1)

Note to Figure 2-45:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

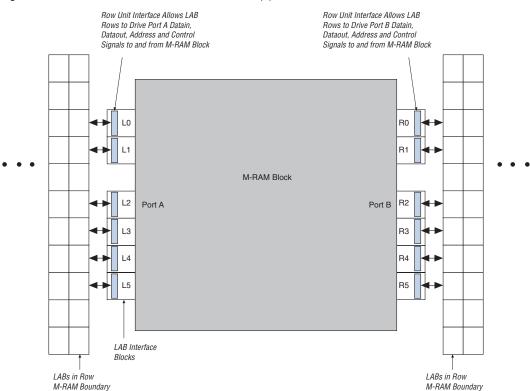

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–53.

Dedicated Row LAB Clocks Local Local Interconnect Interconnect clocken a clock\_b renwe a aclr b Local Local Interconnect Interconnect clocken b clock a aclr\_a renwe b

Figure 2-53. M-RAM Block Control Signals

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–54 shows an example floorplan for the EP2SGX130 device and the location of the M-RAM interfaces. Figures 2–55 and 2–56 show the interface between the M-RAM block and the logic array.

Figure 2–55. M-RAM Block LAB Row Interface Note (1)

*Note to Figure 2–55:*

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

Figure 2-58. DSP Block Diagram for 18 x 18-Bit Configuration

The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs are shown in Table 2–28. The connections to the clocks from the bottom clock pins are shown in Table 2–29.

| Table 2–28. Global and Reg<br>(Part 1 of 2)                   | ional (  | Clock (  | Connec   | ctions   | from T   | Top Clo  | ock Pi   | ns and   | l Enha   | nced F   | PLL Ou   | ıtputs   |          |

|---------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global and<br>Regional Clock Network<br>Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                                    | •        |          |          |          |          |          |          |          | •        |          |          | •        |          |

| CLK12p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13p                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                        | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| CLK12n                                                        |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                        |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK14n                                                        |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                   |          |          |          |          |          |          |          |          | •        |          |          |          |          |

| GCLKDRV0                                                      |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                      |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                      |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                      |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                      |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                      |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                      |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                      |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL5 outputs                                         | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        |          | 1        | 1        | 1        |          |

| c0                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

- Open-drain outputs

- DQ and DQS I/O pins

- Double data rate (DDR) registers

The IOE in Stratix II GX devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 2–76 shows the Stratix II GX IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. You can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, you can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

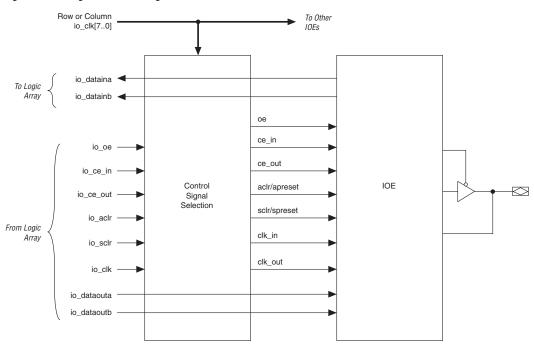

There are 32 control and data signals that feed each row or column I/O block. These control and data signals are driven from the logic array. The row or column IOE clocks, io\_clk [7..0], provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from global or regional clocks. Refer to "PLLs and Clock Networks" on page 2–89 for more information.

Figure 2–79 illustrates the signal paths through the I/O block.

Figure 2-79. Signal Path Through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/apreset, sclr/spreset, clk\_in, and clk\_out. Figure 2–80 illustrates the control signal selection.

Table 2–35 summarizes Stratix II GX MultiVolt I/O support.

| Table 2-3             | Table 2–35. Stratix II GX MultiVolt I/O Support Note (1) |              |              |              |              |              |                   |              |              |          |          |  |

|-----------------------|----------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|-------------------|--------------|--------------|----------|----------|--|

| v (v)                 |                                                          | In           | put Signa    | I (V)        |              |              | Output Signal (V) |              |              |          |          |  |

| V <sub>CCIO</sub> (V) | 1.2                                                      | 1.5          | 1.8          | 2.5          | 3.3          | 1.2          | 1.5               | 1.8          | 2.5          | 3.3      | 5.0      |  |

| 1.2                   | (4)                                                      | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (4) | _                 | _            | _            | _        | _        |  |

| 1.5                   | (4)                                                      | <b>✓</b>     | <b>✓</b>     | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (3) | <b>✓</b>          | _            | _            | _        |          |  |

| 1.8                   | (4)                                                      | <b>✓</b>     | <b>✓</b>     | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (3) | <b>√</b> (3)      | <b>✓</b>     | _            | _        | _        |  |

| 2.5                   | (4)                                                      | _            | _            | <b>✓</b>     | <b>✓</b>     | <b>√</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>✓</b>     | _        | _        |  |

| 3.3                   | (4)                                                      | _            |              | <b>✓</b>     | <b>\</b>     | <b>√</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>√</b> (3) | <b>\</b> | <b>✓</b> |  |

#### Notes to Table 2–35:

- (1) To drive inputs higher than  $V_{\rm CCIO}$  but less than 4.0 V, disable the PCI clamping diode and select the **Allow LVTTL and LVCMOS input levels to overdrive input buffer** option in the Quartus II software.

- (2) The pin current may be slightly higher than the default value. You must verify that the driving device's  $V_{OL}$  maximum and  $V_{OH}$  minimum voltages do not violate the applicable Stratix II GX  $V_{IL}$  maximum and  $V_{IH}$  minimum voltage specifications.

- (3) Although V<sub>CCIO</sub> specifies the voltage necessary for the Stratix II GX device to drive out, a receiving device powered at a different level can still interface with the Stratix II GX device if it has inputs that tolerate the V<sub>CCIO</sub> value.

- (4) Stratix II GX devices support 1.2-V HSTL. They do not support 1.2-V LVTTL and 1.2-V LVCMOS.

The TDO and nCEO pins are powered by  $V_{CCIO}$  of the bank that they reside. TDO is in I/O bank 4 and nCEO is in I/O bank 7. Ideally, the V<sub>CC</sub> supplies for the I/O buffers of any two connected pins are at the same voltage level. This may not always be possible depending on the V<sub>CCIO</sub> level of TDO and nCEO pins on master devices and the configuration voltage level chosen by V<sub>CCSEL</sub> on slave devices. Master and slave devices can be in any position in the chain. Master indicates that it is driving out TDO or nCEO to a slave device. For multi-device passive configuration schemes, the nCEO pin of the master device drives the nCE pin of the slave device. The VCCSEL pin on the slave device selects which input buffer is used for nCE. When  $V_{CCSEL}$  is logic high, it selects the 1.8-V/1.5-V buffer powered by  $V_{CCIO}$ . When  $V_{CCSEL}$  is logic low, it selects the 3.3-V/2.5-V input buffer powered by V<sub>CCPD</sub>. The ideal case is to have the V<sub>CCIO</sub> of the nCEO bank in a master device match the V<sub>CCSEL</sub> settings for the nCE input buffer of the slave device it is connected to, but that may not be possible depending on the application.

- Stratix II Performance and Logic Efficiency Analysis White Paper

- TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

# Document Revision History

Table 2–42 shows the revision history for this chapter.

| Table 2-42. Docu                | ment Revision History (Part 1 of 6)                                                                                                                                                                                                                  |                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                         | Summary of Changes |

| October 2007,<br>v2.2           | Updated:      "Programmable Pull-Up Resistor"      "Reverse Serial Pre-CDR Loopback"      "Receiver Input Buffer"      "Pattern Detection"      "Control and Status Signals"      "Individual Power Down and Reset for the Transmitter and Receiver" |                    |

|                                 | Updated:     Figure 2–14     Figure 2–26     Figure 2–27     Figure 2–86 (notes only)     Figure 2–87                                                                                                                                                |                    |

|                                 | Updated:  Table 2–4  Table 2–7                                                                                                                                                                                                                       |                    |

|                                 | Removed note from Table 2–31.                                                                                                                                                                                                                        |                    |

|                                 | Removed Tables 2-2, 2-7, and 2-8.                                                                                                                                                                                                                    |                    |

|                                 | Minor text edits.                                                                                                                                                                                                                                    |                    |

| August 2007, v2.1               | Added "Reverse Serial Pre-CDR Loopback" section.                                                                                                                                                                                                     |                    |

|                                 | Updated Table 2–2.                                                                                                                                                                                                                                   |                    |

|                                 | Added "Referenced Documents" section.                                                                                                                                                                                                                |                    |

| Table 2–42. Docu                | ment Revision History (Part 4 of 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Summary of Changes |

|                                 | Updated:  "Transmitter PLLs"  "Transmitter Phase Compensation FIFO Buffer"  "8B/10B Encoder"  "Byte Serializer"  "Programmable Output Driver"  "Receiver PLL & CRU"  "Programmable Pre-Emphasis"  "Receiver Input Buffer"  "Control and Status Signals"  "Programmable Run Length Violation"  "Channel Aligner"  "Basic Mode"  "Byte Ordering Block"  "Receiver Phase Compensation FIFO Buffer"  "Loopback Modes"  "Serial Loopback"  "Parallel Loopback"  "Regional Clock Network"  "MultiVolt I/O Interface"  "High-Speed Differential I/O with DPA Support" |                    |

|                                 | Updated bulleted lists at the beginning of the "Transceivers" section.  Added reference to the "Transmit Buffer"                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |

|                                 | section.  Deleted the Programmable V <sub>OD</sub> table from the "Programmable Output Driver" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

|                                 | Changed "PLD Interface" heading to "Parallel Data Width" heading in Table 2–14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |

|                                 | Deleted "Global & Regional Clock<br>Connections from Right Side Clock Pins &<br>Fast PLL Outputs" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

|                                 | Updated notes to Tables 2-29 and 2-37.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

|                                 | Updated notes to Figures 2–72, 2–73 and 2–74.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |

|                                 | Updated bulleted list in the "Advanced I/O Standard Support" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

| Table 4-3 | 3. Stratix II GX Device Recomme | nded Operating Conditions (Part | 2 of 2) A | lote (1) |      |

|-----------|---------------------------------|---------------------------------|-----------|----------|------|

| Symbol    | Parameter                       | Conditions                      | Minimum   | Maximum  | Unit |

| $T_J$     | Operating junction temperature  | For commercial use              | 0         | 85       | С    |

|           |                                 | For industrial use              | -40       | 100      | С    |

#### Notes to Table 4-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 4–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 µs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, the Stratix II GX device will not configure successfully. If the system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

#### **Transceiver Block Characteristics**

Tables 4–4 through 4–6 contain transceiver block specifications.

| Table 4–4. Stratix | II GX Transceiver Block Ab       | solute Maximum Ratings    | Note (1) |         |       |

|--------------------|----------------------------------|---------------------------|----------|---------|-------|

| Symbol             | Parameter                        | Conditions                | Minimum  | Maximum | Units |

| V <sub>CCA</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 4.6     | V     |

| V <sub>CCP</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCR</sub>   | Transceiver block supply Voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCT</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCT_B</sub> | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCL</sub>   | Transceiver block supply voltage | Commercial and industrial | -0.5     | 1.8     | V     |

| V <sub>CCH_B</sub> | Transceiver block supply voltage | Commercial and industrial | -0.5     | 2.4     | V     |

#### Note to Table 4-4:

(1) The device can tolerate prolonged operation at this absolute maximum, as long as the maximum specification is not violated.

| V <sub>CCH</sub> TX<br>= 1.2 V     | First Post Tap Pre-Emphasis Level |                                                 |     |      |      |         |                |      |      |      |      |      |

|------------------------------------|-----------------------------------|-------------------------------------------------|-----|------|------|---------|----------------|------|------|------|------|------|

| V <sub>OD</sub><br>Setting<br>(mV) | 1                                 | 1 2 3 4 5 6 7 8 9 10 11 12                      |     |      |      |         |                |      |      |      |      |      |

|                                    |                                   |                                                 |     |      |      | TX Term | <b>= 120</b> Ω | 2    |      |      |      |      |

| 192                                | 45%                               |                                                 |     |      |      |         |                |      |      |      |      |      |

| 384                                |                                   | 41%                                             | 76% | 114% | 166% | 257%    | 355%           |      |      |      |      |      |

| 576                                |                                   | 23%                                             | 38% | 55%  | 84%  | 108%    | 137%           | 179% | 226% | 280% | 405% | 477% |

| 768                                |                                   | 15% 24% 36% 47% 64% 80% 97% 122% 140% 170% 196% |     |      |      |         |                |      |      |      |      |      |

|                                    |                                   |                                                 |     | 22%  | 30%  | 41%     | 51%            | 63%  | 77%  | 86%  | 98%  | 116% |

Note to Table 4–17:

| V <sub>CCH</sub> TX<br>= 1.2 V     | First Post Tap Pre-Emphasis Level |                                          |     |     |      |         |         |      |      |      |      |      |

|------------------------------------|-----------------------------------|------------------------------------------|-----|-----|------|---------|---------|------|------|------|------|------|

| V <sub>OD</sub><br>Setting<br>(mV) | 1 2 3 4 5 6 7 8 9 10 11           |                                          |     |     |      |         |         |      |      | 12   |      |      |

|                                    |                                   | •                                        | •   | •   |      | TX Term | = 150 Ω | 2    | •    |      |      | l    |

| 240                                | 31%                               | 85%                                      |     |     |      |         |         |      |      |      |      |      |

| 480                                |                                   | 32%                                      | 52% | 78% | 112% | 152%    | 195%    | 275% |      |      |      |      |

| 720                                |                                   | 19%                                      | 28% | 37% | 56%  | 68%     | 86%     | 108% | 133% | 169% | 194% | 239% |

| 960                                |                                   | 17% 22% 30% 39% 51% 59% 75% 85% 94% 109% |     |     |      |         |         |      |      |      |      |      |

Note to Table 4–18:

$<sup>(1) \</sup>quad Applicable \ to \ data \ rates \ from \ 600 \ Mbps \ to \ 3.125 \ Gbps. \ Specification \ is \ for \ measurement \ at \ the \ package \ ball.$

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

| Symbol/<br>Description       | Conditions                                                                                                                   | -3 Speed<br>Commercial Speed<br>Grade |        |      | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |        |        | -5 Speed<br>Commercial Speed<br>Grade |       |      | Unit |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|------|---------------------------------------------------------|--------|--------|---------------------------------------|-------|------|------|

|                              |                                                                                                                              | Min                                   | Тур    | Max  | Min                                                     | Тур    | Max    | Min                                   | Тур   | Max  |      |

| Fibre Channel Tra            | nsmit Jitter Generat                                                                                                         | ion <i>(8)</i> ,                      | (17)   |      |                                                         |        |        |                                       |       |      |      |

| Total jitter FC-1            | $\begin{tabular}{ll} REFCLK = \\ 106.25 \ MHz \\ Pattern = CRPAT \\ V_{OD} = 800 \ mV \\ No \ Pre-emphasis \\ \end{tabular}$ | -                                     | -      | 0.23 | 1                                                       | -      | 0.23   | -                                     | -     | 0.23 | UI   |

| Deterministic jitter<br>FC-1 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis                                     | -                                     | -      | 0.11 | -                                                       | -      | 0.11   | -                                     | -     | 0.11 | UI   |

| Total jitter FC-2            | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis                                     | -                                     | -      | 0.33 | -                                                       | -      | 0.33   | -                                     | -     | 0.33 | UI   |

| Deterministic jitter<br>FC-2 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis                                     | -                                     | -      | 0.2  | -                                                       | -      | 0.2    | -                                     | -     | 0.2  | UI   |

| Total jitter FC-4            | REFCLK = 106.25 MHz Pattern = CRPAT V <sub>OD</sub> = 800 mV No Pre-emphasis                                                 | -                                     | -      | 0.52 | -                                                       | -      | 0.52   | -                                     | -     | 0.52 | UI   |

| Deterministic jitter<br>FC-4 | REFCLK = 106.25 MHz Pattern = CRPAT V <sub>OD</sub> = 800 mV No Pre-emphasis                                                 | -                                     | -      | 0.33 | -                                                       | -      | 0.33   | -                                     | -     | 0.33 | UI   |

| Fibre Channel Red            | ceiver Jitter Tolerand                                                                                                       | ce (8), (                             | 18)    |      |                                                         |        |        |                                       |       |      |      |

| Deterministic jitter<br>FC-1 | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                                                        |                                       | > 0.37 | 7    | > 0.37                                                  |        | > 0.37 |                                       |       | UI   |      |

| Random jitter FC-1           | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                                                        |                                       | > 0.31 | l    |                                                         | > 0.31 | l      |                                       | > 0.3 | 1    | UI   |

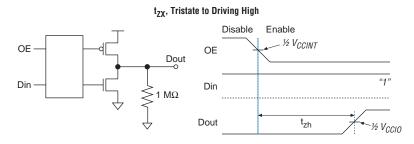

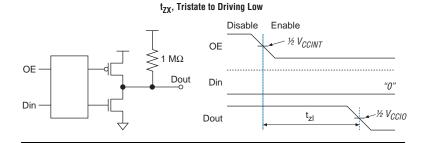

Figure 4–10. Measurement Setup for  $t_{zx}$

Table 4–54 specifies the input timing measurement setup.

| Table 4–54. Timing Measurement | Methodology for In    | put Pins (Part       | <b>1 of 2)</b> Notes | (1), (2), (3), (4) |

|--------------------------------|-----------------------|----------------------|----------------------|--------------------|

| I/O Chandard                   | Mea                   | Measurement Point    |                      |                    |

| I/O Standard                   | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns)       | VMEAS (V)          |

| LVTTL (5)                      | 3.135                 |                      | 3.135                | 1.5675             |

| LVCMOS (5)                     | 3.135                 |                      | 3.135                | 1.5675             |

| 2.5 V (5)                      | 2.375                 |                      | 2.375                | 1.1875             |

| 1.8 V (5)                      | 1.710                 |                      | 1.710                | 0.855              |

| 1.5 V (5)                      | 1.425                 |                      | 1.425                | 0.7125             |

| PCI (6)                        | 2.970                 |                      | 2.970                | 1.485              |

| PCI-X (6)                      | 2.970                 |                      | 2.970                | 1.485              |

| SSTL-2 Class I                 | 2.325                 | 1.163                | 2.325                | 1.1625             |

| SSTL-2 Class II                | 2.325                 | 1.163                | 2.325                | 1.1625             |

| SSTL-18 Class I                | 1.660                 | 0.830                | 1.660                | 0.83               |

| SSTL-18 Class II               | 1.660                 | 0.830                | 1.660                | 0.83               |

| 1.8-V HSTL Class I             | 1.660                 | 0.830                | 1.660                | 0.83               |

| Table 4–112. DLL Frequency Range Specifications (Part 2 of 2) |                                      |    |  |  |

|---------------------------------------------------------------|--------------------------------------|----|--|--|

| Frequency Mode                                                | Frequency Mode Frequency Range (MHz) |    |  |  |

| 3                                                             | 240 to 400 (-3 speed grade)          | 36 |  |  |

|                                                               | 240 to 350 (-4 and -5 speed grade)   | 36 |  |  |

| <b>Table 4–113. DQS Jitter Specifications for DLL-Delayed Clock (t</b> <sub>DQS-JITTER</sub> )  Note (1) |                 |                 |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|--|--|

| Number of DQS Delay Buffer Stages (2)                                                                    | Commercial (ps) | Industrial (ps) |  |  |  |

| 1                                                                                                        | 80              | 110             |  |  |  |

| 2                                                                                                        | 110             | 130             |  |  |  |

| 3                                                                                                        | 130             | 180             |  |  |  |

| 4                                                                                                        | 160             | 210             |  |  |  |

- Peak-to-peak period jitter on the phase-shifted DQS clock. For example, jitter on two delay stages under commercial conditions is 200 ps peak-to-peak or 100 ps.

- (2) Delay stages used for requested DQS phase shift are reported in a project's Compilation Report in the Quartus II software.

| Table 4–114. DQS Phase-Shift Error Specifications for DLL-Delayed Clock ( $t_{ m DQS\_PSERR}$ ) |                     |                     |                     |  |  |  |  |

|-------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|--|--|--|--|

| Number of DQS Delay Buffer Stages (1)                                                           | -3 Speed Grade (ps) | -4 Speed Grade (ps) | -5 Speed Grade (ps) |  |  |  |  |

| 1                                                                                               | 25                  | 30                  | 35                  |  |  |  |  |

| 2                                                                                               | 50                  | 60                  | 70                  |  |  |  |  |

| 3                                                                                               | 75                  | 90                  | 105                 |  |  |  |  |

| 4                                                                                               | 100                 | 120                 | 140                 |  |  |  |  |

(1) Delay stages used for request DQS phase shift are reported in a project's Compilation Report in the Quartus II software. For example, phase-shift error on two delay stages under -3 conditions is 50 ps peak-to-peak or 25 ps.

| Table 4–115. DQS Bus Clock Skew Adder Specifications (t <sub>DQS</sub> _CLOCK_SKEW_ADDER) |                               |  |  |  |

|-------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| Mode                                                                                      | DQS Clock Skew Adder (ps) (1) |  |  |  |

| 4 DQ per DQS                                                                              | 40                            |  |  |  |

| 9 DQ per DQS                                                                              | 70                            |  |  |  |

75

95

This skew specification is the absolute maximum and minimum skew. For example, skew on a 40 DQ group is 40 ps or 20 ps.

| Table 4–116. DQS Phase Offset Delay Per Stage (ps) Notes (1), (2), (3) |                 |     |                 |     |  |  |

|------------------------------------------------------------------------|-----------------|-----|-----------------|-----|--|--|

| Speed Grade                                                            | Positive Offset |     | Negative Offset |     |  |  |

|                                                                        | Min             | Max | Min             | Max |  |  |

| -3                                                                     | 10              | 15  | 8               | 11  |  |  |

| -4                                                                     | 10              | 15  | 8               | 11  |  |  |

| -5                                                                     | 10              | 16  | 8               | 12  |  |  |

(1) The delay settings are linear.

18 DQ per DQS

36 DQ per DQS

- (2) The valid settings for phase offset are -32 to +31.

- (3) The typical value equals the average of the minimum and maximum values.

# JTAG Timing Specifications

Figure 4–14 shows the timing requirements for the JTAG signals