Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1694                                                        |

| Number of Logic Elements/Cells | 33880                                                       |

| Total RAM Bits                 | 1369728                                                     |

| Number of I/O                  | 361                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30cf780c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Control and Status Signals**

The rx\_enapatternalign signal is the FPGA control signal that enables word alignment in non-automatic modes. The rx\_enapatternalign signal is not used in automatic modes (PCI Express, XAUI, GIGE, CPRI, and Serial RapidIO).

In manual alignment mode, after the rx\_enapatternalign signal is activated, the rx\_syncstatus signal goes high for one parallel clock cycle to indicate that the alignment pattern has been detected and the word boundary has been locked. If the rx\_enapatternalign is deactivated, the rx\_syncstatus signal acts as a re-synchronization signal to signify that the alignment pattern has been detected but not locked on a different word boundary.

When using the synchronization state machine, the rx\_syncstatus signal indicates the link status. If the rx\_syncstatus signal is high, link synchronization is achieved. If the rx\_syncstatus signal is low, synchronization has not yet been achieved, or there were enough code group errors to lose synchronization.

In some modes, the rx\_enapatternalign signal can be configured to operate as a rising edge signal.

For more information on manual alignment modes, refer to the *Stratix II GX Device Handbook*, volume 2.

When the rx\_enapatternalign signal is sensitive to the rising edge, each rising edge triggers a new boundary alignment search, clearing the rx syncstatus signal.

The rx\_patterndetect signal pulses high during a new alignment, and also whenever the alignment pattern occurs on the current word boundary.

#### SONET/SDH

In all the SONET/SDH modes, you can configure the word aligner to either align to A1A2 or A1A1A2A2 patterns. Once the pattern is found, the word boundary is aligned and the word aligner asserts the rx\_patterndetect signal for one clock cycle.

asserted. All 8B/10B control signals, such as disparity error or control detect, are pipelined with the data in the Stratix II GX receiver block and are edge aligned with the data.

Figure 2–23 shows how the 20-bit code is decoded to the 16-bit data + 2-bit control indicator.

Figure 2–23. 20-Bit to 16-Bit Decoding Process h1 a<sup>1</sup> b h С а 17 10 8 6 3 2 0 19 18 16 15 14 13 12 11 **MSB** LSB Cascaded 8B/10B Conversion CTRL[1..0] Parallel Data 15 14 13 13 11 10 9 8 7 6 5 3 2 0  $H^1$ G<sup>1</sup>  $E^1$  $D^1$  $C^1$ A<sup>1</sup> Е Н G D С В Α

There are two optional error status ports available in the 8B/10B decoder, rx\_errdetect and rx\_disperr. These status signals are aligned with the code group in which the error occurred.

#### Receiver State Machine

The receiver state machine operates in Basic, GIGE, PCI Express, and XAUI modes. In GIGE mode, the receiver state machine replaces invalid code groups with K30.7. In XAUI mode, the receiver state machine translates the XAUI PCS code group to the XAUI XGMII code group.

#### Byte Deserializer

The byte descrializer widens the transceiver data path before the FPGA interface. This reduces the rate at which the received data needs to be clocked at in the FPGA logic. The byte descrializer block is available in both single- and double-width modes.

The byte deserializer converts the one- or two-byte interface into a two- or four-byte-wide data path from the transceiver to the FPGA logic (see Table 2–9). The FPGA interface has a limit of 250 MHz, so the byte deserializer is needed to widen the bus width at the FPGA interface and

| Transmitter Ph. Transmitter Se Transmitter An. Transmitter An. Transmitter An. Transmitter An. Transmitter An. Transmitter An. BIST Generator Receiver Deske Receiver BA10 Receiver Phase Receiver PLL / Receiver PLL / Receiver PLL / Receiver AUII | Table 2–16. Reset Signal | Transmitter Phase Compensation FIFO Module/ Byte Serializer | Transmitter 8B/10B Encoder | Transmitter Serializer | Transmitter Analog Circuits | Transmitter PLL XX | Transmitter XAUI State Machine | BIST Generators | Receiver Deserializer | Receiver Word Aligner | Receiver Deskew FIFO Module | Receiver Rate Matcher | Receiver 8B/10B Decoder | Receiver Phase Comp FIFO Module/ Byte Deserializer | Receiver PLL / CRU | Receiver XAUI State Machine | ifiers   | Receiver Analog Circuits |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------|----------------------------|------------------------|-----------------------------|--------------------|--------------------------------|-----------------|-----------------------|-----------------------|-----------------------------|-----------------------|-------------------------|----------------------------------------------------|--------------------|-----------------------------|----------|--------------------------|

|                                                                                                                                                                                                                                                      | rx_digitalreset          |                                                             |                            |                        |                             |                    |                                |                 |                       | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           |                    | <b>✓</b>                    | <b>✓</b> |                          |

| In_digitalioned                                                                                                                                                                                                                                      | rx_analogreset           |                                                             |                            |                        |                             |                    |                                |                 | <b>\</b>              |                       |                             |                       |                         |                                                    | <b>✓</b>           |                             |          | <b>✓</b>                 |

|                                                                                                                                                                                                                                                      | tx_digitalreset          | <b>~</b>                                                    | <b>~</b>                   |                        |                             |                    | <b>✓</b>                       | <b>~</b>        |                       |                       |                             |                       |                         |                                                    |                    |                             |          |                          |

| rx_analogreset                                                                                                                                                                                                                                       | gxb_powerdown            | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>           | <b>✓</b>                       | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b> | <b>✓</b>                 |

| rx_analogreset                                                                                                                                                                                                                                       | gxb_enable               | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>           | <b>✓</b>                       | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b> | <b>✓</b>                 |

#### Voltage Reference Capabilities

Stratix II GX transceivers provide voltage reference and bias circuitry. To set up internal bias for controlling the transmitter output driver voltage swings, as well as to provide voltage and current biasing for other analog circuitry, the device uses an internal bandgap voltage reference of 0.7 V. An external 2-K $\Omega$  resistor connected to ground generates a constant bias current (independent of power supply drift, process changes, or temperature variation). An on-chip resistor generates a tracking current that tracks on-chip resistor variation. These currents are mirrored and distributed to the analog circuitry in each channel.

For more information, refer to the *DC and Switching Characteristics* chapter in volume 1 of the *Stratix II GX Handbook*.

#### **M4K RAM Blocks**

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–51.

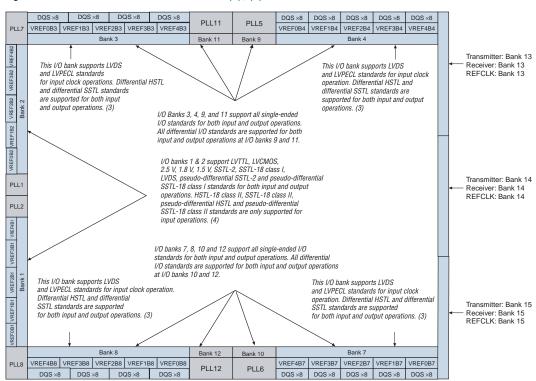

**Figure 2–87. Stratix II GX I/O Banks** Notes (1), (2)

#### Notes to Figure 2-87:

- Figure 2–87 is a top view of the silicon die that corresponds to a reverse view for flip-chip packages. It is a graphical representation only.

- (2) Depending on the size of the device, different device members have different numbers of  $V_{REF}$  groups. Refer to the pin list and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks.

- (4) Horizontal I/O banks feature SERDES and DPA circuitry for high-speed differential I/O standards. See the High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II Device Handbook 2 for more information on differential I/O standards.

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different  $V_{\rm CCIO}$  level independently. Each bank also has dedicated VREF pins to support the voltage-referenced standards (such as SSTL-2).

Each I/O bank can support multiple standards with the same  $V_{\text{CCIO}}$  for input and output pins. Each bank can support one  $V_{\text{REF}}$  voltage level. For example, when  $V_{\text{CCIO}}$  is 3.3 V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs.

For more information on tolerance specifications for differential on-chip termination, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

#### On-Chip Series Termination without Calibration

Stratix II GX devices support driver impedance matching to provide the I/O driver with controlled output impedance that closely matches the impedance of the transmission line. As a result, reflections can be significantly reduced. Stratix II GX devices support on-chip series termination for single-ended I/O standards with typical  $R_{\rm S}$  values of 25 and 50  $\Omega$ . Once matching impedance is selected, current drive strength is no longer selectable. Table 2–34 shows the list of output standards that support on-chip series termination without calibration.

For more information about series on-chip termination supported by Stratix II GX devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination without calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

#### On-Chip Series Termination with Calibration

Stratix II GX devices support on-chip series termination with calibration in column I/O pins in top and bottom banks. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip series termination calibration circuit compares the total impedance of each I/O buffer to the external 25- $\Omega$ or 50- $\Omega$ resistors connected to the RUP and RDN pins, and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

For more information about series on-chip termination supported by Stratix II GX devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 2–42. Docu                | ment Revision History (Part 4 of 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Summary of Changes |

|                                 | Updated:  "Transmitter PLLs"  "Transmitter Phase Compensation FIFO Buffer"  "8B/10B Encoder"  "Byte Serializer"  "Programmable Output Driver"  "Receiver PLL & CRU"  "Programmable Pre-Emphasis"  "Receiver Input Buffer"  "Control and Status Signals"  "Programmable Run Length Violation"  "Channel Aligner"  "Basic Mode"  "Byte Ordering Block"  "Receiver Phase Compensation FIFO Buffer"  "Loopback Modes"  "Serial Loopback"  "Parallel Loopback"  "Regional Clock Network"  "MultiVolt I/O Interface"  "High-Speed Differential I/O with DPA Support" |                    |

|                                 | Updated bulleted lists at the beginning of the "Transceivers" section.  Added reference to the "Transmit Buffer"                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |

|                                 | section.  Deleted the Programmable V <sub>OD</sub> table from the "Programmable Output Driver" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

|                                 | Changed "PLD Interface" heading to "Parallel Data Width" heading in Table 2–14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |

|                                 | Deleted "Global & Regional Clock<br>Connections from Right Side Clock Pins &<br>Fast PLL Outputs" table.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

|                                 | Updated notes to Tables 2-29 and 2-37.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

|                                 | Updated notes to Figures 2–72, 2–73 and 2–74.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |

|                                 | Updated bulleted list in the "Advanced I/O Standard Support" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

The Stratix II GX device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix II GX devices.

| Table 3–2. Stratix II GX Boundary-Sca | nn Register Length            |

|---------------------------------------|-------------------------------|

| Device                                | Boundary-Scan Register Length |

| EP2SGX30                              | 1,320                         |

| EP2SGX60                              | 1,506                         |

| EP2SGX90                              | 2,016                         |

| EP2SGX130                             | 2,454                         |

| Table 3–3. 32-Bit | Stratix II GX Device | e IDCODE              |                                    |             |

|-------------------|----------------------|-----------------------|------------------------------------|-------------|

|                   |                      | IDCODE (32 Bi         | its)                               |             |

| Device            | Version (4 Bits)     | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) |

| EP2SGX30          | 0000                 | 0010 0000 1110 0001   | 000 0110 1110                      | 1           |

| EP2SGX60          | 0000                 | 0010 0000 1110 0010   | 000 0110 1110                      | 1           |

| EP2SGX90          | 0000                 | 0010 0000 1110 0011   | 000 0110 1110                      | 1           |

| EP2SGX130         | 0000                 | 0010 0000 1110 0100   | 000 0110 1110                      | 1           |

# SignalTap II Embedded Logic Analyzer

Stratix II GX devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

### **Configuration**

The logic, circuitry, and interconnects in the Stratix II GX architecture are configured with CMOS SRAM elements. Altera® FPGAs are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.

Stratix II GX devices are configured at system power-up with data stored in an Altera configuration device or provided by an external controller (for example, a MAX® II device or microprocessor). You can configure Stratix II GX devices using the fast passive parallel (FPP), active serial

# Referenced Documents

This chapter references the following documents:

- AN 357: Error Detection Using CRC in Altera FPGA Devices

- AN 414: An Embedded Solution for PLD JTAG Configuration

- AN 418 SRunner: An Embedded Solution for Serial Configuration Device Programming

- Configuring Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

- Configuring the MicroBlaster Fast Passive Parallel Software Driver White Paver

- Configuring the MicroBlaster Passive Serial Software Driver White Paper

- MorphIO: An I/O Reconfiguration Solution for Altera Devices White Paper

- PLLs in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

- Remote System Upgrades with Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

- Serial Configuration Devices (EPCS1, EPCS4, EPCS64, and EPCS128)

Data Sheet in the Configuration Handbook

- Stratix II GX Architecture chapter in volume 1 of the Stratix II GX Device Handbook.

## Document Revision History

Table 3–6 shows the revision history for this chapter.

| Table 3–6. Docu                 | ment Revision History                                                 |                                                         |

|---------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------|

| Date and<br>Document<br>Version | Changes Made                                                          | Summary of Changes                                      |

| October 2007<br>v1.4            | Minor text edits.                                                     | _                                                       |

| August 2007<br>v1.3             | Updated the note in the "IEEE Std. 1149.1 JTAG Boundary-Scan Support" | _                                                       |

|                                 | Updated Table 3–3.                                                    | _                                                       |

|                                 | Added the "Referenced Documents" section.                             | _                                                       |

| May 2007<br>v1.2                | Updated the "Temperature Sensing Diode (TSD)" section.                | _                                                       |

| February 2007<br>v1.1           | Added the "Document Revision History" section to this chapter.        | Added support information for the Stratix II GX device. |

| October 2005<br>v1.0            | Added chapter to the Stratix II GX Device Handbook.                   | _                                                       |

| Table 4–6. Stra                                                   | atix II GX Trans | ceiver Blo | ck AC S                                                                                                                                                                                                                                        | pecificat                     | ion (Part                                                                               | 4 of 6)                                                            |                                                                             |                                                                        |                     |      |      |

|-------------------------------------------------------------------|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|------|------|

| Symbol /<br>Description                                           | Conditions       |            | ed Comn<br>eed Grad                                                                                                                                                                                                                            |                               |                                                                                         | ed Comr<br>Iustrial<br>Grade                                       |                                                                             |                                                                        | ed Com<br>beed Gra  |      | Unit |

|                                                                   |                  | Min        | Тур                                                                                                                                                                                                                                            | Max                           | Min                                                                                     | Тур                                                                | Max                                                                         | Min                                                                    | Тур                 | Max  |      |

| Bandwidth at                                                      | BW = Low         | -          | 30                                                                                                                                                                                                                                             | -                             | ı                                                                                       | 30                                                                 | -                                                                           | -                                                                      | 30                  | -    | MHz  |

| 3.125 Gbps                                                        | BW = Med         | -          | 40                                                                                                                                                                                                                                             | -                             | ı                                                                                       | 40                                                                 | -                                                                           | -                                                                      | 40                  | -    | MHz  |

|                                                                   | BW = High        | -          | 50                                                                                                                                                                                                                                             | -                             | ı                                                                                       | 50                                                                 | -                                                                           | -                                                                      | 50                  | -    | MHz  |

| Bandwidth at                                                      | BW = Low         | -          | 35                                                                                                                                                                                                                                             | -                             | -                                                                                       | 35                                                                 | -                                                                           | -                                                                      | 35                  | -    | MHz  |

| 2.5 Gbps                                                          | BW = Med         | -          | 50                                                                                                                                                                                                                                             | -                             | -                                                                                       | 50                                                                 | -                                                                           | -                                                                      | 50                  | -    | MHz  |

|                                                                   | BW = High        | -          | 60                                                                                                                                                                                                                                             | -                             | -                                                                                       | 60                                                                 | -                                                                           | -                                                                      | 60                  | -    | MHz  |

| Return loss<br>differential<br>mode<br>Return loss<br>common mode |                  |            |                                                                                                                                                                                                                                                | 5<br>10<br>875 GHz<br>5<br>10 | 00 MHz to<br>0 MHz to<br>0 MHz to<br>2 to 10 GH<br>100 MHz to<br>0 MHz to<br>2 to 10 GH | 1.25 GH<br>4.875 GI<br>z (OIF/C<br>o 2.5 GI<br>1.25 GH<br>4.875 GI | z (PCI-É)<br>Hz (OIF/C<br>CEI): 16.6<br>Hz (XAUI)<br>Hz (PCI-E<br>Hz (OIF/C | : -10 dB<br>CEI): -8d<br>dB/deca<br>): -6 dB<br>E): -6 dB<br>CEI): -6d | B<br>ade slope<br>B |      |      |

| Programmable<br>PPM detector<br>(2)                               |                  | 2          | 4.875 GHz to 10 GHz (OIF/CEI): 16.6 dB/decade slope       ±62.5, 100, 125, 200,     ±62.5, 100, 125, 200,     ±62.5, 100, 125, 200,     125, 200, 300,       250, 300,     250, 300,     250, 300,       500, 1000     500, 1000     500, 1000 |                               |                                                                                         |                                                                    |                                                                             |                                                                        |                     |      |      |

| Run length (3), (9)                                               |                  |            | 80 80 80                                                                                                                                                                                                                                       |                               |                                                                                         |                                                                    |                                                                             |                                                                        |                     |      | UI   |

| Programmable equalization                                         |                  | -          | -                                                                                                                                                                                                                                              | 16                            | -                                                                                       | -                                                                  | 16                                                                          | -                                                                      | -                   | 16   | dB   |

| Signal detect/loss threshold (4)                                  |                  | 65         | -                                                                                                                                                                                                                                              | 175                           | 65                                                                                      | -                                                                  | 175                                                                         | 65                                                                     | -                   | 175  | mV   |

| CDR LTR TIme (5), (9)                                             |                  | -          | -                                                                                                                                                                                                                                              | 75                            | -                                                                                       | -                                                                  | 75                                                                          | -                                                                      | -                   | 75   | us   |

| CDR Minimum<br>T1b (6), (9)                                       |                  | 15         | -                                                                                                                                                                                                                                              | -                             | 15                                                                                      | -                                                                  | -                                                                           | 15                                                                     | -                   | -    | us   |

| LTD lock time (7), (9)                                            |                  | 0          | 100                                                                                                                                                                                                                                            | 4000                          | 0                                                                                       | 100                                                                | 4000                                                                        | 0                                                                      | 100                 | 4000 | ns   |

| Data lock time from rx_freqloc ked (8), (9)                       |                  | -          | -                                                                                                                                                                                                                                              | 4                             | -                                                                                       | -                                                                  | 4                                                                           | -                                                                      | -                   | 4    | us   |

| Programmable DC gain                                              |                  |            | 0, 3, 6                                                                                                                                                                                                                                        |                               |                                                                                         | 0, 3, 6                                                            |                                                                             |                                                                        | 0, 3, 6             |      | dB   |

| Transmitter                                                       |                  | •          |                                                                                                                                                                                                                                                |                               |                                                                                         |                                                                    |                                                                             | •                                                                      |                     |      |      |

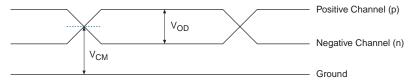

Figure 4-4. Transmitter Output Waveform

# Differential Waveform $V_{OD}$ (diff peak-peak) = 2 x $V_{OD}$ (single-ended) $V_{OD}$ p-n=0 $V_{OD}$

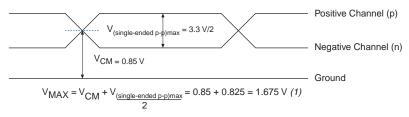

Figure 4-5. Maximum Receiver Input Pin Voltage

#### Single-Ended Waveform

*Note to Figure 4–5:*

(1) The absolute  $V_{MAX}$  that the receiver input pins can tolerate is 2 V.

Tables 4–7 through 4–12 show the typical  $V_{OD}$  for data rates from 600 Mbps to 6.375 Gbps. The specification is for measurement at the package ball.

| Table 4–7. Typical           | I V <sub>OD</sub> Setting, | TX Term = 1                    | <b>00</b> $\Omega$ Note (1) | )   |      |      |      |  |  |  |  |  |  |

|------------------------------|----------------------------|--------------------------------|-----------------------------|-----|------|------|------|--|--|--|--|--|--|

| V <sub>CCH</sub> TX = 1.5 V  |                            | V <sub>OD</sub> Setting (mV)   |                             |     |      |      |      |  |  |  |  |  |  |

|                              | 200                        | 200 400 600 800 1000 1200 1400 |                             |     |      |      |      |  |  |  |  |  |  |

| V <sub>OD</sub> Typical (mV) | 220                        | 430                            | 625                         | 830 | 1020 | 1200 | 1350 |  |  |  |  |  |  |

Note to Table 4-7:

(1) Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

Table 4–19 shows the Stratix II GX transceiver block AC specifications.

| Symbol/<br>Description                 | Conditions                                                                                | -3 Speed<br>Commercial Speed<br>Grade |     |      | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |     |      | Comi | Unit |      |    |

|----------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|-----|------|---------------------------------------------------------|-----|------|------|------|------|----|

|                                        |                                                                                           | Min                                   | Тур | Max  | Min                                                     | Тур | Max  | Min  | Тур  | Max  |    |

| SONET/SDH Trans                        | smit Jitter Generation                                                                    | n <i>(7)</i>                          |     |      |                                                         |     |      |      |      |      |    |

| Peak-to-peak jitter<br>at 622.08 Mbps  | REFCLK = 77.76 MHz Pattern = PRBS23 V <sub>OD</sub> = 800 mV No Pre-emphasis              | -                                     | -   | 0.1  | -                                                       | -   | 0.1  | -    | -    | 0.1  | UI |

| RMS jitter at<br>622.08 Mbps           | REFCLK = 77.76 MHz Pattern = PRBS23 V <sub>OD</sub> = 800 mV No Pre-emphasis              | -                                     | -   | 0.01 | -                                                       | -   | 0.01 | -    | -    | 0.01 | UI |

| Peak-to-peak jitter<br>at 2488.32 Mbps | REFCLK =<br>155.52 MHz<br>Pattern = PRBS23<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                                     | -   | 0.1  | -                                                       | -   | 0.1  | -    | -    | 0.1  | UI |

| RMS jitter at<br>2488.32 Mbps          | REFCLK = 155.52 MHz Pattern = PRBS23 V <sub>OD</sub> = 800 mV No Pre-emphasis             | -                                     | -   | 0.01 | -                                                       | -   | 0.01 |      | -    | 0.01 | UI |

| Symbol/<br>Description                 | Conditions                                                                                                                 | -3 Speed<br>Commercial Speed<br>Grade |     |      | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |      | Comi  | Unit  |      |    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|------|---------------------------------------------------------|-------|------|-------|-------|------|----|

|                                        |                                                                                                                            | Min                                   | Тур | Max  | Min                                                     | Тур   | Max  | Min   | Тур   | Max  |    |

| Peak-to-peak jitter                    | Jitter frequency = 22.1 KHz                                                                                                | > 8.5                                 |     |      | > 8.5                                                   |       |      |       | > 8.5 | 5    | UI |

| Peak-to-peak jitter                    | Jitter frequency = 1.875 MHz                                                                                               | > 0.1                                 |     |      | > 0.1                                                   |       |      | > 0.1 |       |      | UI |

| Peak-to-peak jitter                    | Jitter frequency = 20<br>MHz                                                                                               | > 0.1                                 |     |      | > 0.1                                                   |       |      | > 0.1 |       |      | UI |

| PCI Express Trans                      | smit Jitter Generation                                                                                                     | 1 <i>(10)</i>                         |     |      |                                                         |       |      |       |       |      |    |

| Total jitter at 2.5<br>Gbps            | Compliance pattern $V_{OD} = 800 \text{ mV}$ Pre-emphasis (1st post-tap) = Setting 5                                       | -                                     | -   | 0.25 | -                                                       | -     | 0.25 | -     | -     | 0.25 | UI |

| PCI Express Rece                       | iver Jitter Tolerance                                                                                                      | (10)                                  |     |      |                                                         |       |      |       |       |      |    |

| Total jitter at 2.5<br>Gbps            | Compliance pattern<br>No Equalization<br>DC gain = 3 dB                                                                    | > 0.6                                 |     |      |                                                         | > 0.6 |      |       | > 0.6 | 3    | UI |

| Serial RapidIO Tra                     | nsmit Jitter Generati                                                                                                      | on (11,                               | )   |      | ı                                                       |       |      |       |       |      |    |

| Deterministic Jitter<br>(peak-to-peak) | Data Rate = 1.25,<br>2.5, 3.125 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                                     | -   | 0.17 | -                                                       | -     | 0.17 | -     | -     | 0.17 | UI |

| Total Jitter<br>(peak-to-peak)         | Data Rate = 1.25,<br>2.5, 3.125 Gbps<br>REFCLK = 125 MHz<br>Pattern = CJPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis | -                                     | -   | 0.35 | -                                                       | -     | 0.35 | -     | -     | 0.35 | UI |

| Table 4–19. Strati                                  | ix II GX Transceiver Bl                                                                                                                 | lock AC | Specif                                | fication | Notes ( | (1), (2)                                                | , (3) <b>(P</b> | art 10 | of 19)                   |         |      |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------|----------|---------|---------------------------------------------------------|-----------------|--------|--------------------------|---------|------|

| Symbol/<br>Description                              | Conditions                                                                                                                              |         | -3 Speed<br>Commercial Speed<br>Grade |          |         | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |                 |        | -5 Spe<br>nercia<br>Grad | l Speed | Unit |

|                                                     |                                                                                                                                         | Min     | Тур                                   | Max      | Min     | Тур                                                     | Max             | Min    | Тур                      | Max     |      |

| Sinusoidal Jitter                                   | Jitter Frequency = 1.875 MHz Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB                    |         | > 0.1                                 |          |         | -                                                       |                 |        | -                        |         | UI   |

| Tolerance<br>(peak-to-peak)                         | Jitter Frequency = 20 MHz Data Rate = 3.75 Gbps REFCLK = 187.5 MHz Pattern = CJPAT No Equalization DC Gain = 3 dB                       |         | > 0.1                                 |          |         | -                                                       |                 |        | -                        |         | UI   |

| (OIF) CEI Transmi                                   | tter Jitter Generation                                                                                                                  | (14)    |                                       |          | ı       |                                                         |                 |        |                          |         |      |

| Total Jitter<br>(peak-to-peak)                      | Data Rate =<br>6.375 Gbps<br>REFCLK =<br>318.75 MHz<br>Pattern = PRBS15<br>Vod=1000 mV (5)<br>NoPre-emphasis<br>BER = 10 <sup>-12</sup> |         |                                       | 0.3      |         |                                                         | N/A             |        |                          | N/A     | UI   |

|                                                     | r Jitter Tolerance (14)                                                                                                                 | )       |                                       |          | 1       |                                                         |                 |        |                          |         |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak) | Data Rate = 6.375 Gbps Pattern = PRBS31 Equalizer Setting = 15 DCGain = 0 dB BER = 10 <sup>-12</sup>                                    |         | > 0.67                                | 5        |         | N/A                                                     |                 |        | N/A                      |         | UI   |

| Table 4–54. Timing Measurement Methodology for Input Pins (Part 2 of 2)       Notes (1), (2), (3), (4) |                       |                      |                |                   |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------|-------------------|--|--|--|--|--|--|--|--|

| I/O Standard                                                                                           | Mea                   | surement Cond        | ditions        | Measurement Point |  |  |  |  |  |  |  |  |

| I/O Standard                                                                                           | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns) | VMEAS (V)         |  |  |  |  |  |  |  |  |

| 1.8-V HSTL Class II                                                                                    | 1.660                 | 0.830                | 1.660          | 0.83              |  |  |  |  |  |  |  |  |

| 1.5-V HSTL Class I                                                                                     | 1.375                 | 0.688                | 1.375          | 0.6875            |  |  |  |  |  |  |  |  |

| 1.5-V HSTL Class II                                                                                    | 1.375                 | 0.688                | 1.375          | 0.6875            |  |  |  |  |  |  |  |  |

| 1.2-V HSTL with OCT                                                                                    | 1.140                 | 0.570                | 1.140          | 0.570             |  |  |  |  |  |  |  |  |

| Differential SSTL-2 Class I                                                                            | 2.325                 | 1.163                | 2.325          | 1.1625            |  |  |  |  |  |  |  |  |

| Differential SSTL-2 Class II                                                                           | 2.325                 | 1.163                | 2.325          | 1.1625            |  |  |  |  |  |  |  |  |

| Differential SSTL-18 Class I                                                                           | 1.660                 | 0.830                | 1.660          | 0.83              |  |  |  |  |  |  |  |  |

| Differential SSTL-18 Class II                                                                          | 1.660                 | 0.830                | 1.660          | 0.83              |  |  |  |  |  |  |  |  |

| 1.5-V differential HSTL Class I                                                                        | 1.375                 | 0.688                | 1.375          | 0.6875            |  |  |  |  |  |  |  |  |

| 1.5-V differential HSTL Class II                                                                       | 1.375                 | 0.688                | 1.375          | 0.6875            |  |  |  |  |  |  |  |  |

| 1.8-V differential HSTL Class I                                                                        | 1.660                 | 0.830                | 1.660          | 0.83              |  |  |  |  |  |  |  |  |

| 1.8-V differential HSTL Class II                                                                       | 1.660                 | 0.830                | 1.660          | 0.83              |  |  |  |  |  |  |  |  |

| LVDS                                                                                                   | 2.325                 |                      | 0.100          | 1.1625            |  |  |  |  |  |  |  |  |

| LVPECL                                                                                                 | 3.135                 |                      | 0.100          | 1.5675            |  |  |  |  |  |  |  |  |

#### Notes to Table 4–54:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is 0.5 V<sub>CCIO</sub>.

- (3) Output measuring point is  $0.5\,\mathrm{V}_{\mathrm{CC}}$  at internal node.

- (4) Input edge rate is 1 V/ns.

(5) Less than 50-mV ripple on V<sub>CCIO</sub> and V<sub>CCPD</sub>, V<sub>CCINT</sub> = 1.15 V with less than 30-mV ripple.

- (6)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$ .

| Symbol                       | Parameter                                                                                       | -3 Speed<br>Grade <i>(1)</i> |      | -3 Speed<br>Grade <i>(2)</i> |      | -4 Speed<br>Grade |      | -5 Speed<br>Grade |      | Unit |

|------------------------------|-------------------------------------------------------------------------------------------------|------------------------------|------|------------------------------|------|-------------------|------|-------------------|------|------|

| •                            |                                                                                                 | Min                          | Max  | Min                          | Max  | Min               | Max  | Min               | Max  |      |

| t <sub>INREG2PIPE9</sub>     | Input register to DSP block pipeline register in 9 × 9-bit mode                                 | 1312                         | 2030 | 1312                         | 2131 | 1312              | 2266 | 1312              | 2720 | ps   |

| t <sub>INREG2PIPE18</sub>    | Input register to<br>DSP block pipeline<br>register in 18 × 18-<br>bit mode                     | 1302                         | 2010 | 1302                         | 2110 | 1302              | 2244 | 1302              | 2693 | ps   |

| t <sub>INREG2PIPE36</sub>    | Input register to<br>DSP block pipeline<br>register in 36 × 36-<br>bit mode                     | 1302                         | 2010 | 1302                         | 2110 | 1302              | 2244 | 1302              | 2693 | ps   |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP block pipeline<br>register to output<br>register delay in<br>two-multipliers<br>adder mode  | 924                          | 1450 | 924                          | 1522 | 924               | 1618 | 924               | 1943 | ps   |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP block pipeline<br>register to output<br>register delay in<br>four-multipliers<br>adder mode | 1134                         | 1850 | 1134                         | 1942 | 1134              | 2065 | 1134              | 2479 | ps   |

| t <sub>PD9</sub>             | Combinational input to output delay for $9 \times 9$                                            | 2100                         | 2880 | 2100                         | 3024 | 2100              | 3214 | 2100              | 3859 | ps   |

| t <sub>PD18</sub>            | Combinational input to output delay for 18 × 18                                                 | 2110                         | 2990 | 2110                         | 3139 | 2110              | 3337 | 2110              | 4006 | ps   |

| t <sub>PD36</sub>            | Combinational input to output delay for 36 × 36                                                 | 2939                         | 4450 | 2939                         | 4672 | 2939              | 4967 | 2939              | 5962 | ps   |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                       | 2212                         |      | 2322                         |      | 2469              |      | 2964              |      | ps   |

| t <sub>CLKL</sub>            | Minimum clock low time                                                                          | 1190                         |      | 1249                         |      | 1328              |      | 1594              |      | ps   |

| t <sub>CLKH</sub>            | Minimum clock high time                                                                         | 1190                         |      | 1249                         |      | 1328              |      | 1594              |      | ps   |

$<sup>(1) \</sup>quad \text{This column refers to $-3$ speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.}$

<sup>(2)</sup> This column refers to –3 speed grades for EP2SGX130 devices.

| Table 4-60.              | M4K Block Interna                                       | l Timing           | Micropa | rameters       | (Part 2 | of 2)          | Note (1 | )              |      |      |

|--------------------------|---------------------------------------------------------|--------------------|---------|----------------|---------|----------------|---------|----------------|------|------|

| Symbol                   | Parameter                                               | -3 Speed Grade (2) |         | -3 Speed Grade |         | -4 Speed Grade |         | -5 Speed Grade |      | Unit |

| -<br>I                   |                                                         | Min                | Max     | Min            | Max     | Min            | Max     | Min            | Max  |      |

| t <sub>M4KDATABH</sub>   | B port data hold time after clock                       | 203                |         | 213            |         | 226            |         | 272            |      | ps   |

| t <sub>M4KRADDRBSU</sub> | B port address<br>setup time before<br>clock            | 22                 |         | 23             |         | 24             |         | 29             |      | ps   |

| t <sub>M4KRADDRBH</sub>  | B port address<br>hold time after<br>clock              | 203                |         | 213            |         | 226            |         | 272            |      | ps   |

| t <sub>M4KDATACO1</sub>  | Clock-to-output<br>delay when using<br>output registers | 334                | 524     | 334            | 549     | 334            | 584     | 334            | 701  | ps   |

| t <sub>M4KDATACO2</sub>  | Clock-to-output<br>delay without<br>output registers    | 1616               | 2453    | 1616           | 2574    | 1616           | 2737    | 1616           | 3286 | ps   |

| t <sub>M4KCLKH</sub>     | Minimum clock high time                                 | 1250               |         | 1312           |         | 1395           |         | 1675           |      | ps   |

| t <sub>M4KCLKL</sub>     | Minimum clock low time                                  | 1250               |         | 1312           |         | 1395           |         | 1675           |      | ps   |

| t <sub>M4KCLR</sub>      | Minimum clear pulse width                               | 144                | _       | 151            |         | 160            | -       | 192            |      | ps   |

- (1) The M512 block  $f_{MAX}$  obtained using the Quartus II software does not necessarily equal to 1/TM4KRC.

- (2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

- (3) This column refers to –3 speed grades for EP2SGX130 devices.

| Table 4–61. M-RAM Block Internal Timing Microparameters (Part 1 of 2)         Note (1) |                                              |                       |      |                       |      |                   |      |                   |      |      |

|----------------------------------------------------------------------------------------|----------------------------------------------|-----------------------|------|-----------------------|------|-------------------|------|-------------------|------|------|

| Symbol                                                                                 | Parameter                                    | -3 Speed<br>Grade (2) |      | -3 Speed<br>Grade (3) |      | -4 Speed<br>Grade |      | -5 Speed<br>Grade |      | Unit |

|                                                                                        |                                              | Min                   | Max  | Min                   | Max  | Min               | Max  | Min               | Max  |      |

| t <sub>MEGARC</sub>                                                                    | Synchronous read cycle time                  | 1866                  | 2774 | 1866                  | 2911 | 1866              | 3096 | 1866              | 3716 | ps   |

| t <sub>MEGAWERESU</sub>                                                                | Write or read enable setup time before clock | 144                   |      | 151                   |      | 160               |      | 192               |      | ps   |

| t <sub>MEGAWEREH</sub>                                                                 | Write or read enable hold time after clock   | 39                    |      | 40                    |      | 43                |      | 52                |      | ps   |

| Symbol                   | Parameter                                         | -3 Speed<br>Grade <i>(2)</i> |      | -3 Speed<br>Grade <i>(3)</i> |      | -4 Speed<br>Grade |      | -5 Speed<br>Grade |      | Unit |

|--------------------------|---------------------------------------------------|------------------------------|------|------------------------------|------|-------------------|------|-------------------|------|------|

| -                        |                                                   | Min                          | Max  | Min                          | Max  | Min               | Max  | Min               | Max  |      |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock               | -9                           |      | -10                          |      | -11               |      | -13               |      | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                 | 39                           |      | 40                           |      | 43                |      | 52                |      | ps   |

| t <sub>MEGADATAASU</sub> | A port data setup time before clock               | 50                           |      | 52                           |      | 55                |      | 67                |      | ps   |

| t <sub>MEGADATAAH</sub>  | A port data hold time after clock                 | 243                          |      | 255                          |      | 271               |      | 325               |      | ps   |

| t <sub>MEGAADDRASU</sub> | A port address setup time before clock            | 589                          |      | 618                          |      | 657               |      | 789               |      | ps   |

| t <sub>MEGAADDRAH</sub>  | A port address hold time after clock              | -347                         |      | -365                         |      | -388              |      | -465              |      | ps   |

| t <sub>MEGADATABSU</sub> | B port setup time before clock                    | 50                           |      | 52                           |      | 55                |      | 67                |      | ps   |

| t <sub>MEGADATABH</sub>  | B port hold time after clock                      | 243                          |      | 255                          |      | 271               |      | 325               |      | ps   |

| t <sub>MEGAADDRBSU</sub> | B port address setup time before clock            | 589                          |      | 618                          |      | 657               |      | 789               |      | ps   |

| t <sub>MEGAADDRBH</sub>  | B port address hold time after clock              | -347                         |      | -365                         |      | -388              |      | -465              |      | ps   |

| t <sub>MEGADATACO1</sub> | Clock-to-output delay when using output registers | 480                          | 715  | 480                          | 749  | 480               | 797  | 480               | 957  | ps   |

| t <sub>MEGADATACO2</sub> | Clock-to-output delay without output registers    | 1950                         | 2899 | 1950                         | 3042 | 1950              | 3235 | 1950              | 3884 | ps   |

| t <sub>MEGACLKL</sub>    | Minimum clock low time                            | 1250                         |      | 1312                         |      | 1395              |      | 1675              |      | ps   |

| t <sub>MEGACLKH</sub>    | Minimum clock high time                           | 1250                         |      | 1312                         |      | 1395              |      | 1675              |      | ps   |

| t <sub>MEGACLR</sub>     | Minimum clear pulse width                         | 144                          |      | 151                          |      | 160               |      | 192               |      | ps   |

<sup>(1)</sup> The M512 block  $f_{MAX}$  obtained using the Quartus II software does not necessarily equal to 1/TMEGARC.

<sup>(2)</sup> This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

<sup>(3)</sup> This column refers to –3 speed grades for EP2SGX130 devices.

| I/O Standard | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|--------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| 1.8-V HSTL   | 4 mA              | t <sub>OP</sub>  | 956                                      | 1608                  | 1687                  | 1794              | 1943              | ps   |

| Class I      |                   | t <sub>DIP</sub> | 978                                      | 1674                  | 1757                  | 1868              | 2033              | ps   |

|              | 6 mA              | t <sub>OP</sub>  | 962                                      | 1595                  | 1673                  | 1779              | 1928              | ps   |

|              |                   | t <sub>DIP</sub> | 984                                      | 1661                  | 1743                  | 1853              | 2018              | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 940                                      | 1586                  | 1664                  | 1769              | 1917              | ps   |

|              |                   | t <sub>DIP</sub> | 962                                      | 1652                  | 1734                  | 1843              | 2007              | ps   |

|              | 10 mA             | t <sub>OP</sub>  | 944                                      | 1591                  | 1669                  | 1775              | 1923              | ps   |

|              |                   | t <sub>DIP</sub> | 966                                      | 1657                  | 1739                  | 1849              | 2013              | ps   |

|              | 12 mA (1)         | t <sub>OP</sub>  | 936                                      | 1585                  | 1663                  | 1768              | 1916              | ps   |

|              |                   | t <sub>DIP</sub> | 958                                      | 1651                  | 1733                  | 1842              | 2006              | ps   |

| 1.8-V HSTL   | 16 mA             | t <sub>OP</sub>  | 919                                      | 1385                  | 1453                  | 1545              | 1680              | ps   |

| Class II     |                   | t <sub>DIP</sub> | 941                                      | 1451                  | 1523                  | 1619              | 1770              | ps   |

|              | 18 mA             | t <sub>OP</sub>  | 921                                      | 1394                  | 1462                  | 1555              | 1691              | ps   |

|              |                   | t <sub>DIP</sub> | 943                                      | 1460                  | 1532                  | 1629              | 1781              | ps   |

|              | 20 mA (1)         | t <sub>OP</sub>  | 921                                      | 1402                  | 1471                  | 1564              | 1700              | ps   |

|              |                   | t <sub>DIP</sub> | 943                                      | 1468                  | 1541                  | 1638              | 1790              | ps   |

| 1.5-V HSTL   | 4 mA              | t <sub>OP</sub>  | 956                                      | 1607                  | 1686                  | 1793              | 1942              | ps   |

| Class I      |                   | t <sub>DIP</sub> | 978                                      | 1673                  | 1756                  | 1867              | 2032              | ps   |

|              | 6 mA              | t <sub>OP</sub>  | 961                                      | 1588                  | 1666                  | 1772              | 1920              | ps   |

|              |                   | t <sub>DIP</sub> | 983                                      | 1654                  | 1736                  | 1846              | 2010              | ps   |

|              | 8 mA              | t <sub>OP</sub>  | 943                                      | 1590                  | 1668                  | 1774              | 1922              | ps   |

|              |                   | t <sub>DIP</sub> | 965                                      | 1656                  | 1738                  | 1848              | 2012              | ps   |

|              | 10 mA             | t <sub>OP</sub>  | 943                                      | 1592                  | 1670                  | 1776              | 1924              | ps   |

|              |                   | t <sub>DIP</sub> | 965                                      | 1658                  | 1740                  | 1850              | 2014              | ps   |

|              | 12 mA (1)         | t <sub>OP</sub>  | 937                                      | 1590                  | 1668                  | 1774              | 1922              | ps   |