Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1694                                                        |

| Number of Logic Elements/Cells | 33880                                                       |

| Total RAM Bits                 | 1369728                                                     |

| Number of I/O                  | 361                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30cf780c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

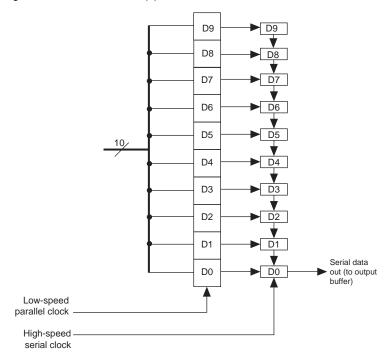

#### Serializer (Parallel-to-Serial Converter)

The serializer converts the parallel 8, 10, 16, or 20-bit data into a serial data bit stream, transmitting the least significant bit (LSB) first. The serialized data stream is then fed to the high-speed differential transmit buffer. Figure 2–7 is a diagram of the serializer.

Figure 2–7. Serializer Note (1)

#### *Note to Figure 2–7:*

(1) This is a 10-bit serializer. The serializer can also convert 8, 16, and 20 bits of data.

#### Transmit Buffer

The Stratix II GX transceiver buffers support the 1.2- and 1.5-V PCML I/O standard at rates up to 6.375 Gbps. The common mode voltage ( $V_{CM}$ ) of the output driver is programmable. The following  $V_{CM}$  values are available when the buffer is in 1.2- and 1.5-V PCML.

- $V_{\rm CM} = 0.6 \, {\rm V}$

- $V_{\rm CM} = 0.7 \, {\rm V}$

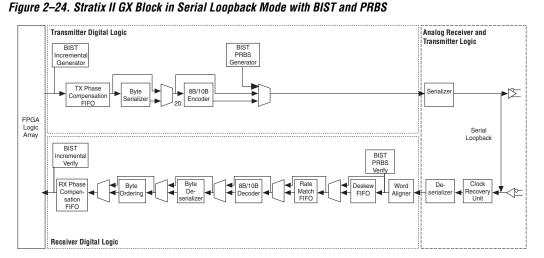

Figure 2–24 shows the data path in serial loopback mode.

Parallel Loopback

The parallel loopback mode exercises the digital logic portion of the transceiver data path. The analog portions are not used in this loopback path, and the received high-speed serial data is not retimed. This protocol is available as one of the sub-protocols under Basic mode and can be used only for Basic double-width mode.

In this loopback mode, the data from the internally available BIST generator is transmitted. The data is looped back after the end of PCS and before the PMA. On the receive side, an internal BIST verifier checks for errors. This loopback enables you to verify the PCS block.

| Transmitter Ph. Transmitter Se Transmitter An. Transmitter An. Transmitter An. Transmitter An. Transmitter An. Transmitter An. BIST Generator Receiver Deske Receiver BA10 Receiver Phase Receiver PLL / Receiver PLL / Receiver PLL / Receiver AUII | Table 2–16. Reset Signal | Transmitter Phase Compensation FIFO Module/ Byte Serializer | Transmitter 8B/10B Encoder | Transmitter Serializer | Transmitter Analog Circuits | Transmitter PLL XX | Transmitter XAUI State Machine | BIST Generators | Receiver Deserializer | Receiver Word Aligner | Receiver Deskew FIFO Module | Receiver Rate Matcher | Receiver 8B/10B Decoder | Receiver Phase Comp FIFO Module/ Byte Deserializer | Receiver PLL / CRU | Receiver XAUI State Machine | ifiers   | Receiver Analog Circuits |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------|----------------------------|------------------------|-----------------------------|--------------------|--------------------------------|-----------------|-----------------------|-----------------------|-----------------------------|-----------------------|-------------------------|----------------------------------------------------|--------------------|-----------------------------|----------|--------------------------|

|                                                                                                                                                                                                                                                      | rx_digitalreset          |                                                             |                            |                        |                             |                    |                                |                 |                       | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           |                    | <b>✓</b>                    | <b>✓</b> |                          |

| In_digitalioned                                                                                                                                                                                                                                      | rx_analogreset           |                                                             |                            |                        |                             |                    |                                |                 | <b>\</b>              |                       |                             |                       |                         |                                                    | <b>✓</b>           |                             |          | <b>✓</b>                 |

|                                                                                                                                                                                                                                                      | tx_digitalreset          | <b>~</b>                                                    | <b>~</b>                   |                        |                             |                    | <b>✓</b>                       | <b>~</b>        |                       |                       |                             |                       |                         |                                                    |                    |                             |          |                          |

| rx_analogreset                                                                                                                                                                                                                                       | gxb_powerdown            | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>           | <b>✓</b>                       | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b> | <b>✓</b>                 |

| rx_analogreset                                                                                                                                                                                                                                       | gxb_enable               | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>           | <b>✓</b>                       | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b> | <b>✓</b>                 |

#### Voltage Reference Capabilities

Stratix II GX transceivers provide voltage reference and bias circuitry. To set up internal bias for controlling the transmitter output driver voltage swings, as well as to provide voltage and current biasing for other analog circuitry, the device uses an internal bandgap voltage reference of 0.7 V. An external 2-K $\Omega$  resistor connected to ground generates a constant bias current (independent of power supply drift, process changes, or temperature variation). An on-chip resistor generates a tracking current that tracks on-chip resistor variation. These currents are mirrored and distributed to the analog circuitry in each channel.

For more information, refer to the *DC and Switching Characteristics* chapter in volume 1 of the *Stratix II GX Handbook*.

# Adaptive Logic Modules

The basic building block of logic in the Stratix II GX architecture is the ALM. The ALM provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.

In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure 2–35 shows a high-level block diagram of the Stratix II GX ALM while Figure 2–36 shows a detailed view of all the connections in the ALM.

carry\_in shared arith in reg\_chain\_in To general or local routing dataf0 To general or adder0 datae0 local routing dataa rea0 datab Combinational Logic datac datad To general or adder1 D local routing datae1 reg1 dataf1 To general or local routing carry\_out

reg\_chain\_out

Figure 2–35. High-Level Block Diagram of the Stratix II GX ALM

shared\_arith\_out

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block, allowing the RAM block to operate in read and write or input and output clock modes. Only the output register can be bypassed. The six labclk signals or local interconnect can drive the inclock, outclock, wren, rden, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, ALMs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–49 shows the M512 RAM block control signal generation logic.

Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local outclocken Interconnect inclocken wren Local outclr inclock outclock rden Interconnect

Figure 2-49. M512 RAM Block Control Signals

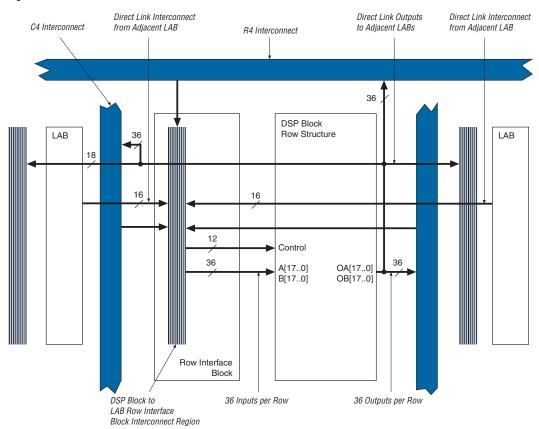

Figure 2-60. DSP Block Interface to Interconnect

A bus of 44 control signals feeds the entire DSP block. These signals include clocks, asynchronous clears, clock enables, signed and unsigned control signals, addition and subtraction control signals, rounding and saturation control signals, and accumulator synchronous loads. The clock signals are routed from LAB row clocks and are generated from specific LAB rows at the DSP block interface. The LAB row source for control signals, data inputs, and outputs is shown in Table 2–23.

Refer to the *DSP Blocks in Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on DSP blocks.

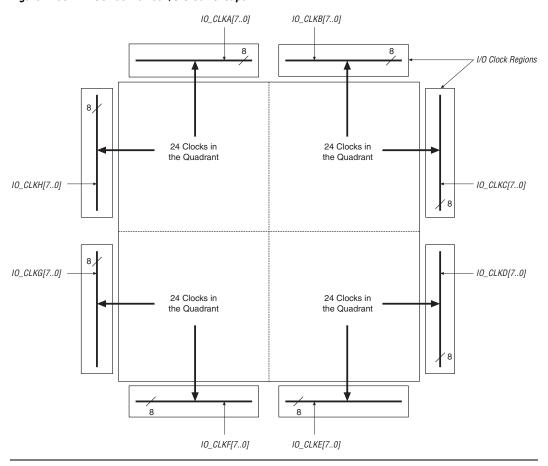

IOE clocks have row and column block regions that are clocked by  $8\,\mathrm{I/O}$  clock signals chosen from the 24 quadrant clock resources. Figures 2–65 and 2–66 show the quadrant relationship to the I/O clock regions.

Figure 2-65. EP2SGX30 Device I/O Clock Groups

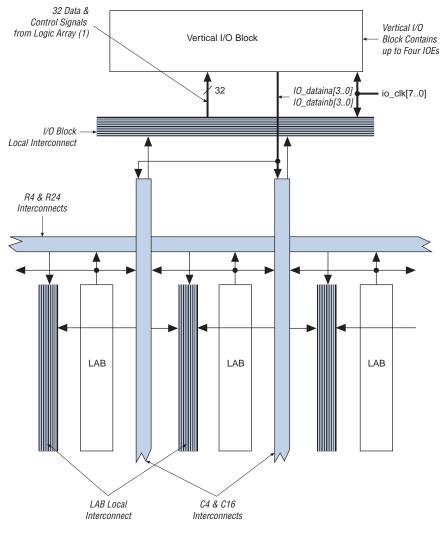

Figure 2–78 shows how a column I/O block connects to the logic array.

#### Figure 2-78. Column I/O Block Connection to the Interconnect

#### Note to Figure 2-78:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io sclr/spreset[3..0].

| Table 2-42. Dod                 | ument Revision History (Part 2 of 6)                                                                                                                |                                                                                                                                                          |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                        | Summary of Changes                                                                                                                                       |

| February 2007<br>v2.0           | Added Chapter 02 "Stratix II GX Transceivers" to the beginning of Chapter 03 "Stratix II GX Architecture".  • Changed chapter number to Chapter 02. | Combined Chapter 02 "Stratix II GX<br>Transceivers" and Chapter 03<br>"Stratix II GX Architecture" in the new<br>Chapter 02 "Stratix II GX Architecture" |

|                                 | Added the "Document Revision History" section to this chapter.                                                                                      |                                                                                                                                                          |

|                                 | Moved the "Stratix II GX Transceiver Clocking" section to after the "Receiver Path" section.                                                        |                                                                                                                                                          |

| Table 2-42. Docu                                        | ment Revision History (Part 5 of 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Date and<br>Document<br>Version                         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes                                                                  |

| Previous Chapter<br>02 changes:<br>June 2006, v1.2      | <ul> <li>Updated notes 1 and 2 in Figure 2–1.</li> <li>Updated "Byte Serializer" section.</li> <li>Updated Tables 2–4, 2–7, and 2–16.</li> <li>Updated "Programmable Output Driver" section.</li> <li>Updated Figure 2–12.</li> <li>Updated "Programmable Pre-Emphasis" section.</li> <li>Added Table 2–11.</li> <li>Added "Dynamic Reconfiguration" section.</li> <li>Added "Calibration Block" section.</li> <li>Updated "Programmable Equalizer" section, including addition of Figure 2–18.</li> </ul> | Updated input frequency range in Table 2–4.                                         |

| Previous Chapter<br>02 changes:<br>April 2006, v1.1     | <ul> <li>Updated Figure 2–3.</li> <li>Updated Figure 2–7.</li> <li>Updated Table 2–4.</li> <li>Updated "Transmit Buffer" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                               | Updated input frequency range in Table 2–4.                                         |

| Previous Chapter<br>02 changes:<br>October 2005<br>v1.0 | Added chapter to the Stratix II GX Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                     |

| Previous Chapter<br>03 changes:<br>August 2006, v1.4    | Updated Table 3–18 with note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |

| Previous Chapter<br>03 changes:<br>June 2006, v1.3      | <ul> <li>Updated note 2 in Figure 3–41.</li> <li>Updated column title in Table 3–21.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |

| Previous Chapter<br>03 changes:<br>April 2006, v1.2     | <ul> <li>Updated note 1 in Table 3–9.</li> <li>Updated note 1 in Figure 3–40.</li> <li>Updated note 2 in Figure 3–41.</li> <li>Updated Table 3–16.</li> <li>Updated Figure 3–56.</li> <li>Updated Tables 3–19 through 3–22.</li> <li>Updated Tables 3–25 and 3–26.</li> <li>Updated "Fast PLL &amp; Channel Layout" section.</li> </ul>                                                                                                                                                                    | Added 1,152-pin FineLine BGA package information for EP2SGX60 device in Table 3–16. |

considerable flexibility for frequency synthesis, allowing real-time variation of the PLL frequency and delay. The rest of the device is functional while reconfiguring the PLL.

See the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on Stratix II GX PLLs.

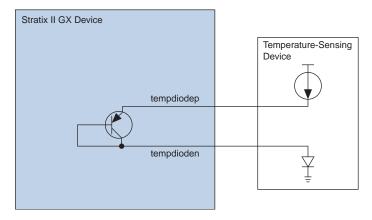

### Temperature Sensing Diode (TSD)

Stratix II GX devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device. These devices steer bias current through the Stratix II GX diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus 1 sign bit). The external device's output represents the junction temperature of the Stratix II GX device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix II GX device to connect to the external temperature-sensing device, as shown in Figure 3–1. The temperature sensing diode is a passive element and therefore can be used before the Stratix II GX device is powered.

Figure 3-1. External Temperature-Sensing Diode

# 4. DC and Switching Characteristics

SIIGX51006-4.6

## Operating Conditions

Stratix<sup>®</sup> II GX devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grade and commercial devices are offered in -3 (fastest), -4, and -5 speed grades.

Tables 4–1 through 4–51 provide information on absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II GX devices.

#### **Absolute Maximum Ratings**

Table 4–1 contains the absolute maximum ratings for the Stratix II GX device family.

| Table 4–1          | . Stratix II GX Device Absolut | te Maximum Ratings Notes | (1), (2),(3) |         |      |

|--------------------|--------------------------------|--------------------------|--------------|---------|------|

| Symbol             | Parameter                      | Conditions               | Minimum      | Maximum | Unit |

| V <sub>CCINT</sub> | Supply voltage                 | With respect to ground   | -0.5         | 1.8     | V    |

| V <sub>CCIO</sub>  | Supply voltage                 | With respect to ground   | -0.5         | 4.6     | V    |

| V <sub>CCPD</sub>  | Supply voltage                 | With respect to ground   | -0.5         | 4.6     | V    |

| VI                 | DC input voltage (4)           |                          | -0.5         | 4.6     | V    |

| I <sub>OUT</sub>   | DC output current, per pin     |                          | -25          | 40      | mA   |

| T <sub>STG</sub>   | Storage temperature            | No bias                  | -65          | 150     | С    |

| T <sub>J</sub>     | Junction temperature           | BGA packages under bias  | <b>-</b> 55  | 125     | С    |

#### Notes to Table 4-1:

- (1) See the Operating Requirements for Altera Devices Data Sheet for more information.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (4) During transitions, the inputs may overshoot to the voltage shown in Table 4–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Table 4–6. Stra                          | atix II GX Transe                                                                                                               | ceiver Blo     | ck AC S                 | pecificati                          | ion (Part                                                        | 5 of 6)                       |                              |            |                    |                |      |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------|-------------------------------------|------------------------------------------------------------------|-------------------------------|------------------------------|------------|--------------------|----------------|------|

| Symbol /<br>Description                  | Conditions                                                                                                                      | -3 Spee<br>Spe | d Comn<br>eed Gra       |                                     | -4 Spee<br>and Ind                                               |                               |                              |            | ed Com<br>peed Gra | mercial<br>ade | Unit |

| •                                        |                                                                                                                                 | Min            | Тур                     | Max                                 | Min                                                              | Тур                           | Max                          | Min        | Тур                | Max            |      |

| Data rate                                |                                                                                                                                 | 600            | -                       | 6375                                | 600                                                              | -                             | 5000                         | 600        | -                  | 4250           | Mbps |

| V <sub>OCM</sub>                         | V <sub>OCM</sub> = 0.6 V<br>setting                                                                                             | 5              | 80±10%                  |                                     | 5                                                                | 80±10%                        | 580±10%                      |            | %                  | mV             |      |

|                                          | V <sub>OCM</sub> = 0.7 V<br>setting                                                                                             | 6              | 80±10%                  | •                                   | 6                                                                | 80±10%                        | ,                            |            | 680±10°            | %              | mV   |

| On-chip                                  | 100 Ω setting                                                                                                                   | 1              | 08±10%                  | •                                   | 1                                                                | 08±10%                        | ,<br>o                       |            | 108±10°            | %              | Ω    |

| termination resistors                    | 120 Ω setting                                                                                                                   | 1:             | 25±10%                  | •                                   | 1                                                                | 25±10%                        | ,<br>o                       |            | 125±10°            | %              | Ω    |

|                                          | 150 Ω setting                                                                                                                   | 1:             | 52±10%                  | )                                   | 1                                                                | 52±10%                        | 0                            |            | 152±10°            | %              | Ω    |

| Return loss<br>differential<br>mode      |                                                                                                                                 |                | MHz to<br>50 N<br>100 N | 3.125 GH<br>MHz to 1.<br>MHz to 4.8 | 625 MHz ()<br>Hz (XAUI):<br>25 GHz (P<br>875 GHz (<br>(OIF/CEI): | -10 dB/<br>CI-E): -<br>OIF/CE | decade s<br>10dB<br>I): -8db | ·          |                    |                |      |

| Return loss common mode                  | 50 MHz to 1.25 GHz (PCI-E): -6dB<br>100 MHz to 4.875 GHz (OIF/CEI): -6db<br>4.875 GHz to 10 GHz (OIF/CEI): 16.6 dB/decade slope |                |                         |                                     |                                                                  |                               |                              |            |                    |                |      |

| Rise time                                |                                                                                                                                 | 35             | -                       | 65                                  | 35                                                               | -                             | 65                           | 35         | -                  | 65             | ps   |

| Fall time                                |                                                                                                                                 | 35             | -                       | 65                                  | 35                                                               | -                             | 65                           | 35         | -                  | 65             | ps   |

| Intra<br>differential pair<br>skew       | V <sub>OD</sub> = 800 mV                                                                                                        | -              | -                       | 15                                  | -                                                                | -                             | 15                           | -          | -                  | 15             | ps   |

| Intra-<br>transceiver<br>block skew (x4) |                                                                                                                                 | -              | -                       | 100                                 | -                                                                | -                             | 100                          | -          | -                  | 100            | ps   |

| Inter-<br>transceiver<br>block skew (x8) |                                                                                                                                 | -              | -                       | 300                                 | -                                                                | -                             | 300                          | -          | -                  | 300            | ps   |

| TXPLL (TXPLL                             | 0 and TXPLL1)                                                                                                                   |                |                         |                                     |                                                                  | ,                             |                              |            | ,                  | •              |      |

| VCO<br>frequency<br>range (low<br>gear)  |                                                                                                                                 | 500            | -                       | 1562.5                              | 500                                                              | -                             | 1562.5                       | 500        | -                  | 1562.5         | MHz  |

| VCO<br>frequency<br>range (high<br>gear) |                                                                                                                                 | 1562.5         |                         | 3187.5                              | 1562.5                                                           |                               | 2500                         | 1562.<br>5 | -                  | 2125           | MHz  |

| Symbol/<br>Description       | Conditions                                                                                                                   |                  | -3 Speo<br>nercial<br>Grade | Speed | Com | -4 Spec<br>imercia<br>istrial S<br>Grade | al and<br>Speed |        | -5 Spe<br>mercia<br>Grad | l Speed | Unit |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------|-------|-----|------------------------------------------|-----------------|--------|--------------------------|---------|------|

|                              |                                                                                                                              | Min              | Тур                         | Max   | Min | Тур                                      | Max             | Min    | Тур                      | Max     |      |

| Fibre Channel Tra            | nsmit Jitter Generat                                                                                                         | ion <i>(8)</i> , | (17)                        |       |     |                                          |                 |        |                          |         |      |

| Total jitter FC-1            | $\begin{tabular}{ll} REFCLK = \\ 106.25 \ MHz \\ Pattern = CRPAT \\ V_{OD} = 800 \ mV \\ No \ Pre-emphasis \\ \end{tabular}$ | -                | -                           | 0.23  | 1   | -                                        | 0.23            | -      | -                        | 0.23    | UI   |

| Deterministic jitter<br>FC-1 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis                                     | -                | -                           | 0.11  | -   | -                                        | 0.11            | -      | -                        | 0.11    | UI   |

| Total jitter FC-2            | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis                                     | -                | -                           | 0.33  | -   | -                                        | 0.33            | -      | -                        | 0.33    | UI   |

| Deterministic jitter<br>FC-2 | REFCLK =<br>106.25 MHz<br>Pattern = CRPAT<br>V <sub>OD</sub> = 800 mV<br>No Pre-emphasis                                     | -                | -                           | 0.2   | -   | -                                        | 0.2             | -      | -                        | 0.2     | UI   |

| Total jitter FC-4            | REFCLK = 106.25 MHz Pattern = CRPAT V <sub>OD</sub> = 800 mV No Pre-emphasis                                                 | -                | -                           | 0.52  | -   | -                                        | 0.52            | -      | -                        | 0.52    | UI   |

| Deterministic jitter<br>FC-4 | REFCLK = 106.25 MHz Pattern = CRPAT V <sub>OD</sub> = 800 mV No Pre-emphasis                                                 | -                | -                           | 0.33  | -   | -                                        | 0.33            | -      | -                        | 0.33    | UI   |

| Fibre Channel Red            | ceiver Jitter Tolerand                                                                                                       | ce (8), (        | 18)                         |       |     |                                          |                 |        |                          |         |      |

| Deterministic jitter<br>FC-1 | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                                                        |                  | > 0.37                      | 7     |     | > 0.37                                   | 7               | > 0.37 |                          |         | UI   |

| Random jitter FC-1           | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                                                        |                  | > 0.31                      | l     |     | > 0.31                                   | l               | > 0.31 |                          |         | UI   |

Table 4–55 shows the Stratix II GX performance for some common designs. All performance values were obtained with the Quartus II software compilation of LPM or MegaCore functions for FIR and FFT designs.

| Table 4-55                       | 5. Stratix II GX Pe                     | rformance | Notes (Pa                     | rt 1 of 3)    | Note (1                  | )                           |                   |                      |       |

|----------------------------------|-----------------------------------------|-----------|-------------------------------|---------------|--------------------------|-----------------------------|-------------------|----------------------|-------|

|                                  |                                         | Re        | sources Us                    | ed            |                          | Pe                          | rformance         |                      |       |

| Applications                     |                                         | ALUTs     | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3 Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4 Speed<br>Grade | -5<br>Speed<br>Grade | Units |

| LE                               | 16-to-1<br>multiplexer (4)              | 21        | 0                             | 0             | 657.03                   | 620.73                      | 589.62            | 477.09               | MHz   |

|                                  | 32-to-1<br>multiplexer (4)              | 38        | 0                             | 0             | 534.75                   | 517.33                      | 472.81            | 369.27               | MHz   |

|                                  | 16-bit counter                          | 16        | 0                             | 0             | 568.18                   | 539.66                      | 507.61            | 422.47               | MHz   |

|                                  | 64-bit counter                          | 64        | 0                             | 0             | 242.54                   | 231.0                       | 217.77            | 180.31               | MHz   |

| TriMatrix<br>Memory<br>M512      | Simple<br>dual-port RAM<br>32 x 18bit   | 0         | 1                             | 0             | 500.0                    | 476.19                      | 447.22            | 373.13               | MHz   |

| block                            | FIFO 32 x 18 bit                        | 22        | 1                             | 0             | 500.00                   | 476.19                      | 460.82            | 373.13               | MHz   |

| TriMatrix<br>Memory<br>M4K block | Simple dual-<br>port RAM 128 x<br>36bit | 0         | 1                             | 0             | 540.54                   | 515.46                      | 483.09            | 401.6                | MHz   |

|                                  | True dual-port<br>RAM 128 x 18bit       | 0         | 1                             | 0             | 540.54                   | 515.46                      | 483.09            | 401.6                | MHz   |

|                                  | FIFO 128 x 36<br>bit                    | 22        | 1                             | 0             | 524.10                   | 500.25                      | 466.41            | 381.38               | MHz   |

To calculate the output toggle rate for a non 0 pF load, use this formula:

The toggle rate for a non 0 pF load

= 1,000 / (1,000 / toggle rate at 0 pF load + derating factor  $\times$  load value in pF /1,000)

For example, the output toggle rate at 0 pF load for SSTL-18 Class II 20 mA I/O standard is 550 MHz on a -3 device clock output pin. The derating factor is 94 ps/pF. For a 10 pF load the toggle rate is calculated as:

$$1,000 / (1,000/550 + 94 \times 10 / 1,000) = 363 (MHz)$$

Table 4–88 shows the maximum input clock toggle rates for Stratix II GX device column pins.

| Table 4–88. Stratix I           | II GX Maximum Input | Clock Rate for Columi | n I/O Pins (Part 1 of 2 | )    |

|---------------------------------|---------------------|-----------------------|-------------------------|------|

| I/O Standard                    | -3 Speed Grade      | -4 Speed Grade        | -5 Speed Grade          | Unit |

| LVTTL                           | 500                 | 500                   | 450                     | MHz  |

| 2.5 V                           | 500                 | 500                   | 450                     | MHz  |

| 1.8 V                           | 500                 | 500                   | 450                     | MHz  |

| 1.5 V                           | 500                 | 500                   | 450                     | MHz  |

| LVCMOS                          | 500                 | 500                   | 450                     | MHz  |

| SSTL-2 Class I                  | 500                 | 500                   | 500                     | MHz  |

| SSTL-2 Class II                 | 500                 | 500                   | 500                     | MHz  |

| SSTL-18 Class I                 | 500                 | 500                   | 500                     | MHz  |

| SSTL-18 Class I I               | 500                 | 500                   | 500                     | MHz  |

| 1.5-V HSTL Class I              | 500                 | 500                   | 500                     | MHz  |

| 1.5-V HSTL Class I I            | 500                 | 500                   | 500                     | MHz  |

| 1.8-V HSTL Class I              | 500                 | 500                   | 500                     | MHz  |

| 1.8-V HSTL Class II             | 500                 | 500                   | 500                     | MHz  |

| PCI                             | 500                 | 500                   | 450                     | MHz  |

| PCI-X                           | 500                 | 500                   | 450                     | MHz  |

| Differential SSTL-2<br>Class I  | 500                 | 500                   | 500                     | MHz  |

| Differential SSTL-2<br>Class II | 500                 | 500                   | 500                     | MHz  |

| Differential SSTL-18<br>Class I | 500                 | 500                   | 500                     | MHz  |

| Table 4–89. Stratix I                | I GX Maximum Input | Clock Rate for Row I/C | O Pins (Part 2 of 2) |      |

|--------------------------------------|--------------------|------------------------|----------------------|------|

| I/O Standard                         | -3 Speed Grade     | -4 Speed Grade         | -5 Speed Grade       | Unit |

| Differential SSTL-2<br>Class II      | 500                | 500                    | 500                  | MHz  |

| Differential SSTL-18<br>Class I      | 500                | 500                    | 500                  | MHz  |

| Differential SSTL-18<br>Class I I    | 500                | 500                    | 500                  | MHz  |

| 1.8-V differential<br>HSTL Class I   | 500                | 500                    | 500                  | MHz  |

| 1.8-V differential<br>HSTL Class I I | 500                | 500                    | 500                  | MHz  |

| 1.5-V differential<br>HSTL Class I   | 500                | 500                    | 500                  | MHz  |

| 1.5-V differential<br>HSTL Class II  | 500                | 500                    | 500                  | MHz  |

| LVDS (1)                             | 520                | 520                    | 420                  | MHz  |

| HyperTransport                       | 520                | 520                    | 420                  | MHz  |

<sup>(1)</sup> The parameters are only available on the left side of the device.

Table 4–90 shows the maximum input clock toggle rates for Stratix II GX device dedicated clock pins.

| Table 4–90. Stratix I | I GX Maximum Input | Clock Rate for Dedica | ted Clock Pins (Part 1 | of 2) |

|-----------------------|--------------------|-----------------------|------------------------|-------|

| I/O Standard          | -3 Speed Grade     | -4 Speed Grade        | -5 Speed Grade         | Unit  |

| LVTTL                 | 500                | 500                   | 400                    | MHz   |

| 2.5 V                 | 500                | 500                   | 400                    | MHz   |

| 1.8 V                 | 500                | 500                   | 400                    | MHz   |

| 1.5 V                 | 500                | 500                   | 400                    | MHz   |

| LVCMOS                | 500                | 500                   | 400                    | MHz   |

| SSTL-2 Class I        | 500                | 500                   | 500                    | MHz   |

| SSTL-2 Class II       | 500                | 500                   | 500                    | MHz   |

| SSTL-18 Class I       | 500                | 500                   | 500                    | MHz   |

| SSTL-18 Class II      | 500                | 500                   | 500                    | MHz   |

| 1.5-V HSTL Class I    | 500                | 500                   | 500                    | MHz   |

| 1.5-V HSTL Class II   | 500                | 500                   | 500                    | MHz   |

| 1.8-V HSTL CLass I    | 500                | 500                   | 500                    | MHz   |

Table 4–96. Stratix II GX Maximum Output Clock Rate for Dedicated Clock Pins (Series Termination) (Part 2 of 2)

| I/O Standard                        | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|-------------------------------------|----------------|----------------|----------------|----------------|------|

| SSTL-18 Class II                    | OCT_25_OHMS    | 550            | 500            | 450            | MHz  |

| 1.5-V HSTL<br>Class I               | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |

| 1.8-V HSTL<br>Class I               | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |

| 1.8-V HSTL<br>Class II              | OCT_25_OHMS    | 500            | 500            | 450            | MHz  |

| DIfferential<br>SSTL-2 Class I      | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |

| DIfferential<br>SSTL-2 Class II     | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |

| DIfferential<br>SSTL-18 Class I     | OCT_50_OHMS    | 560            | 400            | 350            | MHz  |

| DIfferential<br>SSTL-18 Class II    | OCT_25_OHMS    | 550            | 500            | 450            | MHz  |

| 1.8-V differential<br>HSTL Class I  | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |

| 1.8-V differential<br>HSTL Class II | OCT_25_OHMS    | 500            | 500            | 450            | MHz  |

| 1.5-V differential<br>HSTL Class I  | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |

Table 4–97 specifies the derating factors for the output clock toggle rate for a non 0 pF load.

| Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 1 of 5) |                   |                                                           |     |     |              |     |     |                            |     |     |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|--------------|-----|-----|----------------------------|-----|-----|

|                                                                             | Drive<br>Strength | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |              |     |     |                            |     |     |

| I/O Standard                                                                |                   | Column I/O Pins                                           |     |     | Row I/O Pins |     |     | Dedicated Clock<br>Outputs |     |     |

|                                                                             |                   | -3                                                        | -4  | -5  | -3           | -4  | -5  | -3                         | -4  | -5  |

| 3.3-V LVTTL                                                                 | 4 mA              | 478                                                       | 510 | 510 | 478          | 510 | 510 | 466                        | 510 | 510 |

|                                                                             | 8 mA              | 260                                                       | 333 | 333 | 260          | 333 | 333 | 291                        | 333 | 333 |

|                                                                             | 12 mA             | 213                                                       | 247 | 247 | 213          | 247 | 247 | 211                        | 247 | 247 |

|                                                                             | 16 mA             | 136                                                       | 197 | 197 | -            | -   | -   | 166                        | 197 | 197 |

|                                                                             | 20 mA             | 138                                                       | 187 | 187 | -            | -   | -   | 154                        | 187 | 187 |

|                                                                             | 24 mA             | 134                                                       | 177 | 177 | -            | -   | -   | 143                        | 177 | 177 |

| Table 4–112. DLL Frequency Range Specifications (Part 2 of 2) |                                    |                         |  |  |

|---------------------------------------------------------------|------------------------------------|-------------------------|--|--|

| Frequency Mode                                                | Frequency Range (MHz)              | Resolution<br>(Degrees) |  |  |

| 3                                                             | 240 to 400 (-3 speed grade)        | 36                      |  |  |

| 3                                                             | 240 to 350 (-4 and -5 speed grade) | 36                      |  |  |

| Table 4–113. DQS Jitter Specifications for DLL-Delayed Clock ( $t_{DQS-JITTER}$ ) Note (1) |                 |                 |  |  |  |

|--------------------------------------------------------------------------------------------|-----------------|-----------------|--|--|--|

| Number of DQS Delay Buffer Stages (2)                                                      | Commercial (ps) | Industrial (ps) |  |  |  |

| 1                                                                                          | 80              | 110             |  |  |  |

| 2                                                                                          | 110             | 130             |  |  |  |

| 3                                                                                          | 130             | 180             |  |  |  |

| 4                                                                                          | 160             | 210             |  |  |  |

- Peak-to-peak period jitter on the phase-shifted DQS clock. For example, jitter on two delay stages under commercial conditions is 200 ps peak-to-peak or 100 ps.

- (2) Delay stages used for requested DQS phase shift are reported in a project's Compilation Report in the Quartus II software.

| Table 4–114. DQS Phase-Shift Error Specifications for DLL-Delayed Clock (t <sub>DQS_PSERR</sub> ) |                     |                     |                     |  |  |  |

|---------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|--|--|--|

| Number of DQS Delay Buffer Stages (1)                                                             | -3 Speed Grade (ps) | -4 Speed Grade (ps) | -5 Speed Grade (ps) |  |  |  |

| 1                                                                                                 | 25                  | 30                  | 35                  |  |  |  |

| 2                                                                                                 | 50                  | 60                  | 70                  |  |  |  |

| 3                                                                                                 | 75                  | 90                  | 105                 |  |  |  |

| 4                                                                                                 | 100                 | 120                 | 140                 |  |  |  |

(1) Delay stages used for request DQS phase shift are reported in a project's Compilation Report in the Quartus II software. For example, phase-shift error on two delay stages under -3 conditions is 50 ps peak-to-peak or 25 ps.