Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1694                                                        |

| Number of Logic Elements/Cells | 33880                                                       |

| Total RAM Bits                 | 1369728                                                     |

| Number of I/O                  | 361                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30df780c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Pre-emphasis percentage is defined as  $(V_{MAX}/V_{MIN}-1) \times 100$ , where  $V_{MAX}$  is the differential emphasized voltage (peak-to-peak) and  $V_{MIN}$  is the differential steady-state voltage (peak-to-peak).

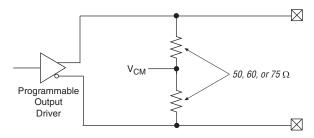

#### **Programmable Termination**

The programmable termination can be statically set in the Quartus II software. The values are  $100~\Omega$ ,  $120~\Omega$ ,  $150~\Omega$ , and external termination. Figure 2–11 shows the setup for programmable termination.

Figure 2-11. Programmable Transmitter Terminations

#### **PCI Express Receiver Detect**

The Stratix II GX transmitter buffer has a built-in receiver detection circuit for use in PIPE mode. This circuit provides the ability to detect if there is a receiver downstream by sending out a pulse on the channel and monitoring the reflection. This mode requires the transmitter buffer to be tri-stated (in electrical idle mode).

#### PCI Express Electric Idles (or Individual Transmitter Tri-State)

The Stratix II GX transmitter buffer supports PCI Express electrical idles. This feature is only active in PIPE mode. The tx\_forceelecidle port puts the transmitter buffer in electrical idle mode. This port is available in all PCI Express power-down modes and has specific usage in each mode.

#### **Receiver Path**

This section describes the data path through the Stratix II GX receiver. The Stratix II GX receiver consists of the following blocks:

- Receiver differential input buffer

- Receiver PLL lock detector, signal detector, and run length checker

- Clock/data recovery (CRU) unit

- Deserializer

- Pattern detector

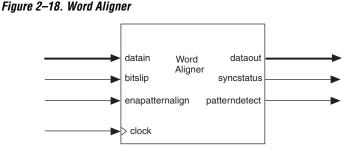

- Word aligner

This module detects word boundaries for the 8B/10B-based protocols, SONET, 16-bit, and 20-bit proprietary protocols. This module is also used to align to specific programmable patterns in PRBS7/23 test mode.

#### **Pattern Detection**

The programmable pattern detection logic can be programmed to align word boundaries using a single 7-, 8-, 10-, 16-, 20, or 32-bit pattern. The pattern detector can either do an exact match, or match the exact pattern and the complement of a given pattern. Once the programmed pattern is found, the data stream is aligned to have the pattern on the LSB portion of the data output bus.

XAUI, GIGE, PCI Express, and Serial RapidIO standards have embedded state machines for symbol boundary synchronization. These standards use K28.5 as their 10-bit programmed comma pattern. Each of these standards uses different algorithms before signaling symbol boundary acquisition to the FPGA.

The pattern detection logic searches from the LSB to the most significant bit (MSB). If multiple patterns are found within the search window, the pattern in the lower portion of the data stream (corresponding to the pattern received earlier) is aligned and the rest of the matching patterns are ignored.

Once a pattern is detected and the data bus is aligned, the word boundary is locked. The two detection status signals (rx\_syncstatus and rx patterndetect) indicate that an alignment is complete.

Figure 2–18 is a block diagram of the word aligner.

Altera Corporation October 2007

The dynamic reconfiguration block can dynamically reconfigure the following PMA settings:

- Pre-emphasis settings

- Equalizer and DC gain settings

- Voltage Output Differential (V<sub>OD</sub>) settings

The channel reconfiguration allows you to dynamically modify the data rate, local dividers, and the functional mode of the transceiver channel.

Refer to the *Stratix II GX Device Handbook*, volume 2, for more information.

The dynamic reconfiguration block requires an input clock between 2.5 MHz and 50 MHz. The clock for the dynamic reconfiguration block is derived from a high-speed clock and divided down using a counter.

#### Individual Power Down and Reset for the Transmitter and Receiver

Stratix II GX transceivers offer a power saving advantage with their ability to shut off functions that are not needed. The device can individually reset the receiver and transmitter blocks and the PLLs. The Stratix II GX device can either globally or individually power down and reset the transceiver. Table  $2{\text -}16$  shows the connectivity between the reset signals and the Stratix II GX transceiver blocks. These reset signals can be controlled from the FPGA or pins.

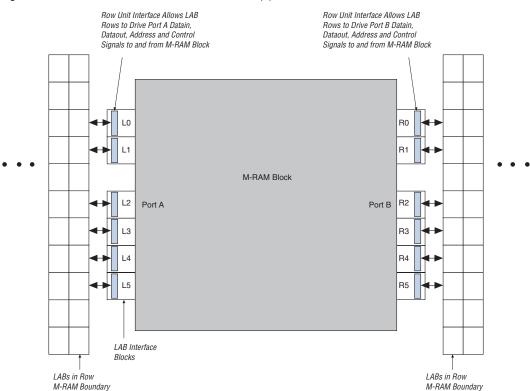

Figure 2–55. M-RAM Block LAB Row Interface Note (1)

*Note to Figure 2–55:*

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

| Table 2-23.             | DSP Block Signal Sources and D                                                                | estinations          |                    |

|-------------------------|-----------------------------------------------------------------------------------------------|----------------------|--------------------|

| LAB Row at<br>Interface | Control Signals Generated                                                                     | Data Inputs          | Data Outputs       |

| 0                       | clock0 aclr0 ena0 mult01_saturate addnsub1_round/ accum_round addnsub1 signa sourcea sourceb  | A1 [170]<br>B1 [170] | OA[170]<br>OB[170] |

| 1                       | clock1 aclr1 enal accum_saturate mult01_round accum_sload sourcea sourceb mode0               | A2 [170]<br>B2 [170] | OC[170]<br>OD[170] |

| 2                       | clock2 aclr2 ena2 mult23_saturate addnsub3_round/ accum_round addnsub3 sign_b sourcea sourceb | A3 [170]<br>B3 [170] | OE[170]<br>OF[170] |

| 3                       | clock3 aclr3 ena3 accum_saturate mult23_round accum_sload sourcea sourceb mode1               | A4 [170]<br>B4 [170] | OG[170]<br>OH[170] |

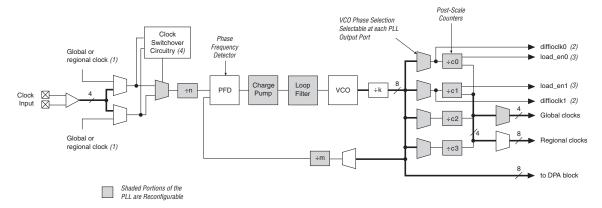

Figure 2-75. Stratix II GX Device Fast PLL

#### Notes to Figure 2-75:

- (1) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the serializer/deserializer (SERDES) circuitry. Stratix II GX devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a differential I/O SERDES control signal.

- (4) Stratix II GX fast PLLs only support manual clock switchover.

Refer to the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on enhanced and fast PLLs. Refer to "High-Speed Differential I/O with DPA Support" on page 2–136 for more information on high-speed differential I/O support.

# I/O Structure

The Stratix II GX IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- On-chip driver series termination

- On-chip termination for differential standards

- Programmable pull-up during configuration

- Output drive strength control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

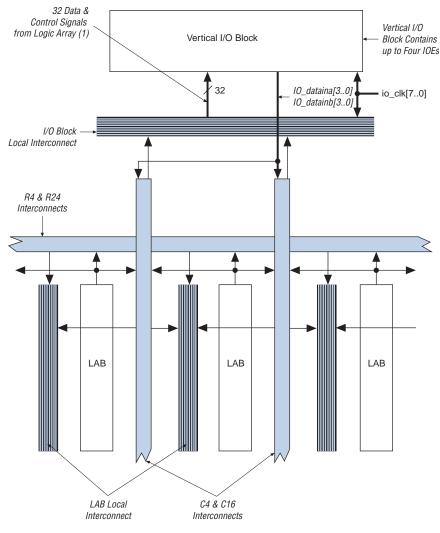

Figure 2–78 shows how a column I/O block connects to the logic array.

## Figure 2-78. Column I/O Block Connection to the Interconnect

#### Note to Figure 2-78:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io sclr/spreset[3..0].

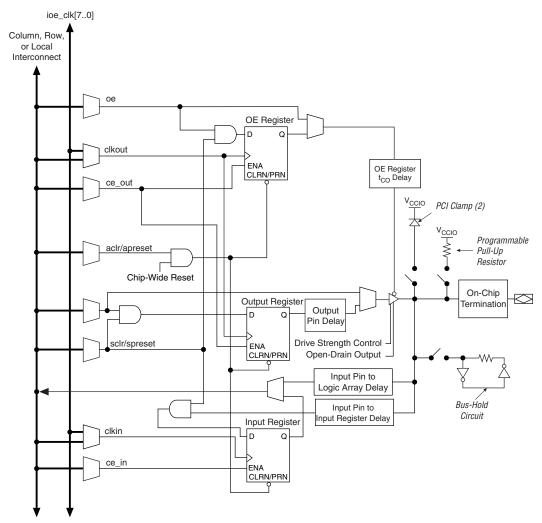

Figure 2–81. Stratix II GX IOE in Bidirectional I/O Configuration Note (1)

Notes to Figure 2-81:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

The Stratix II GX device IOE includes programmable delays that can be activated to ensure input IOE register-to-logic array register transfers, input pin-to-logic array register transfers, or output IOE register-to-pin transfers.

### On-Chip Parallel Termination with Calibration

Stratix II GX devices support on-chip parallel termination with calibration for column I/O pins only. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip parallel termination calibration circuit compares the total impedance of each I/O buffer to the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip parallel termination with calibration is only supported for input pins.

For more information about on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

## MultiVolt I/O Interface

The Stratix II GX architecture supports the MultiVolt I/O interface feature that allows Stratix II GX devices in all packages to interface with systems of different supply voltages. The Stratix II GX VCCINT pins must always be connected to a 1.2-V power supply. With a 1.2-V V<sub>CCINT</sub> level, input pins are 1.2-, 1.5-, 1.8-, 2.5-, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.2-, 1.5-, 1.8-, 2.5-, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). The Stratix II GX VCCPD power pins must be connected to a 3.3-V power supply. These power pins are used to supply the pre-driver power to the output buffers, which increases the performance of the output pins. The VCCPD pins also power configuration input pins and JTAG input pins.

| Table 4–6. Stra                          | atix II GX Transe                   | ceiver Blo     | ck AC S                 | pecificati                          | ion (Part                                                        | 5 of 6)                       |                              |            |                    |                |      |  |  |

|------------------------------------------|-------------------------------------|----------------|-------------------------|-------------------------------------|------------------------------------------------------------------|-------------------------------|------------------------------|------------|--------------------|----------------|------|--|--|

| Symbol /<br>Description                  | Conditions                          | -3 Spee<br>Spe | d Comn<br>eed Gra       |                                     | -4 Spee<br>and Ind                                               |                               |                              |            | ed Com<br>peed Gra | mercial<br>ade | Unit |  |  |

| •                                        |                                     | Min            | Тур                     | Max                                 | Min                                                              | Тур                           | Max                          | Min        | Тур                | Max            |      |  |  |

| Data rate                                |                                     | 600            | -                       | 6375                                | 600                                                              | -                             | 5000                         | 600        | -                  | 4250           | Mbps |  |  |

| V <sub>OCM</sub>                         | V <sub>OCM</sub> = 0.6 V<br>setting | 5              | 80±10%                  |                                     | 5                                                                | 80±10%                        | 0                            |            | 580±10°            | %              | mV   |  |  |

|                                          | V <sub>OCM</sub> = 0.7 V<br>setting | 6              | 80±10%                  |                                     | 6                                                                | 80±10%                        | ,                            |            | 680±10°            | %              | mV   |  |  |

| On-chip                                  | 100 Ω setting                       | 1              | 08±10%                  | •                                   | 1                                                                | 08±10%                        | ,<br>o                       |            | 108±10°            | %              | Ω    |  |  |

| termination resistors                    | 120 Ω setting                       | 1:             | 25±10%                  | •                                   | 1                                                                | 25±10%                        | ,<br>o                       |            | 125±10°            | Ω              |      |  |  |

|                                          | 150 Ω setting                       | 1:             | 52±10%                  | )                                   | 1                                                                | 52±10%                        | 0                            |            | 152±10°            | Ω              |      |  |  |

| Return loss<br>differential<br>mode      |                                     |                | MHz to<br>50 N<br>100 N | 3.125 GH<br>MHz to 1.<br>MHz to 4.8 | 625 MHz ()<br>Hz (XAUI):<br>25 GHz (P<br>875 GHz (<br>(OIF/CEI): | -10 dB/<br>CI-E): -<br>OIF/CE | decade s<br>10dB<br>I): -8db | ·          |                    |                |      |  |  |

| Return loss common mode                  |                                     | 4.875          | 100 N                   | /IHz to 4.8                         | .25 GHz (F<br>875 GHz (<br>(OIF/CEI):                            | OIF/CE                        | l): -6db                     | slope      | •                  |                |      |  |  |

| Rise time                                |                                     | 35             | -                       | 65                                  | 35                                                               | -                             | 65                           | 35         | -                  | 65             | ps   |  |  |

| Fall time                                |                                     | 35             | -                       | 65                                  | 35                                                               | -                             | 65                           | 35         | -                  | 65             | ps   |  |  |

| Intra<br>differential pair<br>skew       | V <sub>OD</sub> = 800 mV            | -              | -                       | 15                                  | -                                                                | -                             | 15                           | -          | -                  | 15             | ps   |  |  |

| Intra-<br>transceiver<br>block skew (x4) |                                     | -              | -                       | 100                                 | -                                                                | -                             | 100                          | -          | -                  | 100            | ps   |  |  |

| Inter-<br>transceiver<br>block skew (x8) |                                     | -              | -                       | 300                                 | -                                                                | -                             | 300                          | -          | -                  | 300            | ps   |  |  |

| TXPLL (TXPLL                             | 0 and TXPLL1)                       |                |                         |                                     |                                                                  | ,                             |                              |            |                    |                |      |  |  |

| VCO<br>frequency<br>range (low<br>gear)  |                                     | 500            | -                       | 1562.5                              | 500                                                              | -                             | 1562.5                       | 500        | -                  | 1562.5         | MHz  |  |  |

| VCO<br>frequency<br>range (high<br>gear) |                                     | 1562.5         |                         | 3187.5                              | 1562.5                                                           |                               | 2500                         | 1562.<br>5 | -                  | 2125           | MHz  |  |  |

| Table 4–19. Strat                                | ix II GX Transceiver Bl                                                                                                                                                                                     | ock AC | Specif                     | ication | Notes ( | 1), (2),                              | (3) <b>(P</b>  | art 7 o | f 19)                      |       |      |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------|---------|---------|---------------------------------------|----------------|---------|----------------------------|-------|------|

| Symbol/<br>Description                           | Conditions                                                                                                                                                                                                  |        | 3 Spee<br>nercial<br>Grade | Speed   | Com     | 4 Spee<br>mercia<br>strial S<br>Grade | l and<br>Speed |         | -5 Spe<br>nercial<br>Grade | Speed | Unit |

|                                                  |                                                                                                                                                                                                             | Min    | Тур                        | Max     | Min     | Тур                                   | Max            | Min     | Тур                        | Max   |      |

|                                                  | Jitter Frequency = 22.1 KHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps  |        | > 8.5                      |         |         | > 8.5                                 |                |         | > 8.5                      |       | UI   |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency = 1.875 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps |        | > 0.1                      |         |         | > 0.1                                 |                |         | > 0.1                      |       | UI   |

|                                                  | Jitter Frequency = 20 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps    |        | > 0.1                      |         |         | > 0.1                                 |                |         | > 0.1                      |       | UI   |

| 10010 7 13. Ollali                                                            | ix II GX Transceiver B                                                                                                                                                                      | look AU | ороон                                 | ivativii |                                             | ·4 Spe |     | 11110                                 | . 13) |     |      |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------|----------|---------------------------------------------|--------|-----|---------------------------------------|-------|-----|------|

| Symbol/<br>Description                                                        | Conditions                                                                                                                                                                                  |         | -3 Speed<br>Commercial Speed<br>Grade |          | Commercial and<br>Industrial Speed<br>Grade |        |     | -5 Speed<br>Commercial Speed<br>Grade |       |     | Unit |

|                                                                               |                                                                                                                                                                                             | Min     | Тур                                   | Max      | Min                                         | Тур    | Max | Min                                   | Тур   | Max |      |

| <b>CPRI Receiver Jitt</b>                                                     | ter Tolerance (15)                                                                                                                                                                          |         |                                       |          |                                             |        |     |                                       |       |     |      |

| Deterministic Jitter<br>Tolerance<br>(peak-to-peak)                           | Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |         | > 0.4                                 |          |                                             | > 0.4  |     |                                       | N/A   |     | UI   |

| Combined<br>Deterministic and<br>Random Jitter<br>Tolerance<br>(peak-to-peak) | Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |         | > 0.66                                |          |                                             | > 0.66 | 3   |                                       | N/A   |     | UI   |

|                    | -22. PCS Late                                                |                 |                | . , ,           |                   | Receiver P                   | CS Latency                |               |                                   |                  |                |

|--------------------|--------------------------------------------------------------|-----------------|----------------|-----------------|-------------------|------------------------------|---------------------------|---------------|-----------------------------------|------------------|----------------|

| Functional<br>Mode | Configuration                                                | Word<br>Aligner | Deskew<br>FIFO | Rate<br>Matcher | 8B/10B<br>Decoder | Receiver<br>State<br>Machine | Byte<br>De-<br>serializer | Byte<br>Order | Receiver<br>Phase<br>Comp<br>FIFO | Receiver<br>PIPE | <b>Sum</b> (2) |

|                    | 16/20-bit<br>channel<br>width; with<br>Rate<br>Matcher       | 4-5             | -              | 11-13           | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 19-23          |

| BASIC              | 16/20-bit<br>channel<br>width;<br>without<br>Rate<br>Matcher | 4-5             | -              | -               | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 8-10           |

| Double<br>Width    | 32/40-bit<br>channel<br>width; with<br>Rate<br>Matcher       | 2-2.5           | -              | 5.5-6.5         | 0.5               | -                            | 1                         | 1             | 1-2                               | -                | 11-14          |

|                    | 32/40-bit<br>channel<br>width;<br>without<br>Rate<br>Matcher | 2-2.5           | -              | -               | 0.5               | -                            | 1                         | 1-3           | 1-2                               | -                | 6-9            |

#### Notes to Table 4–21:

- (1) The latency numbers are with respect to the PLD-transceiver interface clock cycles.

- (2) The total latency number is rounded off in the Sum column.

- (3) The rate matcher latency shown is the steady state latency. Actual latency may vary depending on the skip ordered set gap allowed by the protocol, actual PPM difference between the reference clocks, and so forth.

- (4) For CPRI 614 Mbps and 1.228 Gbps data rates, the Quartus II software customizes the PLD-transceiver interface clocking to achieve zero clock cycle uncertainty in the receiver phase compensation FIFO latency. For more details, refer to the CPRI Mode section in the Stratix II GX Transceiver Architecture Overview chapter in volume 2 of the Stratix II GX Device Handbook

# EP2SGX90 Clock Timing Parameters

Tables 4–71 through 4–74 show the maximum clock timing parameters for EP2SGX90 devices.

| Table 4-71. E        | Table 4–71. EP2SGX90 Column Pins Global Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|

| Parameter            | Fast                                                            | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |

| Farailleter          | Industrial                                                      | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.861                                                           | 1.878      | 3.115    | 3.465    | 4.143    | ns     |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.696                                                           | 1.713      | 2.873    | 3.195    | 3.819    | ns     |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.254                                                          | -0.237     | 0.171    | 0.179    | 0.206    | ns     |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.419                                                          | -0.402     | -0.071   | -0.091   | -0.118   | ns     |  |  |  |  |  |  |

| Table 4-72. E        | Table 4–72. EP2SGX90 Row Pins Global Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |

|----------------------|--------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|

| Parameter            | Fast (                                                       | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |

| raiailletei          | Industrial                                                   | Commercial | Grade    | Grade    | Grade    | Ullita |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.634                                                        | 1.650      | 2.768    | 3.076    | 3.678    | ns     |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.639                                                        | 1.655      | 2.764    | 3.072    | 3.673    | ns     |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.481                                                       | -0.465     | -0.189   | -0.223   | -0.279   | ns     |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.476                                                       | -0.46      | -0.193   | -0.227   | -0.284   | ns     |  |  |  |  |  |  |

| Table 4-73. E        | Table 4–73. EP2SGX90 Column Pins Regional Clock Timing Parameters |            |          |          |          |       |  |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------|------------|----------|----------|----------|-------|--|--|--|--|--|--|--|

| Daramatar            | Fast (                                                            | Corner     | -3 Speed | -4 Speed | -5 Speed | Unito |  |  |  |  |  |  |  |

| Parameter            | Industrial                                                        | Commercial | Grade    | Grade    | Grade    | Units |  |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.688                                                             | 1.702      | 2.896    | 3.224    | 3.856    | ns    |  |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.551                                                             | 1.569      | 2.893    | 3.220    | 3.851    | ns    |  |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.105                                                            | -0.089     | 0.224    | 0.241    | 0.254    | ns    |  |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.27                                                             | -0.254     | 0.224    | 0.241    | 0.254    | ns    |  |  |  |  |  |  |  |

| I/O Standard       | Drive Strength | -3 Speed<br>Grade | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|--------------------|----------------|-------------------|-------------------|-------------------|------|

| 2.5 V              | 4 mA           | 230               | 194               | 180               | MHz  |

|                    | 8 mA           | 430               | 380               | 380               | MHz  |

|                    | 12 mA          | 630               | 575               | 550               | MHz  |

|                    | 16 mA (1)      | 930               | 845               | 820               | MHz  |

| 1.8 V              | 2 mA           | 120               | 109               | 104               | MHz  |

|                    | 4 mA           | 285               | 250               | 230               | MHz  |

|                    | 6 mA           | 450               | 390               | 360               | MHz  |

|                    | 8 mA           | 660               | 570               | 520               | MHz  |

|                    | 10 mA          | 905               | 805               | 755               | MHz  |

|                    | 12 mA (1)      | 1131              | 1040              | 990               | MHz  |

| 1.5 V              | 2 mA           | 244               | 200               | 180               | MHz  |

|                    | 4 mA           | 470               | 370               | 325               | MHz  |

|                    | 6 mA           | 550               | 430               | 375               | MHz  |

|                    | 8 mA (1)       | 625               | 495               | 420               | MHz  |

| SSTL-2 Class I     | 8 mA           | 400               | 300               | 300               | MHz  |

|                    | 12 mA (1)      | 400               | 400               | 350               | MHz  |

| SSTL-2 Class II    | 16 mA          | 350               | 350               | 300               | MHz  |

|                    | 20 mA          | 400               | 350               | 350               | MHz  |

|                    | 24 mA (1)      | 400               | 400               | 350               | MHz  |

| SSTL-18 Class I    | 4 mA           | 200               | 150               | 150               | MHz  |

|                    | 6 mA           | 350               | 250               | 200               | MHz  |

|                    | 8 mA           | 450               | 300               | 300               | MHz  |

|                    | 10 mA          | 500               | 400               | 400               | MHz  |

|                    | 12 mA (1)      | 650               | 550               | 400               | MHz  |

| SSTL-18 Class II   | 8 mA           | 200               | 200               | 150               | MHz  |

|                    | 16 mA          | 400               | 350               | 350               | MHz  |

|                    | 18 mA          | 450               | 400               | 400               | MHz  |

|                    | 20 mA (1)      | 550               | 500               | 450               | MHz  |

| 1.8-V HSTL Class I | 4 mA           | 300               | 300               | 300               | MHz  |

|                    | 6 mA           | 500               | 450               | 450               | MHz  |

|                    | 8 mA           | 650               | 600               | 600               | MHz  |

|                    | 10 mA          | 700               | 650               | 600               | MHz  |

|                    | 12 mA (1)      | 700               | 700               | 650               | MHz  |

| Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 3 of 5) |                   |      |           |          |          |          |         |           |                     |     |  |  |

|-----------------------------------------------------------------------------|-------------------|------|-----------|----------|----------|----------|---------|-----------|---------------------|-----|--|--|

|                                                                             |                   | N    | laximum   | Output ( | lock Tog | gle Rate | Deratin | g Factors | (ps/pF              | )   |  |  |

| I/O Standard                                                                | Drive<br>Strength | Coli | ımn I/O F | Pins     | Ro       | w I/O Pi | ns      |           | icated C<br>Outputs |     |  |  |

|                                                                             |                   | -3   | -4        | -5       | -3       | -4       | -5      | -3        | -4                  | -5  |  |  |

| SSTL-18 Class II                                                            | 8 mA              | 173  | 206       | 206      | -        | -        | -       | 155       | 206                 | 206 |  |  |

|                                                                             | 16 mA             | 150  | 160       | 160      | -        | -        | -       | 140       | 160                 | 160 |  |  |

|                                                                             | 18 mA             | 120  | 130       | 130      | -        | -        | -       | 110       | 130                 | 130 |  |  |

|                                                                             | 20 mA             | 109  | 127       | 127      | -        | -        | -       | 94        | 127                 | 127 |  |  |

| 2.5-V SSTL-2                                                                | 8 mA              | 364  | 680       | 680      | 364      | 680      | 680     | 350       | 680                 | 680 |  |  |

| Class I                                                                     | 12 mA             | 163  | 207       | 207      | 163      | 207      | 207     | 188       | 207                 | 207 |  |  |

| 2.5-V SSTL-2                                                                | 16 mA             | 118  | 147       | 147      | 118      | 147      | 147     | 94        | 147                 | 147 |  |  |

| Class II                                                                    | 20 mA             | 99   | 122       | 122      | -        | -        | -       | 87        | 122                 | 122 |  |  |

|                                                                             | 24 mA             | 91   | 116       | 116      | -        | -        | -       | 85        | 116                 | 116 |  |  |

| 1.8-V SSTL-18                                                               | 4 mA              | 458  | 570       | 570      | 458      | 570      | 570     | 505       | 570                 | 570 |  |  |

| Class I                                                                     | 6 mA              | 305  | 380       | 380      | 305      | 380      | 380     | 336       | 380                 | 380 |  |  |

|                                                                             | 8 mA              | 225  | 282       | 282      | 225      | 282      | 282     | 248       | 282                 | 282 |  |  |

|                                                                             | 10 mA             | 167  | 220       | 220      | 167      | 220      | 220     | 190       | 220                 | 220 |  |  |

|                                                                             | 12 mA             | 129  | 175       | 175      | -        | -        | -       | 148       | 175                 | 175 |  |  |

| 1.8-V SSTL-18                                                               | 8 mA              | 173  | 206       | 206      | -        | -        | -       | 155       | 206                 | 206 |  |  |

| Class II                                                                    | 16 mA             | 150  | 160       | 160      | -        | -        | -       | 140       | 160                 | 160 |  |  |

|                                                                             | 18 mA             | 120  | 130       | 130      | -        | -        | -       | 110       | 130                 | 130 |  |  |

|                                                                             | 20 mA             | 109  | 127       | 127      | -        | -        | -       | 94        | 127                 | 127 |  |  |

| 1.8-V HSTL Class I                                                          | 4 mA              | 245  | 282       | 282      | 245      | 282      | 282     | 229       | 282                 | 282 |  |  |

|                                                                             | 6 mA              | 164  | 188       | 188      | 164      | 188      | 188     | 153       | 188                 | 188 |  |  |

|                                                                             | 8 mA              | 123  | 140       | 140      | 123      | 140      | 140     | 114       | 140                 | 140 |  |  |

|                                                                             | 10 mA             | 110  | 124       | 124      | 110      | 124      | 124     | 108       | 124                 | 124 |  |  |

|                                                                             | 12 mA             | 97   | 110       | 110      | 97       | 110      | 110     | 104       | 110                 | 110 |  |  |

| 1.8-V HSTL                                                                  | 16 mA             | 101  | 104       | 104      | -        | -        | -       | 99        | 104                 | 104 |  |  |

| Class II                                                                    | 18 mA             | 98   | 102       | 102      | -        | -        | -       | 93        | 102                 | 102 |  |  |

|                                                                             | 20 mA             | 93   | 99        | 99       | -        | -        | -       | 88        | 99                  | 99  |  |  |

| 1.5-V HSTL Class I                                                          | 4 mA              | 168  | 196       | 196      | 168      | 196      | 196     | 188       | 196                 | 196 |  |  |

|                                                                             | 6 mA              | 112  | 131       | 131      | 112      | 131      | 131     | 125       | 131                 | 131 |  |  |

|                                                                             | 8 mA              | 84   | 99        | 99       | 84       | 99       | 99      | 95        | 99                  | 99  |  |  |

|                                                                             | 10 mA             | 87   | 98        | 98       | -        | -        | -       | 90        | 98                  | 98  |  |  |

|                                                                             | 12 mA             | 86   | 98        | 98       | -        | -        | -       | 87        | 98                  | 98  |  |  |

| Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 5 of 5) |                   |      |           |          |           |                   |                   |                            |        |     |  |  |

|-----------------------------------------------------------------------------|-------------------|------|-----------|----------|-----------|-------------------|-------------------|----------------------------|--------|-----|--|--|

|                                                                             |                   | N    | /laximum  | Output ( | Clock Tog | gle Rate          | Deratin           | g Factors                  | (ps/pF | )   |  |  |

| I/O Standard                                                                | Drive<br>Strength | Coli | umn I/O F | Pins     | Ro        | w I/O Pi          | ns                | Dedicated Clock<br>Outputs |        |     |  |  |

|                                                                             |                   | -3   | -4        | -5       | -3        | -4                | -5                | -3                         | -4     | -5  |  |  |

| 1.5-V differential                                                          | 16 mA             | 95   | 101       | 101      | -         | -                 | -                 | 96                         | 101    | 101 |  |  |

| HSTL Class II (3)                                                           | 18 mA             | 95   | 100       | 100      | -         | -                 | -                 | 101                        | 100    | 100 |  |  |

|                                                                             | 20 mA             | 94   | 101       | 101      | -         | -                 | -                 | 104                        | 101    | 101 |  |  |

| 3.3-V PCI                                                                   |                   | 134  | 177       | 177      | -         | -                 | -                 | 143                        | 177    | 177 |  |  |

| 3.3-V PCI-X                                                                 |                   | 134  | 177       | 177      | -         | -                 | -                 | 143                        | 177    | 177 |  |  |

| LVDS                                                                        |                   | -    | -         | -        | 155 (1)   | 155<br><i>(1)</i> | 155<br><i>(1)</i> | 134                        | 134    | 134 |  |  |

| LVPECL (4)                                                                  |                   | -    | -         | -        | -         | -                 | -                 | 134                        | 134    | 134 |  |  |

| 3.3-V LVTTL                                                                 | OCT 50 Ω          | 133  | 152       | 152      | 133       | 152               | 152               | 147                        | 152    | 152 |  |  |

| 2.5-V LVTTL                                                                 | OCT 50 Ω          | 207  | 274       | 274      | 207       | 274               | 274               | 235                        | 274    | 274 |  |  |

| 1.8-V LVTTL                                                                 | OCT 50 Ω          | 151  | 165       | 165      | 151       | 165               | 165               | 153                        | 165    | 165 |  |  |

| 3.3-V LVCMOS                                                                | OCT 50 Ω          | 300  | 316       | 316      | 300       | 316               | 316               | 263                        | 316    | 316 |  |  |

| 1.5-V LVCMOS                                                                | OCT 50 Ω          | 157  | 171       | 171      | 157       | 171               | 171               | 174                        | 171    | 171 |  |  |

| SSTL-2 Class I                                                              | OCT 50 Ω          | 121  | 134       | 134      | 121       | 134               | 134               | 77                         | 134    | 134 |  |  |

| SSTL-2 Class II                                                             | OCT 25 Ω          | 56   | 101       | 101      | 56        | 101               | 101               | 58                         | 101    | 101 |  |  |

| SSTL-18 Class I                                                             | OCT 50 Ω          | 100  | 123       | 123      | 100       | 123               | 123               | 106                        | 123    | 123 |  |  |

| SSTL-18 Class II                                                            | OCT 25 Ω          | 61   | 110       | 110      | -         | -                 | -                 | 59                         | 110    | 110 |  |  |

| 1.2-V HSTL (2)                                                              | OCT 50 Ω          | 95   | -         | -        | -         | -                 | -                 | 95                         | -      | -   |  |  |

<sup>(1)</sup> For LVDS output on row I/O pins the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Tables 4–91 through 4–95 for output toggle rates.

<sup>(2) 1.2-</sup>V HSTL is only supported on column I/O pins on -3 devices.

<sup>(3)</sup> Differential HSTL and SSTL is only supported on column clock and DQS outputs.

<sup>(4)</sup> LVPECL is only supported on column clock outputs.

Table 4–109 shows the high-speed I/O timing specifications for -5 speed grade Stratix II GX devices.

| Table 4–109. High-Speed I/O Specifications for -5 Speed Grade       Notes (1), (2) |                                                   |                         |      |                |     |       |                       |

|------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------|------|----------------|-----|-------|-----------------------|

| Symbol                                                                             | Conditions                                        |                         |      | -5 Speed Grade |     |       | Unit                  |

| Cymbol                                                                             |                                                   |                         |      | Min            | Тур | Max   | Ot                    |

| $f_{IN} = f_{HSDR} / W$                                                            | W = 2 to 32 (LVDS, HyperTransport technology) (3) |                         | 16   |                | 420 | MHz   |                       |

|                                                                                    | W = 1 (SERDES bypass, LVDS only)                  |                         |      | 16             |     | 500   | MHz                   |

|                                                                                    | W = 1 (SERDES used, LVDS only)                    |                         |      | 150            |     | 640   | MHz                   |

| f <sub>HSDR</sub> (data rate)                                                      | J = 4 to 10 (LVDS, HyperTransport technology)     |                         |      | 150            |     | 840   | Mbps                  |

|                                                                                    | J = 2 (LVDS, HyperTransport technology)           |                         |      | (4)            |     | 700   | Mbps                  |

|                                                                                    | J = 1 (LVDS only)                                 |                         |      | (4)            |     | 500   | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                               | J = 4 to 10 (LVDS, HyperTransport technology)     |                         |      | 150            |     | 840   | Mbps                  |

| TCCS                                                                               | All differential I/O standards                    |                         |      | -              |     | 200   | ps                    |

| SW                                                                                 | All differential I/O standards                    |                         |      | 440            |     | -     | ps                    |

| Output jitter                                                                      |                                                   |                         |      |                |     | 190   | ps                    |

| Output t <sub>RISE</sub>                                                           | All differential I/O standards                    |                         |      |                |     | 290   | ps                    |

| Output t <sub>FALL</sub>                                                           | All differential I/O standards                    |                         |      |                |     | 290   | ps                    |

| t <sub>DUTY</sub>                                                                  |                                                   |                         |      | 45             | 50  | 55    | %                     |

| DPA run length                                                                     |                                                   |                         |      |                |     | 6,400 | UI                    |

| DPA jitter tolerance                                                               | Data channel peak-to-peak jitter                  |                         |      | 0.44           |     |       | UI                    |

| DPA lock time                                                                      |                                                   |                         |      |                |     |       | Number of repetitions |

|                                                                                    | SPI-4                                             | 000000000<br>1111111111 | 10%  | 256            |     |       |                       |

|                                                                                    | Parallel Rapid I/O                                | 00001111                | 25%  | 256            |     |       | 1                     |

|                                                                                    |                                                   | 10010000                | 50%  | 256            |     |       | 1                     |

|                                                                                    | Miscellaneous                                     | 10101010                | 100% | 256            |     |       | 1                     |

|                                                                                    |                                                   | 01010101                |      | 256            |     |       | 1                     |

<sup>(1)</sup> When J = 4 to 10, the SERDES block is used.

<sup>(2)</sup> When J = 1 or 2, the SERDES block is bypassed.

<sup>(3)</sup> The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤840.

<sup>(4)</sup> The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

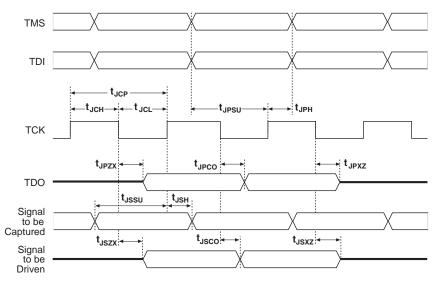

Figure 4-14. Stratix II GX JTAG Waveforms.

Table 4–117 shows the JTAG timing parameters and values for Stratix II GX devices.

| Table 4–117. Stratix II GX JTAG Timing Parameters and Values |                                                |    |     |      |  |

|--------------------------------------------------------------|------------------------------------------------|----|-----|------|--|

| Symbol                                                       | Parameter                                      |    | Max | Unit |  |

| t <sub>JCP</sub>                                             | TCK clock period                               | 30 |     | ns   |  |

| t <sub>JCH</sub>                                             | TCK clock high time                            | 12 |     | ns   |  |

| t <sub>JCL</sub>                                             | TCK clock low time                             | 12 |     | ns   |  |

| t <sub>JPSU</sub>                                            | JTAG port setup time                           | 4  |     | ns   |  |

| t <sub>JPH</sub>                                             | JTAG port hold time                            | 5  |     | ns   |  |

| t <sub>JPCO</sub>                                            | JTAG port clock to output                      |    | 9   | ns   |  |

| t <sub>JPZX</sub>                                            | JTAG port high impedance to valid output       |    | 9   | ns   |  |

| t <sub>JPXZ</sub>                                            | JTAG port valid output to high impedance       |    | 9   | ns   |  |

| t <sub>JSSU</sub>                                            | Capture register setup time                    | 4  |     | ns   |  |

| t <sub>JSH</sub>                                             | Capture register hold time                     | 5  |     | ns   |  |

| t <sub>JSCO</sub>                                            | Update register clock to output                |    | 12  | ns   |  |

| t <sub>JSZX</sub>                                            | Update register high impedance to valid output |    | 12  | ns   |  |

| t <sub>JSXZ</sub>                                            | Update register valid output to high impedance |    | 12  | ns   |  |

| Table 4–118. Document Revision History (Part 4 of 5) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Summary of Changes                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| June 2006, v4.0                                      | <ul> <li>Updated Table 6–5.</li> <li>Updated Table 6–6.</li> <li>Updated all values in Table 6–7.</li> <li>Added Tables 6–8 and 6–9.</li> <li>Added Figures 6–1 through 6–4.</li> <li>Updated Tables 6–85 through 6–96.</li> <li>Added Table 6–80, Stratix II GX Maximum Output Clock Rate for Dedicated Clock Pins.</li> <li>Updated Table 6–100.</li> <li>In "I/O Timing Measurement Methodology" section, updated Table 6–42.</li> <li>In "Internal Timing Parameters" section, updated Tables 6–43 through 6–48.</li> <li>In "Stratix II GX Clock Timing Parameters" section, updated Tables 6–50 through 6–65.</li> <li>In "IOE Programmable Delay" section, updated Tables 6–67 and 6–68.</li> <li>In "I/O Delays" section, updated Tables 6–71 through 6–74.</li> <li>In "Maximum Input &amp; Output Clock Toggle Rate" section, updated Tables 6–85 through 6–83.</li> <li>In "DCD Measurement Techniques" section, updated Tables 6–85 through 6–92.</li> <li>In "High-Speed I/O Specifications" section, updated Tables 6–94 through 6–96.</li> <li>In "External Memory Interface Specifications" section, updated Table 6–100.</li> </ul> | <ul> <li>Removed rows for V<sub>ID</sub>, V<sub>OD</sub>, V<sub>ICM</sub>, and V<sub>OCM</sub> from Table 6–5.</li> <li>Updated values for rx, tx, and refclkb in Table 6–6.</li> <li>Removed table containing 1.2-V PCML I/O information. That information is in Table 6–7.</li> <li>Added values to Table 6–100.</li> </ul> |  |  |  |  |  |