# E·XFL

# Intel - EP2SGX30DF780C5 Datasheet

Welcome to <u>E-XFL.COM</u>

## Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1694                                                       |

| Number of Logic Elements/Cells | 33880                                                      |

| Total RAM Bits                 | 1369728                                                    |

| Number of I/O                  | 361                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30df780c5 |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Lane deskew

- Rate matcher

- 8B/10B decoder

- Byte deserializer

- Byte ordering

- Receiver phase compensation FIFO buffer

## Receiver Input Buffer

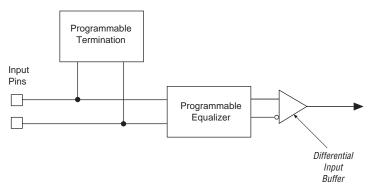

The Stratix II GX receiver input buffer supports the 1.2-V and 1.5-V PCML I/O standard at rates up to 6.375 Gbps. The common mode voltage of the receiver input buffer is programmable between 0.85 V and 1.2 V. You must select the 0.85 V common mode voltage for AC- and DC-coupled PCML links and the 1.2 V common mode voltage for DC-coupled LVDS links.

The receiver has programmable on-chip 100-, 120-, or 150- $\Omega$  differential termination for different protocols, as shown in Figure 2–12. The receiver's internal termination can be disabled if external terminations and biasing are provided. The receiver and transmitter differential termination resistances can be set independently of each other.

## Figure 2–12. Receiver Input Buffer

## Programmable Termination

The programmable termination can be statically set in the Quartus II software. Figure 2–13 shows the setup for programmable receiver termination. The termination can be disabled if external termination is provided.

## Programmable Run Length Violation

The word aligner supports a programmable run length violation counter. Whenever the number of the continuous '0' (or '1') exceeds a user programmable value, the rx\_rlv signal goes high for a minimum pulse width of two recovered clock cycles. The maximum run values supported are shown in Table 2–7.

| Table 2–7. Ma | Table 2–7. Maximum Run Length (UI) |        |        |        |  |  |  |  |  |  |

|---------------|------------------------------------|--------|--------|--------|--|--|--|--|--|--|

| Mode          | PMA Serialization                  |        |        |        |  |  |  |  |  |  |

| moue          | 8 Bit                              | 10 Bit | 16 Bit | 20 Bit |  |  |  |  |  |  |

| Single-Width  | 128                                | 160    | —      | —      |  |  |  |  |  |  |

| Double-Width  | _                                  | —      | 512    | 640    |  |  |  |  |  |  |

## **Running Disparity Check**

The running disparity error rx\_disperr and running disparity value rx\_runningdisp are sent along with aligned data from the 8B/10B decoder to the FPGA. You can ignore or act on the reported running disparity value and running disparity error signals.

## **Bit-Slip Mode**

The word aligner can operate in either pattern detection mode or in bit-slip mode.

The bit-slip mode provides the option to manually shift the word boundary through the FPGA. This feature is useful for:

- Longer synchronization patterns than the pattern detector can accommodate

- Scrambled data stream

- Input stream consisting of over-sampled data

This feature can be applied at 10-bit and 16-bit data widths.

The word aligner outputs a word boundary as it is received from the analog receiver after reset. You can examine the word and search its boundary in the FPGA. To do so, assert the rx\_bitslip signal. The rx\_bitslip signal should be toggled and held constant for at least two FPGA clock cycles.

For every rising edge of the rx\_bitslip signal, the current word boundary is slipped by one bit. Every time a bit is slipped, the bit received earliest is lost. If bit slipping shifts a complete round of bus width, the word boundary is back to the original boundary.

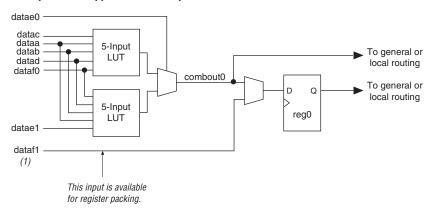

Figure 2–40. Template for Supported Seven-Input Functions in Extended LUT Mode

#### Note to Figure 2–40:

(1) If the seven-input function is un-registered, the unused eighth input is available for register packing. The second register, reg1, is not available.

# **Arithmetic Mode**

The arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An ALM in arithmetic mode uses two sets of two four-input LUTs along with two dedicated full adders. The dedicated adders allow the LUTs to be available to perform pre-adder logic; therefore, each adder can add the output of two four-input functions. The four LUTs share the dataa and datab inputs. As shown in Figure 2–41, the carry-in signal feeds to adder0, and the carry-out from adder0 feeds to carry-in of adder1. The carry-out from adder1 drives to adder0 of the next ALM in the LAB. ALMs in arithmetic mode can drive out registered and/or un-registered versions of the adder outputs.

The direct link interconnect allows a LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself, providing fast communication between adjacent LABs and/or blocks without using row interconnect resources.

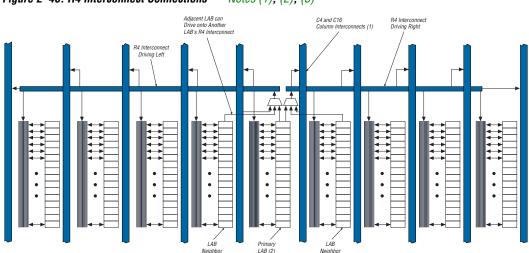

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–46 shows R4 interconnect connections from a LAB.

R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive onto the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive onto the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

## Notes to Figure 2–46:

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–46 show the 16 possible logical outputs per LAB.

# **M4K RAM Blocks**

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–51.

You can use the Quartus II software to control whether a clock input pin drives either a global, regional, or dual-regional clock network. The Quartus II software automatically selects the clocking resources if not specified.

## **Clock Control Block**

Each global clock, regional clock, and PLL external clock output has its own clock control block. The control block has two functions:

- Clock source selection (dynamic selection for global clocks)

- Clock power-down (dynamic clock enable or disable)

| Table 2–34. On-Chip Terminati | on Support by I/O Banks (Pa | art 2 of 2)                          |                  |

|-------------------------------|-----------------------------|--------------------------------------|------------------|

| On-Chip Termination Support   | I/O Standard Support        | Top and Bottom Banks<br>(3, 4, 7, 8) | Left Bank (1, 2) |

|                               | 3.3-V LVTTL                 | $\checkmark$                         | —                |

|                               | 3.3-V LVCMOS                | $\checkmark$                         | _                |

|                               | 2.5-V LVTTL                 | $\checkmark$                         | _                |

|                               | 2.5-V LVCMOS                | $\checkmark$                         | _                |

|                               | 1.8-V LVTTL                 | $\checkmark$                         | _                |

|                               | 1.8-V LVCMOS                | $\checkmark$                         | _                |

| eries termination with        | 1.5-V LVTTL                 | $\checkmark$                         | _                |

| calibration                   | 1.5-V LVCMOS                | $\checkmark$                         | _                |

|                               | SSTL-2 class I and II       | $\checkmark$                         | _                |

|                               | SSTL-18 class I and II      | $\checkmark$                         | _                |

|                               | 1.8-V HSTL class I          | $\checkmark$                         | _                |

|                               | 1.8-V HSTL class II         | $\checkmark$                         | —                |

|                               | 1.5-V HSTL class I          | $\checkmark$                         | _                |

|                               | 1.2-V HSTL                  | $\checkmark$                         | —                |

| Differential termination (4)  | LVDS                        | —                                    | $\checkmark$     |

| Differential termination (1)  | HyperTransport technology   | —                                    | $\checkmark$     |

### Note to Table 2–34:

(1) Clock pins CLK1 and CLK3, and pins FPLL [7..8] CLK do not support differential on-chip termination. Clock pins CLK0 and CLK2, do support differential on-chip termination. Clock pins in the top and bottom banks (CLK [4..7, 12..15]) do not support differential on-chip termination.

# Differential On-Chip Termination

Stratix II GX devices support internal differential termination with a nominal resistance value of 100 for LVDS input receiver buffers. LVPECL input signals (supported on clock pins only) require an external termination resistor. Differential on-chip termination is supported across the full range of supported differential data rates, as shown in the *High-Speed I/O Specifications* section of the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

For more information on differential on-chip termination, refer to the *High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

# **On-Chip Parallel Termination with Calibration**

Stratix II GX devices support on-chip parallel termination with calibration for column I/O pins only. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip parallel termination calibration circuit compares the total impedance of each I/O buffer to the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip parallel termination with calibration is only supported for input pins.

For more information about on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination with calibration, refer to the *DC* & *Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

# MultiVolt I/O Interface

The Stratix II GX architecture supports the MultiVolt I/O interface feature that allows Stratix II GX devices in all packages to interface with systems of different supply voltages. The Stratix II GX VCCINT pins must always be connected to a 1.2-V power supply. With a 1.2-V  $V_{CCINT}$  level, input pins are 1.2-, 1.5-, 1.8-, 2.5-, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.2-, 1.5-, 1.8-, 2.5-, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). The Stratix II GX VCCPD power pins must be connected to a 3.3-V power supply. These power pins are used to supply the pre-driver power to the output buffers, which increases the performance of the output pins. The VCCPD pins also power configuration input pins and JTAG input pins.

| Table 2–3             | 5. Stra                                | tix II G)               | ( MultiVol              | t I/O Sup               | oport N                 | ote (1)                 |                         |                         |                         |              |              |

|-----------------------|----------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------|--------------|

| V <sub>ccio</sub> (V) | (V) Input Signal (V) Output Signal (V) |                         |                         |                         |                         |                         |                         |                         |                         |              |              |

| VCCIO (V)             | 1.2                                    | 1.5                     | 1.8                     | 2.5                     | 3.3                     | 1.2                     | 1.5                     | 1.8                     | 2.5                     | 3.3          | 5.0          |

| 1.2                   | (4)                                    | <ul><li>✓ (2)</li></ul> | <ul> <li>(2)</li> </ul> | <ul><li>✓ (2)</li></ul> | <ul><li>(2)</li></ul>   | <ul><li>✓ (4)</li></ul> | —                       | —                       | —                       | —            | -            |

| 1.5                   | (4)                                    | ~                       | ~                       | <ul> <li>(2)</li> </ul> | <ul> <li>(2)</li> </ul> | 🗸 (3)                   | ~                       | —                       | —                       |              | -            |

| 1.8                   | (4)                                    | ~                       | ~                       | <ul> <li>(2)</li> </ul> | <ul> <li>(2)</li> </ul> | 🗸 (3)                   | 🗸 (3)                   | $\checkmark$            | —                       |              | -            |

| 2.5                   | (4)                                    | —                       | _                       | $\checkmark$            | $\checkmark$            | 🗸 (3)                   | 🗸 (3)                   | 🗸 (3)                   | $\checkmark$            | _            | —            |

| 3.3                   | (4)                                    |                         | _                       | $\checkmark$            | $\checkmark$            | <ul><li>✓ (3)</li></ul> | <ul><li>✓ (3)</li></ul> | <ul> <li>(3)</li> </ul> | <ul> <li>(3)</li> </ul> | $\checkmark$ | $\checkmark$ |

## Table 2-35 summarizes Stratix II GX MultiVolt I/O support.

Notes to Table 2-35:

To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and select the Allow LVTTL and LVCMOS input levels to overdrive input buffer option in the Quartus II software.

(2) The pin current may be slightly higher than the default value. You must verify that the driving device's V<sub>OL</sub> maximum and V<sub>OH</sub> minimum voltages do not violate the applicable Stratix II GX V<sub>IL</sub> maximum and V<sub>IH</sub> minimum voltage specifications.

(3) Although V<sub>CCIO</sub> specifies the voltage necessary for the Stratix II GX device to drive out, a receiving device powered at a different level can still interface with the Stratix II GX device if it has inputs that tolerate the V<sub>CCIO</sub> value.

(4) Stratix II GX devices support 1.2-V HSTL. They do not support 1.2-V LVTTL and 1.2-V LVCMOS.

The TDO and nCEO pins are powered by  $V_{CCIO}$  of the bank that they reside. TDO is in I/O bank 4 and nCEO is in I/O bank 7. Ideally, the V<sub>CC</sub> supplies for the I/O buffers of any two connected pins are at the same voltage level. This may not always be possible depending on the V<sub>CCIO</sub> level of TDO and nCEO pins on master devices and the configuration voltage level chosen by V<sub>CCSEL</sub> on slave devices. Master and slave devices can be in any position in the chain. Master indicates that it is driving out TDO or nCEO to a slave device. For multi-device passive configuration schemes, the nCEO pin of the master device drives the nCE pin of the slave device. The VCCSEL pin on the slave device selects which input buffer is used for nCE. When  $V_{\text{CCSEL}}$  is logic high, it selects the 1.8-V/1.5-V buffer powered by  $V_{\text{CCIO}}$ . When  $V_{\text{CCSEL}}$  is logic low, it selects the 3.3-V/2.5-V input buffer powered by  $V_{CCPD}$ . The ideal case is to have the  $V_{CCIO}$  of the nCEO bank in a master device match the V<sub>CCSEL</sub> settings for the nCE input buffer of the slave device it is connected to, but that may not be possible depending on the application.

| Table 2–42. Docu                                         | ment Revision History (Part 6 of 6)                        |                    |

|----------------------------------------------------------|------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version                          | Changes Made                                               | Summary of Changes |

| Previous Chapter<br>03 changes:<br>December 2005<br>v1.1 | Updated Figure 3–56.                                       |                    |

| Previous Chapter<br>03 changes:<br>October 2005<br>v1.0  | Added chapter to the <i>Stratix II GX Device</i> Handbook. |                    |

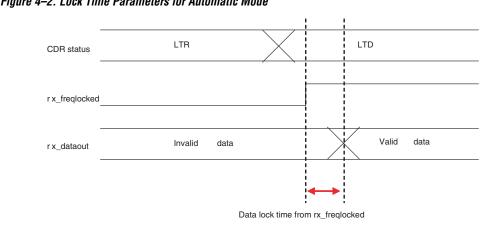

Figure 4–2. Lock Time Parameters for Automatic Mode

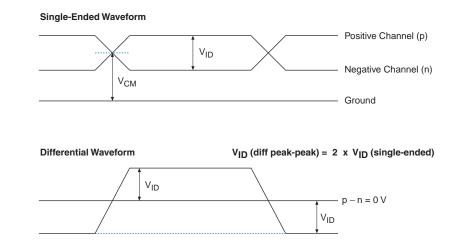

Figures 4–3 and 4–4 show differential receiver input and transmitter output waveforms, respectively.

Figure 4–3. Receiver Input Waveform

| Symbol/<br>Description                           | Conditions                                                                                                                                                    | -3 Speed<br>Commercial Speed<br>Grade |       |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |     |     | -5 Spe<br>mercia<br>Grad | l Speed | Unit |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|---------------------------------------------------------|-------|-----|-----|--------------------------|---------|------|

|                                                  |                                                                                                                                                               | Min                                   | Тур   | Max | Min                                                     | Тур   | Max | Min | Тур                      | Max     |      |

|                                                  | Jitter Frequency =<br>20 KHz<br>Data Rate =<br>1.485 Gbps (HD)<br>REFCLK =<br>74.25 MHz<br>Pattern = 75% Color<br>Bar<br>No Equalization<br>DC Gain = 0 dB    |                                       | >1    |     |                                                         | >1    |     |     | >1                       |         | UI   |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency =<br>100 KHz<br>Data Rate =<br>1.485 Gbps (HD)<br>REFCLK =<br>74.25 MHz<br>Pattern = 75% Color<br>Bar<br>No Equalization<br>DC Gain = 0 dB   |                                       | > 0.2 |     |                                                         | > 0.2 |     |     | > 0.2                    | 2       | UI   |

|                                                  | Jitter Frequency =<br>148.5 MHz<br>Data Rate =<br>1.485 Gbps (HD)<br>REFCLK =<br>74.25 MHz<br>Pattern = 75% Color<br>Bar<br>No Equalization<br>DC Gain = 0 dB |                                       | > 0.2 |     |                                                         | > 0.2 |     |     | > 0.2                    | 2       | UI   |

| Symbol                   | Parameter                                               |      | peed<br>e <i>(2)</i> |      | peed<br>e <i>(3)</i> |      | peed<br>ade | -5 Sj<br>Gra |      | Unit |

|--------------------------|---------------------------------------------------------|------|----------------------|------|----------------------|------|-------------|--------------|------|------|

|                          |                                                         | Min  | Max                  | Min  | Max                  | Min  | Max         | Min          | Max  |      |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock                     | -9   |                      | -10  |                      | -11  |             | -13          |      | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                       | 39   |                      | 40   |                      | 43   |             | 52           |      | ps   |

| t <sub>MEGADATAASU</sub> | A port data setup time before clock                     | 50   |                      | 52   |                      | 55   |             | 67           |      | ps   |

| t <sub>megadataah</sub>  | A port data hold time after clock                       | 243  |                      | 255  |                      | 271  |             | 325          |      | ps   |

| t <sub>MEGAADDRASU</sub> | A port address setup<br>time before clock               | 589  |                      | 618  |                      | 657  |             | 789          |      | ps   |

| t <sub>megaaddrah</sub>  | A port address hold time after clock                    | -347 |                      | -365 |                      | -388 |             | -465         |      | ps   |

| t <sub>MEGADATABSU</sub> | B port setup time<br>before clock                       | 50   |                      | 52   |                      | 55   |             | 67           |      | ps   |

| t <sub>MEGADATABH</sub>  | B port hold time after<br>clock                         | 243  |                      | 255  |                      | 271  |             | 325          |      | ps   |

| t <sub>MEGAADDRBSU</sub> | B port address setup<br>time before clock               | 589  |                      | 618  |                      | 657  |             | 789          |      | ps   |

| t <sub>megaaddrbh</sub>  | B port address hold time after clock                    | -347 |                      | -365 |                      | -388 |             | -465         |      | ps   |

| t <sub>MEGADATACO1</sub> | Clock-to-output delay<br>when using output<br>registers | 480  | 715                  | 480  | 749                  | 480  | 797         | 480          | 957  | ps   |

| t <sub>MEGADATACO2</sub> | Clock-to-output delay<br>without output<br>registers    | 1950 | 2899                 | 1950 | 3042                 | 1950 | 3235        | 1950         | 3884 | ps   |

| t <sub>MEGACLKL</sub>    | Minimum clock low time                                  | 1250 |                      | 1312 |                      | 1395 |             | 1675         |      | ps   |

| t <sub>MEGACLKH</sub>    | Minimum clock high<br>time                              | 1250 |                      | 1312 |                      | 1395 |             | 1675         |      | ps   |

| t <sub>MEGACLR</sub>     | Minimum clear pulse width                               | 144  |                      | 151  |                      | 160  |             | 192          |      | ps   |

(1) The M512 block  $f_{MAX}$  obtained using the Quartus II software does not necessarily equal to 1/TMEGARC.

(2) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(3) This column refers to -3 speed grades for EP2SGX130 devices.

| Table 4–86. Stra | tix II GX I/O (   | Output Delay     | for Column Pi                            | ins (Part 2 o         | of 7)                 |                   |                   |      |

|------------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| I/O Standard     | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| 2.5 V            | 4 mA              | t <sub>OP</sub>  | 1053                                     | 2063                  | 2165                  | 2302              | 2480              | ps   |

|                  |                   | t <sub>DIP</sub> | 1075                                     | 2129                  | 2235                  | 2376              | 2570              | ps   |

|                  | 8 mA              | t <sub>OP</sub>  | 1001                                     | 1841                  | 1932                  | 2054              | 2218              | ps   |

|                  |                   | t <sub>DIP</sub> | 1023                                     | 1907                  | 2002                  | 2128              | 2308              | ps   |

|                  | 12 mA             | t <sub>OP</sub>  | 980                                      | 1742                  | 1828                  | 1944              | 2101              | ps   |

|                  |                   | t <sub>DIP</sub> | 1002                                     | 1808                  | 1898                  | 2018              | 2191              | ps   |

|                  | 16 mA (1)         | t <sub>OP</sub>  | 962                                      | 1679                  | 1762                  | 1873              | 2027              | ps   |

|                  |                   | t <sub>DIP</sub> | 984                                      | 1745                  | 1832                  | 1947              | 2117              | ps   |

| 1.8 V            | 2 mA              | t <sub>OP</sub>  | 1093                                     | 2904                  | 3048                  | 3241              | 3472              | ps   |

|                  |                   | t <sub>DIP</sub> | 1115                                     | 2970                  | 3118                  | 3315              | 3562              | ps   |

|                  | 4 mA              | t <sub>OP</sub>  | 1098                                     | 2248                  | 2359                  | 2509              | 2698              | ps   |

|                  |                   | t <sub>DIP</sub> | 1120                                     | 2314                  | 2429                  | 2583              | 2788              | ps   |

|                  | 6 mA              | t <sub>OP</sub>  | 1022                                     | 2024                  | 2124                  | 2258              | 2434              | ps   |

|                  |                   | t <sub>DIP</sub> | 1044                                     | 2090                  | 2194                  | 2332              | 2524              | ps   |

|                  | 8 mA              | t <sub>OP</sub>  | 1024                                     | 1947                  | 2043                  | 2172              | 2343              | ps   |

|                  |                   | t <sub>DIP</sub> | 1046                                     | 2013                  | 2113                  | 2246              | 2433              | ps   |

|                  | 10 mA             | t <sub>OP</sub>  | 978                                      | 1882                  | 1975                  | 2100              | 2266              | ps   |

|                  |                   | t <sub>DIP</sub> | 1000                                     | 1948                  | 2045                  | 2174              | 2356              | ps   |

|                  | 12 mA (1)         | t <sub>OP</sub>  | 979                                      | 1833                  | 1923                  | 2045              | 2209              | ps   |

|                  |                   | t <sub>DIP</sub> | 1001                                     | 1899                  | 1993                  | 2119              | 2299              | ps   |

| 1.5 V            | 2 mA              | t <sub>OP</sub>  | 1073                                     | 2505                  | 2629                  | 2795              | 3002              | ps   |

|                  |                   | t <sub>DIP</sub> | 1095                                     | 2571                  | 2699                  | 2869              | 3092              | ps   |

|                  | 4 mA              | t <sub>OP</sub>  | 1009                                     | 2023                  | 2123                  | 2257              | 2433              | ps   |

|                  |                   | t <sub>DIP</sub> | 1031                                     | 2089                  | 2193                  | 2331              | 2523              | ps   |

|                  | 6 mA              | t <sub>OP</sub>  | 1012                                     | 1923                  | 2018                  | 2146              | 2315              | ps   |

|                  |                   | t <sub>DIP</sub> | 1034                                     | 1989                  | 2088                  | 2220              | 2405              | ps   |

|                  | 8 mA (1)          | t <sub>OP</sub>  | 971                                      | 1878                  | 1970                  | 2095              | 2262              | ps   |

|                  |                   | t <sub>DIP</sub> | 993                                      | 1944                  | 2040                  | 2169              | 2352              | ps   |

| I/O Standard    | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|-----------------|----------------|----------------|----------------|----------------|------|

| LVTTL           | 4 mA           | 270            | 225            | 210            | MHz  |

|                 | 8 mA           | 435            | 355            | 325            | MHz  |

|                 | 12 mA          | 580            | 475            | 420            | MHz  |

|                 | 16 mA          | 720            | 594            | 520            | MHz  |

|                 | 20 mA          | 875            | 700            | 610            | MHz  |

|                 | 24 mA (1)      | 1030           | 794            | 670            | MHz  |

| LVCMOS          | 4 mA           | 290            | 250            | 230            | MHz  |

|                 | 8 mA           | 565            | 480            | 440            | MHz  |

|                 | 12 mA          | 790            | 710            | 670            | MHz  |

|                 | 16 mA          | 1020           | 925            | 875            | MHz  |

|                 | 20 mA          | 1066           | 985            | 935            | MHz  |

|                 | 24 mA (1)      | 1100           | 1040           | 1000           | MHz  |

| 2.5 V           | 4 mA           | 230            | 194            | 180            | MHz  |

|                 | 8 mA           | 430            | 380            | 380            | MHz  |

|                 | 12 mA          | 630            | 575            | 550            | MHz  |

|                 | 16 mA (1)      | 930            | 845            | 820            | MHz  |

| 1.8 V           | 2 mA           | 120            | 109            | 104            | MHz  |

|                 | 4 mA           | 285            | 250            | 230            | MHz  |

|                 | 6 mA           | 450            | 390            | 360            | MHz  |

|                 | 8 mA           | 660            | 570            | 520            | MHz  |

|                 | 10 mA          | 905            | 805            | 755            | MHz  |

|                 | 12 mA (1)      | 1131           | 1040           | 990            | MHz  |

| 1.5 V           | 2 mA           | 244            | 200            | 180            | MHz  |

|                 | 4 mA           | 470            | 370            | 325            | MHz  |

|                 | 6 mA           | 550            | 430            | 375            | MHz  |

|                 | 8 mA (1)       | 625            | 495            | 420            | MHz  |

| SSTL-2 Class I  | 8 mA           | 400            | 300            | 300            | MHz  |

|                 | 12 mA (1)      | 400            | 400            | 350            | MHz  |

| SSTL-2 Class II | 16 mA          | 350            | 350            | 300            | MHz  |

|                 | 20 mA          | 400            | 350            | 350            | MHz  |

|                 | 24 mA (1)      | 400            | 400            | 350            | MHz  |

Table 4–91 shows the maximum output clock toggle rates for Stratix II GX device column pins.

| I/O Standard             | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|--------------------------|----------------|----------------|----------------|----------------|------|

| Differential             | 4 mA           | 200            | 150            | 150            | MHz  |

| SSTL-18 Class I          | 6 mA           | 350            | 250            | 200            | MHz  |

|                          | 8 mA           | 450            | 300            | 300            | MHz  |

|                          | 10 mA          | 500            | 400            | 400            | MHz  |

|                          | 12 mA          | 700            | 550            | 400            | MHz  |

| Differential             | 8 mA           | 200            | 200            | 150            | MHz  |

| SSTL-18 Class II         | 16 mA          | 400            | 350            | 350            | MHz  |

|                          | 18 mA          | 450            | 400            | 400            | MHz  |

|                          | 20 mA          | 550            | 500            | 450            | MHz  |

| 1.8-V HSTL               | 4 mA           | 300            | 300            | 300            | MHz  |

| differential<br>Class I  | 6 mA           | 500            | 450            | 450            | MHz  |

|                          | 8 mA           | 650            | 600            | 600            | MHz  |

|                          | 10 mA          | 700            | 650            | 600            | MHz  |

|                          | 12 mA          | 700            | 700            | 650            | MHz  |

| 1.8-V HSTL               | 16 mA          | 500            | 500            | 450            | MHz  |

| differential<br>Class II | 18 mA          | 550            | 500            | 500            | MHz  |

|                          | 20 mA          | 650            | 550            | 550            | MHz  |

| 1.5-V HSTL               | 4 mA           | 350            | 300            | 300            | MHz  |

| differential<br>Class I  | 6 mA           | 500            | 500            | 450            | MHz  |

| UI235 I                  | 8 mA           | 700            | 650            | 600            | MHz  |

|                          | 10 mA          | 700            | 700            | 650            | MHz  |

|                          | 12 mA          | 700            | 700            | 700            | MHz  |

| 1.5-V HSTL               | 16 mA          | 600            | 600            | 550            | MHz  |

| differential<br>Class II | 18 mA          | 650            | 600            | 600            | MHz  |

| UI235 II                 | 20 mA          | 700            | 650            | 600            | MHz  |

(1) This is the default setting in the Quartus II software.

|                    |                   | Ν               | laximum | Output ( | Clock Tog    | gle Rate          | Deratin           | g Factors                  | s (ps/pF) | )   |

|--------------------|-------------------|-----------------|---------|----------|--------------|-------------------|-------------------|----------------------------|-----------|-----|

| I/O Standard       | Drive<br>Strength | Column I/O Pins |         |          | Row I/O Pins |                   |                   | Dedicated Clock<br>Outputs |           |     |

|                    |                   | -3              | -4      | -5       | -3           | -4                | -5                | -3                         | -4        | -5  |

| 1.5-V differential | 16 mA             | 95              | 101     | 101      | -            | -                 | -                 | 96                         | 101       | 101 |

| HSTL Class II (3)  | 18 mA             | 95              | 100     | 100      | -            | -                 | -                 | 101                        | 100       | 100 |

|                    | 20 mA             | 94              | 101     | 101      | -            | -                 | -                 | 104                        | 101       | 101 |

| 3.3-V PCI          |                   | 134             | 177     | 177      | -            | -                 | -                 | 143                        | 177       | 177 |

| 3.3-V PCI-X        |                   | 134             | 177     | 177      | -            | -                 | -                 | 143                        | 177       | 177 |

| LVDS               |                   | -               | -       | -        | 155 (1)      | 155<br><i>(1)</i> | 155<br><i>(1)</i> | 134                        | 134       | 134 |

| LVPECL (4)         |                   | -               | -       | -        | -            | -                 | -                 | 134                        | 134       | 134 |

| 3.3-V LVTTL        | OCT 50 Ω          | 133             | 152     | 152      | 133          | 152               | 152               | 147                        | 152       | 152 |

| 2.5-V LVTTL        | OCT 50 Ω          | 207             | 274     | 274      | 207          | 274               | 274               | 235                        | 274       | 274 |

| 1.8-V LVTTL        | OCT 50 Ω          | 151             | 165     | 165      | 151          | 165               | 165               | 153                        | 165       | 165 |

| 3.3-V LVCMOS       | OCT 50 Ω          | 300             | 316     | 316      | 300          | 316               | 316               | 263                        | 316       | 316 |

| 1.5-V LVCMOS       | OCT 50 Ω          | 157             | 171     | 171      | 157          | 171               | 171               | 174                        | 171       | 171 |

| SSTL-2 Class I     | OCT 50 Ω          | 121             | 134     | 134      | 121          | 134               | 134               | 77                         | 134       | 134 |

| SSTL-2 Class II    | OCT 25 Ω          | 56              | 101     | 101      | 56           | 101               | 101               | 58                         | 101       | 101 |

| SSTL-18 Class I    | OCT 50 Ω          | 100             | 123     | 123      | 100          | 123               | 123               | 106                        | 123       | 123 |

| SSTL-18 Class II   | OCT 25 Ω          | 61              | 110     | 110      | -            | -                 | -                 | 59                         | 110       | 110 |

| 1.2-V HSTL (2)     | OCT 50 $\Omega$   | 95              | -       | -        | -            | -                 | -                 | 95                         | -         | -   |

(1) For LVDS output on row I/O pins the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Tables 4–91 through 4–95 for output toggle rates.

(2) 1.2-V HSTL is only supported on column I/O pins on -3 devices.

(3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

(4) LVPECL is only supported on column clock outputs.

| Maximum DCD (ps) for<br>DDIO Column Output I/O<br>Standard | Input IO Standard (No PLL in the Clock Path) |          |                  |          |        |      |  |  |  |

|------------------------------------------------------------|----------------------------------------------|----------|------------------|----------|--------|------|--|--|--|

|                                                            | TTL/C                                        | MOS      | SSTL-2 SSTL/HSTL |          | HSTL12 | Unit |  |  |  |

|                                                            | 3.3/2.5V                                     | 1.8/1.5V | 2.5V             | 1.8/1.5V | 1.2V   |      |  |  |  |

| SSTL-18 Class II                                           | 140                                          | 260      | 70               | 70       | 70     | ps   |  |  |  |

| 1.8-V HSTL Class I                                         | 150                                          | 270      | 60               | 60       | 60     | ps   |  |  |  |

| 1.8-V HSTL Class II                                        | 150                                          | 270      | 60               | 60       | 60     | ps   |  |  |  |

| 1.5-V HSTL Class I                                         | 150                                          | 270      | 55               | 55       | 55     | ps   |  |  |  |

| 1.5-V HSTL Class II                                        | 125                                          | 240      | 85               | 85       | 85     | ps   |  |  |  |

| 1.2-V HSTL                                                 | 240                                          | 360      | 155              | 155      | 155    | ps   |  |  |  |

| LVPECL                                                     | 180                                          | 180      | 180              | 180      | 180    | ps   |  |  |  |

Table A 109 Maximum DCD for DDIO Output on Column 1/0 Bins Without DLL in the Clock Both for 2

(1) Table 4–102 assumes the input clock has zero DCD.

Table 4–103. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 and -5 Devices Note (1)

| Maximum DCD (ps) for _<br>DDIO Column Output I/O<br>Standard | Input IO Standard (No PLL in the Clock Path) |          |        |           |      |  |

|--------------------------------------------------------------|----------------------------------------------|----------|--------|-----------|------|--|

|                                                              | TTL/CMOS                                     |          | SSTL-2 | SSTL/HSTL | Unit |  |

|                                                              | 3.3/2.5V                                     | 1.8/1.5V | 2.5V   | 1.8/1.5V  | 1    |  |

| 3.3-V LVTTL                                                  | 440                                          | 495      | 170    | 160       | ps   |  |

| 3.3-V LVCMOS                                                 | 390                                          | 450      | 120    | 110       | ps   |  |

| 2.5 V                                                        | 375                                          | 430      | 105    | 95        | ps   |  |

| 1.8 V                                                        | 325                                          | 385      | 90     | 100       | ps   |  |

| 1.5-V LVCMOS                                                 | 430                                          | 490      | 160    | 155       | ps   |  |

| SSTL-2 Class I                                               | 355                                          | 410      | 85     | 75        | ps   |  |

| SSTL-2 Class II                                              | 350                                          | 405      | 80     | 70        | ps   |  |

| SSTL-18 Class I                                              | 335                                          | 390      | 65     | 65        | ps   |  |

| SSTL-18 Class II                                             | 320                                          | 375      | 70     | 80        | ps   |  |

| 1.8-V HSTL Class I                                           | 330                                          | 385      | 60     | 70        | ps   |  |

| 1.8-V HSTL Class II                                          | 330                                          | 385      | 60     | 70        | ps   |  |

| 1.5-V HSTL Class I                                           | 330                                          | 390      | 60     | 70        | ps   |  |

| 1.5-V HSTL Class II                                          | 330                                          | 360      | 90     | 100       | ps   |  |

| LVPECL                                                       | 180                                          | 180      | 180    | 180       | ps   |  |

(1) Table 4–103 assumes the input clock has zero DCD.

Table 4–109 shows the high-speed I/O timing specifications for -5 speed grade Stratix II GX devices.

| <b>•</b> • • •                       | Conditions                                           |                         |      | -5 Speed Grade |     |       |                       |

|--------------------------------------|------------------------------------------------------|-------------------------|------|----------------|-----|-------|-----------------------|

| Symbol                               |                                                      |                         |      | Min            | Тур | Max   | Unit                  |

| $f_{IN} = f_{HSDR} / W$              | W = 2 to 32 (LVDS, HyperTransport technology)<br>(3) |                         |      | 16             |     | 420   | MHz                   |

|                                      | W = 1 (SERDES bypass, LVDS only)                     |                         |      |                |     | 500   | MHz                   |

|                                      | W = 1 (SERDES used, LVDS only)                       |                         |      | 150            |     | 640   | MHz                   |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, HyperTransport technology)        |                         |      | 150            |     | 840   | Mbps                  |

|                                      | J = 2 (LVDS, HyperTransport technology)              |                         |      |                |     | 700   | Mbps                  |

|                                      | J = 1 (LVDS only)                                    |                         |      |                |     | 500   | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, HyperTransport technology)        |                         |      |                |     | 840   | Mbps                  |

| TCCS                                 | All differential I/O standards                       |                         |      |                |     | 200   | ps                    |

| SW                                   | All differential I/O standards                       |                         |      |                |     | -     | ps                    |

| Output jitter                        |                                                      |                         |      |                |     | 190   | ps                    |

| Output t <sub>RISE</sub>             | All differential I/O standards                       |                         |      |                |     | 290   | ps                    |

| Output t <sub>FALL</sub>             | All differential I/O standards                       |                         |      |                |     | 290   | ps                    |

| t <sub>DUTY</sub>                    |                                                      |                         |      | 45             | 50  | 55    | %                     |

| DPA run length                       |                                                      |                         |      |                |     | 6,400 | UI                    |

| DPA jitter tolerance                 | Data channel peak-to-peak jitter                     |                         |      |                |     |       | UI                    |

| DPA lock time                        |                                                      |                         |      |                |     |       | Number of repetitions |

|                                      | SPI-4                                                | 000000000<br>1111111111 | 10%  | 256            |     |       |                       |

|                                      | Parallel Rapid I/O                                   | 00001111                | 25%  | 256            |     |       |                       |

|                                      |                                                      | 10010000                | 50%  | 256            |     |       |                       |

|                                      | Miscellaneous                                        | 10101010                | 100% | 256            |     |       | 1                     |

|                                      |                                                      | 01010101                |      | 256            |     |       | 1                     |

(1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤840.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.