Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1694                                                        |

| Number of Logic Elements/Cells | 33880                                                       |

| Total RAM Bits                 | 1369728                                                     |

| Number of I/O                  | 361                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30df780c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

capable of built-in self test (BIST) generation and verification. The ALT2GXB megafunction in the Quartus II software provides a step-by-step menu selection to configure the transceiver.

Figure 2–1 shows the block diagram for the Stratix II GX transceiver channel. Stratix II GX transceivers provide PCS and PMA implementations for all supported protocols. The PCS portion of the transceiver consists of the word aligner, lane deskew FIFO buffer, rate matcher FIFO buffer, 8B/10B encoder and decoder, byte serializer and deserializer, byte ordering, and phase compensation FIFO buffers.

Each Stratix II GX transceiver channel is also capable of BIST generation and verification in addition to various loopback modes. The PMA portion of the transceiver consists of the serializer and deserializer, the CRU, and the high-speed differential transceiver buffers that contain pre-emphasis, programmable on-chip termination (OCT), programmable voltage output differential ( $V_{\rm OD}$ ), and equalization.

#### **Transmitter Path**

This section describes the data path through the Stratix II GX transmitter. The Stratix II GX transmitter contains the following modules:

- Transmitter PLLs

- Access to one of two PLLs

- Transmitter logic array interface

- Transmitter phase compensation FIFO buffer

- Byte serializer

- 8B/10B encoder

- Serializer (parallel-to-serial converter)

- Transmitter differential output buffer

#### Transmitter PLLs

Each transceiver block has two transmitter PLLs which receive two reference clocks to generate timing and the following clocks:

- High-speed clock used by the serializer to transmit the high-speed differential transmitter data

- Low-speed clock to load the parallel transmitter data of the serializer

The serializer uses high-speed clocks to transmit data. The serializer is also referred to as parallel in serial out (PISO). The high-speed clock is fed to the local clock generation buffer. The local clock generation buffers divide the high-speed clock on the transmitter to a desired frequency on a per-channel basis. Figure 2–3 is a block diagram of the transmitter clocks.

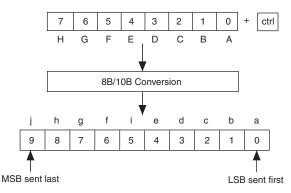

Figure 2-5. 8B/10B Encoding Process

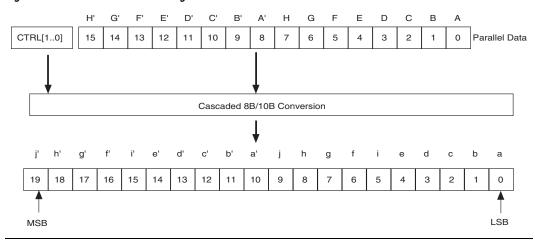

In single-width mode, the 8B/10B encoder generates a 10-bit code group from the 8-bit data and 1-bit control identifier. In double-width mode, there are two 8B/10B encoders that are cascaded together and generate a 20-bit (2 × 10-bit) code group from the 16-bit (2 × 8-bit) data + 2-bit (2 × 1-bit) control identifier. Figure 2–6 shows the 20-bit encoding process. The 8B/10B encoder conforms to the IEEE 802.3 1998 edition standards.

Figure 2-6. 16-Bit to 20-Bit Encoding Process

Upon power on or reset, the 8B/10B encoder has a negative disparity which chooses the 10-bit code from the RD-column. However, the running disparity can be changed via the tx\_forcedisp and tx\_dispval ports.

When the FIFO pointers initialize, the receiver domain clock must remain phase locked to receiver FPGA clock.

After resetting the receiver FIFO buffer, writing to the receiver FIFO buffer begins and continues on each parallel clock. The phase compensation FIFO buffer is eight words deep for PIPE mode and four words deep for all other modes.

### **Loopback Modes**

The Stratix II GX transceiver has built-in loopback modes for debugging and testing. The loopback modes are configured in the Stratix II GX ALT2GXB megafunction in the Quartus II software. The available loopback modes are:

- Serial loopback

- Parallel loopback

- Reverse serial loopback

- Reverse serial loopback (pre-CDR)

- PCI Express PIPE reverse parallel loopback (available only in PIPE mode)

#### Serial Loopback

The serial loopback mode exercises all the transceiver logic, except for the input buffer. Serial loopback is available for all non-PIPE modes. The loopback function is dynamically enabled through the rx\_seriallpbken port on a channel-by-channel basis.

In serial loopback mode, the data on the transmit side is sent by the PLD. A separate mode is available in the ALT2GXB megafunction under Basic protocol mode, in which PRBS data is generated and verified internally in the transceiver. The PRBS patterns available in this mode are shown in Table 2–10.

Table 2–10 shows the BIST data output and verifier alignment pattern.

| Table 2–10. BIST Data Output and Verifier Alignment Pattern |              |       |          |        |          |  |  |  |

|-------------------------------------------------------------|--------------|-------|----------|--------|----------|--|--|--|

| Parallel Data Width                                         |              |       |          |        |          |  |  |  |

| Pattern                                                     | Polynomial   | 8-Bit | 10-Bit   | 16-Bit | 20-Bit   |  |  |  |

| PRBS-7                                                      | ×7 + ×6 + 1  |       |          |        | <b>✓</b> |  |  |  |

| PRBS-10                                                     | ×10 + ×7 + 1 |       | <b>✓</b> |        |          |  |  |  |

Figure 2-33. Direct Link Connection Direct link interconnect from Direct link interconnect from left LAB, TriMatrix™ memory right LAB, TriMatrix memory block, DSP block, or block, DSP block, or IOE output input/output element (IOE) ALMs Direct link Direct link interconnect < interconnect to left to right Local Interconnect LAB

Figure 2–33 shows the direct link connection.

## **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, and synchronous load control signals, providing a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–34. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock. Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous

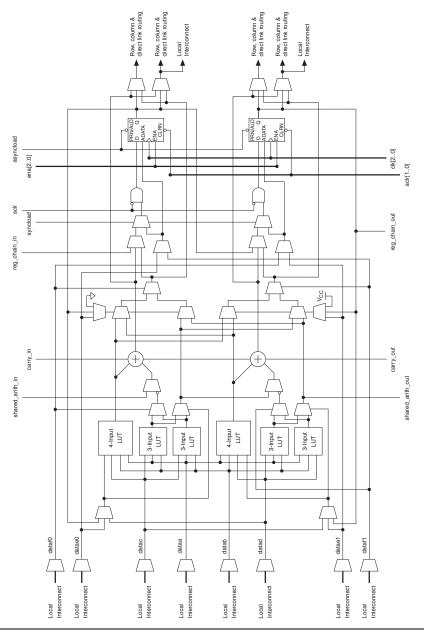

Figure 2-36. Stratix II GX ALM Details

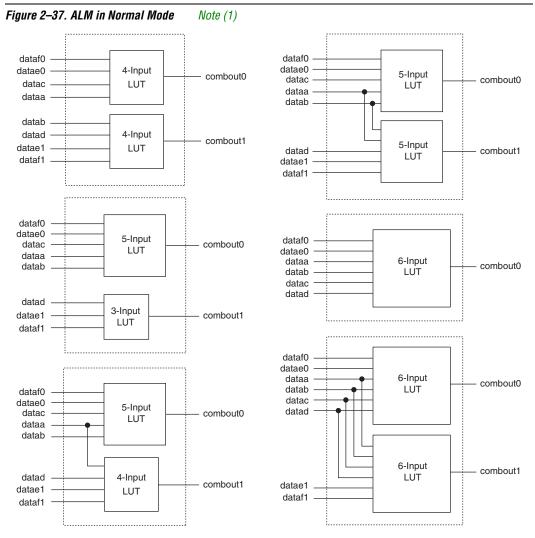

Note to Figure 2-37:

(1) Combinations of functions with less inputs than those shown are also supported. For example, combinations of functions with the following number of inputs are supported: 4 and 3, 3 and 2, 5 and 2, etc.

The normal mode provides complete backward compatibility with four-input LUT architectures. Two independent functions of four inputs or less can be implemented in one Stratix II GX ALM. In addition, a five-input function and an independent three-input function can be implemented without sharing inputs.

#### Carry Chain

The carry chain provides a fast carry function between the dedicated adders in arithmetic or shared arithmetic mode. Carry chains can begin in either the first ALM or the fifth ALM in a LAB. The final carry-out signal is routed to an ALM, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during compilation, or you can create it manually during design entry. Parameterized functions, such as LPM functions, automatically take advantage of carry chains for the appropriate functions. The Quartus II Compiler creates carry chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically, allowing fast horizontal connections to TriMatrix memory and DSP blocks. A carry chain can continue as far as a full column. To avoid routing congestion in one small area of the device when a high fan-in arithmetic function is implemented, the LAB can support carry chains that only utilize either the top half or the bottom half of the LAB before connecting to the next LAB. The other half of the ALMs in the LAB is available for implementing narrower fan-in functions in normal mode. Carry chains that use the top four ALMs in the first LAB will carry into the top half of the ALMs in the next LAB within the column. Carry chains that use the bottom four ALMs in the first LAB will carry into the bottom half of the ALMs in the next LAB within the column. Every other column of the LABs are top-half bypassable, while the other LAB columns are bottom-half bypassable. Refer to "MultiTrack Interconnect" on page 2–63 for more information on carry chain interconnect.

#### Shared Arithmetic Mode

In shared arithmetic mode, the ALM can implement a three-input add. In this mode, the ALM is configured with four 4-input LUTs. Each LUT either computes the sum of three inputs or the carry of three inputs. The output of the carry computation is fed to the next adder (either to adder1 in the same ALM or to adder0 of the next ALM in the LAB) using a dedicated connection called the shared arithmetic chain. This shared arithmetic chain can significantly improve the performance of an adder tree by reducing the number of summation stages required to implement an adder tree. Figure 2–43 shows the ALM in shared arithmetic mode.

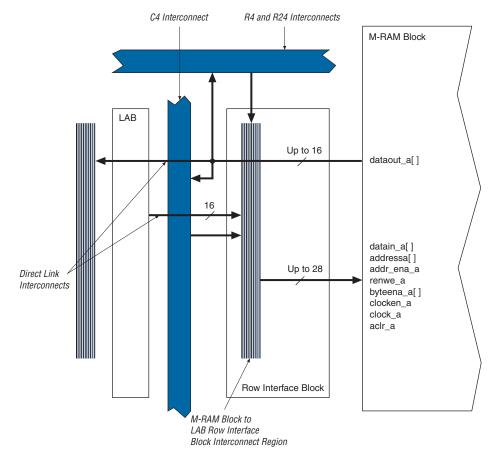

Figure 2-56. M-RAM Row Unit Interface to Interconnect

The Stratix II GX clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state, thereby reducing the overall power consumption of the device. The global and regional clock networks can be powered down statically through a setting in the configuration file (.sof or .pof). Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software. The dynamic clock enable and disable feature allows the internal logic to control power up and down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figures 2–67 through 2–69.

#### **Enhanced and Fast PLLs**

Stratix II GX devices provide robust clock management and synthesis using up to four enhanced PLLs and four fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock frequency synthesis. With features such as clock switchover, spread spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II GX device's enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix II GX high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

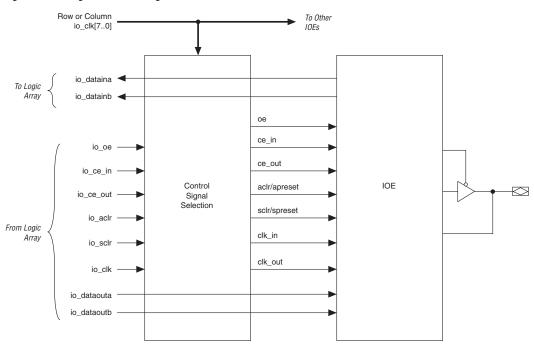

There are 32 control and data signals that feed each row or column I/O block. These control and data signals are driven from the logic array. The row or column IOE clocks, io\_clk [7..0], provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from global or regional clocks. Refer to "PLLs and Clock Networks" on page 2–89 for more information.

Figure 2–79 illustrates the signal paths through the I/O block.

Figure 2-79. Signal Path Through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/apreset, sclr/spreset, clk\_in, and clk\_out. Figure 2–80 illustrates the control signal selection.

- Differential SSTL-2 class I and II

- 1.2-V HSTL class I and II

- 1.5-V HSTL class I and II

- 1.8-V HSTL class I and II

- SSTL-2 class I and II

- SSTL-18 class I and II

Table 2–33 describes the I/O standards supported by Stratix II GX devices.

| Table 2–33. Stratix II GX S                |                    | Input Reference                 | Output Supply                    | Board Termination              |  |

|--------------------------------------------|--------------------|---------------------------------|----------------------------------|--------------------------------|--|

| I/O Standard                               | Туре               | Voltage (V <sub>REF</sub> ) (V) | Voltage (V <sub>CCIO</sub> ) (V) | Voltage (V <sub>TT</sub> ) (V) |  |

| LVTTL                                      | Single-ended       | _                               | 3.3                              | _                              |  |

| LVCMOS                                     | Single-ended       | _                               | 3.3                              | _                              |  |

| 2.5 V                                      | Single-ended       | _                               | 2.5                              | _                              |  |

| 1.8 V                                      | Single-ended       | _                               | 1.8                              | _                              |  |

| 1.5-V LVCMOS                               | Single-ended       | _                               | 1.5                              | _                              |  |

| 3.3-V PCI                                  | Single-ended       | _                               | 3.3                              | _                              |  |

| 3.3-V PCI-X mode 1                         | Single-ended       | _                               | 3.3                              | _                              |  |

| LVDS                                       | Differential       | _                               | 2.5 (3)                          | _                              |  |

| LVPECL (1)                                 | Differential       | _                               | 3.3                              | _                              |  |

| HyperTransport technology                  | Differential       | _                               | 2.5 (3)                          | _                              |  |

| Differential 1.5-V HSTL class I and II (2) | Differential       | 0.75                            | 1.5                              | 0.75                           |  |

| Differential 1.8-V HSTL class I and II (2) | Differential       | 0.90                            | 1.8                              | 0.90                           |  |

| Differential SSTL-18 class I and II (2)    | Differential       | 0.90                            | 1.8                              | 0.90                           |  |

| Differential SSTL-2 class I and II (2)     | Differential       | 1.25                            | 2.5                              | 1.25                           |  |

| 1.2-V HSTL(4)                              | Voltage-referenced | 0.6                             | 1.2                              | 0.6                            |  |

| 1.5-V HSTL class I and II                  | Voltage-referenced | 0.75                            | 1.5                              | 0.75                           |  |

| 1.8-V HSTL class I and II                  | Voltage-referenced | 0.9                             | 1.8                              | 0.9                            |  |

| SSTL-18 class I and II                     | Voltage-referenced | 0.90                            | 1.8                              | 0.90                           |  |

| Table 2–42. Document Revision History (Part 2 of 6) |                                                                                                                                                     |                                                                                                                                                          |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Date and<br>Document<br>Version                     | Changes Made                                                                                                                                        | Summary of Changes                                                                                                                                       |  |  |  |  |  |  |  |

| February 2007<br>v2.0                               | Added Chapter 02 "Stratix II GX Transceivers" to the beginning of Chapter 03 "Stratix II GX Architecture".  • Changed chapter number to Chapter 02. | Combined Chapter 02 "Stratix II GX<br>Transceivers" and Chapter 03<br>"Stratix II GX Architecture" in the new<br>Chapter 02 "Stratix II GX Architecture" |  |  |  |  |  |  |  |

|                                                     | Added the "Document Revision History" section to this chapter.                                                                                      |                                                                                                                                                          |  |  |  |  |  |  |  |

|                                                     | Moved the "Stratix II GX Transceiver Clocking" section to after the "Receiver Path" section.                                                        |                                                                                                                                                          |  |  |  |  |  |  |  |

The nIO\_PULLUP pin is a dedicated input that chooses whether the internal pull-up resistors on the user I/O pins and dual-purpose configuration I/O pins (nCSO, ASDO, DATA [7..0], nWS, nRS, RDYnBSY, nCS, CS, RUnLU, PGM [2..0], CLKUSR, INIT\_DONE, DEV\_OE, DEV\_CLR) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-up resistors, while a logic low turns them on.

Stratix II GX devices also offer a new power supply, V<sub>CCPD</sub>, which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins. V<sub>CCPD</sub> applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the following configuration pins: nCONFIG, DCLK (when used as an input), nio Pullup, Data [7..0], Runlu, nce, nws, nrs, cs, ncs, and CLKUSR. The VCCSEL pin allows the V<sub>CCIO</sub> setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$  voltage, you do not have to take the  $V_{II}$  and  $V_{IH}$  levels driven to the configuration inputs into consideration. The configuration input pins, nCONFIG, DCLK (when used as an input), nIO PULLUP, RUNLU, nCE, nWS, nRS, CS, nCS, and CLKUSR, have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The V<sub>CCSEL</sub> input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD}$ , while the 1.8-V/1.5-V input buffer is powered by  $V_{CCIO}$ .

$V_{CCSEL}$  is sampled during power-up. Therefore, the  $V_{CCSEL}$  setting cannot change on-the-fly or during a reconfiguration. The  $V_{CCSEL}$  input buffer is powered by  $V_{CCINT}$  and must be hardwired to  $V_{CCPD}$  or ground. A logic high  $V_{CCSEL}$  connection selects the 1.8-V/1.5-V input buffer; a logic low selects the 3.3-V/2.5-V input buffer.  $V_{CCSEL}$  should be set to comply with the logic levels driven out of the configuration device or the MAX II microprocessor.

If the design must support configuration input voltages of 3.3 V/2.5 V, set  $V_{CCSEL}$  to a logic low. You can set the  $V_{CCIO}$  voltage of the I/O bank that contains the configuration inputs to any supported voltage. If the design must support configuration input voltages of 1.8 V/1.5 V, set  $V_{CCSEL}$  to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 3–4. Stratix II GX Configuration Features (Part 2 of 2) |                                                  |                 |               |                          |  |  |  |

|---------------------------------------------------------------|--------------------------------------------------|-----------------|---------------|--------------------------|--|--|--|

| Configuration<br>Scheme                                       | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |  |  |  |

|                                                               | Download cable (4)                               |                 |               |                          |  |  |  |

| JTAG                                                          | MAX II device or microprocessor and flash device |                 |               |                          |  |  |  |

#### Notes for Table 3-4:

- (1) In these modes, the host system must send a DCLK that is  $4\times$  the data rate.

- (2) The enhanced configuration device decompression feature is available, while the Stratix II GX decompression feature is not available.

- (3) Only remote update mode is supported when using the AS configuration scheme. Local update mode is not supported.

- (4) The supported download cables include the Altera USB-Blaster universal serial bus (USB) port download cable, MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and the ByteBlasterMV parallel port download cable.

### **Device Security Using Configuration Bitstream Encryption**

Stratix II and Stratix II GX FPGAs are the industry's first FPGAs with the ability to decrypt a configuration bitstream using the AES algorithm. When using the design security feature, a 128-bit security key is stored in the Stratix II GX FPGA. To successfully configure a Stratix II GX FPGA that has the design security feature enabled, the device must be configured with a configuration file that was encrypted using the same 128-bit security key. The security key can be stored in non-volatile memory inside the Stratix II GX device. This nonvolatile memory does not require any external devices, such as a battery back up, for storage.

An encrypted configuration file is the same size as a non-encrypted configuration file. When using a serial configuration scheme such as passive serial (PS) or active serial (AS), configuration time is the same whether or not the design security feature is enabled. If the fast passive parallel (FPP) scheme is used with the design security or decompression feature, a  $4\times$  DCLK is required. This results in a slower configuration time when compared to the configuration time of an FPGA that has neither the design security nor the decompression feature enabled. For more information about this feature, contact an Altera sales representative.

# **Device Configuration Data Decompression**

Stratix II GX FPGAs support decompression of configuration data, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other

generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms.

For more information on the JRunner software driver, refer to the *AN 414: An Embedded Solution for PLD JTAG Configuration* and the source files on the Altera web site (www.altera.com).

### **Programming Serial Configuration Devices with SRunner**

A serial configuration device can be programmed in-system by an external microprocessor using SRunner. SRunner is a software driver developed for embedded serial configuration device programming that can be easily customized to fit into different embedded systems. SRunner reads a Raw Programming Data file (.rpd) and writes to serial configuration devices. The serial configuration device programming time using SRunner is comparable to the programming time when using the Quartus II software.

For more information about SRunner, refer to the *AN 418 SRunner: An Embedded Solution for Serial Configuration Device Programming* and the source code on the Altera web site.

For more information on programming serial configuration devices, refer to the *Serial Configuration Devices* (EPCS1, EPCS4, EPCS64, and EPCS128) Data Sheet in the Configuration Handbook.

## **Configuring Stratix II FPGAs with the MicroBlaster Driver**

The MicroBlaster software driver supports an RBF programming input file and is ideal for embedded FPP or PS configuration. The source code is developed for the Windows NT operating system, although it can be customized to run on other operating systems.

For more information on the MicroBlaster software driver, refer to the Configuring the MicroBlaster Fast Passive Parallel Software Driver White Paper or the Configuring the MicroBlaster Passive Serial Software Driver White Paper on the Altera web site.

## **PLL Reconfiguration**

The phase-locked loops (PLLs) in the Stratix II GX device family support reconfiguration of their multiply, divide, VCO-phase selection, and bandwidth selection settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides

| Table 4-3 | Table 4–3. Stratix II GX Device Recommended Operating Conditions (Part 2 of 2)       Note (1) |                    |     |     |   |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------|--------------------|-----|-----|---|--|--|--|

| Symbol    | Parameter Conditions Minimum Maximum Un                                                       |                    |     |     |   |  |  |  |

| $T_J$     | Operating junction temperature                                                                | For commercial use | 0   | 85  | С |  |  |  |

|           |                                                                                               | For industrial use | -40 | 100 | С |  |  |  |

#### Notes to Table 4-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 4–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 µs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, the Stratix II GX device will not configure successfully. If the system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

#### **Transceiver Block Characteristics**

Tables 4–4 through 4–6 contain transceiver block specifications.

| Table 4–4. Stratix | Table 4–4. Stratix II GX Transceiver Block Absolute Maximum Ratings         Note (1) |                           |         |         |       |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------|---------------------------|---------|---------|-------|--|--|--|--|--|

| Symbol             | Parameter                                                                            | Conditions                | Minimum | Maximum | Units |  |  |  |  |  |

| V <sub>CCA</sub>   | Transceiver block supply voltage                                                     | Commercial and industrial | -0.5    | 4.6     | V     |  |  |  |  |  |

| V <sub>CCP</sub>   | Transceiver block supply voltage                                                     | Commercial and industrial | -0.5    | 1.8     | V     |  |  |  |  |  |

| V <sub>CCR</sub>   | Transceiver block supply Voltage                                                     | Commercial and industrial | -0.5    | 1.8     | V     |  |  |  |  |  |

| V <sub>CCT</sub>   | Transceiver block supply voltage                                                     | Commercial and industrial | -0.5    | 1.8     | V     |  |  |  |  |  |

| V <sub>CCT_B</sub> | Transceiver block supply voltage                                                     | Commercial and industrial | -0.5    | 1.8     | V     |  |  |  |  |  |

| V <sub>CCL</sub>   | Transceiver block supply voltage                                                     | Commercial and industrial | -0.5    | 1.8     | V     |  |  |  |  |  |

| V <sub>CCH_B</sub> | Transceiver block supply voltage                                                     | Commercial and industrial | -0.5    | 2.4     | V     |  |  |  |  |  |

#### Note to Table 4-4:

(1) The device can tolerate prolonged operation at this absolute maximum, as long as the maximum specification is not violated.

| Table 4-            | -22. PCS Late                            | ency (Pa        | rt 1 of 3)           | Note (1)        |                   |                              |                           |               |                                   |                  |                |  |

|---------------------|------------------------------------------|-----------------|----------------------|-----------------|-------------------|------------------------------|---------------------------|---------------|-----------------------------------|------------------|----------------|--|

|                     |                                          |                 | Receiver PCS Latency |                 |                   |                              |                           |               |                                   |                  |                |  |

| Functional<br>Mode  | Configuration                            | Word<br>Aligner | Deskew<br>FIFO       | Rate<br>Matcher | 8B/10B<br>Decoder | Receiver<br>State<br>Machine | Byte<br>De-<br>serializer | Byte<br>Order | Receiver<br>Phase<br>Comp<br>FIFO | Receiver<br>PIPE | <b>Sum</b> (2) |  |

| XAUI                |                                          | 2-2.5           | 2-2.5                | 5.5-6.5         | 0.5               | 1                            | 1                         | 1             | 1-2                               | -                | 14-17          |  |

| PIPE                | ×1, ×4, ×8<br>8-bit<br>channel<br>width  | 4-5             | -                    | 11-13           | 1                 | -                            | 1                         | 1             | 2-3                               | 1                | 21-25          |  |

| 1112                | ×1, ×4, ×8<br>16-bit<br>channel<br>width | 2-2.5           | -                    | 5.5-6.5         | 0.5               | -                            | 1                         | 1             | 2-3                               | 1                | 13-16          |  |

| GIGE                |                                          | 4-5             | -                    | 11-13           | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 19-23          |  |

|                     | OC-12                                    | 6-7             | -                    | -               | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 10-12          |  |

| SONET/<br>SDH       | OC-48                                    | 3-3.5           | -                    | -               | 0.5               | -                            | 1                         | 1-2           | 1-2                               | -                | 7-9            |  |

|                     | OC-96                                    | 2-2.5           | -                    | -               | 0.5               | -                            | 1                         | 1             | 1-2                               | -                | 6-7            |  |

| (OIF)<br>CEI<br>PHY |                                          | 2.5             | -                    | -               | 0.5               | -                            | 1                         | 1             | 1-2                               | -                | 6-7            |  |

| CPRI                | 614 Mbps,<br>1.228 Gbps                  | 4-5             | -                    | -               | 1                 | -                            | 1                         | 1             | 1                                 | -                | 8-9            |  |

|                     | 2.456 Gbps                               | 4-5             | -                    | -               | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 8-10           |  |

| Serial<br>RapidIO   | 1.25 Gbps,<br>2.5 Gbps,<br>3.125 Gbps    | 2-2.5           | -                    | -               | 0.5               | -                            | 1                         | 1             | 1-2                               | -                | 6-7            |  |

| SDI                 | HD<br>10-bit<br>channel<br>width         | 5               | -                    | -               | 1                 | -                            | 1                         | 1             | 1-2                               | -                | 9-10           |  |

|                     | HD, 3G<br>20-bit<br>channel<br>width     | 2.5             | -                    | -               | 0.5               | -                            | 1                         | 1             | 1-2                               | -                | 6-7            |  |

## **Bus Hold Specifications**

Table 4–48 shows the Stratix II GX device family bus hold specifications.

| Table 4–48. Bus Hold Parameters |                                                |       |      |     |       |                   |       |       |      |       |      |      |

|---------------------------------|------------------------------------------------|-------|------|-----|-------|-------------------|-------|-------|------|-------|------|------|

|                                 |                                                |       |      |     |       | V <sub>CCIO</sub> | Level |       |      |       |      |      |

| Parameter                       | Conditions                                     | 1.2 V |      | 1.  | 1.5 V |                   | 8 V   | 2.5 V |      | 3.3 V |      | Unit |

|                                 |                                                | Min   | Max  | Min | Max   | Min               | Max   | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current    | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5  |      | 25  |       | 30                |       | 50    |      | 70    |      | μΑ   |

| High sustaining current         | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5 |      | -25 |       | -30               |       | -50   |      | -70   |      | μΑ   |

| Low<br>overdrive<br>current     | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | 120  |     | 160   |                   | 200   |       | 300  |       | 500  | μΑ   |

| High overdrive current          | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | -120 |     | -160  |                   | -200  |       | -300 |       | -500 | μА   |

| Bus-hold<br>trip point          |                                                | 0.45  | 0.95 | 0.5 | 1.0   | 0.68              | 1.07  | 0.7   | 1.7  | 0.8   | 2.0  | ٧    |

# **On-Chip Termination Specifications**

Tables 4–49 and 4–50 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 4-4                      | Table 4–49. On-Chip Termination Specification for Top and Bottom I/O Banks (Part 1 of 2)         Notes (1), (2) |                                |                   |                      |      |  |  |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|----------------------|------|--|--|--|--|--|

|                                |                                                                                                                 |                                | Resist            | Resistance Tolerance |      |  |  |  |  |  |

| Symbol                         | Description                                                                                                     | Conditions                     | Commercial<br>Max | Industrial<br>Max    | Unit |  |  |  |  |  |

| 25-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (25- $\Omega$ setting)                                             | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                | ±10                  | %    |  |  |  |  |  |

|                                | Internal series termination without calibration (25- $\Omega$ setting)                                          | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30               | ±30                  | %    |  |  |  |  |  |

| 50-ΩR <sub>S</sub><br>3.3/2.5  | Internal series termination with calibration (50-Ω setting)                                                     | V <sub>CCIO</sub> = 3.3/2.5 V  | ±5                | ±10                  | %    |  |  |  |  |  |

|                                | Internal series termination without calibration (50- $\Omega$ setting)                                          | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30               | ± 30                 | %    |  |  |  |  |  |

|                                   |                                                                        |                                  | Resista           | nce Tolerand      | ce   |

|-----------------------------------|------------------------------------------------------------------------|----------------------------------|-------------------|-------------------|------|

| Symbol                            | Description                                                            | Conditions                       | Commercial<br>Max | Industrial<br>Max | Unit |

| 25-ΩR <sub>S</sub><br>3.3/2.5     | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 3.3/2.5V$            | ±30               | ±30               | %    |

| 50-ΩR <sub>S</sub><br>3.3/2.5/1.8 | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5/1.8V | ±30               | ±30               | %    |

| 50-ΩR <sub>S</sub> 1.5            | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5V         | ±36               | ±36               | %    |

| R <sub>D</sub>                    | Internal differential termination for LVDS (100- $\Omega$ setting)     | V <sub>CCIO</sub> = 2.5 V        | ±20               | ±25               | %    |

Note to Table 4-50:

(1) On-chip parallel termination with calibration is only supported for input pins.

# **Pin Capacitance**

Table 4–51 shows the Stratix II GX device family pin capacitance.

| Table 4-51.        | Table 4–51. Stratix II GX Device Capacitance   Note (1)                                                              |         |      |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                            | Typical | Unit |  |  |  |  |  |  |

| C <sub>IOTB</sub>  | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                           | 5.0     | pF   |  |  |  |  |  |  |

| C <sub>IOL</sub>   | Input capacitance on I/O pins in I/O banks 1 and 2, including high-speed differential receiver and transmitter pins. | 6.1     | pF   |  |  |  |  |  |  |

| C <sub>CLKTB</sub> | Input capacitance on top/bottom clock input pins: $CLK[47]$ and $CLK[1215]$ .                                        | 6.0     | pF   |  |  |  |  |  |  |

| C <sub>CLKL</sub>  | Input capacitance on left clock inputs: CLK0 and CLK2.                                                               | 6.1     | pF   |  |  |  |  |  |  |

| C <sub>CLKL+</sub> | Input capacitance on left clock inputs: CLK1 and CLK3.                                                               | 3.3     | pF   |  |  |  |  |  |  |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output/feedback pins in PLL banks 11 and 12.                                 | 6.7     | pF   |  |  |  |  |  |  |

Note to Table 4-51:

(1) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within  $\pm 0.5$  pF.

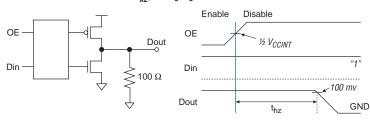

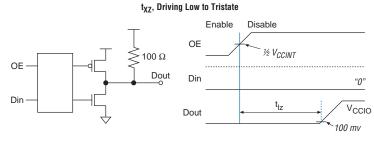

Figures 4–9 and 4–10 show the measurement setup for output disable and output enable timing.

Figure 4–9. Measurement Setup for  $t_{xz}$  Note (1)  $t_{XZ}$ , Driving High to Tristate

*Note to Figure 4–9:*

(1)  $V_{CCINT}$  is 1.12 V for this measurement.