Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1694                                                        |

| Number of Logic Elements/Cells | 33880                                                       |

| Total RAM Bits                 | 1369728                                                     |

| Number of I/O                  | 361                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 780-BBGA                                                    |

| Supplier Device Package        | 780-FBGA (29x29)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx30df780i4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

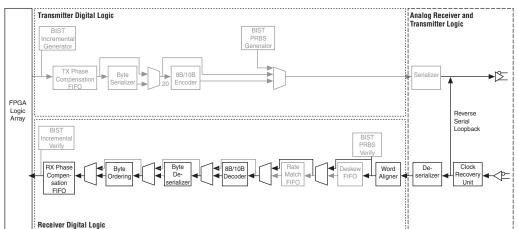

capable of built-in self test (BIST) generation and verification. The ALT2GXB megafunction in the Quartus II software provides a step-by-step menu selection to configure the transceiver.

Figure 2–1 shows the block diagram for the Stratix II GX transceiver channel. Stratix II GX transceivers provide PCS and PMA implementations for all supported protocols. The PCS portion of the transceiver consists of the word aligner, lane deskew FIFO buffer, rate matcher FIFO buffer, 8B/10B encoder and decoder, byte serializer and deserializer, byte ordering, and phase compensation FIFO buffers.

Each Stratix II GX transceiver channel is also capable of BIST generation and verification in addition to various loopback modes. The PMA portion of the transceiver consists of the serializer and deserializer, the CRU, and the high-speed differential transceiver buffers that contain pre-emphasis, programmable on-chip termination (OCT), programmable voltage output differential ( $V_{\rm OD}$ ), and equalization.

#### **Transmitter Path**

This section describes the data path through the Stratix II GX transmitter. The Stratix II GX transmitter contains the following modules:

- Transmitter PLLs

- Access to one of two PLLs

- Transmitter logic array interface

- Transmitter phase compensation FIFO buffer

- Byte serializer

- 8B/10B encoder

- Serializer (parallel-to-serial converter)

- Transmitter differential output buffer

#### Transmitter PLLs

Each transceiver block has two transmitter PLLs which receive two reference clocks to generate timing and the following clocks:

- High-speed clock used by the serializer to transmit the high-speed differential transmitter data

- Low-speed clock to load the parallel transmitter data of the serializer

The serializer uses high-speed clocks to transmit data. The serializer is also referred to as parallel in serial out (PISO). The high-speed clock is fed to the local clock generation buffer. The local clock generation buffers divide the high-speed clock on the transmitter to a desired frequency on a per-channel basis. Figure 2–3 is a block diagram of the transmitter clocks.

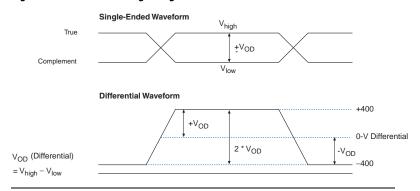

Differential signaling conventions are shown in Figure 2–9. The differential amplitude represents the value of the voltage between the true and complement signals. Peak-to-peak differential voltage is defined as 2 × (V<sub>HIGH</sub> – V<sub>LOW</sub>) = 2 × single-ended voltage swing. The common mode voltage is the average of  $V_{high}$  and  $V_{low}$

Figure 2-9. Differential Signaling

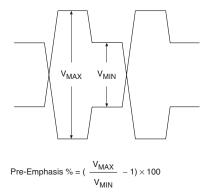

#### **Programmable Pre-Emphasis**

The programmable pre-emphasis module controls the output driver to boost the high frequency components, and compensate for losses in the transmission medium, as shown in Figure 2–10. The pre-emphasis is set statically using the ALT2GXB megafunction or dynamically through the dynamic reconfiguration controller.

Figure 2-10. Pre-Emphasis Signaling

- Lane deskew

- Rate matcher

- 8B/10B decoder

- Byte deserializer

- Byte ordering

- Receiver phase compensation FIFO buffer

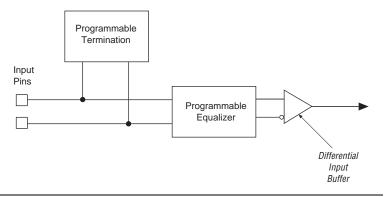

#### Receiver Input Buffer

The Stratix II GX receiver input buffer supports the 1.2-V and 1.5-V PCML I/O standard at rates up to 6.375 Gbps. The common mode voltage of the receiver input buffer is programmable between 0.85 V and 1.2 V. You must select the 0.85 V common mode voltage for AC- and DC-coupled PCML links and the 1.2 V common mode voltage for DC-coupled LVDS links.

The receiver has programmable on-chip 100-, 120-, or 150- $\Omega$  differential termination for different protocols, as shown in Figure 2–12. The receiver's internal termination can be disabled if external terminations and biasing are provided. The receiver and transmitter differential termination resistances can be set independently of each other.

Figure 2–12. Receiver Input Buffer

#### Programmable Termination

The programmable termination can be statically set in the Quartus II software. Figure 2–13 shows the setup for programmable receiver termination. The termination can be disabled if external termination is provided.

The rx syncstatus signal is not available in bit-slipping mode.

#### Channel Aligner

The channel aligner is available only in XAUI mode and aligns the signals of all four channels within a transceiver. The channel aligner follows the IEEE 802.3ae, clause 48 specification for channel bonding.

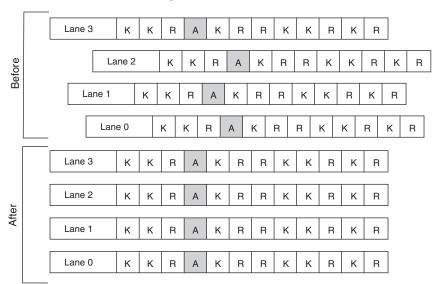

The channel aligner is a 16-word FIFO buffer with a state machine controlling the channel bonding process. The state machine looks for an /A/(K28.3/) in each channel, and aligns all the /A/ code groups in the transceiver. When four columns of /A/ (denoted by //A//) are detected, the <code>rx\_channelaligned</code> signal goes high, signifying that all the channels in the transceiver have been aligned. The reception of four consecutive misaligned /A/ code groups restarts the channel alignment sequence and sends the <code>rx\_channelaligned</code> signal low.

Figure 2–19 shows misaligned channels before the channel aligner and the aligned channels after the channel aligner.

Figure 2-19. Before and After the Channel Aligner

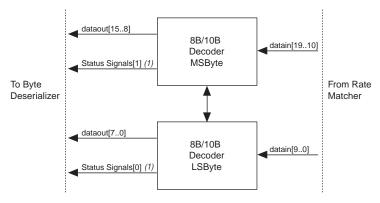

Figure 2-21. 8B/10B Decoder

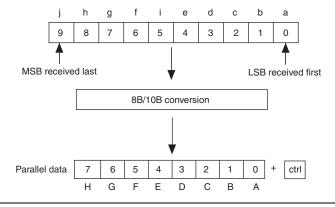

The 8B/10B decoder in single-width mode translates the 10-bit encoded data into the 8-bit equivalent data or control code. The 10-bit code received must be from the supported Dx.y or Kx.y list with the proper disparity or error flags asserted. All 8B/10B control signals, such as disparity error or control detect, are pipelined with the data and edge-aligned with the data. Figure 2–22 shows how the 10-bit symbol is decoded in the 8-bit data + 1-bit control indicator.

Figure 2-22. 8B/10B Decoder Conversion

The 8B/10B decoder in double-width mode translates the 20-bit (2  $\times$  10-bits) encoded code into the 16-bit (2  $\times$  8-bits) equivalent data or control code. The 20-bit upper and lower symbols received must be from the supported Dx.y or Kx.y list with the proper disparity or error flags

Figure 2–26 shows the data path in reverse serial loopback mode.

Figure 2–26. Stratix II GX Block in Reverse Serial Loopback Mode

#### Reverse Serial Pre-CDR Loopback

The reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received since the signal goes through the output buffer and the VOD is changed to the VOD setting level. The pre-emphasis settings have no effect.

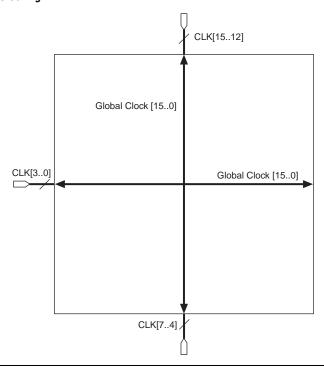

generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–61 shows the 12 dedicated CLK pins driving global clock networks.

Figure 2-61. Global Clocking

#### Regional Clock Network

There are eight regional clock networks (RCLK[7..0]) in each quadrant of the Stratix II GX device that are driven by the dedicated CLK[15..12] and CLK[7..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–62.

| Table 2–27. Global and Regional Clock Connections from Left Side Clock Pins and Fast PLL Outputs (Part 3 of 3) |               |          |          |          |       |       |       |       |          |          |          |          |

|----------------------------------------------------------------------------------------------------------------|---------------|----------|----------|----------|-------|-------|-------|-------|----------|----------|----------|----------|

| Left Side Global and Regional<br>Clock Network Connectivity                                                    | CLKO          | CLK1     | CLK2     | ССКЗ     | RCLKO | RCLK1 | RCLK2 | RCLK3 | RCLK4    | RCLK5    | RCLK6    | RCLK7    |

| PLL 8 outputs                                                                                                  | PLL 8 outputs |          |          |          |       |       |       |       |          |          |          |          |

| c0                                                                                                             |               |          | <b>\</b> | <b>\</b> |       |       |       |       | <b>\</b> |          | <b>✓</b> |          |

| c1                                                                                                             |               |          | <b>✓</b> | <b>✓</b> |       |       |       |       |          | <b>✓</b> |          | <b>✓</b> |

| c2                                                                                                             | <b>✓</b>      | <b>✓</b> |          |          |       |       |       |       | <b>✓</b> |          | <b>✓</b> |          |

|                                                                                                                |               |          |          |          |       |       |       |       |          |          |          |          |

memory, and transmit this compressed bitstream to Stratix II GX FPGAs. During configuration, the Stratix II GX FPGA decompresses the bitstream in real time and programs its SRAM cells. Stratix II GX FPGAs support decompression in the FPP (when using a MAX II device or microprocessor and flash memory), AS, and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.

#### **Remote System Upgrades**

Shortened design cycles, evolving standards, and system deployments in remote locations are difficult challenges faced by system designers. Stratix II GX devices can help effectively deal with these challenges with their inherent re programmability and dedicated circuitry to perform remote system updates. Remote system updates help deliver feature enhancements and bug fixes without costly recalls, reducing time to market, and extending product life.

Stratix II GX FPGAs feature dedicated remote system upgrade circuitry to facilitate remote system updates. Soft logic (Nios processor or user logic) implemented in the Stratix II GX device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, recovers from any error condition by reverting back to a safe configuration image, and provides error status information. This dedicated remote system upgrade circuitry avoids system downtime and is the critical component for successful remote system upgrades.

Remote system configuration is supported in the following Stratix II GX configuration schemes: FPP, AS, PS, and PPA. Remote system configuration can also be implemented in conjunction with Stratix II GX features such as real-time decompression of configuration data and design security using AES for secure and efficient field upgrades.

Refer to the *Remote System Upgrades with Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information about remote configuration in Stratix II GX devices.

# Configuring Stratix II GX FPGAs with JRunner

The JRunner<sup>TM</sup> software driver configures Altera FPGAs, including Stratix II GX FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf)

| Table 4-                           | Table 4–15. Typical Pre-Emphasis (First Post-Tap), Note (1) (Part 2 of 2) |                            |     |     |      |      |      |      |      |      |      |      |

|------------------------------------|---------------------------------------------------------------------------|----------------------------|-----|-----|------|------|------|------|------|------|------|------|

| V <sub>CCH</sub> TX<br>= 1.5 V     | First Post Tap Pre-Emphasis Level                                         |                            |     |     |      |      |      |      |      |      |      |      |

| V <sub>OD</sub><br>Setting<br>(mV) | 1                                                                         | 1 2 3 4 5 6 7 8 9 10 11 12 |     |     |      |      |      |      |      |      |      |      |

| 600                                |                                                                           | 33%                        | 53% | 80% | 115% | 157% | 195% | 294% | 386% |      |      |      |

| 900                                |                                                                           | 19%                        | 28% | 38% | 56%  | 70%  | 86%  | 113% | 133% | 168% | 196% | 242% |

| 1200                               |                                                                           |                            | 17% | 22% | 31%  | 40%  | 52%  | 62%  | 75%  | 86%  | 96%  | 112% |

Note to Table 4-15:

| Table 4–16. Typical Pre-Emphasis (First Post-Tap), Note (1) |                                   |     |      |     |      |         |         |      |      |      |      |      |

|-------------------------------------------------------------|-----------------------------------|-----|------|-----|------|---------|---------|------|------|------|------|------|

| V <sub>CCH</sub> TX<br>= 1.2 V                              | First Post Tap Pre-Emphasis Level |     |      |     |      |         |         |      |      |      |      |      |

| V <sub>OD</sub><br>Setting<br>(mV)                          | 1                                 | 2   | 3    | 4   | 5    | 6       | 7       | 8    | 9    | 10   | 11   | 12   |

|                                                             |                                   |     |      |     |      | TX Term | = 100 Ω | 2    |      |      |      |      |

| 320                                                         | 24%                               | 61% | 114% |     |      |         |         |      |      |      |      |      |

| 480                                                         |                                   | 31% | 55%  | 86% | 121% | 170%    | 232%    | 333% |      |      |      |      |

| 640                                                         |                                   | 20% | 35%  | 54% | 72%  | 95%     | 124%    | 157% | 195% | 233% | 307% | 373% |

| 800                                                         |                                   |     | 23%  | 36% | 49%  | 64%     | 81%     | 97%  | 117% | 140% | 161% | 195% |

| 960                                                         |                                   |     | 18%  | 25% | 35%  | 44%     | 57%     | 69%  | 82%  | 94%  | 108% | 127% |

*Note to Table 4–16:*

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 6.375 Gbps. Specification is for measurement at the package ball.

<sup>(1)</sup> Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

## **DC Electrical Characteristics**

Table 4–23 shows the Stratix II GX device family DC electrical characteristics.

| Table 4-            | Table 4–23. Stratix II GX Device DC Operating Conditions (Part 1 of 2)    Note (1) |                                                  |           |         |         |         |      |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-----------|---------|---------|---------|------|--|--|--|--|

| Symbol              | Parameter                                                                          | Conditions                                       | Device    | Minimum | Typical | Maximum | Unit |  |  |  |  |

| I <sub>I</sub>      | Input pin leakage current                                                          | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 V (2) | All       | -10     |         | 10      | μА   |  |  |  |  |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current                                                 | $V_O = V_{CCIOmax}$ to $0 V (2)$                 | All       | -10     |         | 10      | μА   |  |  |  |  |

| I <sub>CCINT0</sub> | V <sub>CCINT</sub> supply current                                                  | V <sub>I</sub> = ground, no                      | EP2SGX30  |         | 0.30    | (3)     | Α    |  |  |  |  |

|                     | (standby)                                                                          | load, no toggling                                | EP2SGX60  |         | 0.50    | (3)     | Α    |  |  |  |  |

|                     |                                                                                    | inputs<br>T <sub>J</sub> = 25 °C                 | EP2SGX90  |         | 0.62    | (3)     | Α    |  |  |  |  |

|                     |                                                                                    |                                                  | EP2SGX130 |         | 0.82    | (3)     | Α    |  |  |  |  |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current                                                   | V <sub>I</sub> = ground, no                      | EP2SGX30  |         | 2.7     | (3)     | mA   |  |  |  |  |

|                     | (standby)                                                                          | load, no toggling inputs                         | EP2SGX60  |         | 3.6     | (3)     | mA   |  |  |  |  |

|                     |                                                                                    | $T_J = 25 ^{\circ}\text{C},$                     | EP2SGX90  |         | 4.3     | (3)     | mA   |  |  |  |  |

|                     |                                                                                    | $V_{CCPD} = 3.3V$                                | EP2SGX130 |         | 5.4     | (3)     | mA   |  |  |  |  |

| I <sub>CCI00</sub>  | V <sub>CCIO</sub> supply current                                                   | V <sub>I</sub> = ground, no                      | EP2SGX30  |         | 4.0     | (3)     | mA   |  |  |  |  |

|                     | (standby)                                                                          | load, no toggling                                | EP2SGX60  |         | 4.0     | (3)     | mA   |  |  |  |  |

|                     |                                                                                    | inputs $T_{.1} = 25 ^{\circ}\text{C}$            | EP2SGX90  |         | 4.0     | (3)     | mA   |  |  |  |  |

|                     |                                                                                    |                                                  | EP2SGX130 |         | 4.0     | (3)     | mA   |  |  |  |  |

| Table 4-3            | Table 4–35. SSTL-18 Class I Specifications |                                 |                          |           |                          |      |  |  |  |  |  |

|----------------------|--------------------------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|--|--|--|--|--|

| Symbol               | Parameter                                  | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>    | Output supply voltage                      |                                 | 1.71                     | 1.8       | 1.89                     | V    |  |  |  |  |  |

| V <sub>REF</sub>     | Reference voltage                          |                                 | 0.855                    | 0.9       | 0.945                    | ٧    |  |  |  |  |  |

| V <sub>TT</sub>      | Termination voltage                        |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |  |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage                |                                 | V <sub>REF</sub> + 0.125 |           |                          | ٧    |  |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage                 |                                 |                          |           | V <sub>REF</sub> - 0.125 | ٧    |  |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage                |                                 | V <sub>REF</sub> + 0.25  |           |                          | ٧    |  |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage                 |                                 |                          |           | V <sub>REF</sub> - 0.25  | ٧    |  |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                  | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  |           |                          | ٧    |  |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                   | I <sub>OL</sub> = 6.7 mA (1)    |                          |           | V <sub>TT</sub> – 0.475  | ٧    |  |  |  |  |  |

#### Note to Table 4-35:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 4-             | Table 4–36. SSTL-18 Class II Specifications |                                  |                          |           |                          |      |  |  |  |  |  |  |

|----------------------|---------------------------------------------|----------------------------------|--------------------------|-----------|--------------------------|------|--|--|--|--|--|--|

| Symbol               | Parameter                                   | Conditions                       | Minimum                  | Typical   | Maximum                  | Unit |  |  |  |  |  |  |

| $V_{\text{CCIO}}$    | Output supply voltage                       |                                  | 1.71                     | 1.8       | 1.89                     | V    |  |  |  |  |  |  |

| $V_{REF}$            | Reference voltage                           |                                  | 0.855                    | 0.9       | 0.945                    | V    |  |  |  |  |  |  |

| $V_{TT}$             | Termination voltage                         |                                  | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V    |  |  |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage                 |                                  | V <sub>REF</sub> + 0.125 |           |                          | V    |  |  |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage                  |                                  |                          |           | V <sub>REF</sub> - 0.125 | V    |  |  |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage                 |                                  | V <sub>REF</sub> + 0.25  |           |                          | V    |  |  |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage                  |                                  |                          |           | V <sub>REF</sub> - 0.25  | V    |  |  |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                   | $I_{OH} = -13.4 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.28 |           |                          | V    |  |  |  |  |  |  |

| $V_{OL}$             | Low-level output voltage                    | I <sub>OL</sub> = 13.4 mA (1)    |                          |           | 0.28                     | V    |  |  |  |  |  |  |

#### Note to Table 4-36:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

- 3. Simulate the output driver of choice into the actual PCB trace and load, using the appropriate IBIS model or capacitance value to represent the load.

- 4. Record the time to  $V_{MEAS}$ .

- 5. Compare the results of steps 2 and 4. The increase or decrease in delay should be added to or subtracted from the I/O Standard Output Adder delays to yield the actual worst-case propagation delay (clock-to-output) of the PCB trace.

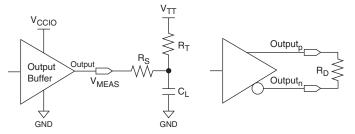

The Quartus II software reports the timing with the conditions shown in Table 4–53 using the above equation. Figure 4–8 shows the model of the circuit that is represented by the output timing of the Quartus II software.

Figure 4–8. Output Delay Timing Reporting Setup Modeled by Quartus II

Notes to Figure 4-8:

- (1) Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2) V<sub>CCPD</sub> is 3.085 V unless otherwise specified.

- (3)  $V_{CCINT}$  is 1.12 V unless otherwise specified.

| Table 4–53. Output Timing Measurement Methodology for Output Pins (Part 1 of 2) Notes (1), (2), (3) |                           |                         |               |                       |                     |                     |                       |  |  |

|-----------------------------------------------------------------------------------------------------|---------------------------|-------------------------|---------------|-----------------------|---------------------|---------------------|-----------------------|--|--|

| I/O Standard                                                                                        |                           | Loading and Termination |               |                       |                     |                     |                       |  |  |

| ·                                                                                                   | <b>R</b> <sub>S</sub> (Ω) | $R_D(\Omega)$           | $R_T(\Omega)$ | V <sub>CCIO</sub> (V) | V <sub>TT</sub> (V) | C <sub>L</sub> (pF) | V <sub>MEAS</sub> (V) |  |  |

| LVTTL (4)                                                                                           |                           |                         |               | 3.135                 |                     | 0                   | 1.5675                |  |  |

| LVCMOS (4)                                                                                          |                           |                         |               | 3.135                 |                     | 0                   | 1.5675                |  |  |

| 2.5 V (4)                                                                                           |                           |                         |               | 2.375                 |                     | 0                   | 1.1875                |  |  |

| 1.8 V (4)                                                                                           |                           |                         |               | 1.710                 |                     | 0                   | 0.855                 |  |  |

| 1.5 V (4)                                                                                           |                           |                         |               | 1.425                 |                     | 0                   | 0.7125                |  |  |

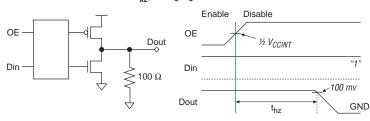

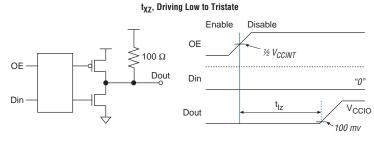

Figures 4–9 and 4–10 show the measurement setup for output disable and output enable timing.

Figure 4–9. Measurement Setup for  $t_{xz}$  Note (1)  $t_{XZ}$ , Driving High to Tristate

*Note to Figure 4–9:*

(1)  $V_{CCINT}$  is 1.12 V for this measurement.

| Table 4–86. Strati | Table 4–86. Stratix II GX I/O Output Delay for Column Pins (Part 7 of 7) |                  |                                          |                       |                       |                   |                   |      |  |  |  |  |

|--------------------|--------------------------------------------------------------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|--|--|--|--|

| I/O Standard       | Drive<br>Strength                                                        | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |  |  |  |  |

| 1.5-V differential | 4 mA                                                                     | t <sub>OP</sub>  | 956                                      | 1607                  | 1686                  | 1793              | 1942              | ps   |  |  |  |  |

| HSTL Class I (2)   |                                                                          | t <sub>DIP</sub> | 978                                      | 1673                  | 1756                  | 1867              | 2032              | ps   |  |  |  |  |

|                    | 6 mA                                                                     | t <sub>OP</sub>  | 961                                      | 1588                  | 1666                  | 1772              | 1920              | ps   |  |  |  |  |

|                    |                                                                          | t <sub>DIP</sub> | 983                                      | 1654                  | 1736                  | 1846              | 2010              | ps   |  |  |  |  |

|                    | 8 mA                                                                     | t <sub>OP</sub>  | 943                                      | 1590                  | 1668                  | 1774              | 1922              | ps   |  |  |  |  |

|                    |                                                                          | t <sub>DIP</sub> | 965                                      | 1656                  | 1738                  | 1848              | 2012              | ps   |  |  |  |  |

|                    | 10 mA                                                                    | t <sub>OP</sub>  | 943                                      | 1592                  | 1670                  | 1776              | 1924              | ps   |  |  |  |  |

|                    |                                                                          | t <sub>DIP</sub> | 965                                      | 1658                  | 1740                  | 1850              | 2014              | ps   |  |  |  |  |

|                    | 12 mA                                                                    | t <sub>OP</sub>  | 937                                      | 1590                  | 1668                  | 1774              | 1922              | ps   |  |  |  |  |

|                    |                                                                          | t <sub>DIP</sub> | 959                                      | 1656                  | 1738                  | 1848              | 2012              | ps   |  |  |  |  |

| 1.5-V differential | 16 mA                                                                    | t <sub>OP</sub>  | 924                                      | 1431                  | 1501                  | 1596              | 1734              | ps   |  |  |  |  |

| HSTL Class II (2)  |                                                                          | t <sub>DIP</sub> | 946                                      | 1497                  | 1571                  | 1670              | 1824              | ps   |  |  |  |  |

|                    | 18 mA                                                                    | t <sub>OP</sub>  | 927                                      | 1439                  | 1510                  | 1605              | 1744              | ps   |  |  |  |  |

|                    |                                                                          | t <sub>DIP</sub> | 949                                      | 1505                  | 1580                  | 1679              | 1834              | ps   |  |  |  |  |

|                    | 20 mA                                                                    | t <sub>OP</sub>  | 929                                      | 1450                  | 1521                  | 1618              | 1757              | ps   |  |  |  |  |

|                    |                                                                          | t <sub>DIP</sub> | 951                                      | 1516                  | 1591                  | 1692              | 1847              | ps   |  |  |  |  |

- (1) This is the default setting in the Quartus II software.

- (1) This is the definition of the Quarter in Software.

(2) These I/O standards are only supported on DQS pins.

(3) This column refers to -3 speed grades for EP2SGX30, EP2SGX60, and EP2SGX90 devices.

(4) This column refers to -3 speed grades for EP2SGX130 devices.

| Table 4–87. Stratix II GX I/O Output Delay for Row Pins (Part 1 of 4) |                   |                  |                                          |                       |                       |                   |                   |      |  |  |  |

|-----------------------------------------------------------------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|--|--|--|

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |  |  |  |

| LVTTL                                                                 | 4 mA              | t <sub>OP</sub>  | 1328                                     | 2655                  | 2786                  | 2962              | 3189              | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 1285                                     | 2600                  | 2729                  | 2902              | 3116              | ps   |  |  |  |

|                                                                       | 8 mA              | t <sub>OP</sub>  | 1200                                     | 2113                  | 2217                  | 2357              | 2549              | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 1157                                     | 2058                  | 2160                  | 2297              | 2476              | ps   |  |  |  |

|                                                                       | 12 mA (1)         | t <sub>OP</sub>  | 1144                                     | 2081                  | 2184                  | 2321              | 2512              | ps   |  |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 1101                                     | 2026                  | 2127                  | 2261              | 2439              | ps   |  |  |  |

Table 4–87. Stratix II GX I/O Output Delay for Row Pins (Part 2 of 4)

| I/O Standard    | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|-----------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| LVCMOS          | 4 mA              | t <sub>OP</sub>  | 1200                                     | 2113                  | 2217                  | 2357              | 2549              | ps   |

|                 |                   | t <sub>DIP</sub> | 1157                                     | 2058                  | 2160                  | 2297              | 2476              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1094                                     | 1853                  | 1944                  | 2067              | 2243              | ps   |

|                 |                   | t <sub>DIP</sub> | 1051                                     | 1798                  | 1887                  | 2007              | 2170              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1061                                     | 1723                  | 1808                  | 1922              | 2089              | ps   |

|                 |                   | t <sub>DIP</sub> | 1018                                     | 1668                  | 1751                  | 1862              | 2016              | ps   |

| 2.5 V           | 4 mA              | t <sub>OP</sub>  | 1183                                     | 2091                  | 2194                  | 2332              | 2523              | ps   |

|                 |                   | t <sub>DIP</sub> | 1140                                     | 2036                  | 2137                  | 2272              | 2450              | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1080                                     | 1872                  | 1964                  | 2088              | 2265              | ps   |

|                 |                   | t <sub>DIP</sub> | 1037                                     | 1817                  | 1907                  | 2028              | 2192              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1061                                     | 1775                  | 1862                  | 1980              | 2151              | ps   |

|                 |                   | t <sub>DIP</sub> | 1018                                     | 1720                  | 1805                  | 1920              | 2078              | ps   |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1253                                     | 2954                  | 3100                  | 3296              | 3542              | ps   |

|                 |                   | t <sub>DIP</sub> | 1210                                     | 2899                  | 3043                  | 3236              | 3469              | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1242                                     | 2294                  | 2407                  | 2559              | 2763              | ps   |

|                 |                   | t <sub>DIP</sub> | 1199                                     | 2239                  | 2350                  | 2499              | 2690              | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1131                                     | 2039                  | 2140                  | 2274              | 2462              | ps   |

|                 |                   | t <sub>DIP</sub> | 1088                                     | 1984                  | 2083                  | 2214              | 2389              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1100                                     | 1942                  | 2038                  | 2166              | 2348              | ps   |

|                 |                   | t <sub>DIP</sub> | 1057                                     | 1887                  | 1981                  | 2106              | 2275              | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1213                                     | 2530                  | 2655                  | 2823              | 3041              | ps   |

|                 |                   | t <sub>DIP</sub> | 1170                                     | 2475                  | 2598                  | 2763              | 2968              | ps   |

|                 | 4 mA (1)          | t <sub>OP</sub>  | 1106                                     | 2020                  | 2120                  | 2253              | 2440              | ps   |

|                 |                   | t <sub>DIP</sub> | 1063                                     | 1965                  | 2063                  | 2193              | 2367              | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 1050                                     | 1759                  | 1846                  | 1962              | 2104              | ps   |

|                 |                   | t <sub>DIP</sub> | 1007                                     | 1704                  | 1789                  | 1902              | 2031              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 1026                                     | 1694                  | 1777                  | 1889              | 2028              | ps   |

|                 |                   | t <sub>DIP</sub> | 983                                      | 1639                  | 1720                  | 1829              | 1955              | ps   |

| SSTL-2 Class II | 16 mA (1)         | t <sub>OP</sub>  | 992                                      | 1581                  | 1659                  | 1763              | 1897              | ps   |

|                 |                   | t <sub>DIP</sub> | 949                                      | 1526                  | 1602                  | 1703              | 1824              | ps   |

| Table 4–91. Stra | tix II GX Maximun | n Output Clock Rat | e for Column Pins | (Part 2 of 3)  |      |

|------------------|-------------------|--------------------|-------------------|----------------|------|

| I/O Standard     | Drive Strength    | -3 Speed Grade     | -4 Speed Grade    | -5 Speed Grade | Unit |

| SSTL-18 Class I  | 4 mA              | 200                | 150               | 150            | MHz  |

|                  | 6 mA              | 350                | 250               | 200            | MHz  |

|                  | 8 mA              | 450                | 300               | 300            | MHz  |

|                  | 10 mA             | 500                | 400               | 400            | MHz  |

|                  | 12 mA (1)         | 700                | 550               | 400            | MHz  |

| SSTL-18 Class II | 8 mA              | 200                | 200               | 150            | MHz  |

|                  | 16 mA             | 400                | 350               | 350            | MHz  |

|                  | 18 mA             | 450                | 400               | 400            | MHz  |

|                  | 20 mA (1)         | 550                | 500               | 450            | MHz  |

| 1.8-V HSTL       | 4 mA              | 300                | 300               | 300            | MHz  |

| Class I          | 6 mA              | 500                | 450               | 450            | MHz  |

|                  | 8 mA              | 650                | 600               | 600            | MHz  |

|                  | 10 mA             | 700                | 650               | 600            | MHz  |

|                  | 12 mA (1)         | 700                | 700               | 650            | MHz  |

| 1.8-V HSTL       | 16 mA             | 500                | 500               | 450            | MHz  |

| Class II         | 18 mA             | 550                | 500               | 500            | MHz  |

|                  | 20 mA (1)         | 650                | 550               | 550            | MHz  |

| 1.5-V HSTL       | 4 mA              | 350                | 300               | 300            | MHz  |

| Class I          | 6 mA              | 500                | 500               | 450            | MHz  |

|                  | 8 mA              | 700                | 650               | 600            | MHz  |

|                  | 10 mA             | 700                | 700               | 650            | MHz  |

|                  | 12 mA (1)         | 700                | 700               | 700            | MHz  |

| 1.5-V HSTL       | 16 mA             | 600                | 600               | 550            | MHz  |

| Class II         | 18 mA             | 650                | 600               | 600            | MHz  |

|                  | 20 mA (1)         | 700                | 650               | 600            | MHz  |

| PCI              | -                 | 1000               | 790               | 670            | MHz  |

| PCI-X            | -                 | 1000               | 790               | 670            | MHz  |

| Differential     | 8 mA              | 400                | 300               | 300            | MHz  |

| SSTL-2 Class I   | 12 mA             | 400                | 400               | 350            | MHz  |

| Differential     | 16 mA             | 350                | 350               | 300            | MHz  |

| SSTL-2 Class II  | 20 mA             | 400                | 350               | 350            | MHz  |

|                  | 24 mA             | 400                | 400               | 350            | MHz  |

| Table 4–95. Stratix II GX Maximum Output Clock Rate for Row Pins (Series Termination) (Part 2 of 2) |                |                |                |                |      |  |  |  |

|-----------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|--|--|

| I/O Standard                                                                                        | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |  |  |

| SSTL-2 Class I                                                                                      | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |  |  |  |

| SSTL-2 Class II                                                                                     | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |  |  |  |

| SSTL-18 Class I                                                                                     | OCT_50_OHMS    | 590            | 400            | 350            | MHz  |  |  |  |

| 1.5-V HSTL<br>Class I                                                                               | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |  |  |  |

| 1.8-V HSTL<br>Class I                                                                               | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |  |  |  |

| Differential<br>SSTL-2 Class I                                                                      | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |  |  |  |

| Differential<br>SSTL-2 Class II                                                                     | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |  |  |  |

| Differential<br>SSTL-18 Class I                                                                     | OCT_50_OHMS    | 590            | 400            | 350            | MHz  |  |  |  |

| Differential<br>HSTL-18 Class I                                                                     | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |  |  |  |

| Differential<br>HSTL-15 Class I                                                                     | OCT_50_OHMS    | 600            | 550            | 500            |      |  |  |  |

Table 4–96 shows the maximum output clock toggle rate for Stratix II GX device series-terminated dedicated clock pins.

| Table 4–96. Stratix II GX Maximum Output Clock Rate for Dedicated Clock Pins (Series Termination) (Part 1 of 2) |                |                |                |                |      |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|--|--|--|

| I/O Standard                                                                                                    | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |  |  |  |

| LVTTL                                                                                                           | OCT_25_OHMS    | 400            | 400            | 350            | MHz  |  |  |  |  |

|                                                                                                                 | OCT_50_OHMS    | 400            | 400            | 350            | MHz  |  |  |  |  |

| LVCMOS                                                                                                          | OCT_25_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |  |

|                                                                                                                 | OCT_50_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |  |

| 2.5 V                                                                                                           | OCT_25_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |  |

|                                                                                                                 | OCT_50_OHMS    | 350            | 350            | 300            | MHz  |  |  |  |  |

| 1.8 V                                                                                                           | OCT_25_OHMS    | 700            | 550            | 450            | MHz  |  |  |  |  |

|                                                                                                                 | OCT_50_OHMS    | 700            | 550            | 450            | MHz  |  |  |  |  |

| 1.5 V                                                                                                           | OCT_50_OHMS    | 550            | 450            | 400            | MHz  |  |  |  |  |

| SSTL-2 Class I                                                                                                  | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |  |  |  |  |

| SSTL-2 Class II                                                                                                 | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |  |  |  |  |

| SSTL-18 Class I                                                                                                 | OCT_50_OHMS    | 450            | 400            | 350            | MHz  |  |  |  |  |

# **Duty Cycle Distortion**

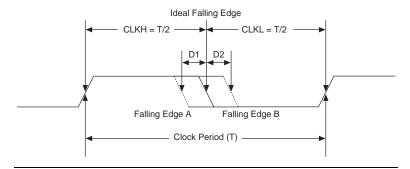

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 4–11. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (see Figure 4–11). The maximum DCD for a clock is the larger value of D1 and D2.

Figure 4-11. Duty Cycle Distortion

DCD expressed in absolution derivation, for example, D1 or D2 in Figure 4–11, is clock-period independent. DCD can also be expressed as a percentage, and the percentage number is clock-period dependent. DCD as a percentage is defined as:

(T/2 - D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

# **DCD Measurement Techniques**

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 4–12). Therefore, any DCD present on the input clock signal or caused by the clock input buffer or different input I/O standard does not transfer to the output signal.

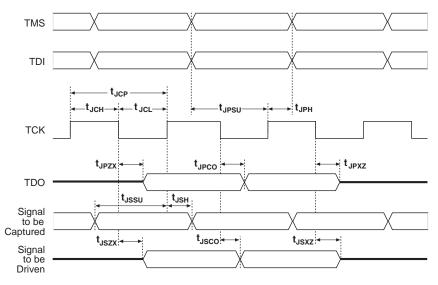

Figure 4-14. Stratix II GX JTAG Waveforms.

Table 4–117 shows the JTAG timing parameters and values for Stratix II GX devices.

| Table 4–117. Stratix II GX JTAG Timing Parameters and Values |                                                |    |     |      |  |  |

|--------------------------------------------------------------|------------------------------------------------|----|-----|------|--|--|

| Symbol                                                       | Parameter                                      |    | Max | Unit |  |  |

| $t_{\rm JCP}$                                                | TCK clock period                               | 30 |     | ns   |  |  |

| t <sub>JCH</sub>                                             | TCK clock high time                            | 12 |     | ns   |  |  |

| t <sub>JCL</sub>                                             | TCK clock low time                             | 12 |     | ns   |  |  |

| t <sub>JPSU</sub>                                            | JTAG port setup time                           | 4  |     | ns   |  |  |

| t <sub>JPH</sub>                                             | JTAG port hold time                            | 5  |     | ns   |  |  |

| t <sub>JPCO</sub>                                            | JTAG port clock to output                      |    | 9   | ns   |  |  |

| t <sub>JPZX</sub>                                            | JTAG port high impedance to valid output       |    | 9   | ns   |  |  |

| t <sub>JPXZ</sub>                                            | JTAG port valid output to high impedance       |    | 9   | ns   |  |  |

| t <sub>JSSU</sub>                                            | Capture register setup time                    | 4  |     | ns   |  |  |

| t <sub>JSH</sub>                                             | Capture register hold time                     | 5  |     | ns   |  |  |

| t <sub>JSCO</sub>                                            | Update register clock to output                |    | 12  | ns   |  |  |

| t <sub>JSZX</sub>                                            | Update register high impedance to valid output |    | 12  | ns   |  |  |

| t <sub>JSXZ</sub>                                            | Update register valid output to high impedance |    | 12  | ns   |  |  |