Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 3022                                                       |

| Number of Logic Elements/Cells | 60440                                                      |

| Total RAM Bits                 | 2544192                                                    |

| Number of I/O                  | 364                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60cf780c3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Support for multiple intellectual property megafunctions from Altera® MegaCore® functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for design security using configuration bitstream encryption

- Support for remote configuration updates

#### Transceiver block features:

- High-speed serial transceiver channels with clock data recovery (CDR) provide 600-megabits per second (Mbps) to 6.375-Gbps full-duplex transceiver operation per channel

- Devices available with 4, 8, 12, 16, or 20 high-speed serial transceiver channels providing up to 255 Gbps of serial bandwidth (full duplex)

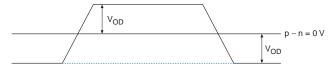

- Dynamically programmable voltage output differential (V<sub>OD</sub>) and pre-emphasis settings for improved signal integrity

- Support for CDR-based serial protocols, including PCI Express, Gigabit Ethernet, SDI, Altera's SerialLite II, XAUI, CEI-6G, CPRI, Serial RapidIO, SONET/SDH

- Dynamic reconfiguration of transceiver channels to switch between multiple protocols and data rates

- Individual transmitter and receiver channel power-down capability for reduced power consumption during non-operation

- Adaptive equalization (AEQ) capability at the receiver to compensate for changing link characteristics

- Selectable on-chip termination resistors (100, 120, or 150  $\Omega$ ) for improved signal integrity on a variety of transmission media

- Programmable transceiver-to-FPGA interface with support for 8-, 10-, 16-, 20-, 32-, and 40-bit wide data transfer

- 1.2- and 1.5-V pseudo current mode logic (PCML) for 600 Mbps to 6.375 Gbps (AC coupling)

- Receiver indicator for loss of signal (available only in PIPE mode)

- Built-in self test (BIST)

- Hot socketing for hot plug-in or hot swap and power sequencing support without the use of external devices

- Rate matcher, byte-reordering, bit-reordering, pattern detector, and word aligner support programmable patterns

- Dedicated circuitry that is compliant with PIPE, XAUI, and GIGE

- Built-in byte ordering so that a frame or packet always starts in a known byte lane

- Transmitters with two PLL inputs for each transceiver block with independent clock dividers to provide varying clock rates on each of its transmitters

#### Programmable Run Length Violation

The word aligner supports a programmable run length violation counter. Whenever the number of the continuous '0' (or '1') exceeds a user programmable value, the rx\_rlv signal goes high for a minimum pulse width of two recovered clock cycles. The maximum run values supported are shown in Table 2–7.

| Table 2–7. Maximum Run Length (UI) |                   |        |        |        |  |  |  |  |  |  |

|------------------------------------|-------------------|--------|--------|--------|--|--|--|--|--|--|

| Modo                               | PMA Serialization |        |        |        |  |  |  |  |  |  |

| Mode                               | 8 Bit             | 10 Bit | 16 Bit | 20 Bit |  |  |  |  |  |  |

| Single-Width                       | 128               | 160    | _      | _      |  |  |  |  |  |  |

| Double-Width                       | _                 | _      | 512    | 640    |  |  |  |  |  |  |

#### **Running Disparity Check**

The running disparity error rx\_disperr and running disparity value rx\_runningdisp are sent along with aligned data from the 8B/10B decoder to the FPGA. You can ignore or act on the reported running disparity value and running disparity error signals.

#### Bit-Slip Mode

The word aligner can operate in either pattern detection mode or in bit-slip mode.

The bit-slip mode provides the option to manually shift the word boundary through the FPGA. This feature is useful for:

- Longer synchronization patterns than the pattern detector can accommodate

- Scrambled data stream

- Input stream consisting of over-sampled data

This feature can be applied at 10-bit and 16-bit data widths.

The word aligner outputs a word boundary as it is received from the analog receiver after reset. You can examine the word and search its boundary in the FPGA. To do so, assert the rx\_bitslip signal. The rx\_bitslip signal should be toggled and held constant for at least two FPGA clock cycles.

For every rising edge of the rx\_bitslip signal, the current word boundary is slipped by one bit. Every time a bit is slipped, the bit received earliest is lost. If bit slipping shifts a complete round of bus width, the word boundary is back to the original boundary.

CLK[15..12] 11 5 **▲**RCLK **RCLK♠** [31..28] [27..24] Stratix II GX Transceiver **RCLK RCLK** Block [3..0] 23..20] CLK[3..0] RCLK RCLK Stratix II GX [7..4] [19..16] Transceiver Block RCLK ŔCLK [11..8] [15..12] 8 12 6 CLK[7..4]

Figure 2–31. Stratix II GX Receiver PLL Recovered Clock to Regional Clock Connection Notes (1), (2)

*Notes to Figure 2–31:*

- (1) CLK# pins are clock pins and their associated number. These are pins for global and local clocks.

- (2) RCLK# pins are regional clock pins.

The dynamic reconfiguration block can dynamically reconfigure the following PMA settings:

- Pre-emphasis settings

- Equalizer and DC gain settings

- Voltage Output Differential (V<sub>OD</sub>) settings

The channel reconfiguration allows you to dynamically modify the data rate, local dividers, and the functional mode of the transceiver channel.

Refer to the *Stratix II GX Device Handbook*, volume 2, for more information.

The dynamic reconfiguration block requires an input clock between 2.5 MHz and 50 MHz. The clock for the dynamic reconfiguration block is derived from a high-speed clock and divided down using a counter.

#### Individual Power Down and Reset for the Transmitter and Receiver

Stratix II GX transceivers offer a power saving advantage with their ability to shut off functions that are not needed. The device can individually reset the receiver and transmitter blocks and the PLLs. The Stratix II GX device can either globally or individually power down and reset the transceiver. Table  $2{\text -}16$  shows the connectivity between the reset signals and the Stratix II GX transceiver blocks. These reset signals can be controlled from the FPGA or pins.

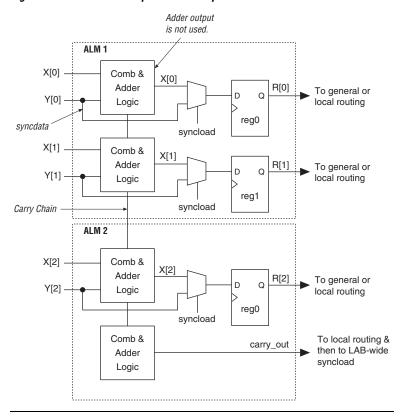

One ALM contains two programmable registers. Each register has data, clock, clock enable, synchronous and asynchronous clear, asynchronous load data, and synchronous and asynchronous load/preset inputs.

Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous load data. The asynchronous load data input comes from the datae or dataf input of the ALM, which are the same inputs that can be used for register packing. For combinational functions, the register is bypassed and the output of the LUT drives directly to the outputs of the ALM.

Each ALM has two sets of outputs that drive the local, row, and column routing resources. The LUT, adder, or register output can drive these output drivers independently (see Figure 2–36). For each set of output drivers, two ALM outputs can drive column, row, or direct link routing connections, and one of these ALM outputs can also drive local interconnect resources. This allows the LUT or adder to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the combinational logic for unrelated functions. Another special packing mode allows the register output to feed back into the LUT of the same ALM so that the register is packed with its own fan-out LUT. This feature provides another mechanism for improved fitting. The ALM can also drive out registered and unregistered versions of the LUT or adder output.

See the *Stratix II Performance and Logic Efficiency Analysis White Paper* for more information on the efficiencies of the Stratix II GX ALM and comparisons with previous architectures.

#### **ALM Operating Modes**

The Stratix II GX ALM can operate in one of the following modes:

- Normal mode

- Extended LUT mode

- Arithmetic mode

- Shared arithmetic mode

Each mode uses ALM resources differently. Each mode has 11 available inputs to the ALM (see Figure 2–35)—the eight data inputs from the LAB local interconnect; carry-in from the previous ALM or LAB; the shared arithmetic chain connection from the previous ALM or LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock,

using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

Figure 2-39. 6-Input Function in Normal Mode Notes (1), (2) To general or dataf0 local routing datae0 6-Input dataa To general or LUT datab Q local routing datac datad reg0 datae1 dataf1 To general or D Q (2) local routing These inputs are available for register packing. reg1

#### Notes to Figure 2–39:

- If datae1 and dataf1 are used as inputs to the six-input function, datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

#### Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–40 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing. Functions that fit into the template shown in Figure 2–40 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

Figure 2-42. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up and down control, add and subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up and down and add and subtract control signals. These control signals may be used for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

| Memory Feature                              | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |

|---------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Simple dual-port memory mixed width support | <b>✓</b>                                                                | ~                                                                                                | <b>✓</b>                                                                                                         |

| True dual-port memory mixed width support   |                                                                         | ~                                                                                                | <b>✓</b>                                                                                                         |

| Power-up conditions                         | Outputs cleared                                                         | Outputs cleared                                                                                  | Outputs unknown                                                                                                  |

| Register clears                             | Output registers                                                        | Output registers                                                                                 | Output registers                                                                                                 |

| Mixed-port read-during-write                | Unknown output/old data                                                 | Unknown output/old data                                                                          | Unknown output                                                                                                   |

| Configurations                              | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |

Note to Table 2-19:

TriMatrix memory provides three different memory sizes for efficient application support. The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This

applies to both read and write operations.

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block, allowing the RAM block to operate in read and write or input and output clock modes. Only the output register can be bypassed. The six labclk signals or local interconnect can drive the inclock, outclock, wren, rden, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, ALMs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–49 shows the M512 RAM block control signal generation logic.

Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local outclocken Interconnect inclocken wren Local outclr inclock outclock rden Interconnect

Figure 2-49. M512 RAM Block Control Signals

#### **M4K RAM Blocks**

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–51.

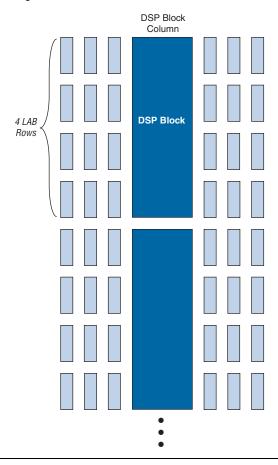

Figures 2–57 shows one of the columns with surrounding LAB rows.

Figure 2-57. DSP Blocks Arranged in Columns

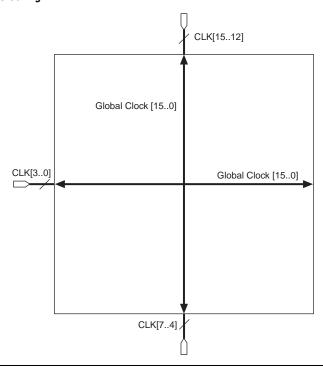

generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–61 shows the 12 dedicated CLK pins driving global clock networks.

Figure 2-61. Global Clocking

#### Regional Clock Network

There are eight regional clock networks (RCLK[7..0]) in each quadrant of the Stratix II GX device that are driven by the dedicated CLK[15..12] and CLK[7..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–62.

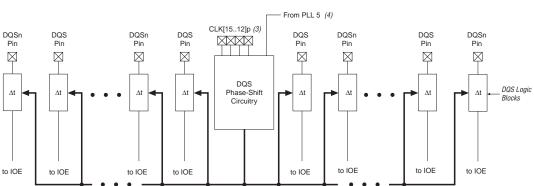

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II GX device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits. Figure 2–86 shows the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Figure 2–86. DQS Phase-Shift Circuitry Notes (1), (2)

#### Notes to Figure 2-86:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II GX device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The "t" module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

# Referenced Documents

This chapter references the following documents:

- AN 357: Error Detection Using CRC in Altera FPGA Devices

- AN 414: An Embedded Solution for PLD JTAG Configuration

- AN 418 SRunner: An Embedded Solution for Serial Configuration Device Programming

- Configuring Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

- Configuring the MicroBlaster Fast Passive Parallel Software Driver White Paver

- Configuring the MicroBlaster Passive Serial Software Driver White Paper

- MorphIO: An I/O Reconfiguration Solution for Altera Devices White Paper

- PLLs in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

- Remote System Upgrades with Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook

- Serial Configuration Devices (EPCS1, EPCS4, EPCS64, and EPCS128)

Data Sheet in the Configuration Handbook

- Stratix II GX Architecture chapter in volume 1 of the Stratix II GX Device Handbook.

### Document Revision History

Table 3–6 shows the revision history for this chapter.

| Table 3–6. Docu                 | Table 3–6. Document Revision History                                  |                                                         |  |  |  |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|--|--|

| Date and<br>Document<br>Version | Changes Made                                                          | Summary of Changes                                      |  |  |  |  |  |  |  |  |

| October 2007<br>v1.4            | Minor text edits.                                                     | _                                                       |  |  |  |  |  |  |  |  |

| August 2007<br>v1.3             | Updated the note in the "IEEE Std. 1149.1 JTAG Boundary-Scan Support" | _                                                       |  |  |  |  |  |  |  |  |

|                                 | Updated Table 3–3.                                                    | _                                                       |  |  |  |  |  |  |  |  |

|                                 | Added the "Referenced Documents" section.                             | _                                                       |  |  |  |  |  |  |  |  |

| May 2007<br>v1.2                | Updated the "Temperature Sensing Diode (TSD)" section.                | _                                                       |  |  |  |  |  |  |  |  |

| February 2007<br>v1.1           | Added the "Document Revision History" section to this chapter.        | Added support information for the Stratix II GX device. |  |  |  |  |  |  |  |  |

| October 2005<br>v1.0            | Added chapter to the Stratix II GX Device Handbook.                   | _                                                       |  |  |  |  |  |  |  |  |

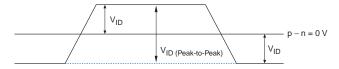

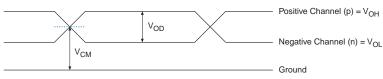

Figures 4–6 and 4–7 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS and LVPECL).

Figure 4-6. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{IH}$ $V_{CM}$ Negative Channel (n) = $V_{IL}$ Ground

#### **Differential Waveform**

Figure 4–7. Transmitter Output Waveforms for Differential I/O Standards

#### Single-Ended Waveform

#### Differential Waveform

| Table 4-3            | Table 4–39. SSTL-2 Class II Specifications |                                  |                         |         |                         |      |  |  |  |  |  |  |  |

|----------------------|--------------------------------------------|----------------------------------|-------------------------|---------|-------------------------|------|--|--|--|--|--|--|--|

| Symbol               | Parameter                                  | Conditions                       | Minimum                 | Typical | Maximum                 | Unit |  |  |  |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage                |                                  | V <sub>REF</sub> + 0.18 |         | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage                 |                                  | -0.3                    |         | V <sub>REF</sub> – 0.18 | V    |  |  |  |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage                |                                  | V <sub>REF</sub> + 0.35 |         |                         | V    |  |  |  |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage                 |                                  |                         |         | V <sub>REF</sub> - 0.35 | V    |  |  |  |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                  | $I_{OH} = -16.4 \text{ mA } (1)$ | V <sub>TT</sub> + 0.76  |         |                         | V    |  |  |  |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                   | I <sub>OL</sub> = 16.4 mA (1)    |                         |         | V <sub>TT</sub> – 0.76  | V    |  |  |  |  |  |  |  |

#### Note to Table 4-39:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 4-40.             | Table 4–40. SSTL-2 Class I and II Differential Specifications |            |                              |                       |                      |      |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------|------------|------------------------------|-----------------------|----------------------|------|--|--|--|--|--|--|

| Symbol                  | Parameter                                                     | Conditions | Minimum                      | Typical               | Maximum              | Unit |  |  |  |  |  |  |

| $V_{\text{CCIO}}$       | Output supply voltage                                         |            | 2.375                        | 2.5                   | 2.625                | V    |  |  |  |  |  |  |

| V <sub>SWING</sub> (DC) | DC differential input voltage                                 |            | 0.36                         |                       |                      | V    |  |  |  |  |  |  |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage                     |            | (V <sub>CCIO</sub> /2) - 0.2 |                       | $(V_{CCIO}/2) + 0.2$ | V    |  |  |  |  |  |  |

| V <sub>SWING</sub> (AC) | AC differential input voltage                                 |            | 0.7                          |                       |                      | V    |  |  |  |  |  |  |

| V <sub>ISO</sub>        | Input clock signal offset voltage                             |            |                              | 0.5 V <sub>CCIO</sub> |                      | V    |  |  |  |  |  |  |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation                   |            |                              | 200                   |                      | mV   |  |  |  |  |  |  |

| V <sub>OX</sub> (AC)    | AC differential output cross point voltage                    |            | (V <sub>CCIO</sub> /2) - 0.2 |                       | $(V_{CCIO}/2) + 0.2$ | V    |  |  |  |  |  |  |

| Table 4-             | Table 4–41. 1.2-V HSTL Specifications |            |                         |                       |                          |      |  |  |  |  |  |  |

|----------------------|---------------------------------------|------------|-------------------------|-----------------------|--------------------------|------|--|--|--|--|--|--|

| Symbol               | Parameter                             | Conditions | Minimum                 | Typical               | Maximum                  | Unit |  |  |  |  |  |  |

| $V_{\text{CCIO}}$    | Output supply voltage                 |            | 1.14                    | 1.2                   | 1.26                     | V    |  |  |  |  |  |  |

| $V_{REF}$            | Reference voltage                     |            | 0.48 V <sub>CCIO</sub>  | 0.5 V <sub>CCIO</sub> | 0.52 V <sub>CCIO</sub>   | ٧    |  |  |  |  |  |  |

| V <sub>IH</sub> (DC) | High-level DC input voltage           |            | V <sub>REF</sub> + 0.08 |                       | V <sub>CCIO</sub> + 0.15 | ٧    |  |  |  |  |  |  |

| V <sub>IL</sub> (DC) | Low-level DC input voltage            |            | -0.15                   |                       | V <sub>REF</sub> - 0.08  | ٧    |  |  |  |  |  |  |

| V <sub>IH</sub> (AC) | High-level AC input voltage           |            | V <sub>REF</sub> + 0.15 |                       | V <sub>CCIO</sub> + 0.24 | V    |  |  |  |  |  |  |

| V <sub>IL</sub> (AC) | Low-level AC input voltage            |            | -0.24                   |                       | V <sub>REF</sub> – 0.15  | ٧    |  |  |  |  |  |  |

| Table 4-65. E        | Table 4–65. EP2SGX30 Column Pins Regional Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|

| Parameter            | Fast Corner                                                       |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |

| raiailletei          | Industrial                                                        | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.493                                                             | 1.507      | 2.522    | 2.806    | 3.364    | ns     |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.353                                                             | 1.372      | 2.525    | 2.809    | 3.364    | ns     |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | 0.087                                                             | 0.104      | 0.237    | 0.253    | 0.292    | ns     |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.078                                                            | -0.061     | 0.237    | 0.253    | 0.29     | ns     |  |  |  |  |  |  |

| Table 4–66. E        | Table 4–66. EP2SGX30 Row Pins Regional Clock Timing Parameters |            |          |             |          |                   |  |                   |  |        |  |  |

|----------------------|----------------------------------------------------------------|------------|----------|-------------|----------|-------------------|--|-------------------|--|--------|--|--|

| Parameter            | Fast Corner                                                    |            | -3 Speed | -4 Speed    | -5 Speed | Units             |  |                   |  |        |  |  |

| Parameter            | Industrial                                                     | Commercial | Grade    | Grade Grade |          | Grade Grade Grade |  | Grade Grade Grade |  | UIIIIS |  |  |

| t <sub>CIN</sub>     | 1.246                                                          | 1.262      | 2.437    | 2.712       | 3.246    | ns                |  |                   |  |        |  |  |

| t <sub>COUT</sub>    | 1.251                                                          | 1.267      | 2.437    | 2.712       | 3.246    | ns                |  |                   |  |        |  |  |

| t <sub>PLLCIN</sub>  | -0.18                                                          | -0.167     | 0.215    | 0.229       | 0.263    | ns                |  |                   |  |        |  |  |

| t <sub>PLLCOUT</sub> | -0.175                                                         | -0.162     | 0.215    | 0.229       | 0.263    | ns                |  |                   |  |        |  |  |

#### EP2SGX60 Clock Timing Parameters

Tables 4–67 through 4–70 show the maximum clock timing parameters for EP2SGX60 devices.

| Table 4–67. E        | Table 4–67. EP2SGX60 Column Pins Global Clock Timing Parameters |            |          |             |          |        |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------|------------|----------|-------------|----------|--------|--|--|--|--|--|

| Parameter            | Fast Corner                                                     |            | -3 Speed | -4 Speed    | -5 Speed | Units  |  |  |  |  |  |

| rarameter            | Industrial                                                      | Commercial | Grade    | Grade Grade |          | Ullits |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.722                                                           | 1.736      | 2.940    | 3.275       | 3.919    | ns     |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.557                                                           | 1.571      | 2.698    | 3.005       | 3.595    | ns     |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | 0.037                                                           | 0.051      | 0.474    | 0.521       | 0.613    | ns     |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.128                                                          | -0.114     | 0.232    | 0.251       | 0.289    | ns     |  |  |  |  |  |

Table 4–87. Stratix II GX I/O Output Delay for Row Pins (Part 3 of 4)

| I/O Standard    | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|-----------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| SSTL-18         | 4 mA              | t <sub>OP</sub>  | 1038                                     | 1709                  | 1793                  | 1906              | 2046              | ps   |

| Class I         |                   | t <sub>DIP</sub> | 995                                      | 1654                  | 1736                  | 1846              | 1973              | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1042                                     | 1648                  | 1729                  | 1838              | 1975              | ps   |

|                 |                   | t <sub>DIP</sub> | 999                                      | 1593                  | 1672                  | 1778              | 1902              | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1018                                     | 1633                  | 1713                  | 1821              | 1958              | ps   |

|                 |                   | t <sub>DIP</sub> | 975                                      | 1578                  | 1656                  | 1761              | 1885              | ps   |

|                 | 10 mA (1)         | t <sub>OP</sub>  | 1021                                     | 1615                  | 1694                  | 1801              | 1937              | ps   |

|                 |                   | t <sub>DIP</sub> | 978                                      | 1560                  | 1637                  | 1741              | 1864              | ps   |

| 1.8-V HSTL      | 4 mA              | t <sub>OP</sub>  | 1019                                     | 1610                  | 1689                  | 1795              | 1956              | ps   |

| Class I         |                   | t <sub>DIP</sub> | 976                                      | 1555                  | 1632                  | 1735              | 1883              | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1022                                     | 1580                  | 1658                  | 1762              | 1920              | ps   |

|                 |                   | t <sub>DIP</sub> | 979                                      | 1525                  | 1601                  | 1702              | 1847              | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1004                                     | 1576                  | 1653                  | 1757              | 1916              | ps   |

|                 |                   | t <sub>DIP</sub> | 961                                      | 1521                  | 1596                  | 1697              | 1843              | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 1008                                     | 1567                  | 1644                  | 1747              | 1905              | ps   |

|                 |                   | t <sub>DIP</sub> | 965                                      | 1512                  | 1587                  | 1687              | 1832              | ps   |

|                 | 12 mA (1)         | t <sub>OP</sub>  | 999                                      | 1566                  | 1643                  | 1746              | 1904              | ps   |

|                 |                   | t <sub>DIP</sub> | 956                                      | 1511                  | 1586                  | 1686              | 1831              | ps   |

| 1.5-V HSTL      | 4 mA              | t <sub>OP</sub>  | 1018                                     | 1591                  | 1669                  | 1774              | 1933              | ps   |

| Class I         |                   | t <sub>DIP</sub> | 975                                      | 1536                  | 1612                  | 1714              | 1860              | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1021                                     | 1579                  | 1657                  | 1761              | 1919              | ps   |

|                 |                   | t <sub>DIP</sub> | 978                                      | 1524                  | 1600                  | 1701              | 1846              | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1006                                     | 1572                  | 1649                  | 1753              | 1911              | ps   |

|                 |                   | t <sub>DIP</sub> | 963                                      | 1517                  | 1592                  | 1693              | 1838              | ps   |

| Differential    | 8 mA              | t <sub>OP</sub>  | 1050                                     | 1759                  | 1846                  | 1962              | 2104              | ps   |

| SSTL-2 Class I  |                   | t <sub>DIP</sub> | 1007                                     | 1704                  | 1789                  | 1902              | 2031              | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 1026                                     | 1694                  | 1777                  | 1889              | 2028              | ps   |

|                 |                   | t <sub>DIP</sub> | 983                                      | 1639                  | 1720                  | 1829              | 1955              | ps   |

| Differential    | 16 mA             | t <sub>OP</sub>  | 992                                      | 1581                  | 1659                  | 1763              | 1897              | ps   |

| SSTL-2 Class II |                   | t <sub>DIP</sub> | 949                                      | 1526                  | 1602                  | 1703              | 1824              | ps   |

Table 4–107 shows the high-speed I/O timing specifications for -3 speed grade Stratix II GX devices.

|                                      |                         |                                                   |             |      | -3 Speed Grade |       |                       |  |

|--------------------------------------|-------------------------|---------------------------------------------------|-------------|------|----------------|-------|-----------------------|--|

| Symbol                               | C                       | onditions                                         |             | Min  | Тур            | Max   | Unit                  |  |

| $f_{IN} = f_{HSDR} / W$              | W = 2 to 32 (LVDS, (3)  | W = 2 to 32 (LVDS, HyperTransport technology) (3) |             |      |                |       | MHz                   |  |

|                                      | W = 1 (SERDES by        | pass, LVDS only                                   | /)          | 16   |                | 500   | MHz                   |  |

|                                      | W = 1 (SERDES us        | ed, LVDS only)                                    |             | 150  |                | 717   | MHz                   |  |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, F    | HyperTransport t                                  | technology) | 150  |                | 1,040 | Mbps                  |  |

|                                      | J = 2 (LVDS, Hyper      | Transport techno                                  | ology)      | (4)  |                | 760   | Mbps                  |  |

|                                      | J = 1 (LVDS only)       |                                                   |             | (4)  |                | 500   | Mbps                  |  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, F    | HyperTransport t                                  | echnology)  | 150  |                | 1,040 | Mbps                  |  |

| TCCS                                 | All differential stand  | ards                                              |             | -    |                | 200   | ps                    |  |

| SW                                   | All differential stand  | ards                                              |             | 330  |                | -     | ps                    |  |

| Output jitter                        |                         |                                                   |             |      |                | 190   | ps                    |  |

| Output t <sub>RISE</sub>             | All differential I/O st | andards                                           |             |      |                | 160   | ps                    |  |

| Output t <sub>FALL</sub>             | All differential I/O st | andards                                           |             |      |                | 180   | ps                    |  |

| t <sub>DUTY</sub>                    |                         |                                                   |             | 45   | 50             | 55    | %                     |  |

| DPA run length                       |                         |                                                   |             |      |                | 6,400 | UI                    |  |

| DPA jitter tolerance (5)             | Data channel peak-      | to-peak jitter                                    |             | 0.44 |                |       | UI                    |  |

| DPA lock time                        |                         |                                                   |             |      |                |       | Number of repetitions |  |

|                                      | SPI-4                   | 111111111                                         |             |      |                |       |                       |  |

|                                      | Parallel Rapid I/O      |                                                   |             |      |                |       | 1                     |  |

|                                      |                         | 10010000                                          | 50%         | 256  |                |       | 1                     |  |

|                                      | Miscellaneous           | 10101010                                          | 100%        | 256  |                |       | 1                     |  |

|                                      |                         | 01010101                                          |             | 256  |                |       | 1                     |  |

<sup>(1)</sup> When J = 4 to 10, the SERDES block is used.

<sup>(2)</sup> When J = 1 or 2, the SERDES block is bypassed.

<sup>(3)</sup> The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤nput clock frequency × W ≤1,040.

<sup>(4)</sup> The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

<sup>(5)</sup> For setup details, refer to the characterization report.

## Document Revision History

Table 6--105 shows the revision history for this chapter.

| Table 4–118. Document Revision History (Part 1 of 5) |                                                                                                                                                                                                                                                                                                                                          |                    |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                                                                                                                                                                             | Summary of Changes |

| June 2009<br>v4.6                                    | Replaced Table 4–31 Updated:      Table 4–5     Table 4–6     Table 4–7     Table 4–8     Table 4–9     Table 4–10     Table 4–11     Table 4–12     Table 4–13     Table 4–15     Table 4–16     Table 4–17     Table 4–18     Table 4–18     Table 4–20     Table 4–50     Table 4–105     Table 4–110     Table 4–110     Table 4–111 |                    |

| October 2007<br>v4.5                                 | Updated:  Table 4–3  Table 4–6  Table 4–16  Table 4–19  Table 4–20  Table 4–21  Table 4–22  Table 4–55  Table 4–106  Table 4–107  Table 4–108  Table 4–109  Table 4–112  Updated title only in Tables 4–88 and 4–89.                                                                                                                     |                    |

|                                                      | Minor text edits.                                                                                                                                                                                                                                                                                                                        |                    |