Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 3022                                                       |

| Number of Logic Elements/Cells | 60440                                                      |

| Total RAM Bits                 | 2544192                                                    |

| Number of I/O                  | 364                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60cf780c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Transmit State Machine

The transmit state machine operates in either PCI Express mode, XAUI mode, or GIGE mode, depending on the protocol used. The state machine is not utilized for certain protocols, such as SONET.

#### GIGE Mode

In GIGE mode, the transmit state machine converts all idle ordered sets (/K28.5/, /Dx.y/) to either /I1/ or /I2/ ordered sets. /I1/ consists of a negative-ending disparity /K28.5/ (denoted by /K28.5/-) followed by a neutral /D5.6/. /I2/ consists of a positive-ending disparity /K28.5/ (denoted by /K28.5/+) and a negative-ending disparity /D16.2/ (denoted by /D16.2/-). The transmit state machines do not convert any of the ordered sets to match /C1/ or /C2/, which are the configuration ordered sets. (/C1/ and /C2/ are defined by [/K28.5/, /D21.5/] and [/K28.5/, /D2.2/], respectively). Both the /I1/ and /I2/ ordered sets guarantee a negative-ending disparity after each ordered set.

#### XAUI Mode

The transmit state machine translates the XAUI XGMII code group to the XAUI PCS code group. Table 2–5 shows the code conversion.

| Table 2–5. | Code Conversion                           |                                        |                         |

|------------|-------------------------------------------|----------------------------------------|-------------------------|

| XGMII TXC  | XGMII TXD                                 | PCS Code-Group                         | Description             |

| 0          | 00 through FF                             | Dxx.y                                  | Normal data             |

| 1          | 07                                        | K28.0 or K28.3 or<br>K28.5             | Idle in    <b>I</b>     |

| 1          | 07                                        | K28.5                                  | Idle in   T             |

| 1          | 9C                                        | K28.4                                  | Sequence                |

| 1          | FB                                        | K27.7                                  | Start                   |

| 1          | FD                                        | K29.7                                  | Terminate               |

| 1          | FE                                        | K30.7                                  | Error                   |

| 1          | See IEEE 802.3<br>reserved code<br>groups | See IEEE 802.3<br>reserved code groups | Reserved code groups    |

| 1          | Other value                               | K30.7                                  | Invalid XGMII character |

The XAUI PCS idle code groups, /K28.0/ (/R/) and /K28.5/ (/K/), are automatically randomized based on a PRBS7 pattern with an  $x^7 + x^6 + 1$  polynomial. The /K28.3/ (/A/) code group is automatically generated between 16 and 31 idle code groups. The idle randomization on the /A/, /K/, and /R/ code groups is done automatically by the transmit state machine.

reduce the interface speed. For example, at  $6.375~\mathrm{Gbps}$ , the transceiver logic has a double-byte-wide data path that runs at  $318.75~\mathrm{MHz}$  in a  $\times 20~\mathrm{deserializer}$  factor, which is above the maximum FPGA interface speed. When using the byte deserializer, the FPGA interface width doubles to  $40~\mathrm{bits}$  (36-bits when using the  $8B/10B~\mathrm{encoder}$ ) and the interface speed reduces to  $159.375~\mathrm{MHz}$ .

| Table 2–9. Byte Deserializer Input and Output Widths |                                                    |  |  |  |  |  |  |  |  |

|------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|--|

| Input Data Width (Bits)                              | Deserialized Output Data Width to t<br>FPGA (Bits) |  |  |  |  |  |  |  |  |

| 20                                                   | 40                                                 |  |  |  |  |  |  |  |  |

| 16                                                   | 32                                                 |  |  |  |  |  |  |  |  |

| 10                                                   | 20                                                 |  |  |  |  |  |  |  |  |

| 8                                                    | 16                                                 |  |  |  |  |  |  |  |  |

#### Byte Ordering Block

The byte ordering block shifts the byte order. A pre-programmed byte in the input data stream is detected and placed in the least significant byte of the output stream. Subsequent bytes start appearing in the byte positions following the LSB. The byte ordering block inserts the programmed PAD characters to shift the byte order pattern to the LSB.

Based on the setting in the MegaWizard® Plug-In Manager, the byte ordering block can be enabled either by the rx\_syncstatus signal or by the rx\_enabyteord signal from the PLD. When the rx\_syncstatus signal is used as enable, the byte ordering block reorders the data only for the first occurrence of the byte order pattern that is received after word alignment is completed. You must assert rx\_digitalreset to perform byte ordering again. However, when the byte ordering block is controlled by rx\_enabyteord, the byte ordering block can be controlled by the PLD logic dynamically. When you create your functional mode in the MegaWizard, you can select byte ordering block only if rate matcher is not selected.

#### Receiver Phase Compensation FIFO Buffer

The receiver phase compensation FIFO buffer resides in the transceiver block at the FPGA boundary and cannot be bypassed. This FIFO buffer compensates for phase differences and clock tree timing skew between the receiver clock domain within the transceiver and the receiver FPGA clock after it has transferred to the FPGA.

#### Applications and Protocols Supported with Stratix II GX Devices

Each Stratix II GX transceiver block is designed to operate at any serial bit rate from 600 Mbps to 6.375 Gbps per channel. The wide data rate range allows Stratix II GX transceivers to support a wide variety of standards and protocols, such as PCI Express, GIGE, SONET/SDH, SDI, OIF-CEI, and XAUI. Stratix II GX devices are ideal for many high-speed communication applications, such as high-speed backplanes, chip-to-chip bridges, and high-speed serial communications links.

#### Example Applications Support for Stratix II GX

Stratix II GX devices can be used for many applications, including:

- Traffic management with various levels of quality of service (QoS) and integrated serial backplane interconnect

- Multi-port single-protocol switching (for example, PCI Express, GIGE, XAUI switch, or SONET/SDH)

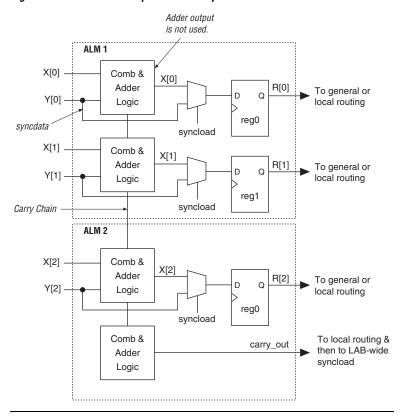

## Logic Array Blocks

Each logic array block (LAB) consists of eight adaptive logic modules (ALMs), carry chains, shared arithmetic chains, LAB control signals, local interconnects, and register chain connection lines. The local interconnect transfers signals between ALMs in the same LAB. Register chain connections transfer the output of an ALM register to the adjacent ALM register in a LAB. The Quartus II Compiler places associated logic in a LAB or adjacent LABs, allowing the use of local, shared arithmetic chain, and register chain connections for performance and area efficiency. Table 2–17 shows Stratix II GX device resources. Figure 2–32 shows the Stratix II GX LAB structure.

| Table 2–17. S | Table 2–17. Stratix II GX Device Resources |                           |                 |                             |                |          |  |  |  |  |  |  |

|---------------|--------------------------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|--|--|--|--|--|--|

| Device        | M512 RAM<br>Columns/Blocks                 | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |  |  |  |  |  |  |

| EP2SGX30      | 6/202                                      | 4/144                     | 1               | 2/16                        | 49             | 36       |  |  |  |  |  |  |

| EP2SGX60      | 7/329                                      | 5/255                     | 2               | 3/36                        | 62             | 51       |  |  |  |  |  |  |

| EP2SGX90      | 8/488                                      | 6/408                     | 4               | 3/48                        | 71             | 68       |  |  |  |  |  |  |

| EP2SGX130     | 9/699                                      | 7/609                     | 6               | 3/63                        | 81             | 87       |  |  |  |  |  |  |

Figure 2-42. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up and down control, add and subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up and down and add and subtract control signals. These control signals may be used for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

| Table 2-23.             | DSP Block Signal Sources and D                                                                | estinations          |                    |

|-------------------------|-----------------------------------------------------------------------------------------------|----------------------|--------------------|

| LAB Row at<br>Interface | Control Signals Generated                                                                     | Data Inputs          | Data Outputs       |

| 0                       | clock0 aclr0 ena0 mult01_saturate addnsub1_round/ accum_round addnsub1 signa sourcea sourceb  | A1 [170]<br>B1 [170] | OA[170]<br>OB[170] |

| 1                       | clock1 aclr1 enal accum_saturate mult01_round accum_sload sourcea sourceb mode0               | A2 [170]<br>B2 [170] | OC[170]<br>OD[170] |

| 2                       | clock2 aclr2 ena2 mult23_saturate addnsub3_round/ accum_round addnsub3 sign_b sourcea sourceb | A3 [170]<br>B3 [170] | OE[170]<br>OF[170] |

| 3                       | clock3 aclr3 ena3 accum_saturate mult23_round accum_sload sourcea sourceb mode1               | A4 [170]<br>B4 [170] | OG[170]<br>OH[170] |

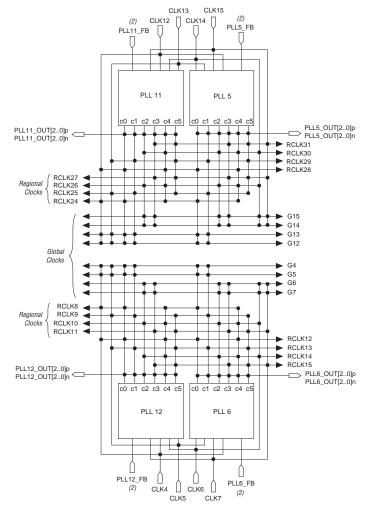

Figure 2–73 shows the global and regional clocking from enhanced PLL outputs and top and bottom CLK pins.

Figure 2–73. Global and Regional Clock Connections from Top and Bottom Clock Pins and Enhanced PLL Outputs Notes (1), (2)

#### *Notes to Figure 2–73:*

- (1) EP2SGX30C/D and EP2SGX60C/D devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you will lose one (or two, if FBIN is differential) external clock output pin.

| Top Side Global and                    | DLLCLK   | CLK12    | CLK13    | 14       | (15      | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | K31      |

|----------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Regional Clock Network<br>Connectivity | DLL      | CE       | Ę.       | CLK14    | CLK15    | RCL      | RCLK31   |

| c2                                     | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                     | ~        |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                     | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                     | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 11 outputs                | •        |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                     |          | <b>✓</b> | <b>~</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                     |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                     |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>\</b> |          |          |          | <b>\</b> |          |

| c3                                     |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                     |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                     |          |          |          |          |          |          | _        |          | /        |          | /        |          | _        |

| Table 2–29. Global and Regional Clock Connections from Bottom Clock Pins and Enhanced PLL<br>Outputs (Part 1 of 2) |                             |          |          |          |          |          |          |          |          |          |          |          |          |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global and<br>Regional Clock Network<br>Connectivity                                                   | DLLCLK                      | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| Clock pins                                                                                                         |                             |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4p                                                                                                              | <b>~</b>                    | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |          |          |

| CLK5p                                                                                                              | <b>✓</b>                    | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6p                                                                                                              | <b>✓</b>                    |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7p                                                                                                              | <b>✓</b>                    |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |

| CLK4n                                                                                                              |                             | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK5n                                                                                                              |                             |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6n                                                                                                              |                             |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7n                                                                                                              |                             |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |

| Drivers from internal logic                                                                                        | Drivers from internal logic |          |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV0                                                                                                           |                             | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                                                                           |                             |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

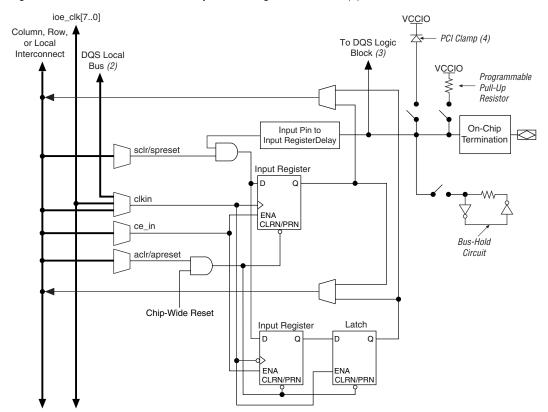

Figure 2–82. Stratix II GX IOE in DDR Input I/O Configuration Note (1)

Notes to Figure 2-82:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

- (4) The optional PCI clamp is only available on column I/O pins.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II GX device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

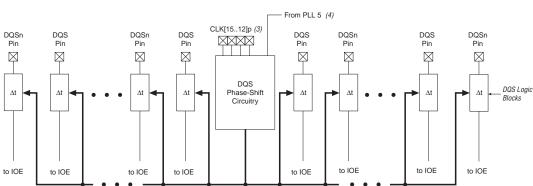

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits. Figure 2–86 shows the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Figure 2–86. DQS Phase-Shift Circuitry Notes (1), (2)

#### Notes to Figure 2-86:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II GX device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The "t" module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

| Table 4–19. Strati                     | ix II GX Transceiver Bi                                                                                                                                                              | ock AC                                | Specia | fication                                                | · · · · · |     |                                       | art 12 | of 19) |      |    |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|---------------------------------------------------------|-----------|-----|---------------------------------------|--------|--------|------|----|

| Symbol/<br>Description                 | Conditions                                                                                                                                                                           | -3 Speed<br>Commercial Speed<br>Grade |        | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |           |     | -5 Speed<br>Commercial Speed<br>Grade |        |        | Unit |    |

|                                        |                                                                                                                                                                                      | Min                                   | Тур    | Max                                                     | Min       | Тур | Max                                   | Min    | Тур    | Max  |    |

| <b>CPRI Transmitter</b>                | Jitter Generation (15)                                                                                                                                                               | )                                     |        |                                                         |           |     |                                       |        |        |      |    |

| Deterministic Jitter<br>(peak-to-peak) | Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps and 1.2288 Gbps REFCLK = 122.88 MHz for 2.4576 Gbps Pattern = CJPAT Vod = 1400 mV No Pre-emphasis |                                       |        | 0.14                                                    |           |     | 0.14                                  |        |        | N/A  | UI |

| Total Jitter<br>(peak-to-peak)         | Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps and 1.2288 Gbps REFCLK = 122.88 MHz for 2.4576 Gbps Pattern = CJPAT Vod = 1400 mV No Pre-emphasis |                                       |        | 0.279                                                   |           |     | 0.279                                 |        |        | N/A  | UI |

| Symbol/<br>Description         | Conditions                                                                                                                                                                                                              | -3 Speed<br>Commercial Speed<br>Grade |       |     | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |       |     | -5 Speed<br>Commercial Speed<br>Grade |     |     | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|---------------------------------------------------------|-------|-----|---------------------------------------|-----|-----|------|

|                                |                                                                                                                                                                                                                         | Min                                   | Тур   | Max | Min                                                     | Тур   | Max | Min                                   | Тур | Max |      |

| Sinusoidal Jitter<br>Tolerance | Jitter Frequency = 22.1 KHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                       | > 8.5 |     |                                                         | > 8.5 |     |                                       | N/A |     | UI   |

| (peak-to-peak) (6)             | Jitter Frequency = 1.875MHz Data Rate = 614.4 Mbps, 1.2288 Gbps, 2.4576 Gbps REFCLK = 61.44 MHz for 614.4 Mbps REFCLK = 122.88 MHz for 1.2288 Gbps and 2.4576 Gbps Pattern = CJPAT Equalizer Setting = 6 DC Gain = 0 dB |                                       | > 0.1 |     |                                                         | > 0.1 |     |                                       | N/A |     | UI   |

|                                   |                                                                        |                                  | Resista           | Resistance Tolerance |      |  |  |  |  |

|-----------------------------------|------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|--|--|--|--|

| Symbol                            | Description                                                            | Conditions                       | Commercial<br>Max | Industrial<br>Max    | Unit |  |  |  |  |

| 25-ΩR <sub>S</sub><br>3.3/2.5     | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 3.3/2.5V$            | ±30               | ±30                  | %    |  |  |  |  |

| 50-ΩR <sub>S</sub><br>3.3/2.5/1.8 | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5/1.8V | ±30               | ±30                  | %    |  |  |  |  |

| 50-ΩR <sub>S</sub> 1.5            | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5V         | ±36               | ±36                  | %    |  |  |  |  |

| R <sub>D</sub>                    | Internal differential termination for LVDS (100- $\Omega$ setting)     | V <sub>CCIO</sub> = 2.5 V        | ±20               | ±25                  | %    |  |  |  |  |

Note to Table 4-50:

(1) On-chip parallel termination with calibration is only supported for input pins.

## **Pin Capacitance**

Table 4–51 shows the Stratix II GX device family pin capacitance.

| Table 4-51.        | Table 4–51. Stratix II GX Device Capacitance Note (1)                                                                |         |      |  |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                            | Typical | Unit |  |  |  |  |  |  |  |

| C <sub>IOTB</sub>  | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                           | 5.0     | pF   |  |  |  |  |  |  |  |

| C <sub>IOL</sub>   | Input capacitance on I/O pins in I/O banks 1 and 2, including high-speed differential receiver and transmitter pins. | 6.1     | pF   |  |  |  |  |  |  |  |

| C <sub>CLKTB</sub> | Input capacitance on top/bottom clock input pins: $CLK[47]$ and $CLK[1215]$ .                                        | 6.0     | pF   |  |  |  |  |  |  |  |

| C <sub>CLKL</sub>  | Input capacitance on left clock inputs: CLK0 and CLK2.                                                               | 6.1     | pF   |  |  |  |  |  |  |  |

| C <sub>CLKL+</sub> | Input capacitance on left clock inputs: CLK1 and CLK3.                                                               | 3.3     | pF   |  |  |  |  |  |  |  |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output/feedback pins in PLL banks 11 and 12.                                 | 6.7     | pF   |  |  |  |  |  |  |  |

Note to Table 4-51:

(1) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within  $\pm 0.5$  pF.

# Power Consumption

Altera offers two ways to calculate power for a design: the Excel-based PowerPlay early power estimator power calculator and the Quartus<sup>®</sup> II PowerPlay power analyzer feature.

The interactive Excel-based PowerPlay early power estimator is typically used prior to designing the FPGA in order to get an estimate of device power. The Quartus II PowerPlay power analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The power analyzer can apply a combination of user-entered, simulation-derived and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

For more information on PowerPlay tools, refer to the *PowerPlay Early Power Estimators* (*EPE*) and *Power Analyzer*, the *Quartus II PowerPlay Analysis and Optimization Technology*, and the *PowerPlay Power Analyzer* chapter in volume 3 of the *Quartus II Handbook*. The PowerPlay early power estimators are available on the Altera web site at **www.altera.com**.

See Table 4–23 on page 42 for typical I<sub>CC</sub> standby specifications.

## **Timing Model**

The DirectDrive technology and MultiTrack interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix II GX device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

## **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–52 shows the status of the Stratix II GX device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

## EP2SGX90 Clock Timing Parameters

Tables 4–71 through 4–74 show the maximum clock timing parameters for EP2SGX90 devices.

| Table 4-71. E        | Table 4–71. EP2SGX90 Column Pins Global Clock Timing Parameters |            |          |          |          |        |  |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------|------------|----------|----------|----------|--------|--|--|--|--|--|--|

| Parameter            | Fast                                                            | Corner     | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |  |  |  |  |

|                      | Industrial                                                      | Commercial | Grade    | Grade    | Grade    | Oilits |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.861                                                           | 1.878      | 3.115    | 3.465    | 4.143    | ns     |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.696                                                           | 1.713      | 2.873    | 3.195    | 3.819    | ns     |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.254                                                          | -0.237     | 0.171    | 0.179    | 0.206    | ns     |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.419                                                          | -0.402     | -0.071   | -0.091   | -0.118   | ns     |  |  |  |  |  |  |

| Table 4–72. EP2SGX90 Row Pins Global Clock Timing Parameters |             |            |          |          |          |        |  |

|--------------------------------------------------------------|-------------|------------|----------|----------|----------|--------|--|

| Parameter                                                    | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |

|                                                              | Industrial  | Commercial | Grade    | Grade    | Grade    | Ullita |  |

| t <sub>CIN</sub>                                             | 1.634       | 1.650      | 2.768    | 3.076    | 3.678    | ns     |  |

| t <sub>COUT</sub>                                            | 1.639       | 1.655      | 2.764    | 3.072    | 3.673    | ns     |  |

| t <sub>PLLCIN</sub>                                          | -0.481      | -0.465     | -0.189   | -0.223   | -0.279   | ns     |  |

| t <sub>PLLCOUT</sub>                                         | -0.476      | -0.46      | -0.193   | -0.227   | -0.284   | ns     |  |

| Table 4–73. EP2SGX90 Column Pins Regional Clock Timing Parameters |             |            |          |          |          |       |  |  |

|-------------------------------------------------------------------|-------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                         | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Unito |  |  |

|                                                                   | Industrial  | Commercial | Grade    | Grade    | Grade    | Units |  |  |

| t <sub>CIN</sub>                                                  | 1.688       | 1.702      | 2.896    | 3.224    | 3.856    | ns    |  |  |

| t <sub>COUT</sub>                                                 | 1.551       | 1.569      | 2.893    | 3.220    | 3.851    | ns    |  |  |

| t <sub>PLLCIN</sub>                                               | -0.105      | -0.089     | 0.224    | 0.241    | 0.254    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                              | -0.27       | -0.254     | 0.224    | 0.241    | 0.254    | ns    |  |  |

| Table 4–77. EP2SGX130 Column Pins Regional Clock Timing Parameters |             |            |          |          |          |        |  |  |

|--------------------------------------------------------------------|-------------|------------|----------|----------|----------|--------|--|--|

| Parameter                                                          | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |

|                                                                    | Industrial  | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |

| t <sub>CIN</sub>                                                   | 1.815       | 1.834      | 3.218    | 3.417    | 4.087    | ns     |  |  |

| t <sub>COUT</sub>                                                  | 1.650       | 1.669      | 3.218    | 3.417    | 4.087    | ns     |  |  |

| t <sub>PLLCIN</sub>                                                | 0.116       | 0.134      | 0.349    | 0.364    | 0.426    | ns     |  |  |

| t <sub>PLLCOUT</sub>                                               | -0.049      | -0.031     | 0.361    | 0.378    | 0.444    | ns     |  |  |

| Table 4–78. EP2SGX130 Row Pins Regional Clock Timing Parameters |             |            |          |          |          |        |  |  |

|-----------------------------------------------------------------|-------------|------------|----------|----------|----------|--------|--|--|

| Parameter                                                       | Fast Corner |            | -3 Speed | -4 Speed | -5 Speed | Units  |  |  |

|                                                                 | Industrial  | Commercial | Grade    | Grade    | Grade    | UIIIIS |  |  |

| t <sub>CIN</sub>                                                | 1.544       | 1.560      | 3.195    | 3.395    | 4.060    | ns     |  |  |

| t <sub>COUT</sub>                                               | 1.549       | 1.565      | 3.195    | 3.395    | 4.060    | ns     |  |  |

| t <sub>PLLCIN</sub>                                             | -0.149      | -0.132     | 0.34     | 0.356    | 0.417    | ns     |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.144      | -0.127     | 0.342    | 0.356    | 0.417    | ns     |  |  |

## **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, the intra-clock network skew adder is not specified. Table 4–79 specifies the intra-clock skew between any two clock networks driving any registers in the Stratix II GX device.

| Table 4–79. Clock Network Specifications (Part 1 of 2) |                                  |     |     |                                             |      |  |  |  |

|--------------------------------------------------------|----------------------------------|-----|-----|---------------------------------------------|------|--|--|--|

| Name                                                   | Description                      | Min | Тур | Max                                         | Unit |  |  |  |

| Clock skew adder                                       | Inter-clock network, same side   |     |     | ±50                                         | ps   |  |  |  |

| EP2SGX30 (1)                                           | Inter-clock network, entire chip |     |     | ±100                                        | ps   |  |  |  |

| Clock skew adder                                       | Inter-clock network, same side   |     |     | ±50                                         | ps   |  |  |  |

| EP2SGX60 (1)                                           | Inter-clock network, entire chip |     |     | ±50 p<br>±100 p<br>±50 p<br>±100 p<br>±55 p | ps   |  |  |  |

| Clock skew adder                                       | Inter-clock network, same side   |     |     | ±55                                         | ps   |  |  |  |

| EP2SGX90 (1)                                           | Inter-clock network, entire chip |     |     | ±110                                        | ps   |  |  |  |

| Table 4–91. Stra         | Table 4–91. Stratix II GX Maximum Output Clock Rate for Column Pins (Part 3 of 3) |                |                |                |      |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|--|--|--|

| I/O Standard             | Drive Strength                                                                    | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |  |  |  |

| Differential             | 4 mA                                                                              | 200            | 150            | 150            | MHz  |  |  |  |  |

| SSTL-18 Class I          | 6 mA                                                                              | 350            | 250            | 200            | MHz  |  |  |  |  |

|                          | 8 mA                                                                              | 450            | 300            | 300            | MHz  |  |  |  |  |

|                          | 10 mA                                                                             | 500            | 400            | 400            | MHz  |  |  |  |  |

|                          | 12 mA                                                                             | 700            | 550            | 400            | MHz  |  |  |  |  |

| Differential             | 8 mA                                                                              | 200            | 200            | 150            | MHz  |  |  |  |  |

| SSTL-18 Class II         | 16 mA                                                                             | 400            | 350            | 350            | MHz  |  |  |  |  |

|                          | 18 mA                                                                             | 450            | 400            | 400            | MHz  |  |  |  |  |

|                          | 20 mA                                                                             | 550            | 500            | 450            | MHz  |  |  |  |  |

| 1.8-V HSTL               | 4 mA                                                                              | 300            | 300            | 300            | MHz  |  |  |  |  |

| differential<br>Class I  | 6 mA                                                                              | 500            | 450            | 450            | MHz  |  |  |  |  |

| Class I                  | 8 mA                                                                              | 650            | 600            | 600            | MHz  |  |  |  |  |

|                          | 10 mA                                                                             | 700            | 650            | 600            | MHz  |  |  |  |  |

|                          | 12 mA                                                                             | 700            | 700            | 650            | MHz  |  |  |  |  |

| 1.8-V HSTL               | 16 mA                                                                             | 500            | 500            | 450            | MHz  |  |  |  |  |

| differential<br>Class II | 18 mA                                                                             | 550            | 500            | 500            | MHz  |  |  |  |  |

| Class II                 | 20 mA                                                                             | 650            | 550            | 550            | MHz  |  |  |  |  |

| 1.5-V HSTL               | 4 mA                                                                              | 350            | 300            | 300            | MHz  |  |  |  |  |

| differential<br>Class I  | 6 mA                                                                              | 500            | 500            | 450            | MHz  |  |  |  |  |

| Ciass I                  | 8 mA                                                                              | 700            | 650            | 600            | MHz  |  |  |  |  |

|                          | 10 mA                                                                             | 700            | 700            | 650            | MHz  |  |  |  |  |

|                          | 12 mA                                                                             | 700            | 700            | 700            | MHz  |  |  |  |  |

| 1.5-V HSTL               | 16 mA                                                                             | 600            | 600            | 550            | MHz  |  |  |  |  |

| differential<br>Class II | 18 mA                                                                             | 650            | 600            | 600            | MHz  |  |  |  |  |

| Ciass II                 | 20 mA                                                                             | 700            | 650            | 600            | MHz  |  |  |  |  |

$<sup>(1) \</sup>quad \text{This is the default setting in the Quartus II software}.$

Table 4–96. Stratix II GX Maximum Output Clock Rate for Dedicated Clock Pins (Series Termination) (Part 2 of 2)

| I/O Standard                        | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |

|-------------------------------------|----------------|----------------|----------------|----------------|------|

| SSTL-18 Class II                    | OCT_25_OHMS    | 550            | 500            | 450            | MHz  |

| 1.5-V HSTL<br>Class I               | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |

| 1.8-V HSTL<br>Class I               | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |

| 1.8-V HSTL<br>Class II              | OCT_25_OHMS    | 500            | 500            | 450            | MHz  |

| DIfferential<br>SSTL-2 Class I      | OCT_50_OHMS    | 600            | 500            | 500            | MHz  |

| DIfferential<br>SSTL-2 Class II     | OCT_25_OHMS    | 600            | 550            | 500            | MHz  |

| DIfferential<br>SSTL-18 Class I     | OCT_50_OHMS    | 560            | 400            | 350            | MHz  |

| DIfferential<br>SSTL-18 Class II    | OCT_25_OHMS    | 550            | 500            | 450            | MHz  |

| 1.8-V differential<br>HSTL Class I  | OCT_50_OHMS    | 650            | 600            | 600            | MHz  |

| 1.8-V differential<br>HSTL Class II | OCT_25_OHMS    | 500            | 500            | 450            | MHz  |

| 1.5-V differential<br>HSTL Class I  | OCT_50_OHMS    | 600            | 550            | 500            | MHz  |

Table 4–97 specifies the derating factors for the output clock toggle rate for a non 0 pF load.

| Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 1 of 5) |                   |      |           |          |          |          |         |           |                     |     |

|-----------------------------------------------------------------------------|-------------------|------|-----------|----------|----------|----------|---------|-----------|---------------------|-----|

|                                                                             |                   | N    | laximum   | Output C | lock Tog | gle Rate | Deratin | g Factors | s (ps/pF            | )   |

| I/O Standard                                                                | Drive<br>Strength | Coli | ımn I/O F | Pins     | Ro       | w I/O Pi | ns      |           | icated C<br>Outputs |     |

|                                                                             |                   | -3   | -4        | -5       | -3       | -4       | -5      | -3        | -4                  | -5  |

| 3.3-V LVTTL                                                                 | 4 mA              | 478  | 510       | 510      | 478      | 510      | 510     | 466       | 510                 | 510 |

|                                                                             | 8 mA              | 260  | 333       | 333      | 260      | 333      | 333     | 291       | 333                 | 333 |

|                                                                             | 12 mA             | 213  | 247       | 247      | 213      | 247      | 247     | 211       | 247                 | 247 |

|                                                                             | 16 mA             | 136  | 197       | 197      | -        | -        | -       | 166       | 197                 | 197 |

|                                                                             | 20 mA             | 138  | 187       | 187      | -        | -        | -       | 154       | 187                 | 187 |

|                                                                             | 24 mA             | 134  | 177       | 177      | -        | -        | -       | 143       | 177                 | 177 |

| Table 4–97. Maxin  | Table 4–97. Maximum Output Clock Toggle Rate Derating Factors (Part 4 of 5) |      |           |          |              |          |         |                            |          |     |

|--------------------|-----------------------------------------------------------------------------|------|-----------|----------|--------------|----------|---------|----------------------------|----------|-----|

|                    |                                                                             | N    | 1aximum   | Output C | lock Tog     | gle Rate | Deratin | g Factors                  | s (ps/pF | )   |

| I/O Standard       | Drive<br>Strength                                                           | Coli | ımn I/O F | Pins     | Row I/O Pins |          |         | Dedicated Clock<br>Outputs |          |     |

|                    |                                                                             | -3   | -4        | -5       | -3           | -4       | -5      | -3                         | -4       | -5  |

| 1.5-V HSTL         | 16 mA                                                                       | 95   | 101       | 101      | -            | -        | -       | 96                         | 101      | 101 |

| Class II           | 18 mA                                                                       | 95   | 100       | 100      | -            | -        | -       | 101                        | 100      | 100 |

|                    | 20 mA                                                                       | 94   | 101       | 101      | -            | -        | -       | 104                        | 101      | 101 |

| 2.5-V differential | 8 mA                                                                        | 364  | 680       | 680      | -            | -        | -       | 350                        | 680      | 680 |

| SSTL Class II (3)  | 12 mA                                                                       | 163  | 207       | 207      | -            | -        | -       | 188                        | 207      | 207 |

|                    | 16 mA                                                                       | 118  | 147       | 147      | -            | -        | ı       | 94                         | 147      | 147 |

|                    | 20 mA                                                                       | 99   | 122       | 122      | -            | -        | -       | 87                         | 122      | 122 |

|                    | 24 mA                                                                       | 91   | 116       | 116      | -            | -        | ·       | 85                         | 116      | 116 |

| 1.8-V differential | 4 mA                                                                        | 458  | 570       | 570      | -            | -        | ·       | 505                        | 570      | 570 |

| SSTL Class I (3)   | 6 mA                                                                        | 305  | 380       | 380      | -            | -        | -       | 336                        | 380      | 380 |

|                    | 8 mA                                                                        | 225  | 282       | 282      | -            | -        | -       | 248                        | 282      | 282 |

|                    | 10 mA                                                                       | 167  | 220       | 220      | -            | -        | -       | 190                        | 220      | 220 |

|                    | 12 mA                                                                       | 129  | 175       | 175      | -            | -        | -       | 148                        | 175      | 175 |

| 1.8-V differential | 8 mA                                                                        | 173  | 206       | 206      | -            | -        | ·       | 155                        | 206      | 206 |

| SSTL Class II (3)  | 16 mA                                                                       | 150  | 160       | 160      | -            | -        | ·       | 140                        | 160      | 160 |

|                    | 18 mA                                                                       | 120  | 130       | 130      | -            | -        | -       | 110                        | 130      | 130 |

|                    | 20 mA                                                                       | 109  | 127       | 127      | -            | -        | -       | 94                         | 127      | 127 |

| 1.8-V differential | 4 mA                                                                        | 245  | 282       | 282      | -            | -        | -       | 229                        | 282      | 282 |

| HSTL Class I (3)   | 6 mA                                                                        | 164  | 188       | 188      | -            | -        | -       | 153                        | 188      | 188 |

|                    | 8 mA                                                                        | 123  | 140       | 140      | -            | -        | -       | 114                        | 140      | 140 |

|                    | 10 mA                                                                       | 110  | 124       | 124      | -            | -        | -       | 108                        | 124      | 124 |

|                    | 12 mA                                                                       | 97   | 110       | 110      | -            | -        | -       | 104                        | 110      | 110 |

| 1.8-V differential | 16 mA                                                                       | 101  | 104       | 104      | -            | -        | -       | 99                         | 104      | 104 |

| HSTL Class II (3)  | 18 mA                                                                       | 98   | 102       | 102      | -            | -        | -       | 93                         | 102      | 102 |

|                    | 20 mA                                                                       | 93   | 99        | 99       | -            | -        | -       | 88                         | 99       | 99  |

| 1.5-V differential | 4 mA                                                                        | 168  | 196       | 196      | -            | -        | -       | 188                        | 196      | 196 |

| HSTL Class I (3)   | 6 mA                                                                        | 112  | 131       | 131      | -            | -        | -       | 125                        | 131      | 131 |

|                    | 8 mA                                                                        | 84   | 99        | 99       | -            | -        | -       | 95                         | 99       | 99  |

|                    | 10 mA                                                                       | 87   | 98        | 98       | -            | -        | -       | 90                         | 98       | 98  |

|                    | 12 mA                                                                       | 86   | 98        | 98       | -            | -        | -       | 87                         | 98       | 98  |

г

| Table 4–115. DQS Bus Clock Skew Adder Specifications (t <sub>DQS</sub> _CLOCK_SKEW_ADDER) |                               |  |  |  |

|-------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| Mode                                                                                      | DQS Clock Skew Adder (ps) (1) |  |  |  |

| 4 DQ per DQS                                                                              | 40                            |  |  |  |

| 9 DQ per DQS                                                                              | 70                            |  |  |  |

75

95

This skew specification is the absolute maximum and minimum skew. For example, skew on a 40 DQ group is 40 ps or 20 ps.

| Table 4–116. DQS Phase Offset Delay Per Stage (ps) Notes (1), (2), (3) |          |        |          |          |  |  |

|------------------------------------------------------------------------|----------|--------|----------|----------|--|--|

| Speed Crede                                                            | Positive | Offset | Negative | e Offset |  |  |

| Speed Grade                                                            | Min      | Max    | Min      | Max      |  |  |

| -3                                                                     | 10       | 15     | 8        | 11       |  |  |

| -4                                                                     | 10       | 15     | 8        | 11       |  |  |

| -5                                                                     | 10       | 16     | 8        | 12       |  |  |

(1) The delay settings are linear.

18 DQ per DQS

36 DQ per DQS

- (2) The valid settings for phase offset are -32 to +31.

- (3) The typical value equals the average of the minimum and maximum values.

## JTAG Timing Specifications

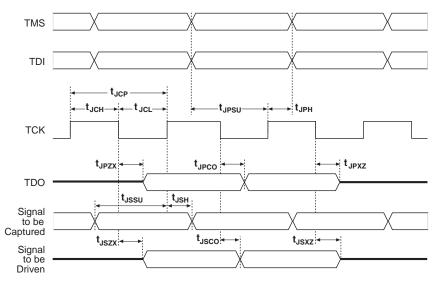

Figure 4–14 shows the timing requirements for the JTAG signals

Figure 4-14. Stratix II GX JTAG Waveforms.

Table 4–117 shows the JTAG timing parameters and values for Stratix II GX devices.

| Table 4-          | Table 4–117. Stratix II GX JTAG Timing Parameters and Values |     |     |      |  |  |  |  |  |

|-------------------|--------------------------------------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol            | Parameter                                                    | Min | Max | Unit |  |  |  |  |  |

| t <sub>JCP</sub>  | TCK clock period                                             | 30  |     | ns   |  |  |  |  |  |

| t <sub>JCH</sub>  | TCK clock high time                                          | 12  |     | ns   |  |  |  |  |  |

| t <sub>JCL</sub>  | TCK clock low time                                           | 12  |     | ns   |  |  |  |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                                         | 4   |     | ns   |  |  |  |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                                          | 5   |     | ns   |  |  |  |  |  |

| t <sub>JPCO</sub> | JTAG port clock to output                                    |     | 9   | ns   |  |  |  |  |  |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output                     |     | 9   | ns   |  |  |  |  |  |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance                     |     | 9   | ns   |  |  |  |  |  |

| t <sub>JSSU</sub> | Capture register setup time                                  | 4   |     | ns   |  |  |  |  |  |

| t <sub>JSH</sub>  | Capture register hold time                                   | 5   |     | ns   |  |  |  |  |  |

| t <sub>JSCO</sub> | Update register clock to output                              |     | 12  | ns   |  |  |  |  |  |

| t <sub>JSZX</sub> | Update register high impedance to valid output               |     | 12  | ns   |  |  |  |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance               |     | 12  | ns   |  |  |  |  |  |