Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 3022                                                       |

| Number of Logic Elements/Cells | 60440                                                      |

| Total RAM Bits                 | 2544192                                                    |

| Number of I/O                  | 364                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2sgx60cf780c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1–3. Stratix II GX FineLine BGA Package Sizes |          |            |            |  |  |  |  |

|-----------------------------------------------------|----------|------------|------------|--|--|--|--|

| Dimension                                           | 780 Pins | 1,152 Pins | 1,508 Pins |  |  |  |  |

| Pitch (mm)                                          | 1.00     | 1.00       | 1.00       |  |  |  |  |

| Area (mm²)                                          | 841      | 1,225      | 1,600      |  |  |  |  |

| Length width (mm × mm)                              | 29 × 29  | 35 × 35    | 40 × 40    |  |  |  |  |

# Referenced Document

This chapter references the following document:

Stratix II GX Architecture chapter in volume 1 of the Stratix II GX Device Handbook

# Document Revision History

Table 1–4 shows the revision history for this chapter.

| Table 1–4. Docume            | nt Revision History                                                                                                                                                                                                          |                                                                             |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Date and Document<br>Version | Changes Made                                                                                                                                                                                                                 | Summary of Changes                                                          |

| October 2007, v1.6           | Updated "Features" section.                                                                                                                                                                                                  |                                                                             |

|                              | Minor text edits.                                                                                                                                                                                                            |                                                                             |

| August 2007, v1.5            | Added "Referenced Documents" section.                                                                                                                                                                                        |                                                                             |

|                              | Minor text edits.                                                                                                                                                                                                            |                                                                             |

| February 2007, v1.4          | <ul> <li>Changed 622 Mbps to 600 Mbps on page 1-2 and Table 1-1.</li> <li>Deleted "DC coupling" from the Transceiver Block Features list.</li> <li>Changed 4 to 6 in the PLLs row (columns 3 and 4) of Table 1-1.</li> </ul> |                                                                             |

|                              | Added the "Document Revision History" section to this chapter.                                                                                                                                                               | Added support information for the Stratix II GX device.                     |

| June 2006, v1.3              | Updated Table 1–2.                                                                                                                                                                                                           |                                                                             |

| April 2006, v1.2             | <ul><li>Updated Table 1–1.</li><li>Updated Table 1–2.</li></ul>                                                                                                                                                              | Updated numbers for receiver channels and user I/O pin counts in Table 1–2. |

| February 2006, v1.1          | Updated Table 1–1.                                                                                                                                                                                                           |                                                                             |

| October 2005<br>v1.0         | Added chapter to the <i>Stratix II GX Device Handbook</i> .                                                                                                                                                                  |                                                                             |

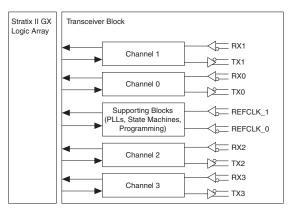

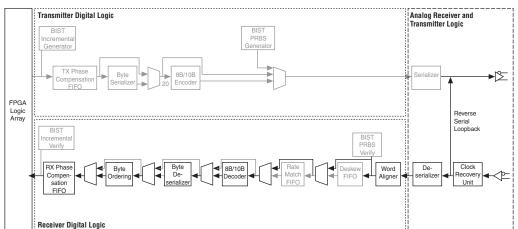

Figure 2-2. Elements of the Transceiver Block

Each Stratix II GX transceiver channel consists of a transmitter and receiver. The transceivers are grouped in four and share PLL resources. Each transmitter has access to one of two PLLs. The transmitter contains the following:

- Transmitter phase compensation first-in first-out (FIFO) buffer

- Byte serializer (optional)

- 8B/10B encoder (optional)

- Serializer (parallel-to-serial converter)

- Transmitter differential output buffer

The receiver contains the following:

- Receiver differential input buffer

- Receiver lock detector and run length checker

- Clock recovery unit (CRU)

- Deserializer

- Pattern detector

- Word aligner

- Lane deskew

- Rate matcher (optional)

- 8B/10B decoder (optional)

- Byte deserializer (optional)

- Byte ordering

- Receiver phase compensation FIFO buffer

Designers can preset Stratix II GX transceiver functions using the Quartus  $^{\otimes}$  II software. In addition, pre-emphasis, equalization, and differential output voltage ( $V_{OD}$ ) are dynamically programmable. Each Stratix II GX transceiver channel supports various loopback modes and is

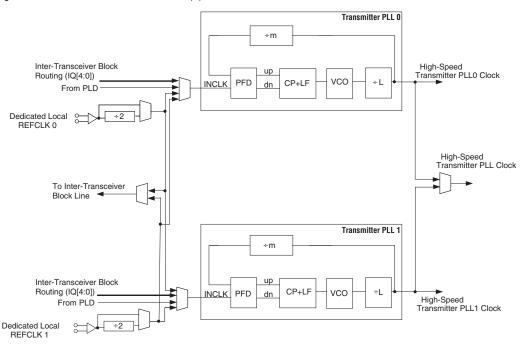

Figure 2-4. Transmitter PLL Block Note (1)

Note to Figure 2-4:

(1) The global clock line must be driven by an input pin.

The transmitter PLLs support data rates up to 6.375 Gbps. The input clock frequency is limited to 622.08 MHz. An optional pll\_locked port is available to indicate whether the transmitter PLL is locked to the reference clock. Both transmitter PLLs have a programmable loop bandwidth parameter that can be set to low, medium, or high. The loop bandwidth parameter can be statically set in the Quartus II software.

Table 2–2 lists the adjustable parameters in the transmitter PLL.

| Table 2–2. Transmitter PLL Specifications |                            |  |  |  |

|-------------------------------------------|----------------------------|--|--|--|

| Parameter                                 | Specifications             |  |  |  |

| Input reference frequency range           | 50 MHz to 622.08 MHz       |  |  |  |

| Data rate support                         | 600 Mbps to 6.375 Gbps     |  |  |  |

| Multiplication factor (W)                 | 1, 4, 5, 8, 10, 16, 20, 25 |  |  |  |

| Bandwidth                                 | Low, medium, or high       |  |  |  |

- Lane deskew

- Rate matcher

- 8B/10B decoder

- Byte deserializer

- Byte ordering

- Receiver phase compensation FIFO buffer

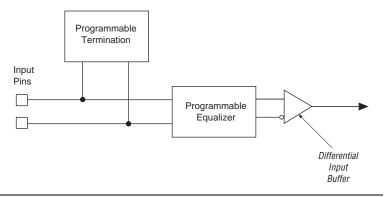

#### Receiver Input Buffer

The Stratix II GX receiver input buffer supports the 1.2-V and 1.5-V PCML I/O standard at rates up to 6.375 Gbps. The common mode voltage of the receiver input buffer is programmable between 0.85 V and 1.2 V. You must select the 0.85 V common mode voltage for AC- and DC-coupled PCML links and the 1.2 V common mode voltage for DC-coupled LVDS links.

The receiver has programmable on-chip 100-, 120-, or 150- $\Omega$  differential termination for different protocols, as shown in Figure 2–12. The receiver's internal termination can be disabled if external terminations and biasing are provided. The receiver and transmitter differential termination resistances can be set independently of each other.

Figure 2–12. Receiver Input Buffer

#### Programmable Termination

The programmable termination can be statically set in the Quartus II software. Figure 2–13 shows the setup for programmable receiver termination. The termination can be disabled if external termination is provided.

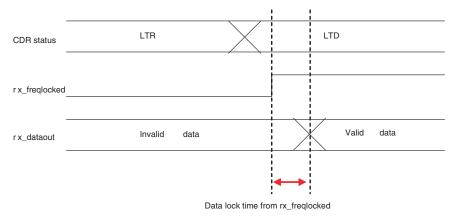

The CRU has a built-in switchover circuit to select whether the PLL VCO is aligned by the reference clock or the data. The optional port rx\_freqlocked monitors when the CRU is in locked-to-data mode.

In the automatic mode, the CRU PLL must be within the prescribed PPM frequency threshold setting of the CRU reference clock for the CRU to switch from locked-to-reference to locked-to-data mode.

The automatic switchover circuit can be overridden by using the optional ports rx\_locktorefclk and rx\_locktodata. Table 2–6 shows the possible combinations of these two signals.

| Table 2–6. Receiver Lock Combinations |                 |                    |  |  |  |  |  |

|---------------------------------------|-----------------|--------------------|--|--|--|--|--|

| rx_locktodata                         | rx_locktorefclk | VCO (Lock to Mode) |  |  |  |  |  |

| 0                                     | 0               | Auto               |  |  |  |  |  |

| 0                                     | 1               | Reference clock    |  |  |  |  |  |

| 1                                     | х               | Data               |  |  |  |  |  |

If the rx\_locktorefclk and rx\_locktodata ports are not used, the default is auto mode.

### Deserializer (Serial-to-Parallel Converter)

The deserializer converts a serial bitstream into 8, 10, 16, or 20 bits of parallel data. The deserializer receives the LSB first. Figure 2–17 shows the deserializer.

Analog Receiver and Transmitter Digital Logic Transmitter Logic BIST BIST PRBS Incrementa Generator Generator Byte **►**|S Compensation FIFO Encoder FPGA Loopback Logic Array ncrementa Verify RX Phase 8B/10B Word Ďe-Compen Aligner sation FIFO **Receiver Digital Logic**

Figure 2–25 shows the data path in parallel loopback mode.

#### Reverse Serial Loopback

Figure 2-25. Stratix II GX Block in Parallel Loopback Mode

The reverse serial loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, passes through the CRU unit, and the retimed serial data is looped back and transmitted though the high-speed differential transmitter output buffer.

Figure 2–26 shows the data path in reverse serial loopback mode.

Figure 2–26. Stratix II GX Block in Reverse Serial Loopback Mode

#### Reverse Serial Pre-CDR Loopback

The reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received since the signal goes through the output buffer and the VOD is changed to the VOD setting level. The pre-emphasis settings have no effect.

Table 2-13. Available Clocking Connections for Transceivers in 2SGX60E **Clock Resource Transceiver** Region Bank 13 Bank 14 Bank 15 Regional **Global Clock** Clock 8 Clock I/O 8 Clock I/O 8 Clock I/O Region0 RCLK 20-27 **✓** 8 LRIO clock Region1 RCLK 20-27 8 LRIO clock Region2 RCLK 12-19 8 LRIO clock RCLK 12-19 Region3 8 LRIO clock

| Region                  | Clock           | Resource          |                        | Transceiver            |                        |                        |  |  |  |

|-------------------------|-----------------|-------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|

|                         | Global<br>Clock | Regional<br>Clock | Bank 13<br>8 Clock I/O | Bank 14<br>8 Clock I/O | Bank 15<br>8 clock I/O | Bank 16<br>8 Clock I/O |  |  |  |

| Region0<br>8 LRIO clock | <b>✓</b>        | RCLK 20-27        | <b>✓</b>               |                        |                        |                        |  |  |  |

| Region1<br>8 LRIO clock | <b>✓</b>        | RCLK 20-27        |                        | ✓                      |                        |                        |  |  |  |

| Region2<br>8 LRIO clock | <b>✓</b>        | RCLK 12-19        |                        |                        | ✓                      |                        |  |  |  |

| Region3<br>8 LRIO clock | <b>✓</b>        | RCLK 12-19        |                        |                        |                        | ~                      |  |  |  |

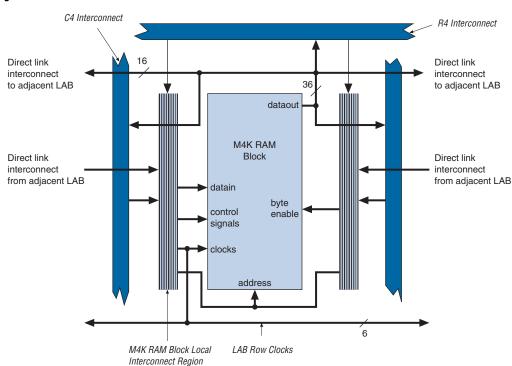

The RAM blocks in Stratix II GX devices have local interconnects to allow ALMs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, C4, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. The M512 RAM block has up to 16 direct link input connections from the left adjacent LABs and another 16 from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through direct link interconnect. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–50 shows the M512 RAM block to logic array interface.

Figure 2-50. M512 RAM Block LAB Row Interface

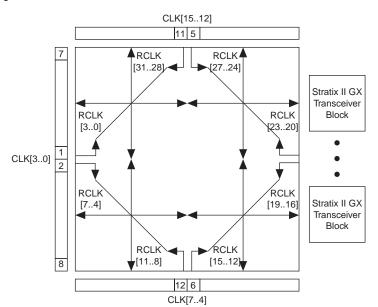

Figure 2-62. Regional Clocks

#### Dual-Regional Clock Network

A single source (CLK pin or PLL output) can generate a dual-regional clock by driving two regional clock network lines in adjacent quadrants (one from each quadrant), which allows logic that spans multiple quadrants to utilize the same low skew clock. The routing of this clock signal on an entire side has approximately the same speed but slightly higher clock skew when compared with a clock signal that drives a single quadrant. Internal logic-array routing can also drive a dual-regional clock. Clock pins and enhanced PLL outputs on the top and bottom can drive horizontal dual-regional clocks. Clock pins and fast PLL outputs on the left and right can drive vertical dual-regional clocks, as shown in Figure 2–63. Corner PLLs cannot drive dual-regional clocks.

For more information on tolerance specifications for differential on-chip termination, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

#### On-Chip Series Termination without Calibration

Stratix II GX devices support driver impedance matching to provide the I/O driver with controlled output impedance that closely matches the impedance of the transmission line. As a result, reflections can be significantly reduced. Stratix II GX devices support on-chip series termination for single-ended I/O standards with typical  $R_{\rm S}$  values of 25 and 50  $\Omega$ . Once matching impedance is selected, current drive strength is no longer selectable. Table 2–34 shows the list of output standards that support on-chip series termination without calibration.

For more information about series on-chip termination supported by Stratix II GX devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination without calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

#### On-Chip Series Termination with Calibration

Stratix II GX devices support on-chip series termination with calibration in column I/O pins in top and bottom banks. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip series termination calibration circuit compares the total impedance of each I/O buffer to the external 25- $\Omega$ or 50- $\Omega$ resistors connected to the RUP and RDN pins, and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

For more information about series on-chip termination supported by Stratix II GX devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

For more information about tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD            | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                                                                                                                                                                               |

| EXTEST(1)                 | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                                                                                                                                                                                  |

| BYPASS                    | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                                                                                                                                          |

| USERCODE                  | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                            |

| IDCODE                    | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                                                |

| HIGHZ (1)                 | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                                                                                                   |

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding the I/O pins to a state defined by the data in the boundary-scan register.                                                                                                                                                  |

| ICR instructions          |                  | Used when configuring a Stratix II GX device via the JTAG port with a USB-Blaster™, MasterBlaster™, ByteBlasterMV™, or ByteBlaster II download cable, or when using a .jam or .jbc via an embedded processor or JRunner.                                                                                                                                                                                                             |

| PULSE_NCONFIG             | 00 0000 0001     | Emulates pulsing the ${\tt nCONFIG}$ pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                                                                                                  |

| CONFIG_IO (2)             | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, during, or after configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction holds nSTATUS low to reset the configuration device. nSTATUS is held low until the IOE configuration register is loaded and the TAP controller state machine transitions to the UPDATE_DR state. |

| SignalTap II instructions |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                                                                                                    |

#### *Notes to Table 3–1:*

- (1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

- (2) For more information on using the CONFIG\_IO instruction, refer to the *MorphIO: An I/O Reconfiguration Solution* for Altera Devices White Paper.

Figure 4-2. Lock Time Parameters for Automatic Mode

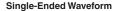

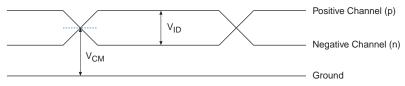

Figures 4–3 and 4–4 show differential receiver input and transmitter output waveforms, respectively.

Figure 4-3. Receiver Input Waveform

#### **Differential Waveform**

#### V<sub>ID</sub> (diff peak-peak) = 2 x V<sub>ID</sub> (single-ended)

| Table 4–19. Strati                    | ix II GX Transceiver B                                                                    | lock AC                               | Specia | fication                                                | Notes ( | (1), (2)                              | , (3) <b>(P</b> | art 4 o | f 19) |      |    |

|---------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|--------|---------------------------------------------------------|---------|---------------------------------------|-----------------|---------|-------|------|----|

| Symbol/<br>Description                | Conditions                                                                                | -3 Speed<br>Commercial Speed<br>Grade |        | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |         | -5 Speed<br>Commercial Speed<br>Grade |                 |         | Unit  |      |    |

|                                       |                                                                                           | Min                                   | Тур    | Max                                                     | Min     | Тур                                   | Max             | Min     | Тур   | Max  |    |

| Sinusoidal jitter                     | Fc/25000                                                                                  |                                       | > 1.5  |                                                         |         | > 1.5                                 |                 |         | > 1.5 | 5    | UI |

| FC-1                                  | Fc/1667                                                                                   |                                       | > 0.1  |                                                         |         | > 0.1                                 |                 |         | > 0.1 |      | U  |

| Deterministic jitter<br>FC-2          | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                     |                                       | > 0.33 | 3                                                       |         | > 0.33                                | 3               |         | > 0.3 | 3    | UI |

| Random jitter FC-2                    | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                     |                                       | > 0.29 | )                                                       |         | > 0.29                                | )               |         | > 0.2 | 9    | UI |

| Sinusoidal jitter                     | Fc/25000                                                                                  |                                       | > 1.5  |                                                         |         | > 1.5                                 |                 |         | > 1.5 | 5    | UI |

| FC-2                                  | Fc/1667                                                                                   |                                       | > 0.1  |                                                         |         | > 0.1                                 |                 |         | > 0.1 |      | UI |

| Deterministic jitter<br>FC-4          | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                     | > 0.33                                |        | > 0.33                                                  |         | > 0.33                                |                 | UI      |       |      |    |

| Random jitter FC-4                    | Pattern = CJTPAT<br>No Equalization<br>DC Gain = 0 dB                                     |                                       | > 0.29 | )                                                       | > 0.29  |                                       | > 0.29          |         | UI    |      |    |

| Sinusoidal jitter                     | Fc/25000                                                                                  |                                       | > 1.5  |                                                         | > 1.5   |                                       | > 1.5           |         | UI    |      |    |

| FC-4                                  | Fc/1667                                                                                   |                                       | > 0.1  |                                                         | > 0.1   |                                       | > 0.1           |         | UI    |      |    |

| XAUI Transmit Jit                     | ter Generation (9)                                                                        |                                       |        |                                                         |         |                                       |                 |         |       |      |    |

| Total jitter at 3.125 Gbps            | REFCLK =<br>156.25 MHz<br>Pattern = CJPAT<br>V <sub>OD</sub> = 1200 mV<br>No Pre-emphasis | -                                     | -      | 0.3                                                     | -       | •                                     | 0.3             | -       | -     | 0.3  | G  |

| Deterministic jitter<br>at 3.125 Gbps | REFCLK =<br>156.25 MHz<br>Pattern = CJPAT<br>V <sub>OD</sub> = 1200 mV<br>No Pre-emphasis | -                                     | -      | 0.17                                                    | -       | -                                     | 0.17            | -       | -     | 0.17 | UI |

| XAUI Receiver Jitt                    | ter Tolerance (9)                                                                         |                                       |        |                                                         |         |                                       |                 |         |       |      |    |

| Total jitter                          | Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB                                      |                                       | > 0.65 | ;<br>                                                   | > 0.65  |                                       | > 0.65          |         | 5     | UI   |    |

| Deterministic jitter                  | Pattern = CJPAT<br>No Equalization<br>DC Gain = 3 dB                                      |                                       | > 0.37 | ,                                                       |         | > 0.37                                | 7               |         | > 0.3 | 7    | UI |

| Table 4–19. Strat                                | ix II GX Transceiver Bl                                                                                                                                                                                     | ock AC                                | Specif | ication                                                 | Notes ( | 1), (2), | (3) <b>(P</b>                         | art 7 o | f 19) |      |    |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|---------------------------------------------------------|---------|----------|---------------------------------------|---------|-------|------|----|

| Symbol/<br>Description                           | Conditions                                                                                                                                                                                                  | -3 Speed<br>Commercial Speed<br>Grade |        | -4 Speed<br>Commercial and<br>Industrial Speed<br>Grade |         |          | -5 Speed<br>Commercial Speed<br>Grade |         |       | Unit |    |

|                                                  |                                                                                                                                                                                                             | Min                                   | Тур    | Max                                                     | Min     | Тур      | Max                                   | Min     | Тур   | Max  |    |

| Sinusoidal Jitter<br>Tolerance<br>(peak-to-peak) | Jitter Frequency = 22.1 KHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps  |                                       | > 8.5  |                                                         |         | > 8.5    |                                       |         | > 8.5 |      | UI |

|                                                  | Jitter Frequency = 1.875 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps |                                       | > 0.1  |                                                         |         | > 0.1    |                                       |         | > 0.1 |      | UI |

|                                                  | Jitter Frequency = 20 MHz Data Rate = 1.25, 2.5, 3.125 Gbps REFCLK = 125 MHz Pattern = CJPAT Equalizer Setting = 0 for 1.25 Gbps Equalizer Setting = 6 for 2.5 Gbps Equalizer Setting = 6 for 3.125 Gbps    |                                       | > 0.1  |                                                         |         | > 0.1    |                                       |         | > 0.1 |      | UI |

| Table 4–41. 1.2-V HSTL Specifications |                           |                          |                  |         |                          |      |  |  |  |

|---------------------------------------|---------------------------|--------------------------|------------------|---------|--------------------------|------|--|--|--|

| Symbol                                | Parameter                 | Conditions               | Minimum          | Typical | Maximum                  | Unit |  |  |  |

| $V_{OH}$                              | High-level output voltage | $I_{OH} = 8 \text{ mA}$  | $V_{REF} + 0.15$ |         | V <sub>CCIO</sub> + 0.15 | ٧    |  |  |  |

| $V_{OL}$                              | Low-level output voltage  | $I_{OH} = -8 \text{ mA}$ | -0.15            |         | V <sub>REF</sub> – 0.15  | V    |  |  |  |

| Table 4-4            | 2. 1.5-V HSTL Class I Specifi | cations                       |                         |         |                        |      |

|----------------------|-------------------------------|-------------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                    | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                               | 1.425                   | 1.5     | 1.575                  | V    |

| V <sub>REF</sub>     | Input reference voltage       |                               | 0.713                   | 0.75    | 0.788                  | V    |

| V <sub>TT</sub>      | Termination voltage           |                               | 0.713                   | 0.75    | 0.788                  | ٧    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                               | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                               | -0.3                    |         | V <sub>REF</sub> - 0.1 | ٧    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                               | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                               |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 8 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | ٧    |

| V <sub>OL</sub>      | Low-level output voltage      | $I_{OH} = -8 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

#### Note to Table 4-42:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

| Table 4-4            | 3. 1.5-V HSTL Class II Specif | ications                     |                         |         |                        |      |

|----------------------|-------------------------------|------------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                   | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                              | 1.425                   | 1.50    | 1.575                  | V    |

| $V_{REF}$            | Input reference voltage       |                              | 0.713                   | 0.75    | 0.788                  | V    |

| V <sub>TT</sub>      | Termination voltage           |                              | 0.713                   | 0.75    | 0.788                  | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                              | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                              | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                              | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                              |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 16 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OH</sub> = -16 mA (1) |                         |         | 0.4                    | ٧    |

#### Note to Table 4-43:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

# Power Consumption

Altera offers two ways to calculate power for a design: the Excel-based PowerPlay early power estimator power calculator and the Quartus<sup>®</sup> II PowerPlay power analyzer feature.

The interactive Excel-based PowerPlay early power estimator is typically used prior to designing the FPGA in order to get an estimate of device power. The Quartus II PowerPlay power analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The power analyzer can apply a combination of user-entered, simulation-derived and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

For more information on PowerPlay tools, refer to the *PowerPlay Early Power Estimators* (*EPE*) and *Power Analyzer*, the *Quartus II PowerPlay Analysis and Optimization Technology*, and the *PowerPlay Power Analyzer* chapter in volume 3 of the *Quartus II Handbook*. The PowerPlay early power estimators are available on the Altera web site at **www.altera.com**.

See Table 4–23 on page 42 for typical I<sub>CC</sub> standby specifications.

## **Timing Model**

The DirectDrive technology and MultiTrack interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix II GX device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

### **Preliminary and Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–52 shows the status of the Stratix II GX device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

| Table 4–86. Stratix II GX I/O Output Delay for Column Pins (Part 1 of 7) |                   |                  |                                          |                       |                       |                   |                   |      |

|--------------------------------------------------------------------------|-------------------|------------------|------------------------------------------|-----------------------|-----------------------|-------------------|-------------------|------|

| I/O Standard                                                             | Drive<br>Strength | Parameter        | Fast Corner<br>Industrial/<br>Commercial | -3 Speed<br>Grade (3) | -3 Speed<br>Grade (4) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| LVTTL                                                                    | 4 mA              | t <sub>OP</sub>  | 1236                                     | 2351                  | 2467                  | 2624              | 2820              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1258                                     | 2417                  | 2537                  | 2698              | 2910              | ps   |

|                                                                          | 8 mA              | t <sub>OP</sub>  | 1091                                     | 2036                  | 2136                  | 2272              | 2448              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1113                                     | 2102                  | 2206                  | 2346              | 2538              | ps   |

|                                                                          | 12 mA             | t <sub>OP</sub>  | 1024                                     | 2036                  | 2136                  | 2272              | 2448              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1046                                     | 2102                  | 2206                  | 2346              | 2538              | ps   |

|                                                                          | 16 mA             | t <sub>OP</sub>  | 998                                      | 1893                  | 1986                  | 2112              | 2279              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1020                                     | 1959                  | 2056                  | 2186              | 2369              | ps   |

|                                                                          | 20 mA             | t <sub>OP</sub>  | 976                                      | 1787                  | 1875                  | 1994              | 2154              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 998                                      | 1853                  | 1945                  | 2068              | 2244              | ps   |

|                                                                          | 24 mA (1)         | t <sub>OP</sub>  | 969                                      | 1788                  | 1876                  | 1995              | 2156              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 991                                      | 1854                  | 1946                  | 2069              | 2246              | ps   |

| LVCMOS                                                                   | 4 mA              | t <sub>OP</sub>  | 1091                                     | 2036                  | 2136                  | 2272              | 2448              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1113                                     | 2102                  | 2206                  | 2346              | 2538              | ps   |

|                                                                          | 8 mA              | t <sub>OP</sub>  | 999                                      | 1786                  | 1874                  | 1993              | 2153              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1021                                     | 1852                  | 1944                  | 2067              | 2243              | ps   |

|                                                                          | 12 mA             | t <sub>OP</sub>  | 971                                      | 1720                  | 1805                  | 1919              | 2075              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 993                                      | 1786                  | 1875                  | 1993              | 2165              | ps   |

|                                                                          | 16 mA             | t <sub>OP</sub>  | 978                                      | 1693                  | 1776                  | 1889              | 2043              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 1000                                     | 1759                  | 1846                  | 1963              | 2133              | ps   |

|                                                                          | 20 mA             | t <sub>OP</sub>  | 965                                      | 1677                  | 1759                  | 1871              | 2025              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 987                                      | 1743                  | 1829                  | 1945              | 2115              | ps   |

|                                                                          | 24 mA (1)         | t <sub>OP</sub>  | 954                                      | 1659                  | 1741                  | 1851              | 2003              | ps   |

|                                                                          |                   | t <sub>DIP</sub> | 976                                      | 1725                  | 1811                  | 1925              | 2093              | ps   |

| Table 4–88. Stratix II GX Maximum Input Clock Rate for Column I/O Pins (Part 2 of 2) |                |                |                |      |  |

|--------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                         | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| Differential SSTL-18<br>Class I I                                                    | 500            | 500            | 500            | MHz  |  |

| 1.8-V differential<br>HSTL Class I                                                   | 500            | 500            | 500            | MHz  |  |

| 1.8-V differential<br>HSTL Class II                                                  | 500            | 500            | 500            | MHz  |  |

| 1.5-V differential<br>HSTL Class I                                                   | 500            | 500            | 500            | MHz  |  |

| .5-V differential 500<br>HSTL Class I I                                              |                | 500            | 500            | MHz  |  |

| 1.2-V HSTL                                                                           | 280            | 250            | 250            | MHz  |  |

| 1.2-V differential<br>HSTL                                                           | 280            | 250            | 250            | MHz  |  |

Table 4–89 shows the maximum input clock toggle rates for Stratix II GX device row pins.

| Table 4–89. Stratix II GX Maximum Input Clock Rate for Row I/O Pins (Part 1 of 2) |                |                |                |      |  |

|-----------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                      | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| LVTTL                                                                             | 500            | 500            | 450            | MHz  |  |

| 2.5 V                                                                             | 500            | 500            | 450            | MHz  |  |

| 1.8 V                                                                             | 500            | 500            | 450            | MHz  |  |

| 1.5 V                                                                             | 500            | 500            | 450            | MHz  |  |

| LVCMOS                                                                            | 500            | 500            | 450            | MHz  |  |

| SSTL-2 Class I                                                                    | 500            | 500            | 500            | MHz  |  |

| SSTL-2 Class II                                                                   | 500            | 500            | 500            | MHz  |  |

| SSTL-18 Class I                                                                   | 500            | 500            | 500            | MHz  |  |

| SSTL-18 Class II                                                                  | 500            | 500            | 500            | MHz  |  |

| 1.5-V HSTL Class I                                                                | 500            | 500            | 500            | MHz  |  |

| 1.5-V HSTL Class II                                                               | 500            | 500            | 500            | MHz  |  |

| 1.8-V HSTL Class I                                                                | 500            | 500            | 500            | MHz  |  |

| 1.8-V HSTL Class II                                                               | 500            | 500            | 500            | MHz  |  |

| PCI                                                                               | 500            | 500            | 425            | MHz  |  |

| PCI-X                                                                             | 500            | 500            | 425            | MHz  |  |

| Differential SSTL-2<br>Class I                                                    | 500            | 500            | 500            | MHz  |  |

| Table 4–91. Stratix II GX Maximum Output Clock Rate for Column Pins (Part 2 of 3) |                |                |                |                |      |  |

|-----------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                      | Drive Strength | -3 Speed Grade | -4 Speed Grade | -5 Speed Grade | Unit |  |

| SSTL-18 Class I                                                                   | 4 mA           | 200            | 150            | 150            | MHz  |  |

|                                                                                   | 6 mA           | 350            | 250            | 200            | MHz  |  |

|                                                                                   | 8 mA           | 450            | 300            | 300            | MHz  |  |

|                                                                                   | 10 mA          | 500            | 400            | 400            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 550            | 400            | MHz  |  |

| SSTL-18 Class II                                                                  | 8 mA           | 200            | 200            | 150            | MHz  |  |

|                                                                                   | 16 mA          | 400            | 350            | 350            | MHz  |  |

|                                                                                   | 18 mA          | 450            | 400            | 400            | MHz  |  |

|                                                                                   | 20 mA (1)      | 550            | 500            | 450            | MHz  |  |

| 1.8-V HSTL                                                                        | 4 mA           | 300            | 300            | 300            | MHz  |  |

| Class I                                                                           | 6 mA           | 500            | 450            | 450            | MHz  |  |

|                                                                                   | 8 mA           | 650            | 600            | 600            | MHz  |  |

|                                                                                   | 10 mA          | 700            | 650            | 600            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 700            | 650            | MHz  |  |

| 1.8-V HSTL                                                                        | 16 mA          | 500            | 500            | 450            | MHz  |  |

| Class II                                                                          | 18 mA          | 550            | 500            | 500            | MHz  |  |

|                                                                                   | 20 mA (1)      | 650            | 550            | 550            | MHz  |  |

| 1.5-V HSTL                                                                        | 4 mA           | 350            | 300            | 300            | MHz  |  |

| Class I                                                                           | 6 mA           | 500            | 500            | 450            | MHz  |  |

|                                                                                   | 8 mA           | 700            | 650            | 600            | MHz  |  |

|                                                                                   | 10 mA          | 700            | 700            | 650            | MHz  |  |

|                                                                                   | 12 mA (1)      | 700            | 700            | 700            | MHz  |  |

| 1.5-V HSTL<br>Class II                                                            | 16 mA          | 600            | 600            | 550            | MHz  |  |

|                                                                                   | 18 mA          | 650            | 600            | 600            | MHz  |  |

|                                                                                   | 20 mA (1)      | 700            | 650            | 600            | MHz  |  |

| PCI                                                                               | -              | 1000           | 790            | 670            | MHz  |  |

| PCI-X                                                                             | -              | 1000           | 790            | 670            | MHz  |  |

| Differential<br>SSTL-2 Class I                                                    | 8 mA           | 400            | 300            | 300            | MHz  |  |

|                                                                                   | 12 mA          | 400            | 400            | 350            | MHz  |  |

| Differential<br>SSTL-2 Class II                                                   | 16 mA          | 350            | 350            | 300            | MHz  |  |

|                                                                                   | 20 mA          | 400            | 350            | 350            | MHz  |  |

|                                                                                   | 24 mA          | 400            | 400            | 350            | MHz  |  |